THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# On Compositional Approaches for Discrete Event Systems Verification and Synthesis

SAHAR MOHAJERANI

Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2015 On Compositional Approaches for Discrete Event Systems Verification and Synthesis SAHAR MOHAJERANI ISBN 978-91-7597-140-7

© Sahar Mohajerani, 2015.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr 3821 ISSN 0346-718X

Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY SE–412 96 Göteborg Sweden

Telephone: +46 (031)772-1000

Cover: Abstraction of a finite-state machine with 132 states to an equivalent finite-state machine with 12 states.

Typeset by the author using  $LAT_EX$ .

Chalmers Reproservice Göteborg, Sweden 2015

To my beloved Ali

# Abstract

Over the past decades, human dependability on technical devices has rapidly increased. Many activities of such devices can be described by sequences of events, where the occurrence of an event causes the system to go from one state to another. This is elegantly modelled by *state machines*. Systems that are modelled in this way are referred to as *discrete event systems*. Usually, these systems are highly complex, and appear in settings that are safety critical, where small failures may result in huge financial and/or human losses. Having a control function is one way to guarantee system correctness.

The work presented in this thesis concerns *verification* and *synthesis* of such systems using the *supervisory control theory* proposed by *Ramadge* and *Wonham* [1]. Supervisory control theory provides a general framework to automatically calculate control functions for discrete event systems. Given a model of the system, the *plant* to be controlled, and a *specification* of the desired behaviour, it is possible to automatically compute, i.e. *synthesise*, a *supervisor* that ensures that the specification is satisfied.

Usually, systems are *modular* and consist of several components interacting with each other. Calculating a supervisor for such a system in the straightforward way involves constructing the complete model of the considered system, which may lead to the inherent complexity problem known as the *state-space explosion* problem. This problem occurs as the number of states grows exponentially with the number of components, which makes it intractable to examine the global states of a system due to lack of memory and time.

One way to alleviate the state-space explosion problem is to use a compositional approach. A compositional approach exploits the modular structure of a system to reduce the size of the model. This thesis mainly focuses on developing abstraction methods for the compositional approach in a way that the final verification and synthesis results are the same as it would have been for the nonabstracted system. The algorithms have been implemented in the discrete event system software tool Supremica and have been applied to verify and compute memory efficient supervisors for several large industrial models.

**Keywords:** Finite-state machines, Extended finite-state machines, Verification, Synthesis, Abstraction, Compositional approach, Supervisory control theory.

# Acknowledgements

In three days, I will be sending the thesis for print. This is the final piece of my thesis puzzle, and honestly the hardest part to write, because it has made me realise that my amazing journey as a PhD student is coming to an end. So I will take this last opportunity to try to thank the many wonderful people who have helped me on this journey. Ideally I would've preferred to mention everyone, but space does not allow me to.

My journey began when Martin Fabian believed in me when nobody else, even I myself, did not and for that I can eternally thankful. I cannot describe in words how happy I was when you gave me the news and I'll forever cherish that moment. During the past five years, whenever I felt stressed you calmed me down and I felt like I am talking to my friend instead of my supervisor. Your valuable supervision, encouragement, and support made this work possible. You are the most understanding and the greatest supervisor anybody could ask for and I am forever grateful to you!

After being a PhD student for six months, I had the great opportunity to meet Robi Malik, who then became my co-supervisor. I have visited Robi twice in New Zealand during my PhD studies. You have made the time I spent in New Zealand memorable and fruitful. You not only gave me great guidance and supervision but you also showed me amazing places in New Zealand and never let me feel homesick. I will always appreciate all the great discussions we had and I hope we can collaborate in future. Robi you are awesome and thanks heaps for everything!

I am also grateful to all my former and present colleagues and friends in the automation group for making the environment a really fun place to work in. Thanks to Bengt Lennartson, Knut Åkesson, Peter Falkman, Mona, Nina, Patrik and Sathya. I would specially like to thank Zhennan and Oskar for all the fun discussions, the cheerful memories and all their helps. I would also like to thank my Iranian friends at the Department of Signals and Systems; Roozbeh, Mitra, Azita and Maryam thank you for being great friends and cheering me up whenever I felt down. Big thanks go to my friends Sogol and Alexandra. You are always there for me and your friendship means a lot.

On the administrative side I would like to thank Lars Börjesson, Madeleine

#### ACKNOWLEDGEMENTS

Parsson and Christine Johansson for always being so helpful.

Finally, I would like to give my utmost gratitude to the sweetest people in my life, my family. To my mother, thank you for all your unconditional love. Sara, Maryam and Alireza, I love you guys so much and thanks for being fantastic sisters and brother. To my father in law, for being always supportive and understanding.

Now comes the most important person in my life, Ali. I could never have done this without you. Every amazing thing that has happened in my life is because of you. Your constant support and love has been there for me through the good and tough times. You are my best friend and my soulmate. Being with you is the *marked state* of my life and my life is never complete without you. I will always love you!

> Sahar Mohajerani Göteborg, February 2015

This work was supported by the Swedish Research Council, Vetenskapsrådet (VR).

# List of publications

This thesis is based on the following three appended papers:

#### Paper 1

**S. Mohajerani**, R. Malik, M. Fabian, "A Framework for Compositional Nonblocking Verification of Extended Finite-State Machines", *Invited paper to Journal of Discrete Event Dynamic Systems: Theory and Applications, special issue on WODES 2014.*

#### Paper 2

**S. Mohajerani**, R. Malik, M. Fabian , "A Framework for Compositional Synthesis of Modular Nonblocking Supervisors", *IEEE Transaction on Automatic Control, vol. 59, no. 1, pp 150-162, 2014.*

#### Paper 3

S. Mohajerani, R. Malik, M. Fabian, "Compositional Supervisor Synthesis with State Merging and Transition Removal", *Submitted to Automatica*, 2014.

#### **Other publications**

In addition to the appended papers, the following papers are also written by the author of the thesis:

- (a) S. Mohajerani, J. Sjöberg "On Initialization of Iterative Algorithms for Nonlinear ARX Models", *In proceeding of the 8th IFAC Symposium on Nonlinear Control Systems*, September 2010, pp. 362-367.

- (b) S. Mohajerani, R. Malik, S. Ware, M. Fabian, "Three variations of observation equivalence preserving synthesis abstraction", University of Waikato, Department of Computer Science, Hamilton, New Zealand, *Technical Report*, January, 2011.

- (c) S. Mohajerani, R. Malik, S. Ware, M. Fabian, "Compositional Synthesis of Discrete Event Systems Using Synthesis Abstraction", *In Proceeding of the* 23th Chinese Control and Decision Conference, May 2011, pp. 1549-1554.

- (d) S. Mohajerani, R. Malik, S. Ware, M. Fabian, "On the use of observation equivalence in synthesis abstraction", *In Proceeding of the 3rd International Workshop on Dependable Control of Discrete Systems (DCDS)*, June 2011, pp. 84-89.

- (e) S. Mohajerani, R. Malik, M. Fabian, "Nondeterminism avoidance in compositional synthesis of discrete event systems", In Proceeding of the 7th IEEE International Conference on Automation Science and Engineering, August 2011, pp. 19-24.

- (f) S. Mohajerani, R. Malik, S. Ware, M. Fabian, "Synthesis observation equivalence and weak synthesis observation equivalence", University of Waikato, Department of Computer Science, Hamilton, New Zealand, *Technical Report*, July, 2012.

- (g) **S. Mohajerani**, R. Malik, S. Ware, M. Fabian, "Five abstraction rules to remove transitions while preserving compositional synthesis results", University of Waikato, Department of Computer Science, Hamilton, New Zealand, *Technical Report*, July, 2012.

- (h) **S. Mohajerani**, R. Malik, M. Fabian, "Transition removal for compositional supervisor synthesis", *In Proceeding of the 8th IEEE International Conference on Automation Science and Engineering*, August 2012, pp. 694-699.

- (i) S. Mohajerani, R. Malik, M. Fabian, "An algorithm for weak synthesis observation equivalence for compositional supervisor synthesis", *In Proceeding of the 11th International Workshop on Discrete Event Systems*, October 2012, pp. 239-244.

- (j) S. Mohajerani, R. Malik, S. Ware, M. Fabian, "Partial unfolding for compositional nonblocking verification of extended finite-state machines", University of Waikato, Department of Computer Science, Hamilton, New Zealand, *Technical Report*, January, 2013.

- (k) S. Mohajerani, R. Malik, M. Fabian, "Compositional nonblocking verification for extended finite-state automata using partial unfolding, *In Proceeding* of the 9th IEEE International Conference on Automation Science and Engineering (CASE), August 2013, pp. 930-935.

- S. Ware, R. Malik, S. Mohajerani, M. Fabian, "Certainly Unsupervisable States", *In Proceeding 2nd International Workshop on Formal Techniques* for Safety-Critical Systems (FTSCS 2013), October 2013, pp. 3-18.

- (m) S. Mohajerani, R. Malik, M. Fabian, "An algorithm for compositional nonblocking verification of extended finite-state machines", *In Proceeding of the 12th International Workshop on Discrete Event Systems (WODES'14)*, October 2014, pp. 376-382.

# Contents

| Abstract             | i   |

|----------------------|-----|

| Acknowledgements     | iii |

| List of publications | v   |

| Contents             | ix  |

## I Introductory chapters

| 1                              | Introduction                  |                                      |    |  |  |  |

|--------------------------------|-------------------------------|--------------------------------------|----|--|--|--|

|                                | 1.1                           | Problem Statement                    | 2  |  |  |  |

|                                | 1.2                           | Main Contributions                   | 3  |  |  |  |

|                                | 1.3                           | Outline                              | 4  |  |  |  |

| 2                              | Prel                          | iminaries                            | 5  |  |  |  |

|                                | 2.1                           | Modelling Formalism                  | 5  |  |  |  |

|                                |                               | 2.1.1 Finite-State Machines          | 5  |  |  |  |

|                                |                               | 2.1.2 Extended Finite-State Machines | 7  |  |  |  |

|                                | 2.2                           | Interaction                          | 9  |  |  |  |

|                                | 2.3                           | Event-Based Marking                  | 11 |  |  |  |

|                                | 2.4                           | Equivalence Relations                | 12 |  |  |  |

| 3                              | Supervisory Control Theory 15 |                                      |    |  |  |  |

|                                | 3.1                           | Requirements for Supervisors         | 16 |  |  |  |

|                                |                               | 3.1.1 Nonblocking                    | 16 |  |  |  |

|                                |                               | 3.1.2 Controllability                | 17 |  |  |  |

|                                |                               | 3.1.3 Least Restrictiveness          | 18 |  |  |  |

| 3.2 Synthesis and Verification |                               | Synthesis and Verification           | 18 |  |  |  |

|                                | 3.3                           | -                                    | 20 |  |  |  |

|                                |                               |                                      |    |  |  |  |

#### CONTENTS

| 4  | The    | Compo                          | ositional Approach                                     | 23 |

|----|--------|--------------------------------|--------------------------------------------------------|----|

|    | 4.1    | Allevi                         | ating the State-Space Explosion Problem                | 23 |

|    | 4.2    | General Compositional Approach |                                                        | 24 |

|    |        | 4.2.1                          | Local Events and Hiding                                | 25 |

|    |        | 4.2.2                          | Abstraction Methods                                    | 27 |

|    |        | 4.2.3                          | Heuristics                                             | 27 |

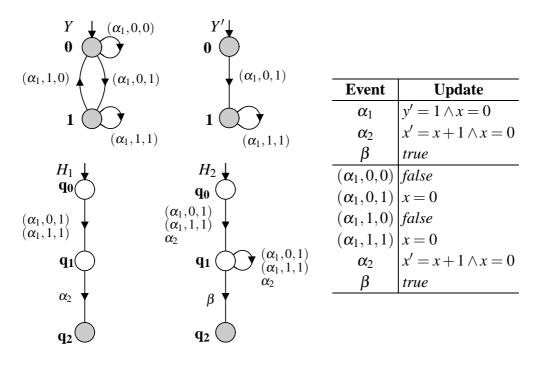

|    | 4.3    | Comp                           | ositional Verification of EFSM Systems                 | 28 |

|    |        | 4.3.1                          | Normalisation                                          | 29 |

|    |        | 4.3.2                          | Partial Unfolding                                      | 31 |

|    |        | 4.3.3                          | Adapting FSM Abstraction Methods for EFSMs             | 33 |

|    |        | 4.3.4                          | Experimental Results                                   | 34 |

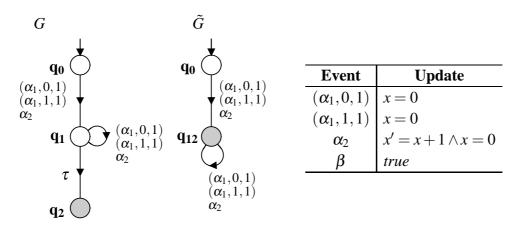

|    | 4.4    | Comp                           | ositional Synthesis                                    | 35 |

|    |        | 4.4.1                          | State Machine-Based Supervisor                         | 35 |

|    |        | 4.4.2                          | Map-Based Supervisor                                   | 38 |

|    |        | 4.4.3                          | Abstraction Methods Preserving Synthesis Equivalence . | 40 |

|    |        | 4.4.4                          | Experimental Results                                   | 42 |

| 5  | Sun    | ımary o                        | of Included Papers                                     | 43 |

| 6  | Con    | cluding                        | g Remarks                                              | 47 |

| 7  | Fut    | ure Wo                         | rk                                                     | 49 |

| Re | eferer | ices                           |                                                        | 51 |

## II Included papers

| Paper 1                                        | A Fra                                                     | amework for Compositional Nonblocking      |    |  |

|------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|----|--|

| Verification of Extended Finite-State Machines |                                                           |                                            |    |  |

| 1                                              | Introduction                                              |                                            |    |  |

| 2                                              | Preliminaries                                             |                                            |    |  |

|                                                | 2.1                                                       | Finite-State Machine                       | 63 |  |

|                                                | 2.2                                                       | Extended Finite-State Machine              | 64 |  |

| 3                                              | Motiva                                                    | ating Example                              | 67 |  |

| 4                                              | Normalisation 7   EFSM-Based Compositional Verification 7 |                                            |    |  |

| 5                                              |                                                           |                                            |    |  |

|                                                | 5.1                                                       | Update Simplification                      | 78 |  |

|                                                | 5.2                                                       | Partial Composition                        | 79 |  |

|                                                | 5.3                                                       | Variable Unfolding                         | 79 |  |

|                                                | 5.4                                                       | Event Simplification                       | 82 |  |

|                                                | 5.5                                                       | FSM-Based Conflict Equivalence Abstraction | 86 |  |

|                                                |                                                           |                                            |    |  |

#### CONTENTS

|     | 6                                       | Algorithm              |                                                       |     |  |

|-----|-----------------------------------------|------------------------|-------------------------------------------------------|-----|--|

|     | 7                                       | Experimental Results   |                                                       |     |  |

|     | 8                                       | Conclusions            |                                                       |     |  |

|     | А                                       | Proof of Normalisation |                                                       |     |  |

|     | B EFSM-Based Compositional Verification |                        |                                                       |     |  |

|     |                                         | <b>B</b> .1            | Proof of Update Simplification                        | 103 |  |

|     |                                         | B.2                    | Proof of Partial Composition                          | 104 |  |

|     |                                         | B.3                    | Proof of Variable Unfolding                           | 105 |  |

|     |                                         | B.4                    | Proof of Event Simplification                         | 109 |  |

|     |                                         | B.5                    | Proof of FSM-Based Conflict Equivalence Abstraction . | 117 |  |

|     | Refe                                    | rences .               |                                                       | 119 |  |

| _   | -                                       |                        |                                                       |     |  |

| Pa  | per 2                                   |                        | amework for Compositional Synthesis                   |     |  |

|     |                                         |                        | Nonblocking Supervisors                               | 125 |  |

|     | 1                                       |                        | uction                                                |     |  |

|     | 2                                       |                        | inaries                                               |     |  |

|     |                                         | 2.1                    | Events and Languages                                  | 127 |  |

|     |                                         | 2.2                    | Finite-State Automata                                 | 128 |  |

|     | _                                       | 2.3                    | Supervisory Control Theory                            | 129 |  |

|     | 3                                       |                        | ating example                                         | 131 |  |

|     | 4                                       |                        | ositional Synthesis                                   | 135 |  |

|     |                                         | 4.1                    | Basic Idea                                            | 136 |  |

|     |                                         | 4.2                    | Renaming                                              | 137 |  |

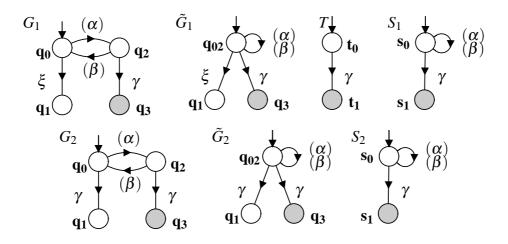

|     |                                         | 4.3                    | Synthesis Triples                                     |     |  |

|     | 5                                       | •                      | esis Triple Abstraction Operations                    | 141 |  |

|     |                                         | 5.1                    | Basic Rewrite Operations                              |     |  |

|     |                                         | 5.2                    | Halfway Synthesis                                     |     |  |

|     |                                         | 5.3                    | Renaming and Selfloop Removal                         |     |  |

|     |                                         | 5.4                    | Abstraction Based on Observation Equivalence          | 144 |  |

|     | 6                                       |                        | ositional Synthesis Algorithm                         |     |  |

|     | 7                                       | Experi                 | mental Results                                        | 151 |  |

|     | 8                                       | Conclu                 | isions                                                | 155 |  |

|     | Refe                                    | rences.                |                                                       | 155 |  |

| Pa  | per 3                                   | Com                    | positional Supervisor Synthesis                       |     |  |

| 1 a | -                                       | -                      | Aerging and Transition Removal                        | 163 |  |

|     | 1                                       |                        |                                                       | 163 |  |

|     | 2                                       |                        | inaries                                               | 165 |  |

|     | -                                       | 2.1                    | Events and Languages                                  | 165 |  |

|     |                                         | 2.1                    | Finite-State Automata                                 | 165 |  |

|     |                                         | 2.2                    | Supervisory Control Theory                            | 167 |  |

|     | 3                                       |                        | ositional Synthesis                                   | 169 |  |

|     | ~                                       | - Sumbe                |                                                       | 107 |  |

#### CONTENTS

| 4    | Abstraction Methods                                |   |  |  |  |

|------|----------------------------------------------------|---|--|--|--|

|      | 4.1 Hiding and State-Wise Synthesis Abstraction 17 | 1 |  |  |  |

|      | 4.2 Removal of Certainly Unsupervisable States     |   |  |  |  |

|      | 4.3 Abstraction by State Merging                   | 4 |  |  |  |

|      | 4.4 Synthesis Transition Removal                   | 5 |  |  |  |

| 5    | State Representation Architecture                  | 6 |  |  |  |

| 6    | Automata-based Supervisor                          | 9 |  |  |  |

| 7    | Experimental Results                               | 0 |  |  |  |

| 8    | Conclusions                                        | 5 |  |  |  |

| Refe | ences                                              | 5 |  |  |  |

# Part I

# **Introductory chapters**

## Chapter 1

## Introduction

The modern human being is a hybrid of a traditional homo-sapiens with fancy electronic gadgets. We use electronic devices everyday, and it seems we are never more than a meter away from our cellphones. These devices are designed to help us live our lives easier, and one of our most important requirement on them is consistency. We expect the devices to work in a certain way when we provide them with a certain input. In engineering terms, everything between the input that we provide and the output we see is broadly termed a *system*. A coffee machine, a printer and industrial robots are some examples of systems.

When dealing with different systems, many questions about the properties of the systems arise. For example, in the case of a mobile phone one may wonder: what will happen if I push a specific button? For a nuclear plant a question could be: what will happen if a nuclear reactor core becomes too hot? Experimentation is one way to answer these kind of questions. In many cases, experiments are very expensive or could even be dangerous. An alternative to answer such questions is to *model* the system behaviour.

Modelling is done from different perspectives. In some cases, using physical knowledge, mathematical equations that describe the output of a system given an input is derived. Newton's law, gravity laws and differential equations are some tools used in this context. In other cases, a system can be viewed as *event-driven*, for example, when a coffee machine goes out of coffee beans, the *event*, it goes from a working *state* to an idle state. The behaviour of such a system can then be described by sequences of events, where the occurrence of an event causes the system to go from one state to another. Such system models are referred to as *discrete event systems* and are the main focus of this thesis. In order to model a discrete event system, intuitive formalisms such as *finite-state machines* and *extended finite-state machines* can be used.

### **1.1 Problem Statement**

Imagine a coffee machine that fills your glass with tea even though you asked for coffee. In this case you may just accept the tea, get back to work and be in a bad mood all day. However, many applications of discrete event systems take place in settings that are safety critical and small failures may result in huge financial and/or human losses. Moreover, as discrete event systems are usually complex, their development is error-prone. Thus we need to verify that a system is error-free or if there are errors, remove them before using the system.

In this thesis *formal verification* is used to approve or disprove the correctness of a system. In formal verification, the first step is to identify a desired property. Then, a model of the system is built and finally it is shown mathematically whether the property of interest is fulfilled or not. Thus, the final result after verification is either "yes" or "no".

In the case that the verification result is not satisfactory, the next step is to design a control function to guarantee system correctness.

In 1989, *Ramadge* and *Wonham* [1] proposed a framework to calculate a controlling agent, called a *supervisor*, for discrete event systems. This framework is called the *supervisory control theory*. Given a model of a system to be controlled, the *plant*, and the desired behaviour, the *specification*, the supervisory control theory proposes methods to design a *supervisor* in such a way that the closed-loop system of plant and supervisor always acts according to the specification.

For simple systems consisting of a small number of states, verification or supervisor calculation can be done straightforwardly. However, this is not viable for complex systems consisting of several interacting subsystems. Such systems are referred to as *modular systems*. Using the straightforward approach to verify or calculate a supervisor for these systems, involves explicitly representing the entire system by a single model which may consist of millions of states. This inherent complexity problem is known as the *state-space explosion* problem. A brute force approach to verify and calculate a supervisor is to go through all states and verify the property of interest for each particular state and remove undesirable states. However, the state-space explosion makes it intractable to analyse all states of a system due to lack of memory and time.

The state-space explosion problem typically occurs when one tries to model a modular system by a single representation. However, it is possible to use the knowledge of modularity of the system to our advantage. One way to exploit the modularity of systems is to use a *compositional approach*. To avoid the state-space explosion problem, a compositional approach tries to build a single representation of a system in an iterative way. The general approach is as follows. First the subsystems are simplified in such a way that the property of interest is preserved. When no further simplification (also called *abstraction*) is possible, the subsystems are combined together one by one and simplified again in each iteration. This process is repeated until it results in one final relatively simple model. This simple model is finally used for verification or synthesis.

## **1.2 Main Contributions**

The main focus of this thesis is to use the compositional approach for verification and supervisor calculation. Questions that immediately arise are:

- What considerations need to be taken into account when the compositional approach is used for different modelling formalism?

- What considerations need to be taken into account when the compositional approach is used for verification and for synthesis?

- Is it possible to find methods in order to efficiently simplify subsystems?

- In the case that the compositional approach is used for supervisor calculation, does the supervisor have a modular structure and is it memory efficient?

Attempting to answer these questions results in the following contributions of this thesis:

- The compositional approach is well-developed for verification of systems modelled as finite-state machines [2]. This framework is extended to consider systems that are modelled as extended finite-state machines. It is shown how the abstraction methods defined for finite-state machines can be applied on extended finite-state machines (Paper 1).

- When using the compositional approach for supervisor calculation or verification, the property of interest is different and thus needs to be defined first before using the compositional approach. *Conflict equivalence* [2] is used as the property to be preserved when the task is to verify whether the system is able to finish some sub-tasks and it is used in Paper 1. When it comes to supervisor calculation, the closed-loop behaviour is the property to be preserved after simplification. For this purpose *synthesis equivalence* is introduced in this thesis (Paper 2 and 3).

- The main focus of this thesis is to develop abstraction methods in the compositional approach such that the property of interest is preserved. It is shown how any abstraction method defined for finite-state machines can

be applied on extended-finite state machines (Paper 1). Different abstraction methods for compositional synthesis are presented, which are mostly based on a well known abstraction method called *observation equivalence*. It is shown how observation equivalence can be strengthened to be applicable in the compositional synthesis framework (Paper 2 and 3).

• The algorithms proposed in this work have been implemented in the discrete event system software tool Supremica and have been applied to compute supervisors for several benchmark examples. The experimental results show that the method efficiently computes modular supervisor for a set of very large industrial models (Paper 2 and 3). The supervisor can also be represented in a compact form and can be stored efficiently (Paper 3).

## 1.3 Outline

The first two chapters, Chapter 2 and Chapter 3, give the preliminaries and background of the supervisory control theory. In Chapter 4, the compositional verification and synthesis proposed in this work is described. The summary of appended paper is provided in Chapter 5. Finally some concluding remarks and future work are given in chapters 6 and 7.

# Chapter 2 Preliminaries

The behaviour of many technical devices and systems in common use can be described by sequences of events, for example a robot arm picking up a workpiece. This includes automated manufacturing systems, traffic control systems, etc. The behaviour of these systems can be modelled as *discrete event systems* (DES). A DES is a dynamic system with events and states as its basic elements. Events represent incidents that cause transitions from one state to another, and states describe the current system status after the occurrence of an event.

### 2.1 Modelling Formalism

A prerequisite to formally analyse discrete event systems is developing suitable models that can accurately represent the activities of the system. Different modelling formalisms have been used in the literature, for instance, state machines [3], Petri nets [4], process algebra [5] and formal languages [1,6].

In this thesis, *finite-state machines* are used to represent the behaviour of discrete event systems as these are intuitive and have structure that allows useful manipulations. For example, abstraction may cause nondeterministic behaviour, and state machines describe nondeterministic behaviour straightforwardly.

#### 2.1.1 Finite-State Machines

Finite-state machines (FSM), referred to as *finite-state automata* in Paper 2 and 3, are devices that represent the behaviour of discrete event systems. An FSM can be considered as a directed graph. A state represents the current status of a system under which certain conditions hold, such as the position of a robot arm. The state set of a system contains all possible situations that the system may encounter. Events represent incidents that cause transitions from one state to another. For a discrete event system, a finite alphabet  $\Sigma$  is defined, the elements

CHAPTER 2. PRELIMINARIES

of which are all the possible events in the system. A sequence of events forms a *string*, and  $\Sigma^*$  is the set of all finite strings of events from  $\Sigma$ . Transitions of FSMs are written as  $x \xrightarrow{\sigma} y$ , where x is the *source state*, and y is the *target state* reached after the occurrence of the event  $\sigma$ . Two more ingredients are necessary to define an FSM: *initial states* and *marked states*. The system starts in one of the initial states. Marked states are desired states with a special meaning attached to them like completion of a task. In the figures, initial states are identified by an arrow pointing into them, and the marked states are shaded grey.

Usually, systems have a unique initial state, and each occurrence of an event in a given state *x* causes a transition to only one state *y*, and all the transitions are labelled by events from the alphabet of the system. Under these conditions, the system is said to be *deterministic*, as the state of the system can be uniquely determined from the sequence of events that have occurred. However the main focus of this thesis is abstraction, which may cause nondeterminism. Moreover, events that represent *internal* behaviour of a component in a system are removed from the alphabet and the transitions labelled by those events are labelled by the *silent event*  $\tau$ . This event is not part of the alphabet of the system, but its use is explicitly mentioned by the notation  $\Sigma_{\tau} = \Sigma \cup {\tau}$ . The act of transforming an event into the silent event is referred to as *hiding* [7] and introduces nondeterminism. The formal definition of hiding can be found in Def. 3 of Paper 3.

Now we can state a formal definition for a finite-state machine.

**Definition 1** A finite-state machine (FSM) is a tuple  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ , where

- $\Sigma$  *is the* alphabet, *a finite set of events*,

- *Q* is the finite set of states,

- $\rightarrow \subseteq Q \times \Sigma_{\tau} \times Q$  is the state transition relation,

- $Q^{\circ} \subseteq Q$  is the set of initial states,

- $Q^{\omega} \subseteq Q$  is the set of marked states.

An FSM *G* is *deterministic* if  $|Q^{\circ}| \leq 1$ , meaning it has at most one initial state,  $x \stackrel{\sigma}{\rightarrow} y_1$  and  $x \stackrel{\sigma}{\rightarrow} y_2$  always implies  $y_1 = y_2$ , meaning that occurrence of an event in a source state leads the system to a unique target state, and  $x \stackrel{\sigma}{\rightarrow} y$  implies  $\sigma \neq \tau$ , meaning transitions are only labelled by events from the alphabet. In this thesis,  $Q^{\circ} \stackrel{\sigma}{\rightarrow} y$  means there exists  $x^{\circ} \in Q^{\circ}$  such that  $x^{\circ} \stackrel{\sigma}{\rightarrow} y$  and  $x \rightarrow y$  means there exists  $\sigma \in \Sigma$  such that  $x \stackrel{\sigma}{\rightarrow} y$ . Moreover,  $x \stackrel{s}{\rightarrow}$  means that  $x \stackrel{s}{\rightarrow} y$  for some  $y \in Q$ .

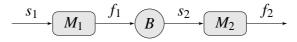

Figure 2.1: Manufacturing system overview.

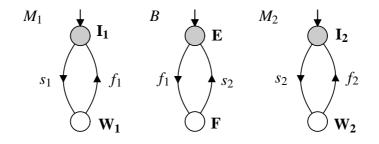

Figure 2.2: FSM models of manufacturing system.

Normally a system is modelled as a set of FSMs where each FSM represents the behaviour of an individual component of the system. This makes the modelling task easier as it is more intuitive to describe each component behaviour rather than the entire system at once.

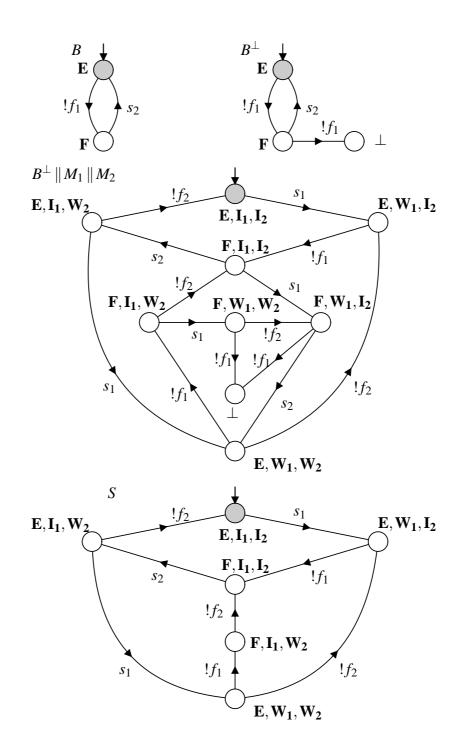

**Example 1** Consider the simple manufacturing system shown in Fig. 2.1. The system consists of two machines  $M_1$  and  $M_2$ , which are linked by a buffer B that can store one workpiece. The first machine  $M_1$  takes workpieces from outside the system (event  $s_1$ ), processes them, and puts them into B (event  $f_1$ ). Machine  $M_2$  takes workpieces from B (event  $s_2$ ), processes them and outputs them from the system (event  $f_2$ ). Fig. 2.2 shows FSMs modelling the system.

#### 2.1.2 Extended Finite-State Machines

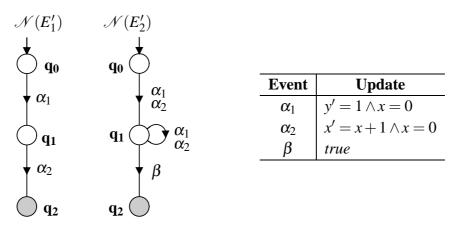

Finite-state machines describe the behaviour of a system using states and events. For systems with data dependency, it is natural to extend finite-state machines with variables and updates. This results in *extended finite-state machines (EFSM)*, also referred to as *extended finite-state automata* [8].

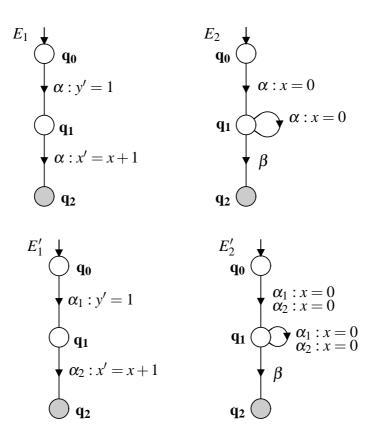

EFSMs are similar to conventional finite-state machines, but the transitions are not only labelled by events, but also by *updates* [8–12]. Updates are predicates and can be evaluated to **T** or **F**. They are constructed from variables, integer constants, the Boolean literals *true* and *false*, and the usual arithmetic and logic connectives. Similar to FSMs, a system changes its state on the occurrence of an event, but the transition in an EFSM is enabled only if the corresponding update evaluates to **T**. The transitions of an EFSM are represented as  $x \xrightarrow{\sigma:p} y$ , where x is the *source location*, and y is the *target location* after the occurrence of the event  $\sigma$ , and p represents the update associated to the transition. Once a transition occurs, the system moves from the source location to the target location, and the variables in the update of the transition may change their value, while the rest of the variables remain unchanged. Thus, the states of an EFSM are combinations of locations of the EFSM and the variable values.

As mentioned, updates are constructed from variables. Each variable has a discrete domain, dom(v), that represents the possible values of the variable. For example, if a buffer with capacity 3 is represented as a variable b in the system then the domain of b is  $\{0, 1, 2, 3\}$ , where each value represents the number of workpieces in the buffer. A variable also has an initial value,  $v^{\circ} \in \text{dom}(v)$ . For example, if the buffer is initially empty then  $b^{\circ} = 0$ . As mentioned, when a transition occurs, the values of the variables in the corresponding update may change while the variables not in the update remain unchanged. To distinguish the changing variables, a second set of variables called *next-state variables*, denoted by V', is used, which have the same domain as the variables in V. For example, again assume we have a buffer with capacity 3 represented by the variable b, a transition with update b' = b + 1 adds a workpiece to the buffer, if the number of workpieces in the buffer is currently less than 3. Otherwise, if b = 3, then the buffer is full and the transition is disabled since no more workpieces can be added. In the model this is detected since the value of b' would become equal to 4, which is outside of the domain of b. An update like b = 3 simply checks if the number of workpieces in the buffer is 3 and enables the transition only if this is true. In this case the value of b in the target location remains unchanged as no workpiece is added to the buffer. Differently, an update like b' = 3 always enables its transition, and the value of b in the target location is forced to be 3.

In the figures of this thesis, for simplicity updates only constructed from *true* are not shown on transitions of EFSMs.

**Definition 2** An extended finite-state machine (EFSM) is a tuple  $E = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ , where  $\Sigma$  is a set of events, Q is a finite set of locations,  $\rightarrow \subseteq Q \times \Sigma \times \Pi_V \times Q$  is the conditional transition relation and  $p \in \Pi_V$ , where  $\Pi_V$  contains all possible updates over the variable set  $V, Q^{\circ} \subseteq Q$  is the set of initial locations, and  $Q^{\omega} \subseteq Q$  is the set of marked locations.

In this thesis, the term *state machine* is used to refer to both finite-state machine and extended finite-state machine.

EFSMs usually simplify the modelling task. However, to analyse EFSM systems the straightforward way would be to convert the EFSM to an FSM by evaluating all the updates to find the variable values in each location of the EFSM. The states of the resultant FSM are then combinations of the locations of the EFSM and the variable values. This is referred to as *unfolding* variables. The complete process of transforming an EFSM to FSM is called *flattening*, and the

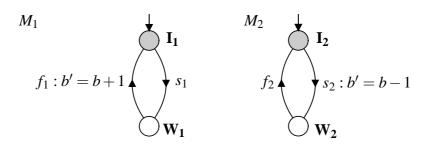

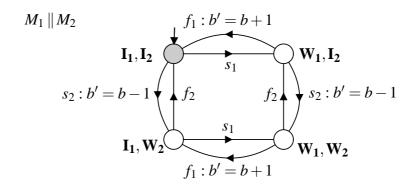

Figure 2.3: EFSM models of the manufacturing system.

resultant FSM is referred to as the *flattened FSM*. At the beginning of the flattening process, the value of each variable is equal to its initial value. Thus, the initial locations  $x^{\circ}$  are combined with the initial values of the variables, denoted as  $\hat{v}^{\circ}$ , to create the initial states of the form  $(x^{\circ}, \hat{v}^{\circ})$ . Next, based on the updates of the transitions going out of the initial locations, the values of some of the variables change at the next locations, and so on. Thus, for each transition  $x \xrightarrow{\sigma:p} y$ in the EFSM model there exist transitions  $(x, \hat{v}) \xrightarrow{\sigma} (y, \hat{w})$  in the flattened FSM model whenever p evaluates to **T** for the values  $\hat{v}$  and  $\hat{w}$ . The formal definition of flattening can be found in Def. 10 of Paper 1.

**Example 2** Consider again the manufacturing system shown in Fig. 2.1. The EFSM model of the system consists of  $M_1$  and  $M_2$  as shown in Fig. 2.3. It uses a variable b with domain  $\{0,1\}$  to represent the number of workpieces in the buffer. The update b' = b + 1 represents an addition of a workpiece to the buffer when the event  $f_1$  is executed. As the domain of b is  $\{0,1\}$ , event  $f_1$  can only be executed if the current value of b is zero, or in other words when there is no workpiece in the buffer. If the buffer is full, then b = 1 and b' = 1 + 1 = 2, which cannot happen as 2 is not in the domain of b. Thus, if the buffer is full,  $M_1$  cannot add another workpiece to the buffer.

#### 2.2 Interaction

As mentioned before, discrete event systems are usually *modular*, in that they are modelled as a set of interacting subsystems. The reason is that typically systems are complex and modelling them by only one state machine is impractical. However, it is possible to combine the state machine components of a system into a single state machine. This process is referred to as *synchronous composition* [13].

When a system is modelled as a set of interacting state machines, a transition in the synchronous composition occurs only if it is possible in all the components *sharing* the event labelling the transition, otherwise the transition is disabled. Af-

Figure 2.4: Synchronous composition of FSM model of the manufacturing system.

ter an occurrence of a shared event, the states (locations) of all the state machines with that event in their alphabet are updated concurrently. If an event only appears in one component then this event is called a *local event* and it is always executed independently. Transitions of EFSMs are in addition to events also labelled by updates. Thus, updates need to be considered during synchronisation. The updates of the shared events are combined by *conjunction* while the updates of local events remain unchanged. Using these principles it is possible to build a single state machine that represents the behaviour of a set of interacting state machines. The formal definition of synchronisation of FSMs is given in Def. 2 in Paper 2 and 3, and of EFSMs in Def. 9 of Paper 1.

After the synchronisation of  $G_1$  and  $G_2$ , in the worst case the number of the states (locations) of the synchronisation result of  $G_1$  and  $G_2$  is  $|Q_1| \times |Q_2|$ . Thus, the state-space of systems consisting of many interacting components may easily become unmanageable. This problem is commonly referred to as the *state-space explosion* problem.

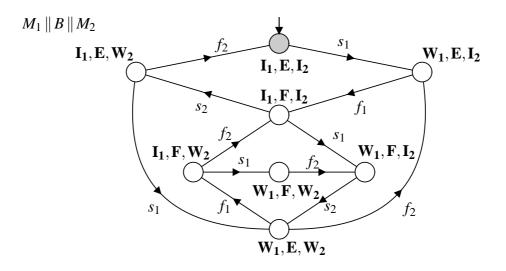

**Example 3** Fig. 2.2 shows the model of the small manufacturing system of Example 1. Initially the machines and the buffer are in their respective I and E states. Thus, the initial state of the synchronous composition is  $(I_1, E, I_2)$ . In this state, only the local event  $s_1$  is possible. Note that  $f_2$  and  $s_2$  are enabled in states E and  $I_2$  respectively. However, they are not enabled in  $(I_1, E, I_2)$  as they are restricted by the other components. After the occurrence of event  $s_1$ , the first machine moves to the  $W_1$  state and the buffer and the second machine remain in their respective E and  $I_2$  states. The entire synchronous composition is shown in Fig. 2.4. Fig. 2.5 shows the synchronous composition of the EFSM model. The updates in the synchronisation result are the same as in  $M_1$  and  $M_2$  because

Figure 2.5: Synchronous composition of the EFSM model of the manufacturing system.

these two EFSMs do not share any events. Flattening the synchronised EFSM  $M_1 \parallel M_2$  results in an FSM isomorphic to FSM  $M_1 \parallel B \parallel M_2$  shown in Fig. 2.4.

## 2.3 Event-Based Marking

Marking is used to represent states of a system that have a special meaning attached to them, like completion of a task. The standard way to represent the marking in a system is by labelling some states (locations) as *marked* [1, 6]. This thesis is mainly focused on equivalence relations to abstract state machines. For this purpose, in Paper 2 and 3 marking of states of FSMs is transformed to an event-based representation, otherwise marking needs special consideration in most of the definitions in these papers. For this, a *termination event*  $\omega$  is introduced. This event, similarly to the silent event, is not included in the alphabet of the system, but its use is explicitly mentioned by the notation  $\Sigma_{\omega} = \Sigma \cup {\omega}$ .

Consider an FSM with  $Q^{\omega}$  as the set of marked states and the alphabet  $\Sigma$ . To transform this to event-based marking, the first step is to add to the set of states a termination state  $\bot \in Q \setminus Q^{\omega}$ . This state has no outgoing transitions and is not originally in Q. After adding the termination state, the transition relation is extended to  $\to \subseteq Q \times \Sigma_{\omega} \times Q$  by adding transitions

$$q^{\omega} \xrightarrow{\omega} \perp$$

for each  $q^{\omega} \in Q^{\omega}$  (2.1)

In synchronous composition,  $\omega$  is considered as an ordinary event. Thus, for a composed state  $(x_1, x_2)$ , it holds that  $(x_1, x_2) \xrightarrow{\omega} \bot$  only if  $x_1 \xrightarrow{\omega} \bot$  and  $x_2 \xrightarrow{\omega} \bot$ . For simplicity in the figures, marked states are shown instead of the  $\omega$  and  $\bot$ .

## 2.4 Equivalence Relations

One way to alleviate the state-space explosion problem is to *abstract* the components of the system by merging some states or removing some transitions. To merge states it is important that the states are equivalent based on some criteria that preserves the property of interest. An *equivalence relation* is a binary relation that partitions a set into disjoint subsets. Thus, an equivalence relation can be used to partition a state set *Q* into the set of its *equivalence classes*. States that belong to the same equivalence class can be merged and consequently an FSM with less states can be obtained, which is referred to as the *quotient FSM*. The quotient FSM is an abstracted FSM. After merging states, the new state has the union of incoming and outgoing transitions of the merged states. The formal definition of quotient state machine is given in Paper 2 and 3 in Defs. 4 and 5, respectively.

Note that, in Paper 1, an EFSM is first transformed to an FSM before applying state merging abstraction. Thus, in the following the definitions are given for FSMs.

Two fundamental equivalence relations that play an important role in this thesis are *bisimulation equivalence* and *observation equivalence*.

Bisimulation requires two equivalent states to have the same future behaviour. Thus, the formal definition of bisimulation [14] is based on relation on states.

**Definition 3** [14] Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an FSM. An equivalence relation  $\approx \subseteq Q \times Q$  is called a bisimulation on G, if the following holds for all  $x_1, x_2 \in Q$  such that  $x_1 \approx x_2$ : if  $x_1 \stackrel{\sigma}{\rightarrow} y_1$  for some  $\sigma \in (\Sigma_{\omega} \cup \Sigma_{\tau})$ , then there exists  $y_2 \in Q$  such that  $x_2 \stackrel{\sigma}{\rightarrow} y_2$  and  $y_1 \approx y_2$ .

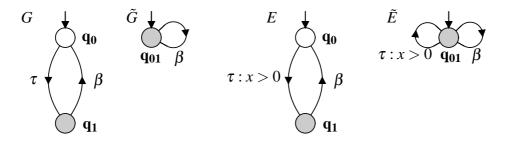

Bisimulation considers states to be equivalent if they have the outgoing transitions with the same events including the silent and marking events to equivalent states. Bisimulation can be computed by an efficient partition refinement algorithm [15]. This algorithm represents an equivalence relation as a partition, i.e., a set of equivalence classes each representing a set of equivalent states. The algorithm starts with an initial partition consisting of only one equivalence class contains all the states of an FSM, which is iteratively refined until a stable partitioning is reached. At each step, those states in equivalence classes that do not transit to the same equivalence classes on the same event are separated into other equivalence classes. This efficient algorithm gives the *minimal* FSM  $\tilde{G}$ , which is bisimilar to the original FSM G.

It is possible to relax bisimulation by ignoring the silent events. Then we can consider two states equivalent if from both of them equivalent states can be reached by the same sequences of events aside from silent events. This results in *weak bisimulation*, also known as *observation equivalence*. In order to ignore

the silent events, *natural projection*  $P: \Sigma^*_{\tau} \to \Sigma^*$  is used which removes silent events  $\tau$  from every string *s*.

**Definition 4** [14] Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  be an FSM. An equivalence relation  $\sim \subseteq Q \times Q$  is called an observation equivalence on G, if the following holds for all  $x_1, x_2 \in Q$  such that  $x_1 \sim x_2$ : if  $x_1 \xrightarrow{s_1} y_1$  for some  $s_1 \in (\Sigma_{\omega} \cup \Sigma_{\tau})^*$ , then there exists  $y_2 \in Q$  and  $s_2 \in (\Sigma_{\omega} \cup \Sigma_{\tau})^*$  such that  $P(s_1) = P(s_2)$ ,  $x_2 \xrightarrow{s_2} y_2$ , and  $y_1 \sim y_2$ .

For observation equivalence a generalised version of the bisimulation algorithm [15] can be used. The only difference is that a split is performed on each known equivalence class *C*, separating states *x* with  $x \xrightarrow{\tau^*P(\sigma)\tau^*} C$ , for all  $\sigma \in (\Sigma_{\omega} \cup \Sigma_{\tau})$ , from other states, i.e, the *transitive closure* of the silent transitions needs to be considered. Similar to bisimulation the algorithm gives the minimal FSM.

Besides state merging abstraction, an FSM can be abstracted by removing redundant transitions. More precisely, a transition  $x \xrightarrow{\sigma} y$  is *observation equivalence redundant* and can be removed [16] if the FSM *G* contains a *matching path*. A matching path starts from *x* and ends up in the state *y* by a string consisting of  $\sigma$  and sequences of silent events before or after  $\sigma$ . The matching path must not contain the transition itself. After removal of the redundant transitions from *G* the abstract FSM *H* is obtained. The following definition describes how *G* and *H* are related.

**Definition 5** Let  $G = \langle \Sigma, Q, \rightarrow_G, Q^{\circ} \rangle$  be an FSM. FSM  $H = \langle \Sigma, Q, \rightarrow_H, Q^{\circ} \rangle$  with  $\rightarrow_H \subseteq \rightarrow_G$  is a result of observation equivalence redundant transition removal from *G*, if for all transitions  $x \xrightarrow{\sigma}_G y$  there exist  $x \xrightarrow{\tau^* P(\sigma)\tau^*}_H y$ .

Bisimulation and observation equivalence are well-known general abstraction methods to merge states. In Chapter 4, bisimulation and a restricted version of observation equivalence are used to abstract FSMs.

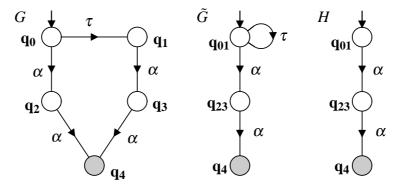

Figure 2.6: Example of observation equivalence based abstractions.

CHAPTER 2. PRELIMINARIES

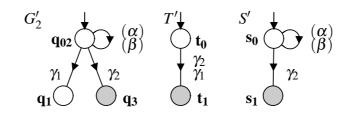

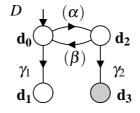

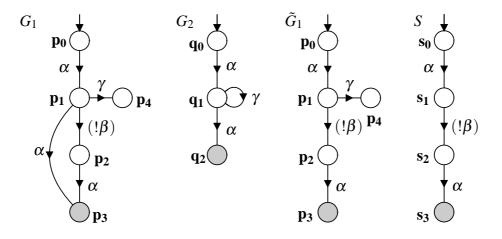

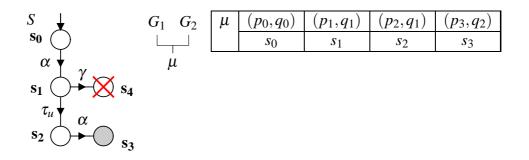

**Example 4** Consider the FSM G shown in Fig. 2.6. States  $q_2$  and  $q_3$  are bisimilar as state  $q_4$  can be reached from both of them by executing event  $\alpha$ . Moreover, states  $q_0$  and  $q_1$  can be merged by applying observation equivalence. These two state merging abstraction steps result in the abstracted FSM  $\tilde{G}$  shown in Fig. 2.6. Next, transition  $q_{01} \stackrel{\tau}{\rightarrow} q_{01}$  is redundant because of  $q_{01} \stackrel{\varepsilon}{\rightarrow} q_{01}$ , where  $\varepsilon$  is the empty string, and can be removed, resulting in the abstracted FSM H in Fig. 2.6.

# Chapter 3 Supervisory Control Theory

A discrete event system usually consists of a set of *plants* and *specifications* modelled as interacting state machines. Plants can be seen as event generators and describe the behaviour of the *uncontrolled* system. Usually, the system behaviour is not acceptable in that it violates some specified requirements, for example, a machine trying to add a workpiece in a buffer that is currently full. Thus, commonly for a system a set of specifications is defined that describe the desired behaviour of the system. Now the task is to first *verify* whether the system satisfies the given specification, and, if not, restrict the system behaviour such that the given specification is fulfilled.

The supervisory control theory [1] provides a mathematical framework to automatically calculate, or synthesise, a control function called a supervisor that restricts the behaviour of the plant such that the specification is always fulfilled. In this thesis, plants, specifications, and supervisors are usually denoted by G, K, and S, respectively.

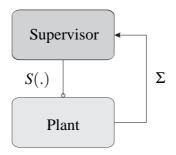

Fig. 3.1, shows the feedback loop of supervisor and plant. The plant generates events in  $\Sigma$  and the supervisor as a function S(.), based on the earlier generated events, influences the plant behaviour, and thus the closed-loop system, by deciding whether or not to enable the possible events. Thus, the supervisor itself is incapable of generating events and only enables or disables them. In [17],

Figure 3.1: The feedback loop of supervisor and plant.

it was shown that when the plant and supervisor are modelled as FSMs, synchronous composition of the plant and supervisor can describe the behaviour of the plant under the control of the supervisor. This results in a simplified notion of controlled behaviour.

Supervisory control theory is generalised for nondeterministic models in [18–20] among others. In [18, 19], even though the plant may be nondeterministic, the specification must be deterministic. This condition is relaxed in [20], where both the plant and specification can be nondeterministic, with the objective that the controlled system be bisimulation equivalent to the specification. This thesis considers systems where both plants and specifications are modelled by deterministic finite-state machines, and the nondeterminism considered in this thesis is the result of abstraction.

## **3.1 Requirements for Supervisors**

A plant describes everything that the uncontrolled system is capable of doing and the specification expresses the desired behaviour. Then a supervisor is a device that restricts the plant behaviour such that the plant in the closed-loop with the supervisor acts as desired. Besides this essential requirement, there are three more requirements that a supervisor should have.

#### 3.1.1 Nonblocking

The supervisor is designed to fulfil a given specification. However, this is not per se useful if the supervisor restricts the plant from doing what it is supposed to do, for example, if the plant under the control of a supervisor gets stuck in a state or a loop from which no tasks can be completed. To avoid these kinds of situations, as mentioned in Chapter 2, some states of particular interest in the plant and the specification can be marked. Then the idea is to design a supervisor such that the closed-loop system can always reach a state that is marked by both the plant and the specification. Such a supervisor is referred to as a *nonblocking* supervisor [1].

**Definition 6** Let  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ . A state  $x \in Q$  is called reachable in G if  $Q^{\circ} \xrightarrow{s} x$  for some  $s \in \Sigma_{\tau}^{*}$ , and coreachable if  $x \xrightarrow{t} Q^{\omega}$  for some  $t \in \Sigma_{\tau}^{*}$ . G is said to be nonblocking if every reachable state is coreachable.

An FSM is nonblocking if from all the reachable states a marked state can be reached by executing a sequence of events. Given a plant *G* and a supervisor *S* the resultant closed-loop behaviour is G/S (reading as *S* controlling *G*), and the closed-loop system should be nonblocking. The nonblocking definition can be

easily extended to an EFSM. An EFSM is nonblocking if the resultant flattened FSM is nonblocking. The formal definition of nonblocking for EFSM is given in Paper 1 in Def. 11. As mentioned in Section 2.3 in this thesis, the special event  $\omega$  is used to represent the marking of states. Then, the nonblocking definition should also be adapted to event-based marking.

**Definition 7** [21] An FSM  $G = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$  is nonblocking, if for every state  $x \in Q$  and every trace  $s \in \Sigma^*_{\tau}$  such that  $Q^{\circ} \xrightarrow{s} x$  there exists  $t \in \Sigma^*_{\tau}$  such that  $x \xrightarrow{t\omega}$ .

Similarly to Def. 6, Def. 7 says that if a state is reachable from an initial state by a sequence of events from  $\Sigma_{\tau}$ , then there must be from that state a sequence of events that ends with  $\omega$ . In Def. 7, the condition that *s* and *t* are constructed from the set  $\Sigma_{\tau}$  and thus do not contain  $\omega$  is important. For example, if  $s \in \Sigma_{\tau,\omega}^*$  then the state  $\bot$  that is used to represent the marking of a state becomes reachable. As no  $\omega$  transition is coming out of  $\bot$ , the FSM may falsely seem blocking.

#### **3.1.2** Controllability

A supervisor is a device that restricts the plant behaviour by disabling some events. It is reasonable to assume that some events cannot be disabled by the supervisor, for example, the breaking of a device. Thus, for the purpose of supervisory control, the alphabet of a system is partitioned into two disjoint subsets, the set  $\Sigma_c$  of *controllable* events and the set  $\Sigma_u$  of *uncontrollable* events. Controllable events can be disabled by a supervisor, but uncontrollable events cannot. Now the question arises whether the silent event  $\tau$  and the termination event  $\omega$  are controllable or uncontrollable. The termination event is considered as a controllable event because the supervisor should be able to disable  $\omega$  in order to remove some markings. Moreover, in this thesis having a silent event in the model of a system is the result of hiding a local event. Thus, in the case that the controllability of events is relevant, the silent event will have the same controllability characteristic as the local event that it replaces. In that, the notation of  $\tau_u$  and  $\tau_c$ is used for the uncontrollable and the controllable silent events, respectively. In the case that the controllability of the events are not relevant, the silent event  $\tau$  is used, for example in Paper 1, where only nonblocking verification is considered.

To distinguish controllable events and uncontrollable events in the figures, uncontrollable events are prefixed by an exclamation mark (!).

Considering uncontrollable events, one requirement for the computed supervisor is that it never tries to disable an executable uncontrollable event in order to restrict the system. In other words, a supervisor is controllable with respect to a plant if the occurrence of an uncontrollable event does not lead to a string which is not acceptable by the supervisor [1]. The formal definition of controllability for deterministic FSMs is given in Paper 2 in Def. 5, and for nondeterministic FSMs in Paper 3, Def. 7.

#### 3.1.3 Least Restrictiveness

The purpose of a supervisor is to restrict a plant behaviour to fulfil a given specification. It is typically required of a supervisor to achieve some minimum functionality. To ensure this minimum functionality, in this thesis the *least restrictive* supervisor, which restricts the system as little as possible is considered. Least restrictiveness may not always be required, and it can in fact ease the synthesis work. However, if a non-least restrictive algorithm synthesizes an overly restrictive supervisor, such as one giving an empty closed-loop system, it is not clear if this is due to a problematic plant/specification combination, or just an ill-chosen synthesis result. With an algorithm that guarantees a least restrictive supervisor, on the other hand, an overly restrictive supervisor will be the best achievable result and hence definitely a consequence of a problematic plant/specification combination. And of course, if you are going to do something why not try to do it optimally!

In this thesis, one goal is to calculate a least restrictive, controllable, and nonblocking supervisor and such a supervisor always exists and is unique with respect to a given plant and specification [1].

## 3.2 Synthesis and Verification

When we are dealing with safety critical systems such as medical devices or systems where errors are expensive such as factories, it is important to know if the systems works as expected in all possible situations. *Formal verification* is used to prove that a system satisfies a given specification. Two important properties that are typically verified are *nonblocking* and *controllability*. Nonblocking verification proves that a system can always complete a certain significant sub-task without violating the specification, and controllability verification proves that the system does not uncontrollably violate the specification.

In this thesis only, nonblocking verification of systems modelled as a set of EFSMs are considered. Nonblocking and controllability verification of FSM models are well-developed in the literature [1, 6, 7]. It was shown in [22] that controllability problems can be converted into nonblocking problems, making it possible to verify both nonblocking and controllability by running the nonblocking verification algorithm only once.

The straightforward approach to verify the nonblocking property is to compose all the components of the system. In the case that the system is modelled as a set of EFSMs, the next step is to flatten the composed EFSM. The final step is to check if the resultant FSM is nonblocking by inspecting if it is possible to reach a marked state from all the reachable states.

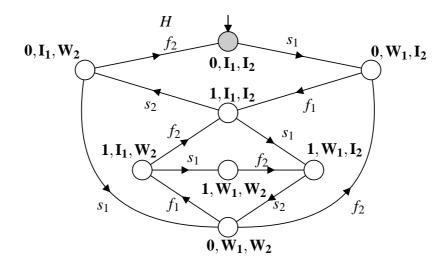

**Example 5** Consider the manufacturing system in Example 1. The EFSM model of the system is shown in Fig. 2.3 and the synchronous composition result is shown in Fig. 2.5. To use the straightforward approach to verify the nonblocking property of the system, the system needs to be flattened first. Fig. 3.2 shows the flattened FSM H. Initially the buffer is empty, which means b = 0, and  $M_1$  and  $M_2$  are in initial locations  $I_1$  and  $I_2$ . Thus, the initial state of H is  $(0,I_1,I_2)$ . At this state the event  $s_1$  can occur. After occurrence of this event, the buffer is still empty and  $M_2$  is still in the location  $I_2$ .  $M_1$  however, moves to location  $W_1$ . Thus the next state of the system is  $(0,W_1,I_2)$  and so on. The flattened FSM H is isomorphic to FSM  $M_1 || B || M_2$  shown in Fig. 2.4. This confirms that both the FSM and EFSM models describe the same behaviour. FSM H is nonblocking as from all the states, the marked state  $(0,I_1,I_2)$  can be reached. Thus, the original EFSM system is nonblocking.

Figure 3.2: The flattened FSM of the EFSM model of the manufacturing system.

After verification, if the result is satisfactory then the task is done and there is no need to design a supervisor as the specification can be used as a supervisor. Otherwise, a supervisor needs to be designed to prevent the system to go to the bad states. To this end, supervisory control theory [1, 6], which automatically *synthesises* such a supervisor is proposed.

The synthesis algorithm in this thesis first transforms all the specifications to plants [22]. A specification FSM is transformed into a plant by adding, for every uncontrollable event that is not enabled in a state, a transition to a new blocking

state  $\perp$ . The formal definition of *plantification* is given in Paper 2, Def. 8. Plantification essentially transforms all initial controllability problems into blocking problems. Then, the plant *G* and the transformed specification  $K^{\perp}$  are synchronised and the synthesis algorithm iteratively identifies and removes blocking states, and the states that uncontrollably go to blocking states. The algorithm in the end returns the least restrictive nonblocking and controllable behaviour allowed by a specification *K* with respect to a plant *G*.

**Example 6** Consider the manufacturing system in Example 1. The events  $!f_1$ and  $!_{f_2}$  are uncontrollable and  $s_1$  and  $s_2$  are controllable. The safety issue in this system is that machine  $M_1$  should not try to put a workpiece in the buffer B if the buffer is currently full, and  $M_2$  should not try to remove a workpiece if the buffer is empty. Therefore, FSM B is considered as the specification to avoid buffer overflow and underflow and the machines are considered as the plants. This specification is uncontrollable as it disables the uncontrollable event  $!f_1$  in the states  $(F, W_1, W_2)$  and  $(F, W_1, I_2)$  to avoid adding a workpiece in a currently full buffer. Thus, the plant violates the specification uncontrollably and a supervisor needs to be designed. The first step to design a supervisor is to plantify the specification. Fig. 3.3 shows the FSM  $B^{\perp}$ , which is the result of plantification. Next,  $B^{\perp}$  is composed with  $M_1$  and  $M_2$ . The state  $\perp$  in the composed FSM  $B^{\perp} \parallel M_1 \parallel M_2$  represents the initial controllability problem, and it is a blocking state as can be seen in Fig. 3.3. The plant needs to be restricted to avoid ending up in the blocking state  $\perp$ . This state however, is reached from  $(F, W_1, W_2)$  and  $(F, W_1, I_2)$  by the uncontrollable event  $!f_1$ , which the supervisor cannot disable. Thus, the best control decision is to disable event  $s_1$  in the states  $(F, I_1, W_2)$  and  $(F, I_1, I_2)$  and thus avoid starting machine  $M_1$  when the buffer is full. The least restrictive, nonblocking and controllable supervisor S is shown in Fig. 3.3.

In the finite-state case, the iteration to remove all problematic states is guaranteed to terminate, and the complexity is  $O(|Q|| \rightarrow |)$ , where |Q| and  $|\rightarrow|$  are the numbers of states and transitions of the state machine. As shown by [23] the synthesis problem is NP-hard, since the size of Q and  $\rightarrow$  grows exponentially with the number of components. Thus, the straightforward approaches for verification and synthesis described in Section 3.2 are limited by the *state-space explosion* problem. Therefore, this thesis proposes a *compositional* approach, described in Chapter 4, to solve synthesis and verification problems more efficiently.

### 3.3 Problems Considered

We assume that the components of a system are given as *deterministic* finitestate machines or extended finite-state machines. The individual components

Figure 3.3: The specification and the supervisor of the manufacturing system.

#### CHAPTER 3. SUPERVISORY CONTROL THEORY

have arbitrary alphabets, all the events of the systems are observable and the controllability characteristic of an event does not change from one component to another.

To be more detailed, the two problems considered are:

The modular nonblocking verification problem A modular system is modelled as

$$\mathscr{E} = \{E_1, \dots, E_n\} \tag{3.1}$$

where each  $E_i$  is an extended finite-state machine. The task is to verify whether the system  $\mathscr{E}$  is nonblocking. As only nonblocking verification is considered, the controllability of the events is irrelevant. Also, there is no need to treat specifications and supervisors differently from plants.

The modular supervisor synthesis problem A modular plant  $G = \{G_1, ..., G_m\}$  and a modular specification  $K = \{K_1, ..., K_l\}$  are given as FSM models. As mentioned before, the specifications are plantified and thus, the system is

$$\mathscr{G} = \{G_1, \dots, G_n\} \tag{3.2}$$

The task is to calculate a least restrictive, controllable and nonblocking supervisor which has a modular structure. Here, as the supervisor not only needs to be nonblocking but also controllable, in contrast to nonblocking verification, the controllability of events is considered.

## Chapter 4 The Compositional Approach

Usually discrete event systems are *modular* in the sense that the model of the system consists of a set of plant components and a set of specifications, all interacting with each other. The straightforward way to analyse a system involves building an explicit monolithic model which may lead to the inherent complexity problem known as the *state-space explosion* problem. This combinatorial problem occurs as the number of states grows exponentially with the number of components. This problem makes it intractable to examine the monolithic statespace of a system due to lack of memory and time. Consequently, constructing the explicit monolithic model of the system is not efficient and methods to exploit the modular structure or methods that efficiently represent the state-space of the system are needed. One way to exploit the modular structure of a system is to use a *compositional approach*. The compositional approach has previously been successfully used for *verification* of discrete event systems [2, 24–27]. In this thesis, the compositional approach is used both for verification and synthesis of systems, which are respectively modelled as a set of interacting EFSMs and FSMs.

In this chapter, Section 4.1 briefly overviews different existing approaches that help to avoid the state-space explosion problem. The general compositional approach is described in Section 4.2. The compositional nonblocking verification algorithm for EFSM systems is explained in Section 4.3. Finally, Section 4.4 describes two frameworks for compositional synthesis of FSM.

## 4.1 Alleviating the State-Space Explosion Problem

Various approaches to avoid state-space explosion have been proposed in the literature. This section briefly describes the *modular*, *hierarchical*, and *symbolic representation* approaches.

The modular approach was first introduced in [28]. In this work it was shown

#### CHAPTER 4. THE COMPOSITIONAL APPROACH

that controllability verification and controllability synthesis can be done by considering one specification at a time with the plant components it imposes requirements on. This approach was later developed in [29, 30]. The modular approach is very efficient, however all the works mentioned only consider controllability of a supervisor, and they do not guarantee global nonblocking of the closedloop behaviour. The work in [31], resolves conflict among modular supervisors. However, in this work the supervisor is not necessarily least restrictive.

Hierarchical approaches divide the system into different levels of hierarchy. This was first introduced by [32], and was later developed in [33]. In [33], the authors divide the system into high-level and low-level subsystems where subsystems communicate through *interfaces*. More recently, decentralized and hierarchical approaches are presented in [34–36]. In these works, the authors obtain decentralized supervisors for each specification and partition the plant components and decentralized supervisor into subsystems. *Natural projection* with the observer property is used as a method to abstract each subsystem. The work in [34] does not necessarily result in a least restrictive supervisor. To guarantee least restrictiveness, *output control consistency* [35] and the less restrictive condition of *local control consistency* [36] are proposed.

Algorithms based on Binary Decision Diagrams (BDDs) [37] convert the model of the system to a symbolic representation in the form of BDDs [38] and explore the full state-space symbolically [39]. By symbolic we mean that during analysis, the system is not represented directly as states and transitions but indirectly as Boolean functions. Representing a system symbolically, in many cases results in smaller representation of the state-space of the system. BDDs were first brought into the supervisory control theory by [40] and were later developed by [41–43].

## 4.2 General Compositional Approach

In this thesis, the compositional approach is used to alleviate the state-space explosion problem, and it is used both for nonblocking verification and supervisor synthesis. If the task is to verify nonblocking, then the controllability of the events is irrelevant and thus, the specifications can be considered as plants. Otherwise, the specifications are first plantified as explained in Section 3.2. Therefore, in both nonblocking verification and synthesis, the input to the compositional approach is a set of interacting plant components

$$\mathscr{G} = G_1 \parallel \cdots \parallel G_n. \tag{4.1}$$

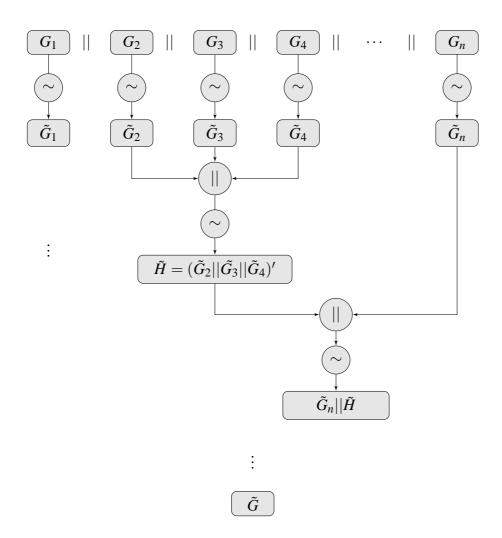

To alleviate the state-space explosion problem, the compositional approach constructs the monolithic model gradually, while abstracting components at each step. Before beginning the synchronisation process, each individual component is first abstracted, and the abstractions replace the original components. By abstractions we mean removing redundancy, and an abstracted component has less states or transitions compared to the original component. If no more abstraction is possible then some components need to be composed or, if the system is an EFSM system, some variables are removed by *partially unfolding* them (as explained in Section 4.3.2). Iteratively, the intermediate results are composed and abstracted again and again, until eventually, the procedure leads to a single state machine, which is an abstract representation of the system. This state machine has less states and transitions than the original system. The final step is to use the final abstracted state machine for either verification or supervisor calculation. Fig. 4.1 illustrates the general compositional approach.