# Electrical characterization of amorphous Al2O3 dielectric films on n-type 4H-SiC

Citation for the original published paper (version of record):

Khosa, R., Thorsteinsson, E., Winters, M. et al (2018). Electrical characterization of amorphous Al2O3 dielectric films on n-type 4H-SiC. AIP Advances, 8(2). http://dx.doi.org/10.1063/1.5021411

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

## Electrical characterization of amorphous Al<sub>2</sub>O<sub>3</sub> dielectric films on n-type 4H-SiC

R. Y. Khosa,<sup>1</sup> E. B. Thorsteinsson,<sup>1</sup> M. Winters,<sup>2</sup> N. Rorsman,<sup>2</sup> R. Karhu,<sup>3</sup> J. Hassan,<sup>3</sup> and E. Ö. Sveinbjörnsson<sup>1,3,a</sup>

(Received 4 January 2018; accepted 29 January 2018; published online 5 February 2018)

We report on the electrical properties of Al<sub>2</sub>O<sub>3</sub> films grown on 4H-SiC by successive thermal oxidation of thin Al layers at low temperatures (200°C - 300°C). MOS capacitors made using these films contain lower density of interface traps, are more immune to electron injection and exhibit higher breakdown field (5MV/cm) than Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition (ALD) or rapid thermal processing (RTP). Furthermore, the interface state density is significantly lower than in MOS capacitors with nitrided thermal silicon dioxide, grown in N<sub>2</sub>O, serving as the gate dielectric. Deposition of an additional SiO<sub>2</sub> film on the top of the Al<sub>2</sub>O<sub>3</sub> layer increases the breakdown voltage of the MOS capacitors while maintaining low density of interface traps. We examine the origin of negative charges frequently encountered in Al<sub>2</sub>O<sub>3</sub> films grown on SiC and find that these charges consist of trapped electrons which can be released from the Al<sub>2</sub>O<sub>3</sub> layer by depletion bias stress and ultraviolet light exposure. This electron trapping needs to be reduced if Al<sub>2</sub>O<sub>3</sub> is to be used as a gate dielectric in SiC MOS technology. © 2018 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5021411

### I. INTRODUCTION

4H-SiC metal-oxide semiconductor field-effect transistors (MOSFETs) are promising devices for power electronics. Such transistors are now commercially available for blocking voltages above 900 V.<sup>1,2</sup> These devices provide higher switching speeds and lower switching losses than Si MOS-FETs. However, SiC MOSFETs cannot compete with Si technology for lower blocking voltages because of poor electron channel mobility which limits the device on-resistance. A key problem is the high density of so called near-interface traps (NITs) detected at the SiO<sub>2</sub>/4H-SiC interface with energy levels near the SiC conduction band edge that limit the electron channel mobility.<sup>3-6</sup> Currently thermal oxides grown or annealed in NO or N<sub>2</sub>O are the mainstream dielectrics but more reduction in NITs is needed. Other large bandgap dielectrics such as AlN, Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> have also been investigated. 8-14 One of the alternatives is aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) with bandgap of  $\sim 7.0$  eV.  $^{8,11,15}$ Recently, an amorphous Al<sub>2</sub>O<sub>3</sub> has been used as a gate dielectric in graphene field effect transistors with some success. 16,17 Those Al<sub>2</sub>O<sub>3</sub> films are grown by atomic layer deposition (ALD) at 300°C or thermal evaporation of metallic Al followed by low temperature oxidation to form Al<sub>2</sub>O<sub>3</sub>. <sup>16,17</sup> As grown Al<sub>2</sub>O<sub>3</sub> deposited on 4H-SiC by ALD typically contains a large number of negative charges which are reduced after annealing in Ar at 1000°C but the Al<sub>2</sub>O<sub>3</sub>/SiC interface contains a high density of interface traps after such treatment.<sup>9,10</sup> More recently, studies on pre-deposition surface cleaning and post deposition annealing at different temperature in N<sub>2</sub>O ambient are been performed on ALD

<sup>&</sup>lt;sup>1</sup>Science Institute, University of Iceland, IS-107 Reykjavik, Iceland

<sup>&</sup>lt;sup>2</sup>Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296 Göteborg, Sweden

<sup>&</sup>lt;sup>3</sup>Department of Physics, Chemistry and Biology (IFM), Semiconductor Materials Division, Linköping University, SE-58183 Linköping, Sweden

<sup>&</sup>lt;sup>a</sup>Corresponding author: einars@hi.is

grown Al<sub>2</sub>O<sub>3</sub>. A high density of negative charge is observed in such samples and after post deposition annealing at  $1000^{\circ}$  C, an interfacial SiO<sub>x</sub> (0 < x < 2) layer grows containing a high density of interface traps. 18 There is a report on a very high peak field effect mobility of 300 cm<sup>2</sup>/Vs in SiC MOSFETs using Al<sub>2</sub>O<sub>3</sub> made by metal-organic chemical vapor deposition (MOCVD) with a thin SiO<sub>2</sub> interfacial layer to the SiC.<sup>13</sup> But, the mobility drops very rapidly with gate voltage and is less than 50 cm<sup>2</sup>/Vs at moderate gate voltages. Recently, a MOSFET with ALD grown Al<sub>2</sub>O<sub>3</sub>, post-annealed in hydrogen ambient at 400°C, was reported with a field effect mobility of 57 cm<sup>2</sup>/Vs. Even though these results are promising the Al<sub>2</sub>O<sub>3</sub> layers were sensitive to electron injection resulting in large threshold voltage shifts of the MOSFETs. 19 In previous studies, a careful attention has not been paid to the origin of negative charges within the Al<sub>2</sub>O<sub>3</sub> which normally are assumed to be a fixed oxide charge. In this work, we studied the interface quality of differently prepared Al<sub>2</sub>O<sub>3</sub>/4H-SiC interfaces, the breakdown properties of the Al<sub>2</sub>O<sub>3</sub> dielectrics as well as the origin of negative charges within the Al<sub>2</sub>O<sub>3</sub>. Recently, we reported a very low density of NITs in Al<sub>2</sub>O<sub>3</sub> layers formed on 4H-SiC by thermal oxidation of Al.<sup>20</sup> In this work, we investigate these layers in more detail and compare them with Al<sub>2</sub>O<sub>3</sub> layers grown by ALD or RTP and with SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack structure. We find that is it possible to grow Al<sub>2</sub>O<sub>3</sub> films with negligible negative charge and very low density of interface states at the Al<sub>2</sub>O<sub>3</sub>/4H-SiC interface.

#### II. EXPERIMENTAL METHODS

The SiC samples used in this study consist of 10 µm thick n-type epitaxial layers, with a net doping concentration of  $\sim 1 \times 10^{16}$  cm<sup>-3</sup>, grown on 4 degrees off-axis (0001) 4H-SiC substrates. The Al<sub>2</sub>O<sub>3</sub> layers are grown on the 4H-SiC substrates by different deposition methods. Prior to deposition all samples were rinsed in 2% HF for 1 min followed by rinse in deionized water and blown dry in nitrogen in order to remove the native oxide. In one of the deposition methods, a 1-2 nm thick Al metal layer is deposited by electron beam evaporation of Al in a vacuum chamber at a rate of 0.5 Å/s and then immediately the sample is baked on a hot plate in room environment at a temperature of 200°C for 5 minutes to form Al<sub>2</sub>O<sub>3</sub> layer, <sup>16,17,21</sup> This process of deposition and subsequent oxidation is repeated twelve times to get target thickness of  $\sim 15$  nm with an overall time span of about 4 hours. We refer to this method as hot plate  $Al_2O_3$ . A hot plate  $Al_2O_3$  sample was grown at  $300^{\circ}$ C as well and we found no difference in the electrical properties of these samples. A stack of SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> was made by growing a thick layer of 40 nm of SiO<sub>2</sub> on the top of the hot plate Al<sub>2</sub>O<sub>3</sub> by plasma enhanced chemical vapor deposition (PECVD) at 300°C using source gases of oxygen and silane. An Al<sub>2</sub>O<sub>3</sub> layer of 15 nm thickness was also grown by ALD at 300°C via thermal decomposition of Al<sub>2</sub>(CH<sub>3</sub>)<sub>6</sub> in water ambient. In addition, Al<sub>2</sub>O<sub>3</sub> films were made by using rapid thermal processing (RTP). The RTP Al<sub>2</sub>O<sub>3</sub> samples were prepared by evaporation of Al metal followed by rapid thermal oxidation in pure oxygen ambient. 6 nm of Al was deposited onto four separate SiC samples and subsequently oxidized at 500°C, 600°C, 700°C, and 1000°C for 30 min, 30 min, 15 min, and 5 min respectively. The Al deposition and oxidation cycle was repeated twice to achieve a target film thickness of 15 nm. Apart from the sample made at 1000°C, the resulting oxides were too leaky for CV characterization. The oxide thickness of all samples was estimated using X-ray reflectivity (XRR) and the crystallinity was investigated with X-ray diffraction (XRD) apart from the RTP grown samples. Our Al<sub>2</sub>O<sub>3</sub> films in this study are amorphous with no crystallization observed by XRD. The chemical composition of the films has not been verified here experimentally but previous studies using similar growth methods reveal the formation of amorphous Al<sub>2</sub>O<sub>3</sub>. <sup>22</sup> Reference samples with 20 nm thick thermal SiO<sub>2</sub> grown in dry oxygen (at 1150°C for 90 min) as well as 37 nm thick thermal SiO<sub>2</sub> grown in N<sub>2</sub>O (1240°C for 90 min) were also analyzed. The Al<sub>2</sub>O<sub>3</sub> samples are summarized in Table I below.

Circular n-type MOS capacitors were made using Al as a gate metal. The backside contact was formed by thick Ni (100nm) metallization. The capacitance- and current-voltage measurements (CV and IV) are performed on circular MOS pads, with diameter of 300  $\mu$ m and 100  $\mu$ m, using Agilent E4980A LCR meter and Keithley 617 electrometer respectively. To estimate the interface quality of Al<sub>2</sub>O<sub>3</sub>/SiC interface, conventional CV measurements are performed at room temperature and at different frequencies ranging from 1 kHz to 1 MHz, while to examine the negative charges within the Al<sub>2</sub>O<sub>3</sub>, room temperature CV measurements are made using UV light illumination. IV measurements

TABLE I. Summary of Al<sub>2</sub>O<sub>3</sub> MOS samples used in this study.

| No. | MOS structures                                           | Thickness of oxide | Method of oxide deposition                                                              |

|-----|----------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|

| 1   | Al/Al <sub>2</sub> O <sub>3</sub> /SiC                   | ~15 nm             | Hot plate at 200°C                                                                      |

| 2   | Al/SiO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> /SiC | ~40 nm/15 nm       | SiO <sub>2</sub> by PECVD at 300°C/Al <sub>2</sub> O <sub>3</sub> by hot plate at 200°C |

| 3   | Al/Al <sub>2</sub> O <sub>3</sub> /SiC                   | ~15 nm             | ALD at 300°C                                                                            |

| 4   | Al/Al <sub>2</sub> O <sub>3</sub> /SiC                   | ~15 nm             | RTP at 1000°C for 5 min                                                                 |

are used to examine the leakage current characteristics, the critical breakdown field and the tunneling barrier height of the dielectric Al<sub>2</sub>O<sub>3</sub>.

#### III. RESULTS AND DISCUSSION

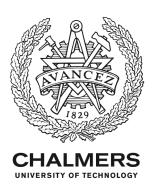

Figure 1 shows CV spectra of aluminum oxide MOS capacitors measured at room temperature and at 1 kHz and 1 MHz frequencies. The gate bias is swept from depletion (negative bias) to accumulation (positive bias) and the capacitance signal for both frequencies is recorded simultaneously at each gate bias point. Figure 1(a) shows the CV curves for a hot plate  $Al_2O_3$  sample. The dielectric constant deduced from the capacitance in accumulation (5 V) is about 6.5. A first estimate of the interface trap density is extracted from frequency dispersion of CV curves.<sup>23</sup> In this case, such dispersion is hardly visible indicating a rather low interface state density. Figure 1(b) shows the CV spectra of the  $SiO_2$ /hot plate  $Al_2O_3$  dielectric stack. Small frequency dispersion is observed indicating some increase in the interface state density. Figure 1(c) shows the CV spectra for ALD grown  $Al_2O_3$ . Two noticeable features are observed in the low frequency (1 kHz) CV curve. A "hump" at  $\sim 0$  V suggests the presence of specific rather deep interface traps that are not able to follow the 1 MHz test signal. Secondly the capacitance in accumulation is higher than the 1MHz curve and this is due to current leakage through the oxide which distorts the 1 kHz measurement. Figure 1(d) shows the CV

FIG. 1. CV curves at room temperature of: (a) a hot-plate  $Al_2O_3$  MOS capacitor (b) a dielectric stack of  $SiO_2$ /hot plate  $Al_2O_3$  (c) ALD grown  $Al_2O_3$  and (d) RTP grown  $Al_2O_3$ .

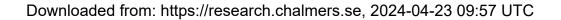

FIG. 2. Density of interface states  $(D_{it})$  as a function of energy from the SiC conduction band edge, extracted from CV analysis at room temperatures for the sole and stack  $Al_2O_3$  dielectric samples grown by different methods and samples with thermal  $SiO_2$  grown in  $O_2$  or  $N_2O$  ambient.

spectra for the RTP grown Al<sub>2</sub>O<sub>3</sub>. A very large frequency dispersion reveals high density of interface states.

Figure 2 compares the interface state density in the different  $Al_2O_3$  samples extracted from frequency dispersion of room temperature CV data (between 1kHz and 1 MHz) together with data from reference samples with thermal  $SiO_2$  made in dry oxygen or  $N_2O$  ambient. It is evident in figure 2 that the hot plate  $Al_2O_3$  sample contains the lowest density of interface traps. The interface state density in the  $Al_2O_3$  stack sample is comparable with nitrided reference  $SiO_2$  sample but is lower than in reference  $SiO_2$  grown in  $O_2$ . The ALD grown  $Al_2O_3$  shows a peak in the interface state density at energies between O.35-O.55 eV from the SiC conduction band edge. RTP grown  $Al_2O_3$  has relatively high density of interface traps.

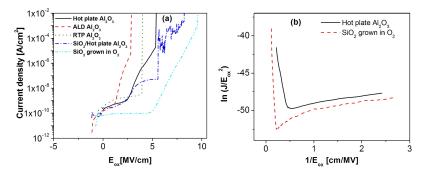

The MOS capacitors were investigated by IV as well at room temperature. Leakage current density vs electric field (J-E) curves for several different samples are shown in figure 3(a). The sole hot plate  $Al_2O_3$  has breakdown field ( $\sim 5$  MV/cm) which is higher than the ALD and RTP grown  $Al_2O_3$  films. This value of the breakdown field is about half the breakdown field achieved in the reference  $SiO_2/SiC$  MOS capacitor (light blue dash dot dot curve in figure 3(a). Reported breakdown field of  $Al_2O_3$  on SiC varies in literature and the highest value, to our knowledge, is approximately 8 MV/cm in amorphous ALD grown films. However, in that study the leakage current density prior to breakdown was of the order of  $10^{-3}$  A/cm<sup>2</sup> which is few orders of magnitudes higher than in the hot-plate grown  $Al_2O_3$ . In case of the  $SiO_2/Al_2O_3$  stack (dark blue dash dot curve in figure 3a), the effective breakdown field,  $E_{eff} = \frac{V_G - V_{FB}}{I_{ox,total}}$  treating the dual dielectric as a single dielectric, is

FIG. 3. (a) Comparison of leakage current density vs electric field across the oxide (J-E) of differently prepared  $Al_2O_3$  along with a reference sample with thermal  $SiO_2$  grown in  $O_2$ , (b) A Fowler-Nordheim plot for hot plate grown  $Al_2O_3$  and for dry  $SiO_2$ .

$\sim 8$  MV/cm. Here  $V_G$ ,  $V_{FB}$  and  $t_{ox,total}$  are the gate voltage, flatband voltage and the thickness of the dielectric stack respectively. A steep increase in the current is observed around 5 MV/cm but before that the leakage current value is relative low around  $10^{-8}$  A/cm. The breakdown field across the Al<sub>2</sub>O<sub>3</sub> dielectric can be determined by considering the difference of the dielectric constants in the stack using the expression:<sup>24</sup>

$$E_{Al2O3} = \frac{V_G - V_{FB}}{t_{Al2O3}} \times \frac{C_{ox,SiO2}}{C_{ox,SiO2} + C_{ox,Al2O3}}$$

(1)

Here  $t_{Al2O3}$  denotes the thickness of  $Al_2O_3$ .  $C_{ox,SiO2}$  and  $C_{ox,Al2O3}$  are the calculated capacitances of  $SiO_2$  and  $Al_2O_3$  respectively by taking into account the corresponding dielectric constant and thickness of the dielectric. This expression gives the breakdown field value of  $\sim 5.5$  MV/cm across the  $Al_2O_3$  dielectric in the stack. This indicates that the addition of  $SiO_2$  layer on top of the hot plate  $Al_2O_3$  has not much impact on the breakdown field of  $Al_2O_3$  but the benefit of stack dielectric MOS capacitor is that it can operate at higher gate voltages.

Significant Fowler-Nordheim (F-N) tunneling is seen in the J-E profile of the sole hot plate Al<sub>2</sub>O<sub>3</sub> and reference dry SiO<sub>2</sub> MOS sample. Therefore, the J-E response of these MOS sample was analyzed further using F-N tunneling mechanism to determine the tunneling barrier height. F-N tunneling current density across MOS devices at high field is described by:<sup>25</sup>

$$J = AE^2 \exp\left(\frac{-B}{E}\right) \tag{2}$$

Where,  $A = \frac{q^3 m}{8\pi h m_{ox} \phi_b}$  and  $B = \frac{8\pi \sqrt{2m_{0x}} \phi_b^{\frac{3}{2}}}{3hq}$ . The parameters A and B depend on the tunneling barrier height  $\phi_b$  and the effective mass of the tunneling electron  $m_{ox}$  in the oxide. A and B, can be derived from the experimental IV characteristics plotted as  $\ln(J/E^2)$  vs. I/E, a so-called F-N plot. The slope of the straight line at high electric fields gives B while A is determined from the intercept. Since B is the exponent in equation (2) for F-N tunneling current density, it is the prominent parameter in determining the current flow in the gate oxide.  $^{25}$

Figure 3(b) shows F-N plot for a hot plate grown  $Al_2O_3$  and for a reference dry  $SiO_2$ . The value of parameter B is 38 MV/cm and 175 MV/cm for  $Al_2O_3$  grown by hot plate and for reference dry  $SiO_2$  respectively. The effective barrier height for the hot plate grown  $Al_2O_3/4$ H-SiC interface extracted from this analysis is 1.15 eV by taking effective electron mass in  $Al_2O_3$  to be  $0.2m_o$  where  $m_o$  is the free electron mass. A  $SiO_2/4$ H-SiC barrier height of 2.50 eV is obtained by assuming  $m_{ox}$  in  $SiO_2$  is  $0.42m_o$ . This barrier height of the reference  $SiO_2/4$ H-SiC MOS sample is reasonably close to the previously reported values for dry  $SiO_2$  determined by F-N tunneling mechanism. The highest barrier height in literature for amorphous ALD grown  $Al_2O_3/4$ H-SiC, determined by F-N tunneling mechanism, is 1.58 eV as compared to 1.15 eV in our hot-plate. This indicates that the hot plate  $Al_2O_3/4$ H-SiC interface has some defect states that limit the oxide breakdown field.

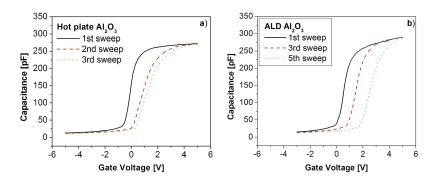

The  $Al_2O_3$  samples are all found to be sensitive to electron injection except the RTP grown  $Al_2O_3$ . RTP grown  $Al_2O_3$  may have a thin interface layer of  $SiO_2$  that forms during the high temperature treatment as reported in literature.  $^{9,10,18}$  The electron injection is observed by a shift of the CV curve after applying accumulation bias. Figure 4 shows such examples for hot plate and ALD grown  $Al_2O_3$  samples. Repeated sweeps from depletion to accumulation result in a positive flatband voltage shift which saturates after several sweeps. This saturation has not been observed in the  $SiO_2$ /hot plate  $Al_2O_3$  stack. The magnitude of the shift depends on the maximum accumulation voltage (in this case 5 V) and is larger in the ALD grown  $Al_2O_3$ . It is evident that electrons are trapped in the dielectric under accumulation bias and do not return to the SiC when the samples are biased in depletion. The electron charge trapped in the hot plate  $Al_2O_3$  is approximately  $3.4 \times 10^{12}$  cm<sup>-2</sup> and  $\sim 5.0 \times 10^{12}$  cm<sup>-2</sup> in the ALD  $Al_2O_3$ . This is significantly lower than previously reported in as grown ALD films where the densities are typically in the  $1 \times 10^{13}$  cm<sup>-2</sup> range or higher.  $^{9-11}$

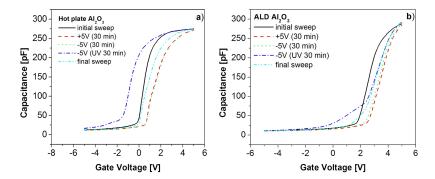

We examined the existence of electron capture and emission from traps within the aluminum oxide by using bias stress and UV illumination. The UV light was provided with a fluorescent lamp with mercury lines providing carrier generation across the 4H-SiC bandgap. Figure 5 shows the results of such an experiment for different  $Al_2O_3$  samples at room temperature. The first reference CV (black solid curve) sweep is from depletion to accumulation on MOS pads after a stable flatband

FIG. 4. (a) CV spectra of a hot plate  $Al_2O_3$  sample upon repeated gate voltage sweeps from depletion to accumulation, (b) the same experiment for ALD grown  $Al_2O_3$ . The shifts of the CV curves are due to trapping of electrons within the  $Al_2O_3$  under strong accumulation bias which saturates after several sweeps.

FIG. 5. CV characteristics ( $100 \, \text{kHz}$ ) at  $300 \, \text{K}$  of (a) hot plate- and (b) ALD- grown  $\text{Al}_2\text{O}_3$  samples before and after applying positive or negative bias stress to them. The black solid curves denote the first reference curves made after obtaining stable flatband voltage at  $300 \, \text{K}$  (see figure 4). The light blue dash dot dot curves are the final curves recorded at the end of the experiment. For details see main text.

voltage is reached (as in figure 4) The MOS capacitor is then kept in accumulation (+5 V) for 30 minutes and then the bias is swept from depletion (-5 V) to accumulation (+5V) and the CV (red dashed curve) is recorded. Electrons are injected into the oxide during the accumulation bias stress and electron trapping is detected as a positive flatband shift.

Next, a depletion bias of -5 V is applied for 30 min to examine if electrons are released from oxide traps under such conditions. The CV (green dotted curves) are recorded directly thereafter and are almost identical to the curves recorded after accumulation bias stress CV (red dashed curves) showing that there is insignificant release of electrons from oxide traps. Next, ultraviolet (UV) light is applied to the sample under depletion bias (-5 V) for 30 min. A negative flatband voltage shift of about 2 V is observed in the hot plate  $Al_2O_3$  sample in the CV sweep following the UV light illumination (dark blue dash dot curve). It is evident that electrons trapped in the  $Al_2O_3$  are released during the UV exposure. The number density of released electrons can be estimated by using the expression:

$$N_{it} = \frac{C_{ox} \left( V_{FB} - V_{FB(UV)} \right)}{qA} \tag{3}$$

where  $V_{FB}$  and  $V_{FB(UV)}$  are flat band voltages before applying accumulation bias stress and after UV light exposure to the MOS capacitors respectively. The number density of released trapped charge in hot plate  $Al_2O_3$  sample is  $\sim 4x10^{12}$  cm<sup>-2</sup>. The flatband voltage after UV exposure is close to the theoretical value suggesting that most of the trapped electrons within the oxide are released during the UV treatment. These traps are filled again once the sample is biased in accumulation as seen in the final sweep (light blue dash dot dot curve).

The behavior in the other  $Al_2O_3$  samples is similar regarding the effect of the UV light exposure. The same experiment for ALD  $Al_2O_3$  is shown in figure 5b). As in the hot plate sample electrons are trapped within the oxide under accumulation bias and are not released again unless UV exposure under deep depletion is applied. The main difference here is that electrons are immediately re-trapped within the oxide during the first sweep after UV exposure (dark blue dash dot curve). A stretch-out of the CV curve suggests that electrons are recaptured within the oxide as the gate voltage leads the device to accumulation. In contrast, strong accumulation bias is needed to recapture electrons within the hot plate  $Al_2O_3$  (see dark blue dash dot curve in Figure 5a).

The possible effect of the UV light is twofold. Firstly, it is possible that the UV photons are "absorbed" by the trapped electrons in the  $Al_2O_3$  resulting in a release of the electrons to the SiC conduction band. Secondly, the UV exposure creates electron hole pairs and the depletion layer shrinks correspondingly. This means that the electric field across the oxide increases which can result in enhanced field assisted emission of electrons from traps within the  $Al_2O_3$  to the SiC conduction band. We cannot distinguish between these two possibilities in this experiment but very similar behavior has been observed for thermal oxides on SiC containing sodium ions.<sup>27</sup>

This experiment demonstrates two things. First, the net negative charge observed in the  $Al_2O_3$  layers is not a permanently fixed charge but rather electrons trapped within the oxide which can be released to the SiC using depletion bias and UV exposure. Such net negative oxide charge is reported in ALD grown  $Al_2O_3$  in literature but the charge density is typically an order of magnitude higher than what is observed in this study.  $^{9-11}$  The negative charge has been attributed to charged ions within the oxide and assumed to be fixed oxide charge but has not been investigated further as done here. Secondly, we have some initial trapping of electrons in the aluminum oxides during growth which is possible to enhance by accumulation bias.

The main results reported here are rather remarkable.  $Al_2O_3$  grown by oxidation of Al on a hot plate has significantly better electrical properties than ALD or RTP grown films. However, electron injection and relatively low breakdown field (5MV/cm) are still parameters that need to be improved in order to use  $Al_2O_3$  dielectrics in SiC MOS technology.

#### IV. CONCLUSIONS

We find the  $Al_2O_3$  layer grown by repeated deposition and subsequent low temperature (200°C) oxidation of thin Al layers using a hot plate are more immune to electron injection and have a very low density of traps at the  $Al_2O_3$ /SiC interface compared to  $Al_2O_3$  grown by ALD or RTP. Electron injection within the  $Al_2O_3$  during positive bias stress and the release of injected electrons by UV light illumination show that our  $Al_2O_3$  samples do not contain negative fixed charge as frequently mentioned in literature. Breakdown field of the hotplate  $Al_2O_3$  is  $\sim 5$  MV/cm which is higher than of  $Al_2O_3$  samples grown by ALD or RTP but still only half the value obtained in thermal  $SiO_2$  grown on 4H-SiC. It is possible to increase the breakdown voltage of the  $Al_2O_3$  based MOS capacitors by depositing a  $SiO_2$  layer on the top of hot plate  $Al_2O_3$  and maintain low density of interface traps at the  $Al_2O_3$ /SiC interface.

#### **ACKNOWLEDGMENTS**

This work was financially supported by The University of Iceland Research Fund. We also acknowledge support from the Swedish Foundation for Strategic Research (SSF), and the Knut and Alice Wallenberg Foundation (KAW).

```

<sup>1</sup> www.wolfspeed.com.

```

<sup>&</sup>lt;sup>2</sup> www.rohm.com.

<sup>&</sup>lt;sup>3</sup> V. V. Afanasev, A. Stesmans, M. Bassler, G. Pensl, and M. J. Schulz, Appl. Phys. Lett. **76**, 336 (2000).

<sup>&</sup>lt;sup>4</sup> G. Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, M. D. Ventra, S. T. Pantelides, L. C. Feldman, and R. A. Weller, Appl. Phys. Lett. 76, 1713 (2000).

<sup>&</sup>lt;sup>5</sup> H. Ö. Ólafsson, F. Allerstam, and E. Ö. Sveinbjörnsson, Mater. Sci. Forum **389**, 1005 (2002).

<sup>&</sup>lt;sup>6</sup> H. Yoshioka, J. Senzaki, A. Shimozato, Y. Tanaka, and H. Okumura, AIP Advances 5, 017109 (2015).

<sup>&</sup>lt;sup>7</sup> T. Kimoto, Japanese J. Appl. Phys. **54**, 040103 (2015).

<sup>&</sup>lt;sup>8</sup> V. V. Afanasev, F. Ciobanu, S. Dimitrijev, G. Pensl, and A. Stesmans, J. Phys. Condens. Matter 16, 1839 (2004).

- <sup>9</sup> M. Avice, U. Grossner, I. Pintilie, B. G. Svensson, M. Servidori, R. Nipoti, O. Nilsen, and H. Fjellvag, J. Appl. Phys. 102, 054513 (2007).

- <sup>10</sup> M. Avice, U. Grossner, O. Nilsen, J. S. Christensen, H. Fjellvag, and B. G. Svensson, Mater. Sci. Forum **527**, 1067 (2006).

- <sup>11</sup> C. M. Tanner, Y.-C. Perng, C. Frewin, S. E. Saddow, and J. P. Chang, Appl. Phys. Lett. **91**, 203510 (2007).

- <sup>12</sup> C. M. Zetterling, M. Östling, N. Nordell, O. Schön, and M. Deschler, Appl. Phys. Lett. **70**, 3459 (2000).

- <sup>13</sup> T. Hatayama, S. Hino, N. Miura, T. Oomori, and E. Tokumitsu, IEEE Trans. Electron Devices **55**, 2041 (2008).

- <sup>14</sup> M. Horita, M. Noborio, T. Kimoto, and J. Suda, IEEE Trans. Electron Devices 35, 339 (2014).

- <sup>15</sup> F. Zheng, G. Sun, L. Zheng, S. Liu, B. Liu, L. Dong, L. Wang, W. Zhao, X. Liu, G. Yan, L. Tian, and Y. Zeng, J. Appl. Phys. 113, 044112 (2013).

- <sup>16</sup> Z. Feng, C. Yu, J. Li, Q. Liu, Z. He, X. Song, J. Wang, and S. Cai, Carbon 75, 249 (2014).

- <sup>17</sup> A. Badmaev, Y. Che, Z. Li, C. Wang, and C. Zhou, ACS Nano **6**, 3371 (2012).

- <sup>18</sup> S. S. Suvanam, Ph.D. thesis, KTH Royal Institute of Technology, Sweden (2017) (ISBN: 978-91-7729-252-4).

- <sup>19</sup> H. Yoshioka, M. Yamazaki, and S. Harada, AIP Advances 6, 105206 (2016).

- <sup>20</sup> R. Y. Khosa, E. Ö. Sveinbjörnsson, M. Winters, J. Hassan, R. Karhu, E. Janzén, and N. Rorsman, Mater. Sci. Forum 897, 135 (2017).

- <sup>21</sup> M. Winters, E. Ö. Sveinbjörnsson, C. Melios, O. Kazakova, W. Strupinski, and N. Rorsman, AIP Advances 6, 085010 (2016).

- <sup>22</sup> L. P. H. Jeurgens, W. G. Sloof, F. D. Tichelaar, and E. J. Mittemeijer, Thin Solid Films 418, 89 (2002).

- <sup>23</sup> D. K. Schroder, *Semiconductor Material and Device Characterization*, 3rd edition (Wiley, New York, USA, 1998).

- <sup>24</sup> R. G. Southwick, J. Reed, C. Buu, R. Butler, G. Bersuker, and W. B. Knowlton, IEEE Trans. Device Mater. Rel. 10, 201 (2010).

- <sup>25</sup> Y. L. Chiou, J. P. Gambino, and M. Mohammad, Solid-State Electron. **45**, 1787 (2001).

- <sup>26</sup> A. K. Agarwal, S. Seshadri, and L. B. Rowland, IEEE Electron Device Lett. **18**, 592 (1997).

- <sup>27</sup> F. Allerstam, H. Ö. Ólafsson, G. Gudjonsson, D. Dochev, E. Ö. Sveinbjörnsson, T. Rödle, and R. Jos, J. Appl. Phys. 101, 124502 (2007).