## Graphene field-effect transistors with high extrinsic fT and fmax

Downloaded from: https://research.chalmers.se, 2025-12-04 22:38 UTC

Citation for the original published paper (version of record):

Bonmann, M., Asad, M., Yang, X. et al (2019). Graphene field-effect transistors with high extrinsic fT and fmax. IEEE Electron Device Letters, 40(1): 131-134. http://dx.doi.org/10.1109/LED.2018.2884054

N.B. When citing this work, cite the original published paper.

© 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, or reuse of any copyrighted component of this work in other works.

#### 1

# Graphene field-effect transistors with high extrinsic $f_T$ and $f_{max}$

Marlene Bonmann, Muhammad Asad, Xinxin Yang, Andrey Generalov, Andrei Vorobiev, Luca Banszerus, Christoph Stampfer, Martin Otto, Daniel Neumaier, and Jan Stake, *Senior Member, IEEE*

Abstract—In this work, we report on the performance of graphene field-effect transistors (GFETs) in which the extrinsic transit frequency (f<sub>T</sub>) and maximum frequency of oscillation (fmax) showed improved scaling behavior with respect to the gate length (Lg). This improvement was achieved by the use of high-quality graphene in combination with successful optimization of the GFET technology, where extreme low source/drain contact resistances were obtained together with reduced parasitic pad capacitances. GFETs with gate lengths ranging from 0.5  $\mu$ m to 2  $\mu$ m have been characterized, and extrinsic fr and fmax frequencies of up to 34 GHz and 37 GHz, respectively, were obtained for GFETs with the shortest gate lengths. Simulations based on a small-signal equivalent circuit model are in good agreement with the measured data. Extrapolation predicts extrinsic f<sub>T</sub> and f<sub>max</sub> values of approximately 100 GHz at Lg=50 nm. Further optimization of the GFET technology enables fmax values above 100 GHz, which is suitable for many millimeter wave applications.

Index Terms—graphene, field-effect transistor, maximum frequency of oscillation, transit frequency, scaling

#### I. INTRODUCTION

HE two-dimensional material graphene is a promising candidate for application in high-frequency devices due to its high charge carrier saturation velocity [1]. Until recently, the realization of graphene field-effect transistors (GFETs) for high-frequency electronics was hindered by extrinsic limitations caused by impurities that reduced the carrier velocity, large extrinsic source/drain contact resistances, and large pad capacitances [2]-[5]. Recent publications have shown that efforts to develop high-frequency GFETs have resulted in a continuous step-by-step improvement of the extrinsic transit (cut-off) frequency ( $f_T$ ) and the maximum frequency of oscillation ( $f_{\text{max}}$ ) [5]–[10]. However, even the best reported extrinsic values of  $f_T$  and  $f_{max}$  of GFETs are still below those of n-channel Si MOSFETs with comparable gate lengths [11]-[13]. Furthermore, the increase in  $f_T$  and  $f_{max}$  with scaling down of the gate length has been suppressed [5], [7].

This work was supported in part by the European Unions Horizon 2020 program under Grant No. 696656 and No. 785219, by the Swedish Foundation for Strategic Research under Grant No. SE13-0061, and by the Swedish Research Council under Grant No. 2017-04504.

M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, and J. Stake are with the Chalmers University of Technology, SE-41296 Gothenburg, Sweden (e-mail: marbonm@chalmers.se.)

A. Generalov is now with Aalto University, Helsinki, Finland.

L. Banszerus, and C. Stampfer are with the 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany.

M. Otto, and D. Neumaier are with the Advanced Microelectronic Center Aachen, AMO GmbH, 52074 Aachen, Germany.

In this work, we report on GFETs that exhibit improved extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  values and improved scaling behavior with the gate length in comparison to the best published data for GFETs. Furthermore, the scaling behavior is comparable to that of Si n-channel MOSFETs. The enhancement was achieved by a combination of the following improvements of the GFET design and fabrication process: i) usage of high-quality graphene films, ii) effective removal of polymer residues in the contact areas, and iii) usage of a thicker SiO<sub>2</sub> layer (1  $\mu$ m) on top of the silicon substrate. These improvements resulted in charge carrier saturation velocities as high as  $1.5 \times 10^5$  m/s (at drain fields of 1.5 kV/cm), source/drain specific edge contact resistivities as low as  $90~\Omega\mu$ m, and considerably reduced extrinsic pad capacitances.

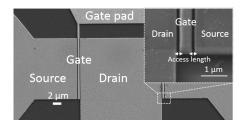

Fig. 1. SEM image of a two-finger GFET with gate length  $L_{\rm g}=0.5~\mu{\rm m}$  and gate width  $W_{\rm g}=2\times15~\mu{\rm m}$ . The inset shows a 70° tilted view of the gate area.

#### II. FABRICATION

Two-finger gate GFETs (shown in Fig. 1) with the same layout as previously published in [4] were fabricated. The process flow was modified with the aim of increasing, first of all  $f_{\text{max}}$  but also  $f_{\text{T}}$ . The graphene film used for fabricating the GFETs was very high-quality chemical vapor deposition (CVD) graphene with a Hall mobility of up to 7000 cm<sup>2</sup>/Vs. The graphene film was transferred to a highresistivity silicon/silicon oxide (Si/SiO<sub>2</sub>) substrate with an increased SiO<sub>2</sub> thickness of  $1 \,\mu m$  compared to the  $0.09 \,\mu m$ and  $0.3 \,\mu \text{m}$  used in our previous works [4], [14]. This resulted in a reduction in the parasitic pad capacitances. After the graphene transfer, but prior to any further processing, the graphene film was covered by an 5 nm protective Al<sub>2</sub>O<sub>3</sub> layer. This layer was obtained by repeating four times the process step in which 1 nm Al was evaporated and subsequently oxidized by baking on a hotplate at 160 °C for 5 min. The protective layer encapsulates graphene in the transistor

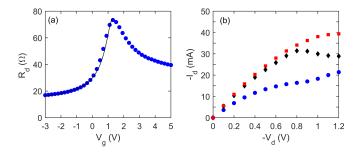

Fig. 2. Typical drain resistance  $(R_{\rm d})$  versus gate voltage  $(V_{\rm g})$  at the drain voltage  $V_{\rm d}=-0.1$  V (a) and output characteristics measured at  $V_{\rm g}$ =-3,-1, and 0.5 V (squares, diamonds, and circles, respectively) (b) of a GFET with  $L_{\rm g}=0.5~\mu{\rm m}$  and  $W_{\rm g}=2\times15~\mu{\rm m}$ . The solid line represents fitting by the drain resistance model [17].

channel and prevents it from contamination during further processing, thereby reducing the trap concentration at the graphene/gate dielectric interface. The graphene mesa and, subsequently, the drain and source contacts are patterned by e-beam lithography followed by etching the protective Al<sub>2</sub>O<sub>3</sub> in a buffered oxide etch. Oxygen plasma was used to etch the graphene mesa. The drain/source contacts were formed by deposition of 1 nm Ti/15 nm Pd/250 nm Au and use of standard lift-off technology. Apparently, the use of a buffered oxide etch resulted in a more effective removal of e-beam resist and PMMA residues and, hence, an extremely low graphene/metal specific contact resistivity as low as  $90 \Omega \mu m$ . In the next step, atomic layer deposition was used to thicken the protective  $Al_2O_3$  layer to a total thickness of  $t_{ox} = 22 \text{ nm}$  in the gate area. The gate electrode was fabricated by e-beam lithography and deposition of 10 nm Ti/290 nm Au by e-beam evaporation followed by standard lift-off. GFETs with total gate widths  $(W_g)$  ranging from  $2x1.25 \,\mu\mathrm{m}$  to  $2x15 \,\mu\mathrm{m}$  and gate lengths  $(L_{\rm g})$  ranging from 0.5  $\mu{\rm m}$  to 2  $\mu{\rm m}$  were fabricated. In the final step, the gate and the drain/source contact pads were formed by e-beam lithography, deposition of 10 nm Ti/290 nm Au and lift-off.

### III. MEASUREMENTS

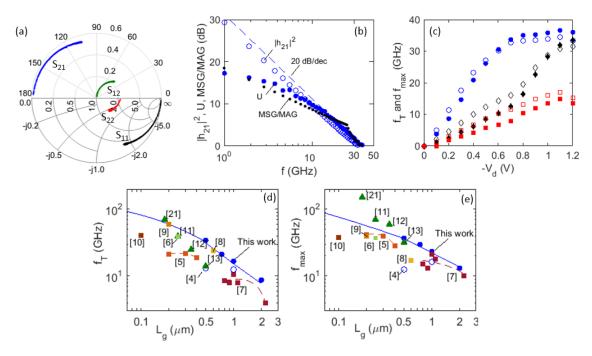

The dc and ac performance of the GFETs was characterized using a Keithley 2612B dual-channel source meter and an Agilent N5230A network analyzer, respectively. The ac measurement system was calibrated at the ground-source-ground microwave probe tips using a CS-5 calibration substrate. The output characteristics were obtained during the S-parameter measurements with a holding time of 30 s at each bias point. This holding time is long enough for the trapping/de-trapping processes to stabilize at high fields [4]. The S-parameters were measured under different bias conditions in the frequency range of 1-50 GHz and were used to calculate the small-signal current gain  $(h_{21})$  and the unilateral power gain (U) [15], [16]. As shown in Fig. 3(a),  $f_{\rm T}$  and  $f_{\rm max}$  are defined as the frequencies at which the magnitudes of  $h_{21}$  and U, respectively, have decreased to 0 dB.

#### IV. RESULTS AND DISCUSSION

Fig. 2(a) shows a typical drain resistance versus gate voltage of a GFET with  $L_{\rm g}=0.5\,\mu{\rm m}$  and  $W_{\rm g}=2\times15\,\mu{\rm m}$ . The solid line represents fitting by the drain resistance model [17], which is used to estimate the contact resistance  $(R_{\rm c})$ , low-field mobility  $(\mu_0)$ , and residual charge carrier concentration  $(n_0)$  which are found to be  $11\,\Omega$ ,  $1800\,{\rm cm^2/Vs}$  and  $9\times10^{11}\,{\rm cm^{-2}}$ , respectively. The calculated graphene/metal width specific contact resistivity is  $90\,\Omega\mu{\rm m}$ , which is in good agreement with the value of  $95\,\Omega\mu{\rm m}$  found using transfer length method test structures fabricated on the same substrate.

Fig. 2(b) shows the typical output characteristics of GFETs. The drain current exhibits a saturation tendency at higher drain voltages  $(V_d)$ . The observed so-called kink effect at  $V_g = 0.5 \,\mathrm{V}$ is most likely associated with the reduction in the charge carrier concentration and a subsequent change in the charge carrier type at the drain side of the channel [3]. A negative differential resistance at  $V_{\rm g} = -1 \, {\rm V}$  can be associated with a reduction in the charge carrier density-dependent saturation velocity [18]. Both effects are consequences of the ambipolar nature of graphene. Fig. 3(a) shows the smith chart with measured S-parameters between 1 GHz and 50 GHz. Fig. 3(b) shows the small-signal current gain  $(|h_{21}|^2)$ , maximum stable gain/maximum available gain (MSG/MAG), and unilateral power gain (U) versus frequency (f) at  $V_d = -1.1 \,\mathrm{V}$  and  $V_{\rm g} = 0.5 \, \text{V}$ . As it can be seen, the unilateral power gain reveals typical frequency dependence. The low frequency gain is approx. 18 dB. Above the roll-off frequency of approx. 5 GHz the gain starts decreasing as  $1/f^2$ , corresponding to 20 dB/dec slope [19]. Fig. 3(c) shows  $f_{\rm T}$  and  $f_{\rm max}$  versus  $V_{\rm d}$ at different gate voltages of  $V_{\rm g}=0.5,-1,$  and -3 V. Both  $f_{\rm T}$ and  $f_{\text{max}}$  saturate at higher drain voltages, apparently, due to velocity saturation [4], reaching values of 34 GHz and 37 GHz, respectively. To estimate the gate width and length dependence of  $f_{\rm T}$  and  $f_{\rm max}$ , expressions in terms of small-signal equivalent circuit parameters are used [20], [21]:

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi (C_{\rm gs} + C_{\rm gd})} \frac{1}{1 + g_{\rm d}R_{\rm c} + \frac{C_{\rm gd}g_{\rm m}R_{\rm c}}{C_{\rm gs} + C_{\rm gd}} + C_{\rm pad}}, \quad (1)$$

$$f_{\rm max} = \frac{g_{\rm m}}{4\pi C_{\rm gs}} \frac{1}{\sqrt{g_{\rm d}(R_{\rm i} + R_{\rm s} + R_{\rm g}) + g_{\rm m}R_{\rm g}\frac{C_{\rm gd}}{C_{\rm gs}}}},$$

(2)

where  $g_{\rm m}$  and  $g_{\rm d}$  are the intrinsic transconductance and drain conductance, respectively;  $C_{\rm gs}$ ,  $C_{\rm gd}$  and  $C_{\rm pad}$  are the gatesource, gate-drain and parasitic pad capacitances, respectively; and  $R_{\rm g}$ ,  $R_{\rm s}$ , and  $R_{\rm i}$  are the gate resistance, source series resistance, and charging resistance of the gate-source capacitance, respectively. We estimated  $C_{\rm gs}$  and  $C_{\rm gd}$  as  $C_{\rm gs} = 0.5C_{\rm ox}L_{\rm g}W_{\rm g}$  and  $C_{\rm gd}=k_1C_{\rm ox}L_{\rm g}W_{\rm g}$ , where  $C_{\rm ox}\propto 1/t_{\rm ox}$  and  $k_1$  is a fitting parameter taking into account the decrease in charge carrier concentration at the drain side [8]. The intrinsic transconductance was found to be  $g_{\rm m}=v(C_{\rm gs}+C_{\rm gd})/L_{\rm g}$ , where v is the field-dependent effective velocity of the charge carriers, with values between 1.2 and  $1.5\times10^5$  m/s for different devices extracted from a field-dependent velocity model [4]. The intrinsic drain conductance was found by analyzing the GFET output characteristics. The resistances are estimated

Fig. 3. (a) Smith chart with measured S-parameters between 1 GHz and 50 GHz. (b) Small-signal current gain  $(|h_{21}|^2)$ , maximum stable gain/maximum available gain (MSG/MAG), and unilateral power gain (U) versus frequency (f) at  $V_d = -1.1$  V and  $V_g = 0.5$  V. The dashed line indicates the 20 dB/dec slope. (c) Extrinsic transit frequency  $(f_T, \text{ open symbols})$  and extrinsic maximum frequency of oscillation  $(f_{\text{max}}, \text{ filled symbols})$  versus drain voltage  $(V_d)$  at different gate voltages  $V_g = 3, -1$ , and 0.5 V (squares, diamonds, and circles, respectively) of a GFET with  $L_g = 0.5 \,\mu\text{m}$  and  $W_g = 2 \times 15 \,\mu\text{m}$ . (d) Extrinsic transit frequency  $(f_T)$  versus gate length  $(L_g)$  of GFETs measured in this work (solid circles) and simulated using (1) (solid line). (e) Extrinsic maximum frequency of oscillation  $(f_{\text{max}})$  versus gate length  $(L_g)$  of GFETs measured in this work (solid circles) and simulated using (2) (solid line). Also shown are the highest published extrinsic  $f_T$  and  $f_{\text{max}}$  values of GFETs [5]–[10] (squares) and Si MOSFETs [11]–[13], [22] (triangles) and our previous published work (open circles) [4] for comparison. Dashed lines are polynomial fitting curves.

as  $R_{\rm i}=1/(3g_{\rm m})$  and  $R_{\rm g}=1/3R_{\rm shg}W_{\rm g}/L_{\rm g}$ , where  $R_{\rm shg}$  is the gate electrode sheet resistance [21]. The source series resistance  $R_{\rm s}$  is assumed to be  $R_{\rm c}/2$ . The parasitic gate pad capacitance, formed between the gate pad and low-conductivity surface of Si, is taken as 3 times less than that found in [4] by delay-time analysis ( $\approx 27\,{\rm fF}$ ) due to the three times thicker SiO<sub>2</sub> layer.

Fig. 3(d-e) shows the measured and simulated extrinsic  $f_T$ and  $f_{\rm max}$  values versus gate length for GFETs with  $W_{\rm g} =$  $2 \times 15 \,\mu\text{m}$ . The simulations and measurements are in good agreement. Also shown are the extrinsic  $f_T$  and  $f_{max}$  values obtained in our previous work and the best values published in the literature. It can be seen, that the GFETs in this work reveal higher  $f_{\rm T}$  and  $f_{\rm max}$  values than that of the best reported GFETs [3], [7], including the GFETs fabricated by our prior technology [4], and even Si MOSFETs [12] at similar gate lengths. The scaling behavior of the GFETs published in [5] and [7] is suppressed, as indicated by the polynomial fitting lines, whereas the GFETs in this work show a promising scaling trend. At  $L_{\rm g}=0.5\,\mu{\rm m}$ , the GFETs in this work reveal higher extrinsic frequencies of  $f_{\rm T}=34\,{\rm GHz}$  and  $f_{\rm max}=$  $37\,\mathrm{GHz}$  than the GFET counterpart in [5] at  $L_\mathrm{g}=0.4\,\mu\mathrm{m}$ , which is most likely due to its larger width specific contact resistivity of 550  $\Omega\mu$ m.

The small-signal simulations, using the same model parameters used for the GFET with  $L_{\rm g}=0.5~\mu{\rm m}$ , indicate that  $f_{\rm T}$  and  $f_{\rm max}$  values of up to 100 GHz can be achieved at  $L_{\rm g}=50~{\rm nm}$ . The intrinsic value of  $f_{\rm T}$  is estimated to exceed 400 GHz which

is competing well with the best published intrinsic values of  $f_{\rm T}$  [23], [24]. To compete with the shorter-gate-length Si MOSFETs shown in Fig. 3(d-e), further optimizations are required. It follows from the analysis of (1) and (2) that further improvement of the performance can be achieved with extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  values above 100 GHz at  $L_{\rm g}=0.1\,\mu{\rm m}$  by i) increasing the saturation velocity of the charge carriers in the GFET channel, e.g., by replacing the SiO<sub>2</sub> with another dielectric material with a higher optical phonon energy, such as Al<sub>2</sub>O<sub>3</sub> or hexagonal boron nitride [4]; ii) reducing the gate oxide thickness if the condition  $C_{\rm gs}=0.5C_{\rm ox}L_{\rm g}W_{\rm g}$  applies; and iii) reducing the gate resistance, and iv) reducing the part of the contact resistance associated with the access areas. The last two approaches can be realized, for example, by applying the self-aligned T-gate technology.

#### V. CONCLUSIONS

GFETs with high extrinsic frequency values of  $f_{\rm T}=34\,{\rm GHz}$  and  $f_{\rm max}=37\,{\rm GHz}$  at  $L_{\rm g}=0.5\,\mu{\rm m}$  are presented. The GFETs also exhibit a promising scaling behavior versus gate length. The performance enhancement was achieved by minimizing the extrinsic limiting parameters by modifying the fabrication process. Analysis of the small-signal model shows that further optimization of the GFET design and fabrication will allow even better performances to be achieved with  $f_{\rm max}$  above 100 GHz for  $L_{\rm g}$  below 100 nm and will further exploit the potential of GFET transistors integrated in devices for high-frequency applications.

#### REFERENCES

- M. A. Yamoah, W. Yang, E. Pop, and D. Goldhaber-Gordon, "High-velocity saturation in graphene encapsulated by hexagonal boron nitride," ACS Nano, vol. 11, no. 10, pp. 9914–9919, Sept. 2017. DOI: 10.1021/acsnano.7b03878.

- [2] J. Chauhan, and J. Guo, "High-field transport and velocity saturation in graphene," *Appl. Phys. Lett.*, vol. 95, no. 2, 023120, Jul. 2009. DOI: 10.1063/1.3182740.

- [3] I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," *Nature Nanotechnology*, vol. 3, pp. 654–659, Sept. 2008. DOI: 10.1038/nnano.2008.268.

- [4] M. Bonmann, A. Vorobiev, M. A. Andersson, and J. Stake, "Charge carrier velocity in graphene field-effect transistors," *Appl. Phys. Lett.*, vol. 111, no. 23, 233505, Dec. 2017. DOI: 10.1063/1.5003684.

- [5] H. Lyu, Q. Lu, J. Liu, X. Wu, J. Zhang, J. Li, J. Niu, Z. Yu, H. Wu, and H. Qian, "Deep-submicron graphene field-effect transistors with state-ofart f<sub>max</sub>," Sci. Rep., vol. 6, 35717, Oct. 2016. DOI: 10.1038/srep35717.

- [6] J. S. Moon, H.-C. Seo, M. Antcliffe, D. Le, C. McGuire, A. Schmitz, L. O. Nyakiti, D. K. Gaskill, P. M. Campbell, K.-M. Lee, and P. Asbeck, "Graphene FETs for Zero-Bias Linear Resistive FET Mixers," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 465–467, Mar. 2013. DOI: 10.1109/LED.2012.2236533.

- [7] E. Guerriero, P. Pedrinazzi, A. Mansouri, O. Habibpour, M. Winters, N. Rorsman, A. Behnam, E. A. Carrion, A. Pesquera, A. Centeno, A. Zurutza, E. Pop, H. Zirath, and R. Sordan, "High-gain graphene transistors with a thin AlO<sub>x</sub> top-gate oxide," *Sci. Rep.*, vol. 7, 2419, May. 2017. DOI: 10.1038/s41598-017-02541-2.

- [8] I. Meric, C. R. Dean, S.-J. Han, L. Wang, K. A. Jenkins, J. Hone, K. L. Shepard, "High-frequency performance of graphene field effect transistors with saturating IV-characteristics," in *Proc. IEDM 2011*, Washington, DC, USA, 2011. DOI: 10.1109/IEDM.2011.6131472.

- [9] C. Yu, Z. Z. He, Q. B. Liu, X. B. Song, T. T. Han, J. Li, Z. H. Feng, and S. J. Cai, "Graphene Amplifier MMIC on SiC Substrate," *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 684–687, Jun. 2016. DOI: 10.1109/LED.2016.2544938.

- [10] Z. Guo, R. Dong, P. S. Chakraborty, N. Lourenco, J. Palmer, Y. Hu, M. Ruan, J. Hankinson, J. Kunc, J. D. Cressler, C. Berger, and W. A. de Heer, "Record Maximum Oscillation Frequency in C-Face Epitaxial Graphene Transistors," *Nano Lett.*, vol. 13, no. 3, pp. 942–947, Feb. 2013. DOI: 10.1021/nl303587r.

- [11] C. Raynaud, O. Faynot, J.-L. Pelloie, C. Tabone, A. Grouillet, F. Martin, G. Dambrine, M. Vanmackelberg, L. Picheta, E. Mackowiak, H. Brut, P. Llinares, J. Sevenhans, E. Compagne, G. Fletcher, D. Flandre, V. Dessard, D. Vanhoenacker, and J.-P. Raskin, "70 GHz f<sub>max</sub> fully-depleted SOI MOSFET's for low-power wireless applications," in *GAAS* 2000, Paris, France, Oct. 2000. DOI: 10.6092/unibo/amsacta/207.

- [12] R. A. Johnson, P. R. de la Houssaye, C. E. Chang, P.-F. Chen, M. E. Wood, G. A. Garcia, I. Lagnado, and P. M. Asbeck, "Advanced thin-film silicon-on-sapphire technology: Microwave circuit applications," *IEEE Trans. Electron Devices*, vol. 45, no. 5, pp. 1047–1054, May 1998. DOI: 10.1109/16.669525.

- [13] P. R. de la Houssaye, C. E. Chang, B. Offord, G. Imthurn, R. Johnson, P. M. Asbeck, G. A. Garcia, and I. Lagnado, "Microwave performance of optically fabricated T-gate thin film silicon-on-sapphire based MOS-FET's," *IEEE Electron Device Lett.*, vol. 16, no. 6, pp. 289–292, Jun. 1995. DOI: 10.1109/55.790738.

- [14] M. Tanzid, M. A. Andersson, J. Sun, and J. Stake, "Microwave noise characterization of graphene field effect transistors," *App. Phys. Lett.*, vol. 104, no. 1, 013502, Jan. 2014. DOI: 10.1063/1.4861115.

- [15] S. Mason, "Power Gain in Feedback Amplifier," IEEE Trans. of the IRE Professional Group on Circuit Theory, vol. CT-1, no. 2, pp. 20–25, June 1954. DOI: 10.1109/TCT.1954.1083579.

- [16] M. S. Gupta, "Power gain in feedback amplifiers, a classic revisited," IEEE Trans. Microw. Theory Tech., vol. 40, no. 5, pp. 864–879, May 1992. DOI: 10.1109/22.137392.

- [17] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, "Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," *Appl. Phys. Lett.*, vol. 94, no. 6, 062107, Feb. 2009. DOI: 10.1063/1.3077021.

- [18] P. Scharma, L. S. Bernard, A. Bazigos, A. Magrez, and A. M. Ionescu, "Room-Temperature Negative Differential Resistance in Graphene Field Effect Transistors: Experiments and Theory," ACS Nano, vol. 9, no. 1, pp. 620–625, Dec. 2015. DOI: 10.1021/nn5059437.

- [19] G. Gonzales, "Microwave transistor amplifiers: analysis and design," Pearson, 2nd ed. 1996.

- [20] K. Numilla, A. A. Ketterson, and I. Adesida, "Delay time analysis for short gate-length GaAs MESFETs," *Solid-Sate Electronics*, vol. 38, no. 2, pp. 517–524, Feb. 1995. DOI: 0.1016/0038-1101(94)00097-Y.

- [21] S. M. Sze, and K. K. Ng, "Physics of semiconductor devices," New Jersey: Wiley, 2007.

- [22] L. F. Tiemeijer, H. Boots, R. L. Havens, A. J. Scholten, P. H. W. de Vreede, A. Heringa, and D. B. M. Klaassen, "A record high 150 GHz f<sub>max</sub> realized at 0.18 μm gate length in an industrial RF-CMOS technology," in *International Electron Devices Meeting*. *Technical Dig. (Cat. No.01CH37224)*, Washington, DC, USA, 2001. DOI: 10.1109/IEDM.2001.979471.

- [23] L. Liao, Y.-C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K. L. Wang, Y. Huang, and X. Duan, "High-speed graphene transistors with a selfaligned nanowire gate," *Nature*, vol. 467, pp. 305–308, Sept. 2010. DOI: 10.1038/nature09405.

- [24] R. Cheng, J. Bai, L. Liao, H. Zhou, Y. Chen, L. Liu, Y.-C. Lin, S. Jiang, Y. Huang, and X. Duan, "High-frequency self-aligned graphene transistors with transferred gate stacks," *PNAS*, vol. 109, no. 29, pp. 11588–11592, Jul. 2012. DOI: 10.1073/pnas.1205696109.