## Toward CMOS compatible wafer-scale fabrication of carbon-based microsupercapacitors for IoT

Downloaded from: https://research.chalmers.se, 2024-04-20 15:29 UTC

Citation for the original published paper (version of record):

Smith, A., Li, Q., Anderson, A. et al (2018). Toward CMOS compatible wafer-scale fabrication of carbon-based microsupercapacitors for IoT. Journal of Physics: Conference Series, 1052(1). http://dx.doi.org/10.1088/1742-6596/1052/1/012143

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

#### **PAPER • OPEN ACCESS**

# Toward CMOS compatible wafer-scale fabrication of carbon-based microsupercapacitors for IoT

To cite this article: A D Smith et al 2018 J. Phys.: Conf. Ser. 1052 012143

View the article online for updates and enhancements.

#### **Related content**

- <u>High-energy-density, all-solid-state</u> <u>microsupercapacitors with three-</u> <u>dimensional interdigital electrodes of</u> <u>carbon/polymer electrolyte composite</u> Juan Pu, Xiaohong Wang, Tianyi Zhang et al.

- <u>Gravure printed interdigital</u> microsupercapacitors on a flexible polyimide substrate using crumpled graphene ink Qi Zhang, Lei Huang, Quanhong Chang et al.

- Printed all-solid flexible microsupercapacitors: towards the general route for high energy storage devices Ye Wang, Yumeng Shi, Cheng Xi Zhao et al.

### IOP ebooks<sup>™</sup>

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

### **Toward CMOS compatible wafer-scale fabrication of carbon**based microsupercapacitors for IoT

#### A D Smith<sup>1</sup>, Q Li<sup>1</sup>, A Anderson<sup>2</sup>, A Vyas<sup>1</sup>, V Kuzmenko<sup>1</sup>, M Haque<sup>1</sup>, L G H Staaf<sup>1</sup>, P Lundgren<sup>1</sup> and P Enoksson<sup>1</sup>

<sup>1</sup> Chalmers University of Technology, Kemivägen 9, Göteborg 41258, Sweden <sup>2</sup> University of Santa Barbara, Santa Barbara, CA 93106, USA

E-mail: smdavid@chalmers.se

Abstract. This work presents a wafer-scale method of microsupercapacitor (MSC) fabrication. Deposition of the electrode precursor, i.e. graphene oxide, is accomplished through spin-coating which allows for potential application in CMOS compatible processes for future integrated onchip energy storage systems. Our MSCs have an areal capacitance of  $0.4 \text{ mF/cm}^2$  at  $10 \mu A$ , which is a very promising result. Further, the MSC has good rate capability as its capacitance decreases by only 0.03 mF/cm<sup>2</sup> when the current increases to 50  $\mu$ A. The MSCs have a maximum energy density of 0.04  $\mu$ Wh/cm<sup>2</sup> and a maximum power density as high as 96  $\mu$ W/cm<sup>2</sup>. Additionally, the wafer-scale process demonstrates industrial viability.

#### 1. Introduction

As microsystems shrink and become increasingly integrated (Internet of Things (IoT)), they have ever increasing power demands and can therefore greatly benefit from on-chip power supply and management systems. Microsupercapacitors (MSCs), combined with energy harvesting, offer the potential to alleviate these increasing power demands [1]-[6]. However, implementation of reliable wafer scalable and fully CMOS compatible MSC fabrication processes remains challenging. In this work, we present a novel, CMOS compatible fabrication method for development of wafer scalable MSC technology using rGO electrodes. This method has a potential to be incorporated back-end-of-theline (BEOL) with other microsystems and many other carbon-based materials (such as, carbon nanotubes (CNTs), activated carbon (AC) and carbon nanofibers (CNFs)). These carbon materials show promising electrical characteristics as well as high surface to volume ratios – making them well-suited as MSC electrodes [7].

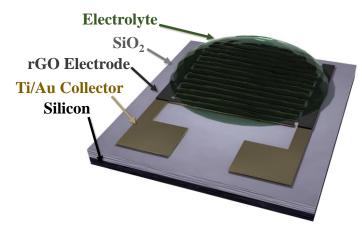

The MSC devices are comprised of metal current collectors. On top of these current collectors, GO is spin-coated and selectively etched to form positive and negative high surface area electrodes. GO is converted to rGO after annealing at high temperature. The porous nature of the rGO allows for the electrolyte to penetrate into the electrode and form a double layer capacitance at the electrode/electrolyte interface. Consequently, rGO offers tremendous capacitive properties due to its high surface area. A schematic of a typical MSC device fabricated in a wafer-scale process is shown in figure 1 with the silicon/SiO<sub>2</sub> substrate in black/grey, the current collectors in gold, the rGO in dark grey, and the electrolyte in green.

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. Published under licence by IOP Publishing Ltd 1

Figure 1. Graphical representation of a generic carbon-based MSC with interdigitated electrodes.

#### 2. Device Fabrication

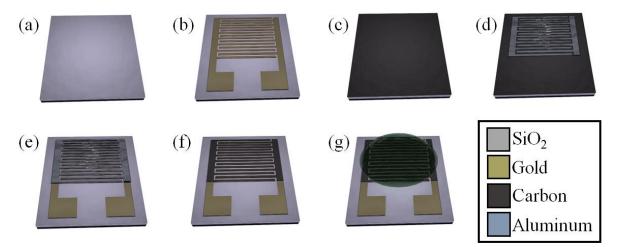

The wafer-scale fabrication procedure for MSCs is shown in Figure 2. A 2" silicon wafer with 400 nm of SiO<sub>2</sub> is employed as the substrate (figure 2a). Interdigitated Ti/Au (10/50 nm) current collectors are fabricated using metal evaporation and lift-off (figure 2b). Although gold is used for proof of concept, it can be replaced with CMOS compatible metals. Next, Graphene oxide (GO) is spin-coated (figure 2c). A 50 nm aluminum layer is then deposited and patterned to form a hard mask (figure 2d). This hard mask protects the GO electrode material during oxygen plasma etching at 100 W in a 100 mTorr (figure 2e). Aluminum is then etched away and GO is reduced (figure 2f) for 20 mins at 500 °C with hydrogen used as a reductant.

Figure 2. Schematic process plan for a ubiquitous carbon-based MSC.

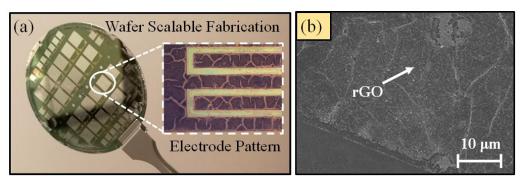

Figure 3a displays rGO-based MSCs fabricated on a 2" silicon wafer (fabricated to step (e) in figure 2) where the inset presents an optical microscopy image of the interdigitated contact pattern – illustrating a very good etch profile from the Aluminum hard mask. Likewise, scanning electron microscopy (SEM) further confirms the presence of rGO (figure 3b).

**Figure 3**. (a) Full size 2" wafer after graphene oxide etch, (inset) rGO interdigitated pattern post GO reduction. (b) SEM image rGO electrode after complete processing.

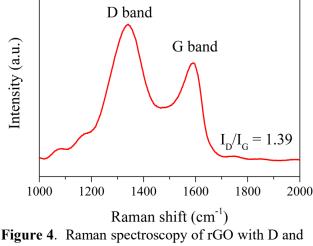

To evaluate the successful reduction of GO to rGO, Raman spectroscopy measurement was performed. The Raman spectrum of the material after the reduction process shows two major features, the G band due to  $E_{2g}$  symmetry of sp<sup>2</sup> carbon at 1587 cm<sup>-1</sup> and the D band corresponding to breathing mode of  $A_{1g}$  symmetry at 1338 cm<sup>-1</sup>. The intensity ratio of D to G band ( $I_D/I_G$ ) is 1.39, similar to a previous report on rGO [8]. Finally, 6 M KOH electrolyte is applied onto the device (figure 2g). Although KOH is used for initial measurements, it can be replaced by a gel-based electrolyte (e.g. polyvinyl alcohol based electrolyte PVA/H<sub>3</sub>PO<sub>4</sub>) for CMOS compatibility.

G bands. rGO is suggested by the intensity ratio of the two bands.

#### 3. Results/Discussion

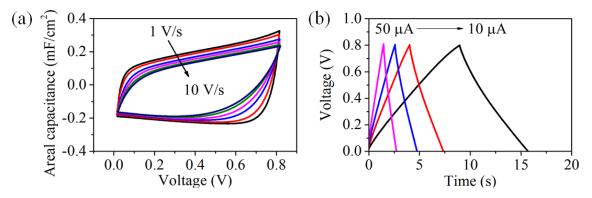

The electrochemical performance of the MSC is evaluated on Kari Suss PM 5 probe station coupled with Gamry Reference 3000AE potentiostat. Cyclic Voltammetry (CV) at scan rates of 1 - 10 V/s (figure 5a) show quasi-rectangular curves that indicate electric double layer (EDL) behavior dominates the storage mechanism, which is further evidenced by the linear Galvanostatic Charge/Discharge (GCD) curves at a current of 10, 20, 30 and 50  $\mu$ A (figure 5b).

The following equations are applied for the calculation of capacitance:  $C = I \cdot t / S \cdot \Delta V$ , where *C* is the areal capacitance, *I* is the charge/discharge current, S is surface area of the device including the space between fingers and  $\Delta V$  is the voltage range during discharge excluding IR drop. The energy density can be further calculated by  $E = \frac{1}{2} C \cdot \Delta V^2$ , where *E* stands for energy density, and average power density by P = E / t. The calculation shows that the MSC has an areal capacitance of 0.4 mF/cm<sup>2</sup> at 10 µA. The value is comparable to 0.51 mF/cm<sup>2</sup> of a rGO based MSC fabricated by laser writing method [9]. The areal capacitance can be easily controlled by increase the thickness of active material layer by repeating

the spin-coating step. The device also has excellent rate capability that capacitance drops by only approx. 0.3 mF/cm<sup>2</sup> when the current increases 5 times to 50  $\mu$ A. The maximum energy of the device is around 0.04  $\mu$ Wh/cm<sup>2</sup> while the maximum power is as high as 96  $\mu$ W/cm<sup>2</sup>.

Figure 5. (a) Cyclic voltammetry, (b) Galvanostatic charge/discharge.

Although measurements for rGO are presented, the fabrication method is ubiquitously transferrable to other carbon materials. Due to the robust nature of the fabrication process, there is much room for performance enhancement with the resulting MSCs potentially being implemented on-chip with other microsystem technologies for future development of self-powering microsystems.

#### 4. Conclusion

We present a MSC fabrication method which uses rGO as an electrode material. Deposition of rGO is accomplished through spin-coating and therefore offers potential CMOS compatibility. The process is scalable to wafer-scale sizes which allows for potential industrial viability. Our MSCs currently have an areal capacitance of 0.4 mF/cm<sup>2</sup> at 10  $\mu$ A which is comparable to previous reports. Further, the MSC capacitance decreases by only approx. 0.03 mF/cm<sup>2</sup> when the current increases to 50  $\mu$ A. The MSCs have a maximum energy density of approximately 0.04  $\mu$ Wh/cm<sup>2</sup> and a maximum power density as high as 96  $\mu$ W/cm<sup>2</sup>. The MSC fabrication method aims toward potential future application involving on-chip energy storage systems.

#### References

- [1] Yun J, Kim D, Lee G, and Ha J S, 2014 Carbon, 79 pp 156–164

- [2] Wang S, Hsia B, Carraro C, and Maboudian R 2014 J. Mater. Chem. A 2 7997–8002

- [3] Meng Q, Wu H, Meng Y, Xie K, Wei Z, and Guo Z 2014 Adv. Mater 26 4100-6

- [4] Yang Y, He L, Tang C, Hu P, Hong X, Yan M, Dong Y, Tian X, Wei Q, and Mai L 2016 Nano Res 9 2510–19

- [5] Wu Z-S, Feng X, and Cheng H-M 2014 Natl. Sci. Rev. 1 277–92

- [6] Zhai Y, Dou Y, Zhao D, Fulvio P F, Mayes R T, and Dai S 2011 Adv. Mater. 23 4828–50

- [7] Staaf L G H, Lundgren P, and Enoksson P 2014 Nano Energy 9 128-41

- [8] Das A K, Srivastav M, Layek R K, Uddin M E, Jung D, Kim N H, and Lee J H 2014 J. Mater. Chem. A 2 1332-40

- [9] Gao W, Singh N, Song L, Liu Z, A L M Reddy, Ci L, Vajtai R, Zhang Q, Wei B and Ajayan P M, Nat. Nanotechnol. 6 496-500