## Effects of self-heating on high-frequency performance of graphene field-effect transistors

Marlene Bonmann<sup>1</sup>, Marijana Krivic<sup>1</sup>, Muhammad Asad<sup>1</sup>, Xinxin Yang<sup>1</sup>, Andrei Vorobiev<sup>1</sup>, Jan Stake<sup>1</sup>, Luca Banszerus<sup>2</sup>, Christoph Stampfer<sup>2</sup>, Martin Otto<sup>3</sup>, Daniel Neumaier<sup>3</sup>

<sup>1</sup>Terahertz and Millimetre Wave Laboratory, Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296 Gothenburg, Sweden, <sup>2</sup>2<sup>nd</sup> Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany, <sup>3</sup>Advanced Microelectronic Center Aachen, AMO GmbH, 52074, Aachen, Germany

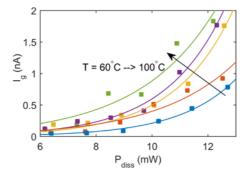

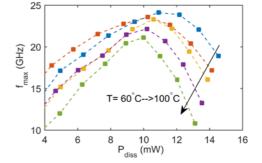

In this work, we study the effects of self-heating (Joule heating) on the performance of graphene field-effect transistors (GFETs) with high extrinsic transit frequency ( $f_1$ ) and maximum frequency of oscillation ( $f_{max}$ ) [1]. It has been shown, that self-heating in the GFETs might be significant and lead to degradation of the output characteristics with potential effects on the  $f_1$  and  $f_{max}$  [2,3,4]. Due to relatively short gate length of 0.5 µm in the GFETs, used in this work, the local channel temperature cannot be accurately estimated by means of the infrared microscopy. Therefore, we applied the method of thermosensitive electrical parameters [5]. In particular, we analysed the gate and drain currents in response to variations of the external heater temperature and dc power (Fig. 1). The analysis allows for estimation of the thermal resistance, which is, for GFETs on SiO<sub>2</sub>/Si substrates, approx.  $2 \cdot 10^4$  K/W, and in good agreement with that calculated by the model based on the solution of Laplace's equation [6]. In turn, the known thermal resistance allows for evaluation of the GFET channel self-heating temperature. Fig. 2 shows the  $f_{max}$  versus dc power ( $P_{diss}$ ) at different external heater temperatures. The self-heating temperature at  $P_{diss}$  can be fully explained by self-heating. Apparently, one can expect reduced self-heating effects in the GFETs on higher thermal conductive substrates as hBN or SiC.

Fig. 1. The gate current,  $I_{\rm g}$ , vs dc power,  $P_{\rm diss}$ , of GFETs on SiO<sub>2</sub>/Si substrates at different external heater temperatures in the range 60-100 °C and gate voltage  $V_{\rm g} = 0.5$  V.

Fig. 2. The measured (extrinsic) maximum frequency of oscillation,  $f_{\text{max}}$ , vs dc power,  $P_{\text{diss}}$ , of GFETs on SiO<sub>2</sub>/Si substrates at different external heater temperatures in the range 60-100 °C and gate voltage  $V_{\text{g}} = -1 \text{ V}$ .

## References

- [1] M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier, and J. Stake, IEEE Electron Device Lett., 40, 131 (2019).

- [2] M.-H. Bae, S. Islam, V. E. Dorgan, and E. Pop, ACSNano, 5 (10), (2011).

- [3] S. Islam, Z. Li, V. E. Dorgan, M.-H. Bae, and E. Pop, IEEE Electron Device Lett., 34 (2), (2013).

- [4] F. Schwierz, Proceedings of the IEEE, 101 (7), 1567 (2013).

- [5] L. Dupont, Y. Avenas, and P.-O. Jeannin, IEEE T. Ind. Appl., 40 (4), (2013).

- [6] A. Darwish, A. J. Bayba, and H. A. Hung, IEEE T Electron Dev., 62 (3), (2015).