THESIS FOR THE DEGREE OF LICENTIATE OF ENGINEERING

# Towards an on-chip power supply

### Integration of micro energy harvesting and storage techniques for wireless sensor networks

Agin Vyas

Department of Microtechnology and Nanoscience (MC2) CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2019 Towards an on-chip power supply Integration of micro energy harvesting and storage techniques for wireless sensor networks AGIN VYAS

© AGIN VYAS, 2019.

Licentiatavhandlingar vid Chalmers tekniska högskola Technical report No. 427 ISSN 1652-0769

Department of Microtechnology and Nanoscience (MC2) Chalmers University of Technology SE–412 96 Göteborg, Sweden Telephone + 46 (0) 31 772 1000

Printed by Chalmers Reproservice Göteborg, Sweden 2019

one step closer...

# Abstract

The lifetime of a power supply in a sensor node of a wireless sensor network is the decisive factor in the longevity of the system. Traditional Li-ion batteries cannot fulfill the demands of sensor networks that require a long operational duration. Thus, we require a solution that produces its own electricity from its surrounding and stores it for future utility. Moreover, as the sensor node architecture is developed on complimentary metal-oxide-semiconductor technology (CMOS), the manufacture of the power supply must be compatible with it. In this thesis, we shall describe the components of an onchip lifetime power supply that can harvest the vibrational mechanical energy through piezoelectric microcantilevers and store it in a reduced graphene oxide (rGO) based microsupercapacitor, and that is fabricated through CMOS compatible techniques. Our piezoelectric microcantilevers confirm the feasibility of fabricating micro electromechanical-systems (MEMS) size two-degree-of-freedom systems which can solve the major issue of small bandwidth of piezoelectric micro-energy harvesters. These devices use a cut-out trapezoidal cantilever beam to enhance the stress on the cantilever's free end while reducing the gap remarkably between its first two eigenfrequencies in 400 -500 Hz and 1 - 2 kHz range. The energy from the M-shaped harvesters will be stored in rGO based microsupercapacitors. These microsupercapacitors are manufactured through a fully CMOS compatible, reproducible, and reliable micromachining processes. Furthermore, we have also demonstrated an improvement in their electrochemical performance and yield of fabrication through surface roughening from iron nanoparticles. We have also examined the possibility of integrating these devices into a power management unit to fully realize a lifetime power supply for wireless sensor networks.

**Keywords:** MEMS, CMOS compatible, Piezoelectric energy harvester, Microsupercapacitor, On-chip power supply.

# Acknowledgments

First and foremost, I wish to thank Prof. Peter Enoksson for taking me as an intern student all those years ago. His supervision and easy-to-approach attitude during severe periods of this work have guided me in becoming a better scientist and an engineer.

Next, I wish to express my deepest appreciation towards Prof. Per Lundgren. Without his guidance in projects, formulating plans, and assessing data, "Moreover", I thoroughly revel in answering his remarks and outlooks in a manuscript as you need things in life that are the Per-Standard.

My daily supervisor, Dr. Anderson Smith, who helped me in understanding the elements of the writing process, advising me on designing methodologies, and speed writing. Special thanks to Dr. Volodymyr Kuzmenko, who helped me in understanding the academic world and insights on world situations made me reflect on my understanding of the subjects. Also, a mention of gratefulness to Dr. Henrik Staaf to undertake me as a master's student and Dr. Sofia Rahiminejad, who introduced me to the cleanroom and inspired me to undertake the EMM-Nano route.

I wish to acknowledge my group members and friends - Qi, Mazharul, Elof, and Sadia, who are also passengers on this Ph.D. boat; the colleagues and friends I have made along the way - Steven, Michael, Wim, Adriana, Ankit, Ankur, and Apoorv who have been a constant places for motivation in sometimes a stressful and mundane life.

Finally there is no way that I can thank my family enough. Without your love, affection and support, I do not think I would have survived this long in this strange, huge, and perilous world.

Agin Vyas Göteborg, November 2019

# **List of Publications**

This thesis is based on the following appended papers:

- Paper 1. Agin Vyas, H. Staaf, C. Rusu, T. Ebefors, J. Liljeholm, A. D. Smith, P. Lundgren and P. Enoksson. A Micromachined Coupled Cantilever for Piezoelectric Energy Harvesters. Micromachines (ISSN 2072-6669), no. 5 (2018): 252.

- Paper 2. Agin Vyas, Q. Li, F. Cornaglia, K. Wang, A. Anderson, M. Haque, V. Kuzmenko, A. D. Smith, P. Lundgren, P. Enoksson. Surface Roughening with Iron Nanoparticles for Promoted Adhesion of Spin Coated Microsupercapacitor Electrodes. MRS Advances 4, no. 23 (2019): 1335-1340.

- Paper 3. Agin Vyas, K. Wang, A. Anderson, A. Velasco, R. Van den Eeckhoudt, M. Haque, Q. Li, A. D. Smith, P. Lundgren, P. Enoksson. Enhanced electrode deposition for on-chip integrated micro-supercapacitors by controlled surface roughening. Submitted

Other relevant contributions co-authored by Agin Vyas:

- A. D. Smith, Q. Li, Agin Vyas, M. Haque, K. Wang, A. Velasco, X. Zhang, S. Thurakkal, A. Quellmalz, F. Niklaus, K. Gylfason, P. Lundgren, P. Enoksson. Carbon-Based Electrode Materials for Microsupercapacitors in Self-Powering Sensor Networks: Present and Future Development, Sensors 19.19 (2019): 4231.

- A. D. Smith, Q. Li, A Anderson, Agin Vyas, V Kuzmenko, M Haque, L. G. H. Staaf, P. Lundgren, P. Enoksson, *Toward CMOS compatible wafer-scale fabrication of carbon based microsupercapacitors for IoT*, IOP Conference Series: Journal of Physics: Conference Series 1052 (2018) 012143.

- Agin Vyas, F. Cornaglia, T. Rattanasawatesun, Q. Li, M. Haque, J. Sun, V. Kuzmenko, A. D. Smith, P. Lundgren, P. Enoksson. *Investigation of Palladium Current Collectors for Vertical Graphene-based Microsupercapacitors*, Journal of Physics: Conference Series. Vol. 1319. No. 1. IOP Publishing, 2019.

- Q. Li, A. D. Smith, M. Haque, Agin Vyas, V. Kuzmenko, P. Lundgren, P. Enoksson. Graphite paper/carbon nanotube composite: A potential supercapacitor electrode for powering microsystem technology, Journal of Physics: Conference Series, 922 (2017) 012014

- Q. Li, A. D. Smith, Agin Vyas, F. Cornaglia, A. Anderson, M. Haque, V. Kuzmenko, E. Kohler, P. Enoksson. *Giving micro-supercapacitor fingers?*, 29th Micromechanics and Microsystems Europe workshop 2018, August 26-29, Bratislava, Slovakia.

- A. Velasco, Agin Vyas, K. Wang, Q. Li, A. D. Smith, P. Lundgren, P. Enoksson. *Investigation of vertical carbon nanosheet growth and its potential for microsupercapacitors*, 30th Micromechanics and Microsystems Europe workshop 2018, August 18-21, Oxford, United Kingdom.

- R. Van den Eeckhoudt, Agin Vyas, E. Karabulut, G. Gereb, P. Gatenholm, P. Lundgren, C. Rusu and P. Enoksson. *Flexible and robust design for acoustic and vibrational energy harvesting*, 30th Micromechanics and Microsystems Europe workshop 2018, August 18-21, Oxford, United Kingdom.

- Agin Vyas, R. van den Eeckhoudt, Q. Li, G. Geréb, A. Smith, C. Rusu, P. Lundgren, P. Enoksson. *Integrated Flexible Energy Harvester and Supercapacitor for Selfpowered Textile Sensors*, PowerMEMS 2019, December 2-6, 2019, Kraków, Poland.

# List of Acronyms

| T-T    |   | Laterna et a f mlain an                           |

|--------|---|---------------------------------------------------|

| IoT    | - | Internet-of-Things                                |

| WSN    | _ | wireless sensor network                           |

| CMOS   | - | Complimentary metal-oxide-semiconductor           |

| PEH    | - | Piezoelectric energy harvester                    |

| MEMS   | _ | Micro electro-mechanical-systems                  |

| VLSI   | - | Very large scale integration                      |

| MOSFET | - | Metal oxide semiconductor field effect transistor |

| MKS    | _ | Mass spring damper                                |

| MSC    | _ | Microsupercapacitor                               |

| IC     | _ | Integrated circuit                                |

| LDV    | _ | Laser doppler vibrometer                          |

| SOI    | _ | Silicon-on-Insulator                              |

| DRIE   | _ | Deep reactive ion etching                         |

| PZT    | _ | Lead Zironate Titanate                            |

| GO     | _ | Graphene oxide                                    |

| rGO    | _ | reduced graphene oxide                            |

| CAD    | _ | Computer Aided Design                             |

| CNF    | _ | Carbon nanofiber                                  |

| CNT    | _ | Carbon nanotube                                   |

| VACNS  | _ | Vertically aligned carbon nanosheets              |

| CV     | _ | Cyclic voltammetry                                |

| GCD    | _ | Galvanic charge discharge                         |

| PMU    | _ | Power management unit                             |

| D2W    | _ | Die to wafer                                      |

| W2W    | _ | Wafer to wafer                                    |

|        |   |                                                   |

# Contents

| Ał | ostra   | ct                                                | v                                                                                                                                                                                |

|----|---------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ac | knov    | vledgments vi                                     | ii                                                                                                                                                                               |

| Li | st of   | Publications i                                    | X                                                                                                                                                                                |

| Li | st of . | Acronyms x                                        | ge       3         ng       4         mpatibility       4         thesis       6 <b>ro-energy Harvester</b> 7         1       7         degree of freedom (2DOF) design       13 |

| 1  | Intr    | oduction                                          | 1                                                                                                                                                                                |

|    | 1.1     | Energy harvesting                                 | 3                                                                                                                                                                                |

|    | 1.2     | Energy storage                                    | 3                                                                                                                                                                                |

|    | 1.3     | Manufacturing                                     | 4                                                                                                                                                                                |

|    |         | 1.3.1 IC-compatibility                            | 4                                                                                                                                                                                |

|    | 1.4     | Scope of the thesis                               | 6                                                                                                                                                                                |

| 2  | Piez    | zoelectric Micro-energy Harvester                 | 7                                                                                                                                                                                |

|    | 2.1     | Introduction                                      | 7                                                                                                                                                                                |

|    |         | 2.1.1 Two-degree of freedom (2DOF) design         | 3                                                                                                                                                                                |

|    | 2.2     | Simulations                                       | 5                                                                                                                                                                                |

|    |         | 2.2.1 Design                                      | 5                                                                                                                                                                                |

|    |         | 2.2.2 Results                                     | 6                                                                                                                                                                                |

|    | 2.3     | Fabrication                                       | 8                                                                                                                                                                                |

|    |         | 2.3.1 Process plan                                | 8                                                                                                                                                                                |

|    |         | 2.3.2 Issues in fabrication                       | 9                                                                                                                                                                                |

|    | 2.4     | Results and discussion                            | 0                                                                                                                                                                                |

| 3  | Mic     | rosupercapacitors (MSCs) 2                        | 3                                                                                                                                                                                |

|    | 3.1     | Device design                                     | 5                                                                                                                                                                                |

|    |         | 3.1.1 Laser scribing                              | 6                                                                                                                                                                                |

|    |         | 3.1.2 Ink-jet printing                            | 7                                                                                                                                                                                |

|    |         | 3.1.3 Photolithography                            | 7                                                                                                                                                                                |

|    |         | 3.1.4 Chemical vapor deposition                   | 9                                                                                                                                                                                |

|    | 3.2     | Material selection                                | 9                                                                                                                                                                                |

|    | 3.3     | Fabrication                                       | 1                                                                                                                                                                                |

|    |         | 3.3.1 Oxidation and current collector fabrication | 1                                                                                                                                                                                |

|    |         | 3.3.2 Electrode deposition                        |                                                                                                                                                                                  |

|    |         | 3.3.3 Al hard masking                             | 3                                                                                                                                                                                |

|    |       | 3.3.4 Electrode etching                                                                                    | 34 |

|----|-------|------------------------------------------------------------------------------------------------------------|----|

|    |       | 3.3.5 Annealing                                                                                            | 34 |

|    | 3.4   | Issues in fabrication                                                                                      | 35 |

|    | 3.5   | Electrochemical results                                                                                    | 35 |

|    | 3.6   | Surface optimization for effective spin coating                                                            | 36 |

|    |       | 3.6.1 Surface enhancement study                                                                            | 38 |

| 4  |       | chip integration                                                                                           | 41 |

|    | 4.1   | Circuit design                                                                                             | 41 |

|    | 4.2   | Integration possibilities                                                                                  | 43 |

| 5  | Con   | clusion                                                                                                    | 47 |

| Bi | bliog | raphy                                                                                                      | 49 |

| I  | Ap    | pended papers                                                                                              | 59 |

| 1  | AM    | icromachined Coupled Cantilever for Piezoelectric Energy Harvesters                                        | 61 |

| 2  |       | ace Roughening with Iron Nanoparticles for Promoted Adhesion of Spin<br>ted Microsupercapacitor Electrodes | 79 |

| 3  |       | anced electrode deposition for on-chip integrated micro-supercapacitors ontrolled surface roughening       | 89 |

# Chapter 1 Introduction

A new era of computing technology is developing called the Internet of Things (IoT). It envisions a technology where there is an interaction between machines and infrastructure. Smart devices connected devices over a cloud computing-based infrastructure will encompass several aspects of our lives [1]. The groundwork of this platform is laid by the interaction of microsystems in machines, objects, environments, and infrastructure to collect and analyze data accrued by such systems. With the collection and processing of this data, we can command and control things to make our lives much more comfortable and safer. These devices would make the simple household technologies more energy efficient [2]. Integration of such a lifetime power supply into an IoT platform would lead to some efficiency in the overall sustainable development [3].

When these microsystems combine to interact with each other, they form a wireless sensor network (WSN) with them acting as nodes of an information circuit. The research on these microsystems has blown up since the advancement in micro-electromechanical systems (MEMS) technology [4, 5, 6, 7]. MEMS technology has enabled the development of microsystems at a low cost with an even lower power requirement than before. WSNs can influence all sectors of life with application areas ranging from health, military and security to agriculture, mining, and deep-sea exploration. For example, a doctor can monitor a patient's information remotely through sensing his physiological data while allowing a better understanding of the patient's condition. Sensor networks can detect chemical agents in air and water, which can lead to the identification of their types, concentration, and location that can lead to an early alarm. WSNs on rail tracks with strong vibrations can detect faults in the tracks, wheels, or the surroundings. Essentially, these sensor networks will provide a user with better information and intelligence of the surrounding [8].

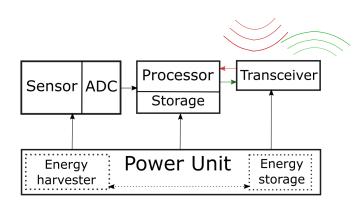

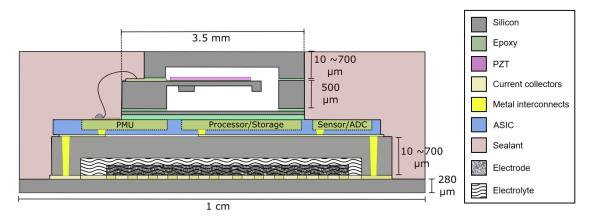

A sensor node is a composition of four units, as shown in Figure 1.1. They are transceiver, processing unit, sensor unit, and the power unit. Sensor nodes interact and communicate with each other wirelessly through a unit called transceiver. A transceiver is a combination of a transmitter that sends the signal and a receiver that accepts the signal. The transceiver is connected to a processing unit that comprises a processor and storage. A processor performs the basic arithmetic, I/O operations, and logic operations alongside allocating commands for the different components running in the system. The storage saves the information in the form of bits for future use. The processing

Figure 1.1: Components of a wireless sensor node.

unit is also connected to the sensing unit. The sensing unit is made up of a sensor and a unit that converts analog signals into digital called the analog-digital-converter (ADC). The sensor senses the physical information of its surrounding like temperature, vibrations, chemical concentration, light, humidity in the form of an electric current or a potential ( $\Delta V$ ) in most cases. The ADC's function is a translator of the sensor's information to the processor from analog to digital. The acquired digital information is stored and processed in the processing unit. The power unit powers all three subunits of the microsystem. There can be other subunits, too depending on the type of application.

There are several restrictions on the sensor node in order to be fully compatible with a WSN deployment. First, they must be small, sometimes as small as a cubic centimeter [9] (and be light enough at the same time). Secondly, they need to be consuming low power. Thirdly, they require low production costs, and finally, as these sensor nodes are to be used in often inaccessible places, the lifetime of these devices must be long. Having a large power unit and being small are two conditions that contradict each other. The wireless sensor node, being a microelectronic device, can only be equipped with a limited power source (< 0.5 Ah, 1.2 V) [8]. In some application scenarios, replenishment of power resources might be impossible. Sensor node lifetime, therefore, shows a strong dependence on battery lifetime. Currently, these sensors are powered by typical Li coin cells that we use in analog watches. These batteries are traditionally created of an electrode from earth metal and an electrolyte of an acidic solution and have a maximum lifetime of 3-5 years. Once they stop functioning, they need to be dumped somewhere in the environment as these batteries as not recyclable. Disposal of these systems has an immensely negative impact on the environment. The toxic acidic nature of the electrolyte, when dumped, poses a significant threat to our ecological dimension of soil, water, and air. The acidic batteries disposed on the ground can reduce the agricultural output [10]. Moreover, usage of earth metals deplete the finite resources of the ecosystem's economic capital [11]. Burning them would lead to a release of toxic waste gases[12]. With growing concerns with climate change, it is imperative to devise solutions that not only extend the lifetime of these sensors but are also environmental friendly.

It is possible to extend the lifetime of these devices using units of energy harvesting and energy storage. Energy harvesting is the process of extracting energy present in the environment in the form of solar, wind, thermal, or vibrational energy and convert it into usable electrical energy [13]. These sources of energy will never deplete as long as the earth is rotating and revolving around the sun. Energy storage units are devices that can store this electrical energy in the form of charge and then supply it to the system when needed [14]. The power consumption of these devices is based on the microelectronics for data processing, sensing, and communication. Since the microelectronic devices are fabricated through complimentary metal-oxide-semiconductor (CMOS) technology, the power unit's fabrication process must be compatible with it.

### 1.1 Energy harvesting

The first component of the on-chip power supply comprises an energy harvesting unit. This unit converts forms of energies that are present in their environment into useable electrical energy through various physical mechanisms. These energies can be of the form of solar, wind, hydrothermal, mechanical, thermoelectric, or acoustic [13]. These energies are harvested and used to power miniaturized sensors in WSNs and wearable electronics. Among these energy sources, mechanical energy is the most distributed as some vibrations are present in all surroundings, be it a person in motion, a jet engine, a railway track or a mining or underwater location [15].

Mechanical energy can be extracted by the vibrations, noise, rotation, and most recently, hydraulic pressure induced in the device through three different mechanisms - electrostatic, electromagnetic and piezoelectric harvesting [16]. If a harvester device is fabricated with its characteristic frequency similar to the surroundings' one, it can utilize these vibrations and convert the mechanical energy into electrical energy. This form of energy harvesting is called kinetic energy harvesting. Out of the three, piezoelectric energy harvesters (PEH) has the maximum energy density and a high energy conversion efficiency. [17]. They have a simple configuration that can utilize MEMS technology for their fabrication. PEHs also do not require any input voltage for starting up compared to the electrostatic and electromagnetic harvester [3-5][18, 19]. Thus, they can be considered as potential candidates for powering miniature devices and wireless sensors.

Vibrational energy harvesters (VEH) in PEHs use the concept of converting stress induced by mechanical vibrations into electrical energy by expansion and contraction of the piezoelectric material which is layered on top of a vibrating surface, usually a cantilever. The cantilever is designed in such a way that it has its natural frequency within a targeted range. They, however, suffer from two significant drawbacks - 1) their range of output producing frequencies is quite low, 2) being MEMS, their power cannot easily reach the desired levels [20].

### 1.2 Energy storage

The second main component of an on-chip power supply is the energy storage unit. The energy harvesters gather the energy from ambient sources in the surroundings and deliver it to the power conditioning unit. The energy storage unit is then connected to the output of the power conditioning circuit, which provides a steady stream of DC output whenever the harvester extracts energy. First chosen as primary energy storage systems were rechargeable batteries such as NiMH [21] and Li-ion [22]. While rechargeable batteries show high capacity and low leakage, wireless sensor life is limited by the cycle life of rechargeable batteries [23]. Cycle life of a battery is the number of charge-discharge cycles it can go through before its capacity drops below 80 % of its maximum capacity. The residues from the electrode-electrolyte reaction ages the device by increasing the internal resistance over a period of time. However in reality, by the time it has completed its cycle life, the capacity of the battery can reach up to 50 % or even 20 % in some cases. Due to this, a WSN would require replacement after not even 1-2 years. Supercapacitors, in recent years, have emerged to be successful technological tools in storing charge. They have a higher cycle life than batteries, and in recent years, their performance has been demonstrated to be equivalent to the low-end commercial batteries [24]. Therefore, they can be, again as PEHs, considered as a truly viable option for a lifetime on-chip power supply.

### 1.3 Manufacturing

#### 1.3.1 IC-compatibility

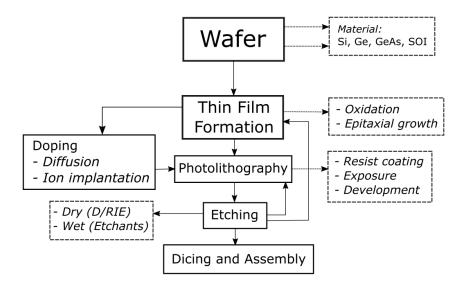

The standard process technology for integrated circuits (ICs) and very large scale integrated (VLSI) circuits is shown in Figure 1.2. The fabrication of these components starts on a wafer which is a polished semiconductor substrate. The next step usually involves deposition or growth of thin films such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, polySi or dielectric films, and even metalized oxides. After the growth of thin films, the substrate undergoes doping through diffusion or ion implantation. This process is used in IC technology to fabricate pn junction diodes which can later be used in MOSFET (metal oxide semiconductor field effect transistor) fabrication. Then, the substrate is subjected to photolithography where a polymeric photoresist is spin-coated on it and then exposed in UV light through a special mask with a specific design. The photoresist is sensitive to UV light depending on its chemical structure. It is generally of two types - positive and negative. In the case of the positive photoresist, the UV light breaks the linkages of the polymer exposed, while in the negative, the exposure strengthens the bonds of the polymer. During the development of the photoresist step, the weaker linkage polymers are etched out of the substrate while leaving the photoresist in the desired pattern. The exposed surface is then used for further doping, film formation, or etching, depending on the process' requirement. The process is then repeated in several cycles depending on the total number of photolithographic masks [25].

However, there are several constraints in the IC fabrication process regarding the choice of material and equipment. The first major constraint is the material for the wafer. An IC wafer should be mechanically robust with necessary hardness required to survive indentations, laser marking, stains, streaks, and scratches. The second constraint comes in the form of radiation required for photolithography which is restricted to the users of optical and UV light, X-ray, and e-beam, a short for electron beam. The third constraint is in the form of metals used in IC fabrication. This list is restricted to Al, Au, Ag, Cr, Mo, W, Pt, Pd, Ta, and Ti [25]. Furthermore, the process is also dependent on the melting point of these metals. Among the used metal, Al has the lowest melting point at

660 °C. So, the fabrication of energy harvesters, supercapacitors, and their subsequent integration should be conducted with the techniques within these constraints.

Fabrication of VEHs requires photolithography, etching, metallization, doping, and deposition techniques. These processes are standard in micromachining techniques too. Furthermore, with improving MEMS technology, these processes have become highly developed in improved reliability, mass production, and cost reduction while achieving a high wafer yield. Therefore, energy harvesters that are fabricated through MEMS techniques can be easily integrated into a CMOS compatible fabrication process.

However, for the energy storage element, supercapacitors generally require a large volume and specialized manufacturing techniques that make them hard to be integrable in microsystem electronics technology that requires semiconductor micromachining. Therefore, developing CMOS compatible fabrication processes has attracted much attention over the past few years [26, 27, 28, 29, 30]. Microsupercapacitors are miniaturized supercapacitors that are small enough to be integrated into electronic devices. They can be integrated either as self-powering systems with charging through energy harvesters, or enhanced micro battery systems where they act as hybrid devices with batteries to improve the lifetime of a device.

Successful integration of MSCs in a fully IC compatible process scheme can lead to an on-chip power supply that improve their lifetime. Compared to other techniques to manufacture MSCs such as screen printing[31], ink-jet printing[30], laser scribing[29], electrostatic spray deposition[28], electrophoretic deposition[32], chemical exfoliation[33] and doctor blade coating[34], the use of spin coating has the advantage of already being an established conventional part of standard CMOS processing, implying that it is as such inherently CMOS/MEMS compatible. These techniques are not compatible with semiconductor device processing, with it moving towards a completely automatic factory. Processes like ink-jet printing and screen printing do not have an

Figure 1.2: Main fabrication steps for a IC fabrication process. The dotted square boxes show the constrained variety of processes possible in a CMOS compatible fabrication facility.

effective scaling down technique, while its raster-scanning process inhibits laser scribing. Thus, in view of the expected further automation in IC manufacturing [35], its compatibility advantage makes spin coating a strong candidate for being the preferred MSC manufacturing technique, provided it can demonstrate that it can fabricate devices of sufficient quality and yield.

### 1.4 Scope of the thesis

In this thesis, we are going to discuss different components of an on-chip power supply in the following chapters: Chapter 2 deals with discussion of VEHs. First, we will examine the theoretical principles of single degree of freedom structures, followed by the restrictions on its performance. Then we shall review the solutions used in macro energy harvesting for improvement in bandwidth and power efficiency. We have also described the fabrication process for energy harvesters, issues related to it, and ensuing mechanical characterization. In Chapter 3, we shall take up supercapacitors and more specifically MSCs. We will argue for the potential fabrication methods for these devices that can demonstrate integration into an on-chip platform in CMOS compatible process scheme. The fabrication methods that we followed for their manufacturing are described with a special section for the issues that we encountered while performing the process. We shall then examine some of the results for the designs fabricated and optimizations for performance improvement. Finally, in Chapter 4, we shall discuss the feasibility of on-chip integration of the fabricated VEHs and MSCs through a describing the circuit design and performance requirements for each device. Finally, we will conclude with a discussion on the best possible method for their packaging and integration.

## **Chapter 2**

## **Piezoelectric Micro-energy Harvester**

Piezoelectric energy harvesters are devices that convert the energy in the surroundings through actuation of a piezoelectric material. Piezoelectricity is the property of materials that develop voltage upon application of stress onto their surface. It is a reversible process as the material can develop strain when an electric field is applied to it[36]. This effect was demonstrated by Pierre Curie and Jacques Curie in 1880 [37]. VEHs convert the vibrations in the surrounding into electrical energy through stress on their cantilever beams.

### 2.1 Introduction

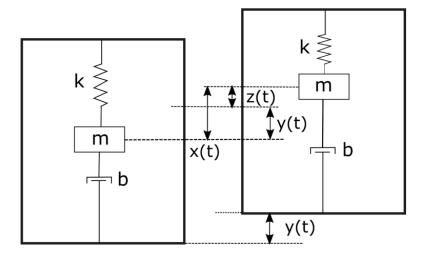

In order to understand the working mechanism of VEHs, the device must be visualized as an analogous to a mass-spring-damper (MKS) system, as seen in Figure 2.1. The mass of the device is m, y is the amplitude of displacement, k is stiffness of the beam, y(t) is the displacement of the beam, z(t) is the relative position of the center of mass of the beam with respect to its displacement and  $b_m$  and  $b_e$  are the damping coefficients and  $b = b_m + b_e$ , where m and e are the mechanical and electrical indices respectively.

Let the displacement of the system  $y(t) = Y sin(\omega t)$ . With that we get the transfer function as a second order differential equation

$$mz''(t) + bz'(t) + kz(t) = -my''(t)$$

(2.1)

Now in a standard form,

$$z''(t) + \frac{b}{m}z'(t) + \frac{k}{m}z(t) = y''(t)$$

(2.2)

From the solutions of the second order differential equation, we know that

$$\frac{b}{m} = 2\zeta\omega_n \qquad \qquad \frac{k}{m} = \omega_n^2$$

where  $\omega_n$  is the natural frequency of the system, and  $\zeta$  is the damping ratio. So, from this, we get

$$\omega_n = \sqrt{\frac{k}{m}} \qquad \qquad \zeta = \frac{b}{2\sqrt{km}}$$

We can also write  $\zeta$  in terms of a derived notation called the quality factor (*Q*) as

$$Q = \frac{\sqrt{km}}{b}$$

which can also written in terms of  $\omega_n$  as

$$Q \approx \frac{\omega_n}{\Delta \omega} \tag{2.3}$$

where  $\Delta \omega$  is the bandwidth of frequencies that have an output of at least half the amplitude at the resonant frequency  $\omega_n$ . It is also denoted as the 3 dB bandwidth of any harvesting system. Considering our input signal y(t) the solution to equation 2.1 is

$$z(t) = \frac{m\omega^2 Y}{k - m\omega^2 + j\omega b} sin\omega t$$

(2.4)

After calculating the solution for z(t), we get

$$z(t) = \frac{\omega^2}{\sqrt{(\omega_r^2 - \omega^2) + (\frac{b\omega}{m})^2}} Y sin(\omega t + \phi)$$

(2.5)

where  $\phi$  is the phase angle

$$\phi = tan^{-1} \frac{b\omega}{k - \omega^2 m}.$$

(2.6)

Now that we have a solution for z(t), we can calculate the average power, mechanical parasitic and electrical output as

$$P = b(z'(t))^2$$

(2.7)

which gives us

$$P(\omega) = \frac{m(\zeta_m + \zeta_e) Y^2(\frac{\omega}{\omega_r})^3 \omega^3}{[1 - (\frac{\omega}{\omega_r})^2] + (2(\zeta_m + \zeta_e) \frac{\omega}{\omega_r})^2}$$

(2.8)

Figure 2.1: Typical schematic of the MKS 1DOF system.

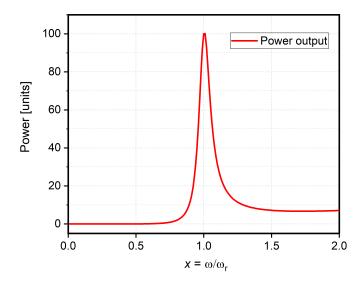

Figure 2.2: Simulated power output of a generic single cantilever based energy harvester with respect to  $x = \frac{\omega}{\omega_r}$

When the frequency of the system  $\omega$  is equal to the resonant freqency  $\omega_r$ , the power reaches its maximum which is

$$P = \frac{mY^2\omega_r^3}{4(\zeta_m + \zeta_e)} \tag{2.9}$$

On analysis of equation 2.8 further, we figure out the main issue that needs to be optimized with the utilization of VEHs in on-chip power units, i.e., narrow bandwidth of operational frequencies.

Considering  $\frac{\omega}{\omega_r} = x$  and keeping *m*, *Y* and  $\zeta_m$ ,  $\omega_r$ , and  $\zeta_e$  as constants  $C_n$ , we get the equation 2.8 as

$$P = \frac{C_1 x^6}{(1 - x^2)^2 + C_2 x^2} \tag{2.10}$$

When we plot this equation in Figure 2.2, we see the dramatic reduction of output power at either side of  $\omega_r$ . Therefore, we need to find solutions for improving its bandwidth of frequencies by reviewing some of the pre-existing solutions in macro-energy harvesters. These solutions must also be feasible for realization in a MEMS structure which can then further be integrated with an on-chip power supply.

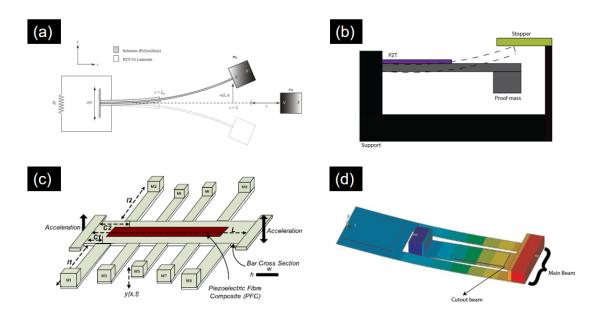

One of the potential solutions to the bandwidth and power problem is a nonlinear generator with bistable structures. A bistable structure provides the cantilever design with multiple stable equilibrium positions that allows it to have multiple frequencies where the stress distribution on the beams is optimal. Stanton et al. [38] incorporated a magnetic nonlinearity with the help of two magnets strategically placed in a linear system. Wu et al. [39] and Erturk et al. [40] also arrived at the same conclusion of obtaining a broad bandwidth. Having a bistable structure with magnetic attachments is a novel idea; however, it is usually large and requires an auxiliary support structure that cannot be currently placed in a MEMS design.

Similarly, studies by Blystad [41] and Liu [42] suggest amplitude limiters as another way to increase the bandwidth. A metal plate is used as a mechanical stopper to limit the displacement of the cantilevers. Soliman et al. [43] experimented on such a structure with a single stopper and showed an improvement in the power output bandwidth of the device. Even with the improved bandwidth, in practicality, lower maximum output power and fatigue-induced failures in such designs make their incorporation harder in microstructural harvesters.

Another idea of improving bandwidth is to create a generator array consisting of cantilever beams of different lengths and proof masses operating at different frequencies. Studies conducted by Shahruz et al. [44], Ferrari [45], Xue [46], and Liu [47], Qi et al. [48] expounded upon this concept with more cantilevers in a single array. Although favorable results are obtained, the requirement of integrating particular coupling mechanisms for each cantilever and the device's volume efficiency, make multifrequency generator array more complicated to design and fabricate as a MEMS design.

Currently, known solutions use two-degree-of-freedom (2DOF) structures to improve the bandwidth in micro-cantilever designs. Roundy et al. (2005) [49] initially proposed the idea of incorporating multiple proof masses to create a multiple-DOF with at least one structure resonating in the desired frequency range. Ou et al. (2010) [50], then, derived a theoretical model of a dual-mass beam structure for bandwidth broadening. Aldraihem and Baz (2011) [51] and Arafa et al. [52] (2011) studied a 2DOF acting as a dynamic magnifier. Although close resonances could be achieved, the magnifier required a huge weight, which proved counterproductive to miniature harvesters. Later, Erturk et al. [53] and Xu et al. [54] considered innovative L-shaped designs for cantilevers to bridge the gap of natural frequencies.

To devise natural frequencies closer, Jang et al. [55] (2011) developed a 2DOF piezoelectric energy harvesting device which exploited the structure's translation and rotation vibration modes. The device showed two-peak power output and displayed bandwidth improvement at high power levels compared to the conventional singledegree-of-freedom (SDOF) device. Kim et al. [56] (2011) demonstrated the performance comparison between a 2DOF and conventional SDOF device. Wu et al.[57] proposed a "cut-out" 2DOF harvester with a secondary beam enclosed within the main beam, which achieves two close resonances with significantly large amplitudes. Although, even with close resonance peaks, the bandwidth of the system included an anti-resonance frequency which led to a significant drop of the output voltage.

While several studies show significant improvement of bandwidth through 2DOF structures, much research on it does not focus on the distribution of stress on the cantilever beams. Studies by Staaf et al. [58, 59] provide an assessment of using parallel cantilevers coupled to one another at one end. This improves the stress distribution patterns and the bandwidth through coupled resonance at frequencies near the natural excitation. The details of the VEHs can be found in Table 2.1.

Macro-energy harvesters are a potential source for energy; however, their manufacturing is not equipped to produce hundreds of devices at the same time. Surface micro-machining fabrication techniques have been used in manufacturing CMOS devices, sensors, actuators, and also energy harvesters at a large scale [60]. They presented a single cantilever with a hanging proof mass. A single cantilever based piezoelectric

Figure 2.3: Techniques in macro-energy harvesting that are used for improving the device's bandwidth of frequencies: (a) a bistable structure [41], (b) amplitude limiter, (c) array configuration [46], (d) 2DOF freedom structure [42]. Images are reproduced after permission from the publishers.

energy harvester is one of the efficient designs. In principle, the micro-structure consists of a rectangular beam with a hanging proof mass. The proof mass is usually quite thick compared to the cantilever beam. The large proof mass acts as a hanging mass to the spring system, thereby reducing its natural frequency. The proof mass can be made during the micromachining process, or it can be added onto the fabricated structure. One of the first micro-energy harvesters were fabricated by Marzenski et al. [61]. Later, Jeon and Choi [62], [63] fabricated a d<sub>33</sub>, PZT-based vibrational harvester. The cantilever beam was composed of a thin SiO<sub>2</sub>/SiN<sub>x</sub> layer with a diffusion barrier of ZrO<sub>2</sub> separating PZT from the structure. The proof mass was made up of SU-8 thick resist. Fang et al. [64] similarly created microcantilevers through micromachining techniques and added a Ni proof mass post-processing. Due to Ni's higher density over Si (8.9 g/cm<sup>3</sup> vs. 2.3 g/cm<sup>3</sup>), it reduces the resonance frequency of the device. We have examined several micro-energy harvesters in a more concise format in Paper 1. Also, the list of device performances can be found in Table 2.1.

With the above energy harvesters, most of the designs comprise of a beam that has an active piezoelectric area along the fixed ends while the free end is left unused as it experiences minimal stress, which can be considered as a "dead area". The piezoelectric material is essentially a capacitor. When the material is stressed, its molecular orientation starts exhibiting a dipole moment. This dipole moment gives rise to an electric field that leads to the redistribution of charge in the crystal lattice. If there is no stress on the piezoelectric material, the total dipole moment of the piezoelectric material reduces, thus giving less charge. This is an issue when we discuss the performance of MEMS vibrational harvesters as these devices require the utilization of all the piezoelectric material area on the cantilevers for efficient performance. Therefore, we require novel solutions from the macroscopic VEHs to test them on a MEMS scale.

In recent years, the focus of the vibrational micro-energy harvester research has shifted to the fabrication of specialized designs to improve the bandwidth of the energy-providing frequencies. Park et al. [65] designed an intrinsically stress-induced bent Si cantilever of 3 mm × 2 mm × 18  $\mu$ m. The harvester had two directions of oscillation, vertical and radial. When the cantilever is released, it undergoes bending deformation through the presence of a low temperature oxide (SiO<sub>2</sub>) and a low stress nitride (SiN<sub>x</sub>) on top of the Si substrate. They designed the study on the principle of proportional dependence of the output power on the bending moment. They also shaped the cantilevers in a trapezoidal form to improve the distribution of stress on the beam. The device gave 1  $\mu$ W power output at a resonance frequency of 115 Hz with a Q-factor of 51. Leuke et al. [67] fabricated a set of folded spring structures for reduction of operating frequency of the microstructures. The folded beam shape reduces the overall stiffness of the design and thus bring the natural frequency of the system unto 30 - 300 Hz. Also, the next natural frequencies of the structure are brought closer to one another. They achieved a power output of 690.5 nW at 226 Hz in one of the designs which had four

| Ref. | Volume<br>(mm <sup>3</sup> ) | Res. Freq.<br>(Hz) | • <b>V</b> <sub>pp</sub> (V) | Power (W)   | Geometry                         |

|------|------------------------------|--------------------|------------------------------|-------------|----------------------------------|

| [64] | 0.6                          | 608                | 0.89                         | 2.16 µ      | Single cantilever                |

| [63] | 0.05304                      | 13900              | 2.4                          | $1 \mu$     | Cantilever                       |

| [47] | 0.045                        | 610                | 3.9                          | $3.98  \mu$ | Array                            |

| [45] | 13.5                         | 113                | -                            | $89 \mu$    | Array                            |

| [40] | 620                          | 46.4               | -                            | -           | Dynamic magni-<br>fier           |

| [54] | 480                          | 39.8               | -                            | 13.54 m     | Right angle                      |

| [50] | 3640                         | 26                 | -                            | -           | 2DOF no cutout                   |

| [48] | 6800                         | 14-30              | 18                           | -           | Array                            |

| [56] | 800                          | 11                 | 60 V/g                       |             | 2DOF two can-<br>tilevers        |

| [52] | 1650                         | 21                 | 4.7                          | $5.68  \mu$ | 2DOF no cutout                   |

| [39] | 2640                         | 18                 | 22 V                         | 1.25 m      | 2DOF "cut-out"<br>rectangular    |

| [42] | 0.075                        | 30-48              | 100 m                        | 100 n       | Dynamic magni-<br>fier           |

| [65] | 3                            | 115                | 16 m                         | 1 n         | Quasi bendable<br>cantilever     |

| [66] | 0.36                         | 234.5              | 1.62 - 5                     | $66.75~\mu$ | Rectangular                      |

| [67] |                              | 45 - 3667          | -                            | 690 n       | Folded Spring                    |

| [59] | 48                           | 330-410            | 11.7 V                       |             | S-shaped cou-<br>pled cantilever |

| [36] | 0.05                         | 1258               | -                            | -           | M-shaped                         |

Table 2.1: List of macro- and micro-VEHs ordered according to year of publication from oldest to newest.

folded Si springs attached to a central hanging proof mass. Yu et al. [66] designed a five cantilever system with a single large proof mass. The fabricated generator had plates of size 3 mm × 2.4 mm × 50  $\mu$ m and a Si proof mass of 8 mm × 12.4 mm × 0.5 mm. The power output at its resonant frequency of 234 Hz was 66.75  $\mu$ W. A similar concept was also employed by Zhang et al. [68] where instead of rectangular folded springs, they used circular annular rings, each attached to the central proof mass. The device die is 6 mm × 6 mm in size and demonstrated resonance frequencies less than 11 Hz with a voltage output 7.5 mV at less than 0.2*g* acceleration.

#### 2.1.1 Two-degree of freedom (2DOF) design

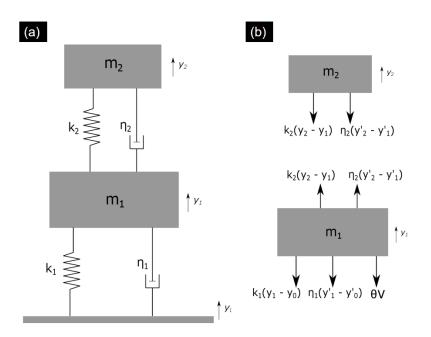

A piezoelectric energy harvester is normally designed as a spring-mass-damper (MKS) system for analytical modeling. The schematic in Figure 2.4(a) is a conventional 2DOF lumped parameter model which is used for the analysis of the M-shaped designs. In this model,  $m_1$  and  $m_2$  are the masses of the primary and secondary structures respectively,  $k_1$ ,  $k_2$ , and  $b_m$ ,  $b_e$  are their respective spring constants and dampings. When the system is in an excited base configuration, the initial displacements of the base, primary, and secondary proof masses are  $y_0$ ,  $y_1$  and  $y_2$ .  $-V\theta$  is the force induced by mechanical coupling, where *V* is the potential formed in the piezoelectric film and  $\theta$  is electromechanical coupling coefficient.

Two equations of motions and two Kirchoff's voltage equation are derived from the free-body-diagram shown in Figure 2.4(b). They are as follows:

$$m_2 y_2" = -k_2(y_2 - y_1) - b_e(y_2' - y_1')$$

(2.11)

$$m_1 y_1 " + m_2 y_2 " = -k_1 (y_1 - y_0) - b_m (y_1' - y_0')$$

(2.12)

$$C_s V' + \frac{1}{R} V = \theta(y_1' - y_0')$$

(2.13)

Taking a Laplace transform of equations 2.11, 2.12, and 2.13, where  $s = j\omega$  we get,

$$m_1 s^2 \hat{U}_1 + m_2 s^2 \hat{U}_2 = -k_1 (\hat{U}_1 - \hat{U}_0) + s b_m (\hat{U}_1 - \hat{U}_0) - \theta \hat{V}$$

(2.14)

$$s^2 m_2 \hat{U}_2 = -k_2 (\hat{U}_2 - \hat{U}_1) + b_e s (\hat{U}_2 - \hat{U}_1)$$

(2.15)

$$\hat{V}(C + \frac{1}{R}) = s\theta(\hat{U}_1 - \hat{U}_0)$$

(2.16)

Now, a standard  $2^{nd}$  order ordinary differential equation can be written in terms of  $\omega$ , frequency and  $\zeta$ , damping coefficient.

$$x'' + \frac{b}{m}x' + \frac{k}{m}x = 0$$

(2.17)

where  $\frac{b}{m} = 2\zeta \omega_n$  and  $\frac{k}{m} = \omega^2$ . Therefore, after using the annotations, we have

Figure 2.4: (a) Typical MKS system for 2DOF cantilever design (b) Free body diagram of each mass.

$$\omega_{1} = \sqrt{\frac{k_{1}}{m_{1}}} \qquad \qquad \omega_{2} = \sqrt{\frac{k_{2}}{m_{2}}} \qquad \qquad \zeta_{1} = \frac{b_{m}}{2\sqrt{k_{1}m_{1}}}$$

$$\zeta_{2} = \frac{b_{e}}{2\sqrt{k_{2}m_{2}}} \qquad \qquad \mu = \frac{m_{2}}{m_{1}} \qquad \qquad \lambda = \frac{\omega_{2}}{\omega_{1}}$$

$$\Omega = \frac{\omega}{\omega_{1}} \qquad \qquad r = \omega_{1}CR \qquad \qquad k_{e}^{2} = \frac{\theta^{2}}{Ck_{1}}.$$

Solving equations 2.14, 2.15, and 2.16, we get the equation for the two dimensionless natural frequencies as [69]

$$\Omega_{1,2} = \sqrt{\frac{(1+\mu)\lambda^2 + (1+k_e^2)}{2} \pm \frac{\sqrt{((1+\mu)\lambda^2 + (1+k_e^2))^2 - 4\lambda^2(1+k_e^2)}}{2}}$$

(2.18)

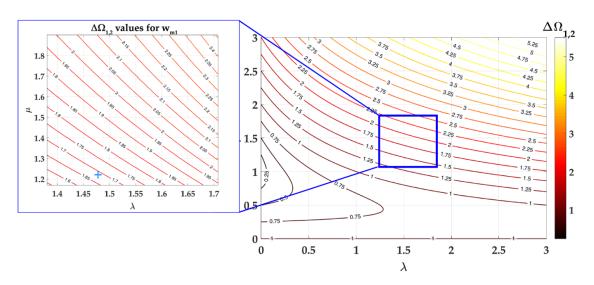

It can be seen from equation 2.18, that the closening of the first two natural frequencies depends on the parameters  $\mu$  and  $\lambda$ . Figure 2.5 shows the contour plot of  $\Delta\Omega$  vs  $\mu$  and  $\lambda$ . The next section describes the simulation results in COMSOL for three designs that provided different values of and  $\mu$  and extends the hypothesis generated by equation 2.18.

Figure 2.5: Contour plot of difference in the first two dimensionless eigenfrequencies  $(\Delta \Omega)$  with respect to ratio of beam masses  $(\mu)$  and their respective first eigenfrequencies  $(\lambda)$

### 2.2 Simulations

#### 2.2.1 Design

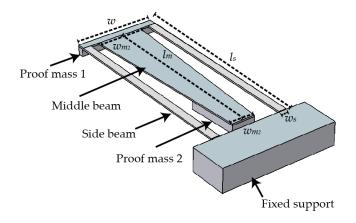

The 2DOF micro-energy harvester is numerically simulated in COMSOL to acquire the optimal dimensions for the realization of enhanced stress distribution and narrowing of natural frequencies. Three different topologies of designs were investigated, namely, M-shape, M-long, and M-big. Figure 2.6 shows the schematic of the generalized harvester in COMSOL. The big-block is taken as the fixed support in the simulation. For modeling a MEMS piezoelectric energy harvester, the design structure consists of Si and the piezoelectric material is chosen to be PZT-5A, the one with the closest elasticity matrix with the PZT that we could accrue from Silex Microsystems on our wafers. The five main dimensional parameters that play an important role in determining natural frequencies are the length and width of the side beams,  $l_s$  and w respectively; length of middle beam,  $l_m$ , and widths of the middle beam at the attached and free ends,  $w_{m1}$  and  $w_{m2}$  respectively. The thickness of the device is decided by the SOI wafer used, i.e., 20  $\mu$ m. The thickness of the proof mass is 100  $\mu$ m for each design so that they could be fabricated within a single fabrication process plan.

Dimensions  $l_s$  and w govern the natural frequency of the system. They were chosen such that the device is in 1.2 - 1.5 kHz. If M-shape is taken as a reference, then M-long has a longer and narrower middle beam, while M-big is approximately double the size of M-shape to test the scaling of characteristics. Table 2.2 provides the detailed differentiation of dimensions on each design. The designs employed for the M-shape, M-long, and M-big were chosen to bring the first two natural frequencies as close to each other as possible. Therefore, each of these designs is an ideal representation of its particular features. Further description of the dimensional analysis relating to  $\mu$  and  $\lambda$ is given in Paper 1.

Figure 2.6: Schematic image of the M-design harvester setup in COMSOL. Table 2.2 outlines the dimensions of each design.

Table 2.2: Dimensions of M-shape, M-long, and M-big used in COMSOL simulations, in  $\mu$ m.

| Dimensions | M-shape | M-long | M-big |

|------------|---------|--------|-------|

| $l_s$      | 2500    | 2900   | 5000  |

| w          | 1000    | 1000   | 2000  |

| $l_m$      | 2288    | 2700   | 4576  |

| $w_{m1}$   | 560     | 500    | 1000  |

| $w_{m2}$   | 300     | 100    | 400   |

| ws         | 100     | 100    | 200   |

#### 2.2.2 Results

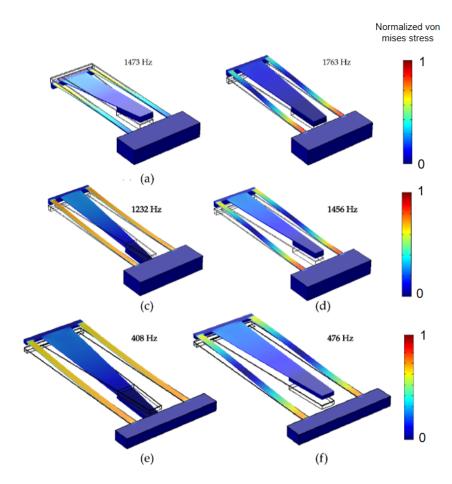

The results for the eigenfrequency simulations are shown in Figure 2.7. For the M-shape, the first and second eigenfrequencies are observed at 1473 Hz and 1763 Hz. The M-long design has its first two resonating frequencies at 1232 Hz and 1456 Hz. The M-big design, which is twice the dimension of the M-shape, gives its mode shapes at 408 Hz and 476 Hz. To the best of the author's knowledge, when the frequencies are in kHz, such closening of the first two natural frequencies has not been published anywhere else.

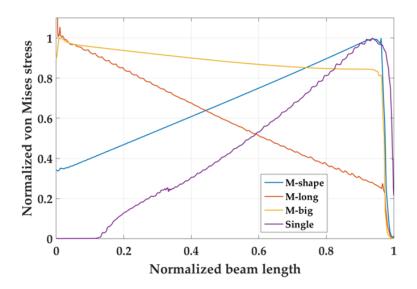

The von-mises stress gradient suggests that the vibration of the middle beam enhances the distribution of stress on the cantilever beams on each of the three designs. The middle beam does not act as a dormant proof mass; it has its own characteristic vibrational mode. The presence of stress on the middle beam is coupled with the side beam's stress, which leads to a larger area acting under stress. Figure 2.8 displays the distribution of stress on the outer edge of the cantilever side beams. The free end of the beam is at x = 0. The boundary conditions for each design were kept constant. Gravity and body load are the only forces acting on the whole device. There is no external acceleration provided to the system. The single cantilever has the maximum stress at its fixed end. About 20% of the beam experiences no stress near the free end. In contrast, the M-shape has the highest stress at its fixed end, half of it at approximately 75% from

Figure 2.7: Mode shapes of (a), (b) M-shape, (c), (d) M-long and (e), (f) M-big at the first and second natural frequencies. The gradient on the side displays the von-mises Stress  $(N/m^2)$  on the cantilever beams without the PZT piezoelectric layer.

the fixed at, and around 40 % at the fixed end. M-long and M-big devices display a different characteristic curve where the stress at their free and fixed ends are nearly constant. M-shape shows a constant stress at both ends, while M-big demonstrates an increased stress at its free end. Furthermore, on analyzing Figure 2.8, M-shape and M-long have a more than double the stress average than of Single cantilever. Although M-big has a lower value, the near-constant characteristic curve compensates for it.

The simulation output of the voltage of the designs suggest that M-shape has a peak voltage of 16.1 V at its first resonance frequency of 1538 Hz. It demonstrates a characteristic coupled curve from its 1538 Hz to 1820 Hz (2<sup>*nd*</sup> eigenfrequency). This demonstrates that even at frequencies far off from the resonant frequencies, there is enough stress on the beams to generate an output. The Q-factor for the M-shape is 34.9. In M-long, a peak voltage of 4.7 V is obtained at 1257 Hz with a Q-factor of 36.9. At 1320 Hz, the output voltage reduces to 0 V, and it starts rising again until the second natural frequency at 1477 Hz. Figure 2.7(d) suggests the formation of an S-shape at 1456 Hz. Although the beam experiences high stress, the piezoelectric material on the same beam is stressed in opposite directions, thereby negating their respective outputs. Anti-resonance is featured at the second eigenfrequency in all designs. Similarly, M-big

Figure 2.8: Normalized von mises stress on the sidebeams of the M-shaped energy harvesters compared to the single cantilever.

shows anti-resonance in between the two characteristic frequencies. It has the highest voltage output of the three design due to a larger piezoelectric area. Its peak voltage of 30.5 V is demonstrated at 426 Hz with a Q-factor of 35.5. Among these three designs, M-shape fares the best by having a lower Q-factor and a strongly-coupled model that induces a broader bandwidth of utilizable frequencies.

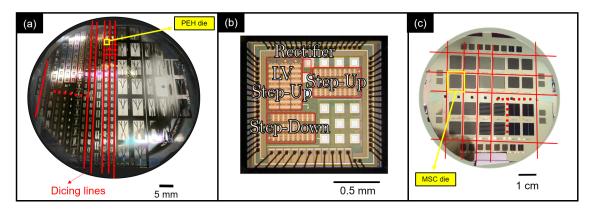

### 2.3 Fabrication

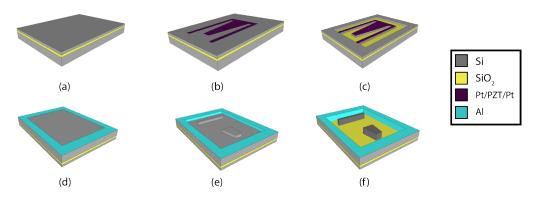

#### 2.3.1 Process plan

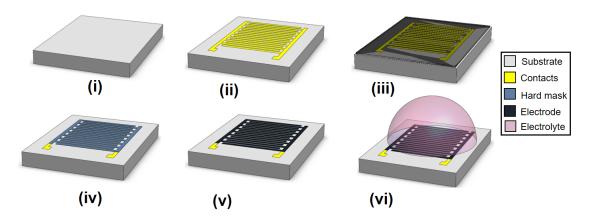

After modeling and simulations for various cantilever designs, the fabrication of all three energy harvesters is performed through the following process scheme on a 6" Si-on-Insulator (SOI) wafer. Figure 2.9 shows the fabrication scheme.

- A 6" SOI wafer is cleaned (Figure 2.9(a)). The deposition processes of the bottom electrodes, lead zirconate titanate (PZT), and top electrodes were performed by Silex Microsystems AB, Sweden. A 20 nm layer of TiO<sub>2</sub> is sputtered onto the substrate. TiO<sub>2</sub> acts as an adhesion layer for Pt and also provides epitaxial uniformity to the buffer oxide. The Pt layer of 100 nm is sputtered, keeping the texture template uniform for the subsequent PZT deposition. A buffer layer of LaNiO (20 nm) is added on top of the surface. Then, a PZT layer of 1.1  $\mu$ m is deposited by a sol-gel process on the buffer layer. The PZT layer has previously demonstrated an electromechanical coupling coefficient,  $e_{31} = -18$  C/m<sup>2</sup>. Finally, the top electrode Pt/Ti layer is evaporated.

- The layers are etched one-by-one through separately patterned resist masks. For each layer, an AZ4562 thick resist pattern is spin-coated at 3000 rpm/s for 30

sec, and then soft-baked at 100 °C for 3 min. The resist is exposed through an Ultra Violet (UV) enabled mask aligner for 50 sec. The exposed pattern is then developed in MF319. The resist deposited on top of the surface protects the required layouts on the wafer. Thereafter, the top Pt/Ti layers are etched under Argon plasma at 400 W for 10 mins. The resist mask is removed, and another is patterned for the PZT layer. The 1.1  $\mu$ m PZT layer is etched through a solution of HF:HNO<sub>3</sub>:H<sub>2</sub>O in 1 min 20 sec. Finally, the buffer oxide and the bottom Pt/Ti layers are etched by the same Argon plasma. (Figure 2.9(b)).

- A resist mask is deposited over the electrodes, and the device Si layer of the SOI wafer is etched until the buried oxide through SF<sub>6</sub> and C<sub>4</sub>F<sub>8</sub> deep reactive ion etching (DRIE) process in Centura II (DPS & MxP). The etch process is performed by the tool in three steps, 1.2 sec of C<sub>4</sub>F<sub>8</sub> passivation layer deposition, followed by the passivation breakthrough step of 1.3 sec and Si etching step of 1.5 sec. More information on the recipe is provided in Paper 1. The DRIE process lasted for 21 min for a 20  $\mu$ m Si etch. (Figure 2.9(c))

- The wafer is then processed from the backside. The SOI wafer is bonded onto a carrier wafer by a thermal tape (120 °C release temperature), and an Al hard mask is etched; firstly a 500 nm Al layer is sputtered at the back; it is then patterned via ma-N1410 negative resist wafer is heated at 100 °C for 5 min, the resist is spin-coated at 4000 rpm and then patterned through backside enabled UV mask aligner; finally an 85 %  $H_3PO_4$  solution is used for etching Al in 3 min and 30 sec. (Figure 2.9(d))

- An AZ4562 resist mask is deposited and patterned to protect the proof mass structures. Since the etch rates for AZ resist:Si is 1:66, the 7  $\mu$ m resist mask is thick enough to sustain the 100  $\mu$ m Si etching. Si is then DRIE etched using SF<sub>6</sub> and C<sub>4</sub>F<sub>8</sub> in STS-ICP plasma etcher in two cycles etching for 12 sec and passivation for 7 sec. (Figure 2.9(e))

- The resist mask is then removed, and the bare wafer is etched from the backside for 280  $\mu$ m until the buried oxide layer. (Figure 2.9(f))

Once the required structures are obtained, the wafer is diced into smaller chips.

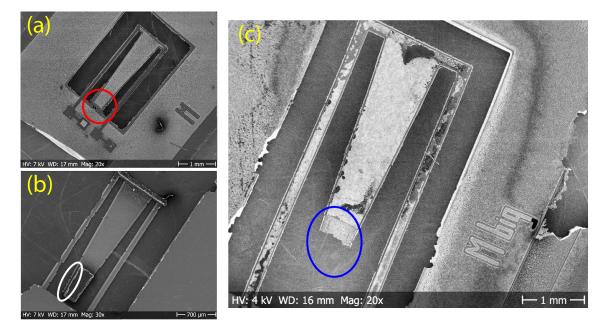

#### 2.3.2 Issues in fabrication

During the fabrication process, the challenges in frontside etching and the final thermal tape release led to the failure of nearly 90 % of the devices on the wafer. The frontside etching is to be performed on a resist patterned, 20  $\mu$ m thick device layer. Centura II (DPS & MxP) is used for this process step. There were several bubbles trapped at the adhesive during the bonding of SOI wafer to the 8" carrier. This led to an uneven distribution of cooling on the wafer backside and eventually, the resist evaporated due to high temperature. This led to an uneven etching of Si in the device layer. Moreover, some of the electrodes were also etched during the process. Figure 2.10(a) shows the partially released *M-shape* device. The unetched Si is visible in the red circle. During

Figure 2.9: Process scheme for the microenergy harvester fabrication.

the release of thermal tape at 120 °C, there were several devices snapped near the edges of the secondary proof mass. Figure 2.10 demonstrates one such *M-big* device, which does not has a secondary proof mass, indicated at the blue circle.

### 2.4 Results and discussion

A setup of instruments is designed to record the vibrational characteristics of the device, shown in Figure 2.11. It consisted of a laser interferometer (Figure 2.11(1)) and reference, shaker table (Figure 2.11(2)), photodetector, and a vibrometer. The object is placed at the excitation table (Figure 2.11(3)). The laser beam from the scanning head is positioned to a scan point on the object through mirrors fitted into the system. The scattered light

Figure 2.10: SEM micrographs of the fabricated energy harvesters. (a) *M-shape*. The red circle shows the partially etched Si device layer. (b) *M-long* after complete fabrication process. (c) *M-big*. The secondary proof mass is snapped off during thermal release, its intended place denoted through the blue circle.

from the device is received correspondingly. The backscattered light interferes with the reference beam at the scanning head and the photodetector records this interference. The decoder in the vibrometer provides a voltage which is proportional to the velocity of the vibration parallel to the measurement beam. This voltage output is digitized and processed as a vibrometer signal. There are various kinds of excitations possible in the measurement setup. They can be periodic with rectangular or sinusoidal vibrations, transient, i.e., with a pulse or an impact blow, and random noise generated signals.

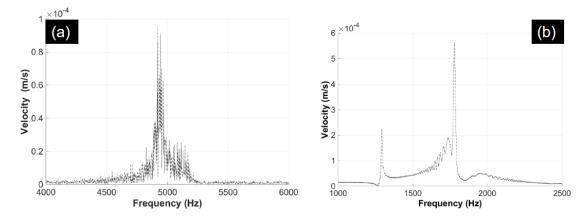

Figure 2.12 shows velocity response in the measured frequency domain for the free end of the *M-shape* and *M-long* devices when investigated under an electrical signal. In the first graph, Figure 2.12(a), the response is recorded under a Gaussian white of amplitude 0.1 V across a frequency spectrum of 3.5 kHz. The first eigenfrequency of the design is measured at around 5000 Hz. It can be assumed that this is the eigenfrequency of the unreleased structure.

The second graph in Figure 2.12(b) shows the *M*-long device under a periodic chirp signal of 0.1 V across 3.5 kHz. The first two eigenfrequencies are measured at 1294 Hz and 1781 Hz. The shift in resonance peaks can possibly be due to over-etching of the proof masses; it still remains to be investigated. An interesting phenomenon in the graph is the presence of bandwidth of frequencies that oscillate at a measurable velocity between the two natural frequencies. This is the effect of using a 2DOF design that the device is stressed even at frequencies away from its eigenfrequencies due to its coupling mechanism. However, the coupling is not the only possible explanation for the shape of the response - and a simulation or model calculation of the shape of the frequency response is needed to draw further conclusions.

Figure 2.11: LDV setup for the vibration measurement experiments

Figure 2.12: Characterization of *M-shape* and *M-long* in a LDV setup in different excitation signals. (a) *M-shape* under a gaussian white noise signal of 0.1 V amplitude. (b) *M-long* under a periodic chirp voltage signal of 0.1 V.

# **Chapter 3**

# **Microsupercapacitors (MSCs)**

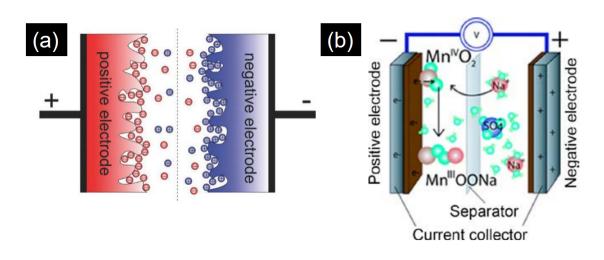

As discussed in chapter 1, supercapacitors are energy storage devices that are essential for realizing an on-chip power supply. Supercapacitors generally utilize formation of capacitors at the electrode-electrolyte interface in the presence of a potential difference. The electrode material is a conductive film, sheet, or group of particles that have a large surface area for the interaction with the electrolyte. The electrolyte is a solution that can form ionic charges when a potential difference gives rise to an electric field in them. In the presence of a potential difference, the electrode atoms interact with the electrolyte atoms. This electrostatic interaction between the atoms leads to the formation of nano-capacitors with  $d \approx nA$  [70]. These capacitors in parallel configuration lead to a substantial capacitance at the electrode-electrolyte interface. It is generally considered in the literature that these interacting molecules form an electric double layer (EDL) at the electrode-electrolyte interface. Helmholtz discovered this phenomenon for the first time in 1853 [71]. The studies by Guoy-Chapman in 1910 and 1913 [72] and later on Stern in 1924 [73], improved the theory of EDL charge storage further. The stored charge is then used to power the sensor node or the electronic unit connected to the output of the on-chip power storage unit. A supercapacitor has three main principles of storing charge - the electric double layer (EDL), pseudocapacitive, or a hybrid of the two. Figure 3.1 shows the schematic representation of the two mechanisms.

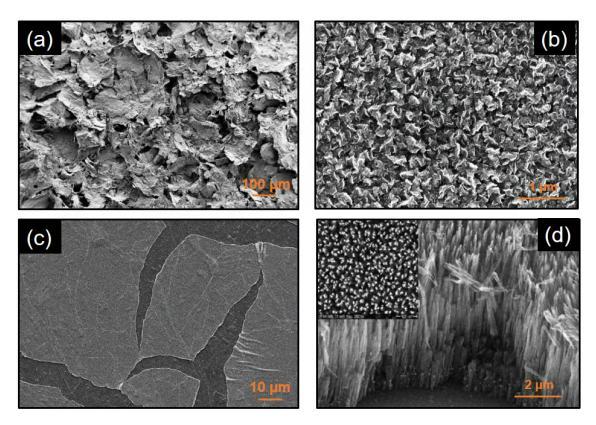

In EDLCs, charge storage takes place electrostatically (non-Faradaic) i.e., no shifting of charge takes place between electrode and electrolyte (which makes them highly reversible along with high cycling stability). Pseudocapacitance is another form of charge delivery in supercapacitors. In this case, the electrode stores charge through electrosorption, intercalation, and oxidation/reduction reactions between the electrode and electrolyte. Both these forms require a high surface area of interaction between the electrode and electrolyte. Thus, we can say that the choice of electrode material is mainly dependent on its specific surface area. Also, for a better capacitor formation at the interface, the electrolyte ion size should be equivalent to the pore size in the electrodes [70].

Supercapacitors are generally manufactured in the form of coin cells or box-like configuration. Coin cells are circular coin-shaped current collectors that also form the casing of the electrodes and electrolytes in the form of a cylindrical shell. The electrodes are cut out in the form of circular films to fit into each end of the coin cell. The electrolyte

Figure 3.1: Schematics of (a) EDL and (b) Pseudocapacitive mechanisms for charge storage in supercapacitors [74]. Images are reproduced after permission from the publishers.

is then introduced in the system through a separator, a porous non-conducting film that allows transportation of ionic charges across its interface. The coin cell is sealed using a packing glue. These coin cells can be connected either in series or parallel depending on the requirements of the device that needs to be powered. The second configuration is the box-type assembly, where a rectangular box is used instead of the circular shaped current collector[75]. Both these designs have been commercially manufactured and are being used in high power applications in conjunction with batteries [76].

However, these supercapacitors generally require a large volume and specialized manufacturing techniques that make them hard to be integrable in microsystem electronics technology. Therefore, developing CMOS compatible fabrication processes has attracted much attention over the past few years [26, 27, 28, 29, 30]. Miniaturized supercapacitors, also referred to as microsupercapacitors (MSCs), are small enough to be integrated into electronic devices. Kim et al. [77] first conceptualized an MSC using a thin film capacitor with W-RuO<sub>2</sub> electrodes . Further, Yang [78] fabricated wire-like MSCs in 2007. These studies have now expanded quite much since the integration of micromachining techniques in fabricating these devices. These devices can be integrated either as self-powering systems with charging through energy harvesters, or enhanced micro battery systems where they act as hybrid devices with batteries to improve the lifetime of a device. MSCs are devices that are generally fabricated on a substrate using MEMS technology. These devices are emerging as strong candidates for energy storage units in conjunction with micro-batteries due to various reasons. Firstly, they can be easily integrated into on-chip integrated circuits and secondly, they are cheap to manufacture as MEMS technology can be used to fabricate several devices on a single substrate while using a standardized process. However, we require optimization of such advantages for MSC integration into pre-existing MEMS and CMOS processes. In the next few sections, we are going to discuss the MSCs in more detail. We will first discuss a brief literature survey of the field and describe the advantages/disadvantages of different MSC fabrication techniques. Next, we shall talk about the electrodes materi-

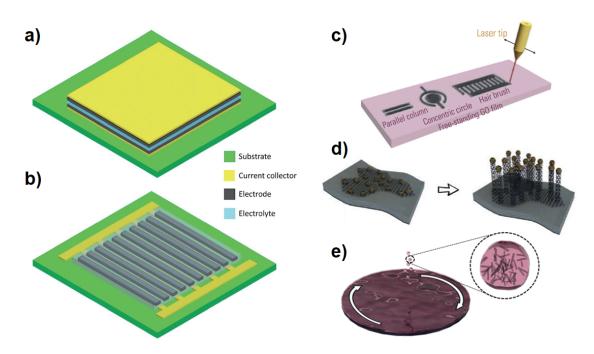

Figure 3.2: Types of MSC designs (a) stacked and (b) planar [79]. Methods for electrode deposition (c) laser scribing [79], (d) chemical vapor deposition for CNFs and VACNS [80], (e) spin coating of carbon based solutions (Paper 3. Images are reproduced after permission from the publishers.

als that can be utilized in a CMOS-compatible fabrication process. In section 3.1, we shall discuss the fabrication methods of CMOS-compatible processes, and subsequent issues in fabrication. Then we shall discuss the results from these fabrication processes. Finally, we shall talk about the optimization process performed and its effect on the electrochemical performance of the devices.

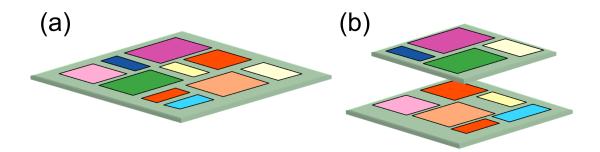

# 3.1 Device design

There are two main configurations for MSC fabrication – stacked and planar (Figure 3.2(a,b)). Stacked MSCs are sandwich-type structures with an electrolyte between two electrodes, while planar MSCs are devices with two in-plane electrodes separated by a specific distance. A planar MSC design holds several advantages over the stacked structure. Firstly, since the planar electrodes are on the same substrate, the side-by-side interactions of the electrolyte with electrodes results in an improved rate performance. Secondly, fabrication of the planar structure through microfabrication can allow us to accurately control the spacing between the two electrodes, leading to high ion transport across the two terminals. Moreover, the stack of electrodes, electrolytes, and current collectors would require specific masking techniques in the fabrication process, leading to a challenging list of process steps. Thus, for high-performance planar MSCs, it is imperative to have an electrode deposition technique that results in thicker electrodes and ensures that the deposited film can sustain and withstand post-processing lithography and device integration steps. A variety of methods can be used to fabricate thin films of

these materials [81].

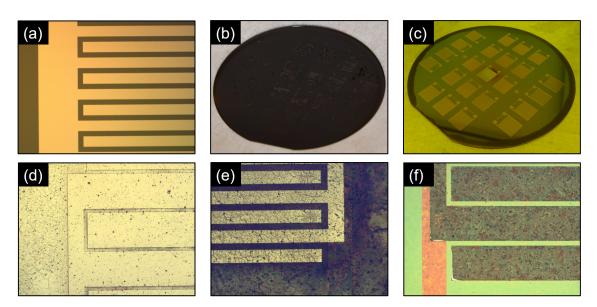

Figure 3.2(c-e) show the different fabrication processes that are generally used to deposit, etch, or grow the electrode structures onto planar substrates. Among these, we will mainly discuss the possible techniques utilized for CMOS compatible integration, namely - laser scribing, ink-jet printing, photolithography, and chemical vapor deposition.

#### 3.1.1 Laser scribing

Laser scribing, as shown in Figure 3.2(c), is a method to develop MSCs in a simple, costeffective, and scalable way. Its concept is to irradiate graphite oxide with a laser beam to convert it into graphene through a photothermal effect. This ability of reduction makes it feasible for direct patterning of electrodes on any form of substrates. It is also possible to fabricate both planar and stacked MSCs through this process.

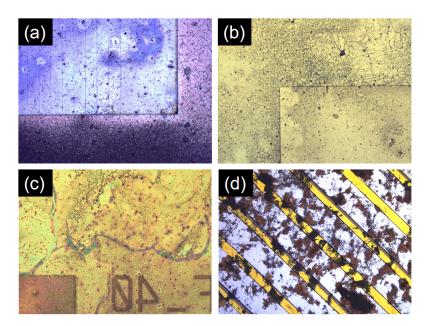

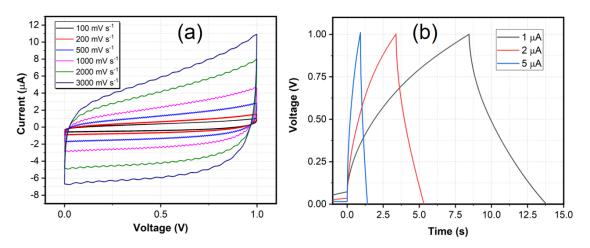

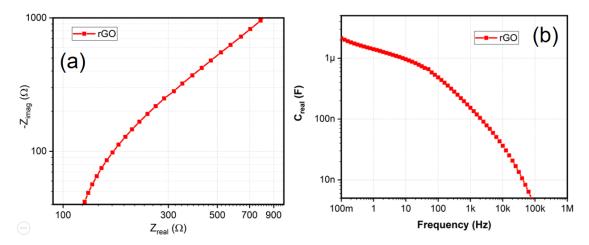

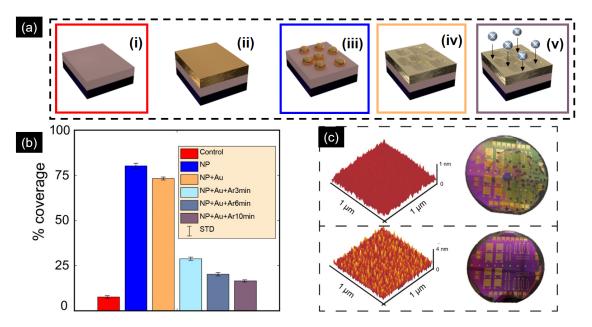

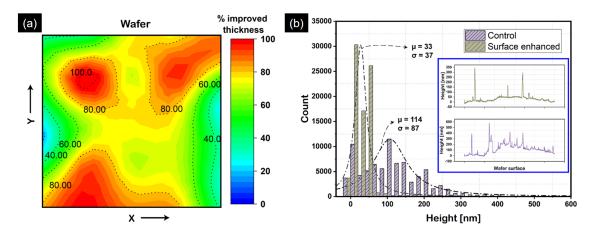

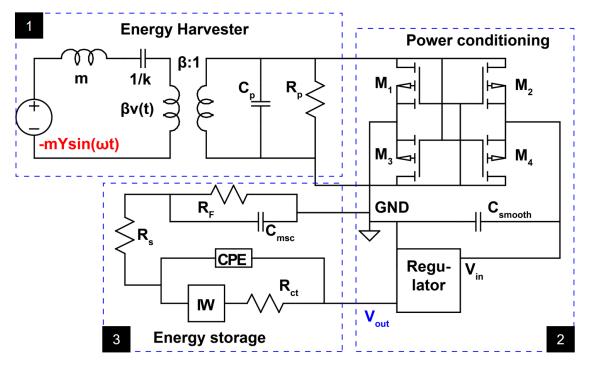

In some cases, direct laser reduction of GO to graphene sheets can be performed by a LightScribe DVD optical drive [82, 83, 84]. The films that were produced were mecahnically robust. They also showed a high electrical conductivity. The authors claimed that these films can be used directly on a substrate without requiring binders or current collectors. These electrodes were fabricated on flexible substrates such as nitrocellulose membrane, photocopy paper, or conductive Al foil. The devices demonstrated a high power density and excellent cyclic stability. Later, Wen et al. [85] improved the performance of LSG by combining it with a coated layers of GO/carbon nanotubes (CNTs) hybrid powders on flexible polyethylene terephthalate (PET) sheets. In the presence of CNTs with a smaller diameter, the laser-scribed CNT combination of electrodes is yeilds a better electrochemical performance. These devices were integrated with solar cells to demonstrate the feasibility of using MSCs as energy storage units for an on-chip power supply [86].