# Falsification of Signal-Based Specifications for Cyber-Physical Systems

with applications from the automotive domain

# Johan Lidén Eddeland

Department of Electrical Engineering Chalmers University of Technology Göteborg, Sweden, 2019

#### Falsification of Signal-Based Specifications for Cyber-Physical Systems with applications from the automotive domain

Johan Lidén Eddeland

Copyright © 2019 JOHAN LIDÉN EDDELAND All rights reserved.

This thesis has been prepared using LATEX.

Department of Electrical Engineering Chalmers University of Technology SE-412 96 Göteborg, Sweden Phone: +46 (0)31 772 1000 www.chalmers.se

Printed by Chalmers Reproservice Göteborg, Sweden, December 2019 To Hanna

# Abstract

In the development of software for modern Cyber-Physical Systems, testing is an integral part that is rightfully given a lot of attention. Testing is done on many different abstraction levels, and especially for large-scale industrial systems, it can be difficult to know when the testing should conclude and the software can be considered correct enough for making its way into production.

This thesis proposes new methods for analyzing and generating test cases as a means of being more certain that proper testing has been performed for the system under test. For analysis, the proposed approach includes automatically finding how much a given test suite has executed the physical properties of the simulated system.

For test case generation, an up-and-coming approach to find errors in Cyber-Physical Systems is *simulation-based falsification*. While falsification is suitable also for some large-scale industrial systems, sometimes there is a gap between what has been researched and what problems need to be solved to make the approach tractable in the industry. This thesis attempts to close this gap by applying falsification techniques to real-world models from Volvo Car Corporation, and adapting the falsification procedure where it has shortcomings for certain classes of systems. Specifically, the thesis includes a method for automatically transforming a signal-based specification into a formal specification in temporal logic, as well as a modification to the underlying optimization problem that makes falsification more viable in an industrial setting.

The proposed methods have been evaluated for both academic benchmark examples and real-world industrial models. One of the main conclusions is that the proposed additions and changes to analysis and generation of tests can be useful, given that one has enough information about the system under test. It is difficult to provide a general solution that will always work best – instead, the challenge lies in identifying which properties of the given system should be taken into account when trying to find potential errors in the system.

**Keywords:** Testing, Simulation-Based Verification, Falsification, Cyber-Physical Systems.

# List of Publications

This thesis is based on the following publications:

[A] J. Eddeland, J.G. Cepeda, R. Fransen, S. Miremadi, M. Fabian and K. Åkesson, "Automated Mode Coverage Analysis for Cyber-Physical Systems Using Hybrid Automata". *The 20th World Congress of the International Federation of Automatic Control*, 2017, Toulouse, France

[B] **J. Eddeland**, S. Miremadi, M. Fabian and K. Åkesson, "Objective Functions for Falsification of Signal Temporal Logic Properties in Cyber-Physical Systems". *13th IEEE Conference on Automation Science and Engineering (CASE)*, 2017, Xi'an, China.

[C] K. Claessen, N. Smallbone, **J. Eddeland**, Z. Ramezani and K. Åkesson, "Using Valued Booleans to Find Simpler Counterexamples in Random Testing of Cyber-Physical Systems". *14th Workshop on Discrete Event Systems* (WODES), 2018, Sorrento Coast, Italy.

[D] J. Lidén Eddeland, K. Claessen, N. Smallbone, Z. Ramezani, S. Miremadi and K. Åkesson, "Enhancing Temporal Logic Falsification with Specification Transformation and Valued Booleans". Submitted for possible journal publication.

[E] J. Lidén Eddeland and K. Åkesson, "A Case Study of Optimization Solvers and Objective Functions for Falsification of Cyber-Physical Systems". Submitted for possible conference publication.

### Acknowledgments

First of all, I would like to thank my supervisors Knut Åkesson and Sajed Miremadi for always giving me the support I need in my doctoral studies. During times when I have struggled, you have always helped me with encouraging words and fruitful discussions, all of which has contributed greatly to this thesis. Thanks also goes to my assistant supervisor Martin Fabian, who always helps me with proofreading and specifying the theoretical concepts of my research.

I also want to thank everyone I have worked with at Volvo for making it a good workplace for me. Specifically, I want to thank my first manager Isak Öberg for all the help during the start of my time as a PhD student. Andreas Andersson has always been available for good discussion on technical details, and Ulf Eliasson and Johan Alenius have helped me out with specific issues more times than I can count. Team MM and Team Red have always contributed to a great experience at work.

I am thankful to everyone at Chalmers who help make it a good working environment as well, especially the Automation group and the other industrial PhD students whom I share my office with. I am also very grateful to Koen Classen and Nicholas Smallbone for taking their time to discuss interesting concepts with me. I would also like to show my deep appreciation to Alexandre Donzé, who always helps me to solve different problems even though my questions are not always well-posed.

This research has been performed as part of Volvo Cars Industrial PhD Program (VIPP). The work has been performed with support from the Swedish Governmental Agency for Innovation Systems (VINNOVA) project TESTRON 2015-04893 and from the Swedish Research Council (VR) project SyTeC 2016-06204. I gratefully acknowledge this support.

Finally, I want to thank my family who have endured me from the very beginning. I express my gratitude to my parents and brothers for their continuous love and support. The one who remains to be mentioned is the one who I could not live without: my wife Hanna. Coming home from work every day to you and our sons Vidar and Sixten makes me the happiest person in the world. Thank you for your endless patience and love, I will try to match it for the rest of our lives!

# Acronyms

| CI:    | Continuous Integration               |

|--------|--------------------------------------|

| CPS:   | Cyber-Physical System                |

| MBT:   | Model-Based Testing                  |

| MC/DC: | Modified Condition/Decision Coverage |

| SMT:   | Satisfiability Modulo Theories       |

| SUT:   | System Under Test                    |

# Contents

| AI | ostrad            | :t                                           | i  |  |  |  |  |

|----|-------------------|----------------------------------------------|----|--|--|--|--|

| Li | List of Papers ii |                                              |    |  |  |  |  |

| A  | know              | vledgements                                  | v  |  |  |  |  |

| Ad | crony             | ms                                           | vi |  |  |  |  |

|    |                   |                                              |    |  |  |  |  |

| I  | 0                 | verview                                      | 1  |  |  |  |  |

| 1  | Intr              | oduction                                     | 3  |  |  |  |  |

|    | 1.1               | Testing in industry                          | 6  |  |  |  |  |

|    |                   | Levels of testing                            | 6  |  |  |  |  |

|    |                   | Continuous integration                       | 8  |  |  |  |  |

|    | 1.2               | Thesis outline                               | 8  |  |  |  |  |

| 2  | Soft              | ware testing                                 | 11 |  |  |  |  |

|    | 2.1               | Model checking versus testing                | 11 |  |  |  |  |

|    | 2.2               | Coverage criteria                            | 12 |  |  |  |  |

|    |                   | Coverage criteria for Cyber-Physical Systems | 14 |  |  |  |  |

|    | 2.3               | Random testing                               | 14 |  |  |  |  |

|    |                   |                                              |    |  |  |  |  |

| 3  | Opt           | imization-based testing of cyber-physical systems                        | 17 |  |

|----|---------------|--------------------------------------------------------------------------|----|--|

|    | 3.1           | Cyber-Physical Systems                                                   | 17 |  |

|    |               | Requirements of CPSs                                                     | 18 |  |

|    | 3.2           | Discrete-time signals                                                    | 20 |  |

|    | 3.3           | Signal temporal logic                                                    | 20 |  |

|    |               | Robust satisfaction of STL formulas $\ldots \ldots \ldots \ldots \ldots$ | 21 |  |

|    | 3.4           | Falsification                                                            | 23 |  |

|    |               | Input generators                                                         | 25 |  |

|    |               | Robustness function                                                      | 25 |  |

|    |               | Parameter optimizer                                                      | 26 |  |

|    | 3.5           | Falsification example                                                    | 26 |  |

| 4  | Rela          | ted Work and Research Questions                                          | 29 |  |

|    | 4.1           | Related work                                                             | 29 |  |

|    |               | Signal Temporal Logic and Metric Temporal Logic                          | 29 |  |

|    |               | Falsification of Cyber-Physical Systems                                  | 30 |  |

|    | 4.2           | Research questions                                                       | 31 |  |

|    | 4.3           | Methodology                                                              | 33 |  |

|    |               | Method                                                                   | 34 |  |

|    |               | Analysis                                                                 | 35 |  |

|    |               | Limitations of the methodology                                           | 35 |  |

|    | 4.4           | Contributions                                                            | 35 |  |

| 5  | Sun           | nmary of included papers                                                 | 37 |  |

|    | 5.1           | Paper A                                                                  | 37 |  |

|    | 5.2           | Paper B                                                                  | 38 |  |

|    | 5.3           | Paper C                                                                  | 38 |  |

|    | 5.4           | Paper D                                                                  | 39 |  |

|    | 5.5           | Paper E                                                                  | 39 |  |

| 6  | Con           | cluding Remarks and Future Work                                          | 41 |  |

| Re | References 43 |                                                                          |    |  |

# II Papers

| Α             | Automated Mode Coverage Analysis for Cyber-Physical Systems |                                                                                            |                                                                                                  |                                                                                                                                                        |

|---------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                             | •••                                                                                        | rid Automata                                                                                     | A1                                                                                                                                                     |

|               | 1                                                           |                                                                                            | duction                                                                                          |                                                                                                                                                        |

|               | 2                                                           |                                                                                            | id Automata and the MC/DC Criterion                                                              |                                                                                                                                                        |

|               | 3                                                           | •                                                                                          | id Automata                                                                                      |                                                                                                                                                        |

|               | 4                                                           |                                                                                            | rage Criterion                                                                                   |                                                                                                                                                        |

|               |                                                             | 4.1                                                                                        | Mode coverage                                                                                    |                                                                                                                                                        |

|               |                                                             | 4.2                                                                                        | Comparison to other coverage definitions                                                         |                                                                                                                                                        |

|               | 5                                                           |                                                                                            | motive use case $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |                                                                                                                                                        |

|               |                                                             | 5.1                                                                                        | Introduction of the model                                                                        |                                                                                                                                                        |

|               |                                                             | 5.2                                                                                        | Generating the modes                                                                             |                                                                                                                                                        |

|               |                                                             | 5.3                                                                                        | Characteristics of generated modes                                                               |                                                                                                                                                        |

|               |                                                             | 5.4                                                                                        | Coverage results                                                                                 |                                                                                                                                                        |

| 6 Conclusions |                                                             |                                                                                            |                                                                                                  |                                                                                                                                                        |

|               | Refe                                                        | erences                                                                                    |                                                                                                  | A18                                                                                                                                                    |

| в             | Obje                                                        | ective                                                                                     | Functions for Falsification of Signal Temporal Logic                                             |                                                                                                                                                        |

|               | -                                                           |                                                                                            | in Cyber-Physical Systems                                                                        | B1                                                                                                                                                     |

|               | 1                                                           | Intro                                                                                      | duction                                                                                          | B3                                                                                                                                                     |

|               | 2                                                           |                                                                                            |                                                                                                  | 20                                                                                                                                                     |

|               |                                                             | Probl                                                                                      | em Overview                                                                                      |                                                                                                                                                        |

|               |                                                             | Probl<br>2.1                                                                               | em Overview                                                                                      | B5                                                                                                                                                     |

|               |                                                             |                                                                                            |                                                                                                  | B5 $B5$                                                                                                                                                |

|               |                                                             | 2.1                                                                                        | Falsification of temporal properties                                                             | B5<br>B5<br>B6                                                                                                                                         |

|               | 3                                                           | 2.1<br>2.2<br>2.3                                                                          | Falsification of temporal properties                                                             | B5<br>B5<br>B6<br>B8                                                                                                                                   |

|               | 3                                                           | 2.1<br>2.2<br>2.3                                                                          | Falsification of temporal propertiesGenerating inputs based on parametersExample                 | B5<br>B5<br>B6<br>B8<br>B9                                                                                                                             |

|               | 3                                                           | 2.1<br>2.2<br>2.3<br>Prelin                                                                | Falsification of temporal properties                                                             | B5<br>B5<br>B6<br>B8<br>B9<br>B11                                                                                                                      |

|               | 3                                                           | 2.1<br>2.2<br>2.3<br>Prelin<br>3.1                                                         | Falsification of temporal properties                                                             | B5<br>B5<br>B6<br>B8<br>B9<br>B11<br>B11                                                                                                               |

|               | 3                                                           | 2.1<br>2.2<br>2.3<br>Prelin<br>3.1<br>3.2<br>3.3                                           | Falsification of temporal properties                                                             | B5<br>B6<br>B8<br>B9<br>B11<br>B11<br>B12                                                                                                              |

|               |                                                             | 2.1<br>2.2<br>2.3<br>Prelir<br>3.1<br>3.2<br>3.3<br>Alter                                  | Falsification of temporal properties                                                             | B5<br>B6<br>B8<br>B9<br>B11<br>B11<br>B12<br>B13                                                                                                       |

|               | 4                                                           | 2.1<br>2.2<br>2.3<br>Prelir<br>3.1<br>3.2<br>3.3<br>Alter                                  | Falsification of temporal properties                                                             | B5<br>B6<br>B8<br>B9<br>B11<br>B11<br>B12<br>B13<br>B14                                                                                                |

|               | 4                                                           | 2.1<br>2.2<br>2.3<br>Prelin<br>3.1<br>3.2<br>3.3<br>Altern<br>Imple                        | Falsification of temporal properties                                                             | B5<br>B6<br>B8<br>B9<br>B11<br>B11<br>B12<br>B13<br>B14<br>B16                                                                                         |

|               | 45                                                          | 2.1<br>2.2<br>2.3<br>Prelin<br>3.1<br>3.2<br>3.3<br>Alter:<br>Imple<br>5.1                 | Falsification of temporal properties                                                             | <ul> <li>B5</li> <li>B6</li> <li>B8</li> <li>B9</li> <li>B11</li> <li>B11</li> <li>B12</li> <li>B13</li> <li>B14</li> <li>B16</li> <li>B16</li> </ul>  |

|               | 45                                                          | 2.1<br>2.2<br>2.3<br>Prelin<br>3.1<br>3.2<br>3.3<br>Altern<br>Imple<br>5.1<br>Use C        | Falsification of temporal properties                                                             | <ul> <li>B5</li> <li>B6</li> <li>B8</li> <li>B9</li> <li>B11</li> <li>B112</li> <li>B13</li> <li>B14</li> <li>B16</li> <li>B16</li> <li>B16</li> </ul> |

|               | 45                                                          | 2.1<br>2.2<br>2.3<br>Prelin<br>3.1<br>3.2<br>3.3<br>Altern<br>Imple<br>5.1<br>Use C<br>6.1 | Falsification of temporal properties                                                             | B5<br>B6<br>B8<br>B9<br>B11<br>B11<br>B12<br>B13<br>B14<br>B16<br>B16<br>B16<br>B17                                                                    |

| С | Using Valued Booleans to Find Simpler Counterexamples in Ran-<br>dom Testing of Cyber-Physical Systems C1 |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | aon<br>1                                                                                                  |                                                                                                       | g of Cyber-Physical Systems C1<br>uction                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|   | 1                                                                                                         | 1.1                                                                                                   | Related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|   |                                                                                                           | 1.1                                                                                                   | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   | 2                                                                                                         |                                                                                                       | $\begin{array}{c} \text{contributions} & \dots & $                                                                                                                                                                                                                                                                                                                                                                                 |  |

|   | 2                                                                                                         | 2.1                                                                                                   | The model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|   |                                                                                                           | 2.1<br>2.2                                                                                            | Testing and shrinking with QuickCheck                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   |                                                                                                           | 2.2<br>2.3                                                                                            | Falsification with Breach                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|   | 3                                                                                                         | -                                                                                                     | ach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|   | 0                                                                                                         | 3.1                                                                                                   | Valued Booleans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|   |                                                                                                           | 3.2                                                                                                   | Comparison with Signal Temporal Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   | 4                                                                                                         | -                                                                                                     | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   | -                                                                                                         | 4.1                                                                                                   | The heater example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|   |                                                                                                           | 4.2                                                                                                   | Automatic transmission example                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|   | 5                                                                                                         | Conclu                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|   | Refe                                                                                                      | erences                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|   |                                                                                                           |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| D | Enh                                                                                                       | ancing                                                                                                | Temporal Logic Falsification with Specification Trans-                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|   |                                                                                                           | -                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|   | forn                                                                                                      | -                                                                                                     | and Valued Booleans D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|   | forn<br>1                                                                                                 | nation a                                                                                              | Ind Valued Booleans     D1       uction     D3                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|   |                                                                                                           | nation a                                                                                              | D1       uction     D3       Related work     D4                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|   |                                                                                                           | nation a<br>Introd                                                                                    | Ind Valued Booleans     D1       uction                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|   |                                                                                                           | nation a<br>Introd<br>1.1<br>1.2                                                                      | And Valued BooleansD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1                                                     | And Valued BooleansD1uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2                                              | And Valued BooleansD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD6Signal Temporal LogicD7                                                                                                                                                                                                                                                                                                                                                         |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3                                       | DuctionD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD6Signal Temporal LogicD7FalsificationD7                                                                                                                                                                                                                                                                                                                                                      |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3                                       | And Valued BooleansD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD6Signal Temporal LogicD7                                                                                                                                                                                                                                                                                                                                                         |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3                                       | DuctionD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD6Signal Temporal LogicD7FalsificationD7                                                                                                                                                                                                                                                                                                                                                      |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3<br>Signal                             | And Valued BooleansD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD7FalsificationD7FalsificationD9                                                                                                                                                                                                                                                                                                                                                  |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3<br>Signal<br>3.1                      | DameD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD7FalsificationD7FalsificationD7Sased SpecificationsD9STL specifications in a signal-based frameworkD10                                                                                                                                                                                                                                                                                          |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3<br>Signal<br>3.1<br>3.2               | Ond Valued BooleansD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD7FalsificationD7FalsificationD7Based SpecificationsD9STL specifications in a signal-based frameworkD10Signal-based specifications expressed in STLD11                                                                                                                                                                                                                            |  |

|   | 1                                                                                                         | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3<br>Signal<br>3.1<br>3.2<br>3.3<br>3.4 | DuctionD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD7FalsificationD7FalsificationD9STL specifications in a signal-based frameworkD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD10Signal-based specificationsD14 |  |

|   | 1<br>2<br>3                                                                                               | nation a<br>Introd<br>1.1<br>1.2<br>Signal<br>2.1<br>2.2<br>2.3<br>Signal<br>3.1<br>3.2<br>3.3<br>3.4 | Ond Valued BooleansD1uctionD3Related workD4ContributionsD5Temporal Logic and FalsificationD6Discrete-time signalsD6Signal Temporal LogicD7FalsificationD7Based SpecificationsD9STL specifications in a signal-based frameworkD10Signal-based specifications expressed in STLD11Recursive loops in specificationsD14When semantics do not matchD17                                                                                                                                                  |  |

|   |      | 4.3    | Properties for reasoning about Valued Booleans D22          |

|---|------|--------|-------------------------------------------------------------|

|   |      | 4.4    | Other properties of VBools                                  |

|   | 5    | Result | s and Discussion                                            |

|   |      | 5.1    | Automatic Transmission Benchmark                            |

|   |      | 5.2    | Abstract Fuel Control Benchmark                             |

|   |      | 5.3    | Third Order $\Delta - \Sigma$ Modulator                     |

|   |      | 5.4    | Static Switched System D32                                  |

|   |      | 5.5    | Transforming Volvo requirements to STL D33                  |

|   |      | 5.6    | Discussion                                                  |

|   | 6    | Conclu | 1sions                                                      |

|   |      | 6.1    | Future work                                                 |

|   | Refe | rences |                                                             |

| _ |      |        |                                                             |

| Ε |      |        | udy of Optimization Solvers and Objective Functions         |

|   |      |        | tion of Cyber-Physical Systems E1                           |

|   | 1    |        | uction                                                      |

|   |      | 1.1    | Related work                                                |

|   | ~    | 1.2    | Contribution                                                |

|   | 2    |        | inaries E5                                                  |

|   |      | 2.1    | Discrete-time signals                                       |

|   |      | 2.2    | Signal Temporal Logic                                       |

|   |      | 2.3    | Robust semantics for STL                                    |

|   | _    | 2.4    | Falsification                                               |

|   | 3    |        | imental setup and results                                   |

|   |      | 3.1    | Optimization solvers                                        |

|   |      | 3.2    | Automatic Transmission Benchmark                            |

|   |      | 3.3    | Third Order $\Delta - \Sigma$ Modulator                     |

|   |      | 3.4    | Static Switched System                                      |

|   |      | 3.5    | Discussion                                                  |

|   | 4    |        | sions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |

|   | Refe | rences | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                      |

|   |      |        |                                                             |

# Part I Overview

# CHAPTER 1

### Introduction

When we as humans create something, it is usually a process of trial and error. "Rome was not built in a day" is a proverbial saying that can suggest both that great things take a long time to finish, but perhaps also that there will be mistakes made along the way. Developing modern software is no exception, which means that we need to systematize how to catch the errors so that they do not exist in the final product.

This thesis tackles the problem of testing software. Specifically, techniques to increase the level of automation in testing of Cyber-Physical Systems (CPSs) are presented, in an effort to find bugs or errors without creating much additional work effort for the engineers designing the system. A CPS is, as the name suggests, a system which consists of both *cyber* and *physical* properties – meaning that there is some software interacting with actual physical components. Some examples of CPSs are cars, industrial robots, and advanced medical devices. A CPS is considered a *hybrid* system in the sense that it contains both discrete and continuous elements.

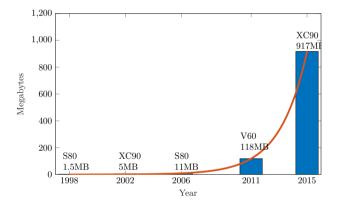

To efficiently develop modern CPSs, a common design paradigm is to use models. A model in this case is a mathematical description of the inner workings of the CPS, and the model can be defined for different levels of abstraction. For example, a simple model of a car could simply define how a point mass accelerates forward as a function of how hard the driver pushes the gas pedal. However, a more detailed model could take into account the friction between the car and the road, the weight of the passengers in the car, the weather and air resistance around the car, and many other characteristics that determine how the car moves through space. Performing testing on models is naturally called Model-Based Testing (MBT). MBT typically involves much automatic testing and is becoming more and more useful as the software size in cars is increasing rapidly, which means that manual testing does not scale well enough time-wise to be viable for the future. For example, Figure 1.1 shows the historical downloadable software size in certain Volvo cars, which indicates that the software size is increasing approximately exponentially. This motivates introducing more automated testing as a complement to the manual testing which is usually already in place in development of modern CPSs.

Figure 1.1: A bar chart of the downloadable software size in certain Volvo car models during the years 1998 - 2015.

To test the models that are being developed, one must define what needs to be tested. This is done by defining a *specification*, *i.e.*, the desired behaviour of the system. A specification can be written in natural language, *e.g.* "*The car's velocity should be lower than 150 km/h*", or in some more mathematical way, *e.g.* "v < 150". The output of the system given a certain input, a *test case*, can then be evaluated against the specification to see if the test case has passed or failed.

An important and difficult question is how to create new test cases for the System Under Test (SUT). Generating a test case for a model of a CPS typically means coming up with inputs to a simulation of the closed-loop system including both software and the physical components of the system. In the end, the tests are created to find faults if they exist in the system (testing can never prove absence of errors in the system), but there are different approaches to guide the generation to this end. One approach is to consider *code coverage* of the software being tested. As an example, consider the pseudo-code below.

```

if a then

x = x + 1

else

x = x - 1

end if

```

#### If one wants full statement coverage of the given code, all statements need to be executed, meaning that *a* needs to take on both values true and false (for example in a *test suite*, a collection of test cases). There are many types of coverage other than statement coverage, for example branch coverage and decision coverage, but the main idea of a coverage criterion is to give a number indicating how much of the structure of the code that has actually been tested.

Another approach to generate new test cases is via optimization-based testing (or *falsification*) of CPSs. This approach formulates the problem of generating test cases as an optimization problem, where the objective function measures how far a formal specification is from being falsified, *i.e.*, not being fulfilled. To be clear, whenever falsification is mentioned in this thesis, it refers to the specific optimization-based method of finding counterexamples to temporal logic specifications of CPSs.

No matter which test method is considered, it is clear that testing attracts many practitioners from both academia as well as industry. It is however also clear, as in most research areas, that methods developed in academical contexts are not always found in industry. In other words, there is a discrepancy in methods developed by researchers and methods used in industry. This thesis attempts to diminish this discrepancy by adapting academical methods to be suitable for industrial models as well as academical ones.

# 1.1 Testing in industry

Testing in an industrial context often becomes difficult because of the sheer scale of software development. When several hundred engineers work together to develop (a part of) a CPS, for example a component in a car, there are typically different levels of testing performed. It is also common to introduce different automatic methods for faster and more reliable software development. One of these methods is *Continuous Integration* (CI), which is detailed later in this section.

#### Levels of testing

As part of a Model-Based Design approach, the testing levels can include, but are not limited to:

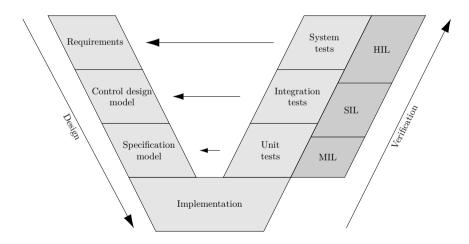

- Model-in-the-Loop (MIL): The software component(s) to be tested are modeled and simulated (meaning that no explicit code is written, rather the software components are created using a model language, for example Modelica or Simulink). The plant, *i.e.*, the physical part of the system which the software interacts with, is also simulated.

- Software-in-the-Loop (SIL): The modeled software (or *controller*) is code-generated, and then this generated code is tested against a simulated plant.

- Hardware-in-the-Loop (HIL): Some component(s) of the actual hardware are used in the testing, while some of the plant is still being simulated.

The final stage of testing is to physically test the entire system, for example by driving the finished car and trying to evaluate whether all the requirements on the system are fulfilled. The earlier testing phases presented here are the ones that are cheapest and easiest to scale. For MIL and SIL testing, since everything is simulated, the only limiting factor in creating and evaluating new test cases is computational power. For HIL testing, since there is an actual hardware component interacting with the software, the testing needs to be performed in real time, typically also with additional safety measures since parts could potentially catch fire or be part of similar hazards. In this thesis, the main focus is on testing environments where the whole system is simulated, *e.g.* MIL and SIL testing. It should still be noted that all different testing environments are vital for complete testing of the CPS, as MIL and SIL testing for example cannot capture any hardware problems. Similarly, for a car there are certain aspects that can only be tested by actual driving of the car and not in HIL testing.

There is also another aspect of testing in the software development process. When a software component is created, typically the software developer will create *unit tests* to verify that the component works as expected by itself. When several software components are created, the next step is for them to be connected to each other as part of the functionality of the system. Now testing needs to be performed to validate that the interface and interaction between the components work as expected – this is called *integration testing*. When all different parts of the final system are connected, the final testing stage is called *system testing*. Figure 1.2 shows how MIL, HIL and SIL testing can be related to unit, integration and system testing in an interpretation of the V model of software development.

Figure 1.2: An illustration of how MIL, SIL, and HIL testing can be related to unit, integration, and system testing in the V model of software development. Even though each of the testing levels come sequentially in the testing process, there is not a 1:1 correspondence between (for example) MIL/Unit, SIL/Integration, or HIL/System.

#### **Continuous integration**

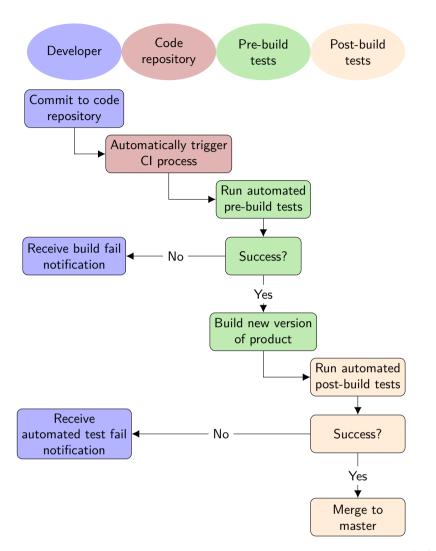

A common way to incorporate testing in industry is to use Continuous Integration (CI). CI is the practice of automatically merging developed code often, in order to more frequently find smaller faults rather than having to fix large errors with many potentially complex causes at larger time intervals. An overview of a typical CI workflow is shown in Figure 1.3.

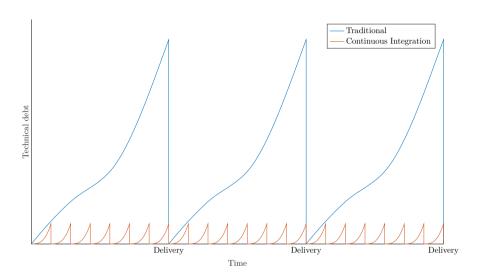

A sketch of the desired effect of CI, in terms of time spent finding and correcting errors in the developed software, can be seen in Figure 1.4. It is clear that in the ideal case, it is easier to find bugs when there are few of them and there are not many different versions of the software to check against. However, implementing CI also requires writing of automated tests and a general change in the way of working (compared to not using CI). As this thesis is focused on automated testing, it can be seen as part of making a CI chain work.

### 1.2 Thesis outline

The thesis is divided into two parts. In the first part, an overview is presented to give the reader the understanding needed for the papers appended in the second part.

**Chapter 2** contains a brief overview of why to perform testing for the software that is part of CPSs. There are also presentations of coverage criteria (needed for understanding Paper A) and random testing (needed for Paper C and Paper D).

**Chapter 3** is about optimization-based testing of CPSs. In this chapter the falsification process is detailed, including a definition of Signal Temporal Logic for discrete-time signals. These definitions are useful for understanding papers B, D, and E.

**Chapter 4** first includes a summary of related and recent work in related research areas. It also contains the research questions, the methodology, and the main contributions of the thesis.

Chapter 5 summarizes the content of the appended papers.

**Chapter 6** contains a conclusion of the work presented in the thesis, and also an outlook on the future work to be done.

Figure 1.3: A flowchart including typical elements of continuous integration (CI). When a developer pushes their code, the code needs to be built and pass both unit tests and other automated tests before being pushed to the master branch. If the code does not build, or if it fails any tests, the developer will be notified and needs to change the code before trying to push again. In the context of this figure, pre-build tests could be unit tests, while post-build tests could be integration tests.

Figure 1.4: A sketch of intended technical debt over time using traditional development methods versus continuous integration. Committing the developed code with high frequency typically also means that the faults are easier to find and less time-consuming to fix.

# CHAPTER 2

### Software testing

This chapter gives a short insight into what software testing is, and the different kinds of software testing that are related to this thesis. In Section 2.1, there is a brief discussion about why testing is a reasonable approach to verifying behaviour of CPSs. Section 2.2 discusses coverage criteria for testing and how they are used in industry. In Section 2.3, random testing is presented.

# 2.1 Model checking versus testing

An approach to verify correctness of programs is model checking [1]. Model checking is exhaustive, meaning that if there is an error in the model with regards to the specification, a model checking algorithm that finishes will find it [2]. While this sounds appealing, model checking techniques have limitations and are not possible to use for general industrial CPSs. In fact, the general problem of verifying properties for hybrid systems, *i.e.*, systems with both discrete and continuous dynamics, is undecidable [3]. This means that it has been proven that in the general case, no algorithm can decide whether a certain property for a hybrid system holds or does not hold. In addition to this, while model checking methods are very useful for models without the limitations discussed here, there are several other obstacles to overcome [4] for model checking to be viable in industry (the most notable being a lack of experience in industry in formalizing the models and specifications to be checked).

With this in mind, we turn to testing instead. Testing is non-exhaustive, meaning that no matter how long we test, we can not *prove* the absence of bugs, but testing can still raise the confidence in the correctness of the final product. Testing is scalable and usable for complex industrial-sized systems, making it suitable for the research presented in this thesis which is close to application.

# 2.2 Coverage criteria

Testing the inner structure of the SUT is called white-box testing, while testing the system behaviours without considering the inner workings of the SUT is called black-box testing. If the scope is to perform white-box testing, one may be interested in looking at different code coverage criteria for evaluating if the test cases have tested the system appropriately or not. For examples of some common coverage criteria, consider the simple example below.

```

1: if (a and b) or c then

2: x = x + 1

3: else

4: x = x - 1

5: end if

```

To fulfill statement coverage, every statement needs to be executed by the test suite. To fulfill branch coverage, every branch of the program needs to be executed. In this case, there are two branches; the "if" branch (row 2) and the "else" branch (row 4), which means that "(a and b) or c" has to evaluate to true at least once and false at least once in the test suite.

Fulfilling decision coverage is sometimes defined as fulfilling branch coverage, and sometimes as making sure that every point of entry and exit in the program has been invoked at least once as well as that every decision in the program has taken all possible outcomes at least once [5]. A decision is a Boolean expression composed of *conditions* and zero or more Boolean operators, where a condition is a Boolean expression containing no Boolean operators. In the given example, "(a and b) or c" is a decision, while "a", "b" and "c" are conditions.

Another coverage criterion that covers more than the ones mentioned above is *Modified Condition/Decision Coverage* (MC/DC). MC/DC is especially interesting because it is used widely in industry to validate test suites, and because MC/DC is highly recommended for ASIL D (the highest classification of *Automotive Safety Integrity Level*) in ISO 26262 [6]. MC/DC requires all of the following:

- 1. Every point of entry and exit in the program has been invoked at least once.

- 2. Every condition in a decision in the program has taken all possible outcomes at least once.

- 3. Every decision in the program has taken all possible outcomes at least once.

- 4. Each condition in a decision has been shown to independently affect that decision's outcome. A condition is shown to independently affect a decision's outcome by varying just that condition while holding fixed all other possible conditions.

Below is a short analysis of what is needed to fulfill each of the points of MC/DC for the given code example.

- 1. To fulfill the first point, branches of the **if**-statement need to be exited, meaning that "(a and b) or c" needs to evaluate to true at least once, and false at least once.

- 2. To fulfill the second point, each condition (a, b and c) must be true at least once, and false at least once.

- 3. To fulfill the third point, it is enough for this example to fulfill the same things as the first point since there is only one decision present.

- 4. To fulfill the fourth point is the trickiest. Consider the two cases below

a = true, b = true, c = truea = false, b = false, c = false These inputs fulfill the first three points, but they do not fulfill the fourth point. The reason is that for both of these cases, none of the conditions a, b or c independently affect the decisions outcome. Instead, an example of cases required to fulfill MC/DC are shown below (where conditions in **bold** can be shown to independently affect the decisions outcome by keeping the other conditions fixed).

$\mathbf{a} = \mathbf{true}, \mathbf{b} = \mathbf{true}, \mathbf{c} = \mathbf{false}$  $\mathbf{a} = \mathbf{false}, \mathbf{b} = \mathbf{true}, \mathbf{c} = \mathbf{false}$  $\mathbf{a} = \mathbf{true}, \mathbf{b} = \mathbf{false}, \mathbf{c} = \mathbf{false}$

a = false, b = false, c = true

#### **Coverage criteria for Cyber-Physical Systems**

In the realm of testing Cyber-Physical Systems, different kinds of coverage criteria have also been considered to improve the testing procedure. One approach [7] uses the *star discrepancy* to measure how well-filled a set of points is. This is applied to the values of the continuous state variables in a test suite for the SUT, and the test generation algorithm presented uses start discrepancy as a guide.

In another work [8], the authors present several coverage metrics to be used as evaluation of a requirements-driven falsification tool. The proposed coverage metrics typically include information about the discrete states of the hybrid SUT.

# 2.3 Random testing

A testing technique relevant to this thesis is random testing (or randomized testing; the terms will be used interchangeably in this thesis). In random testing, the user supplies the testing tool with properties that need to be tested, and generators that define how the inputs to a program can be created [9] (at least for user-defined types where the testing tool cannot know how to generate data otherwise). Some different random testing techniques are *fuzz testing* [10], where faulty inputs are sent into a program to test its security, and *concolic testing* [11], where random inputs is combined with symbolic execution to easier find very specific path conditions leading to bugs in programs.

As an example of random testing, consider the following (faulty) implementation of a function to calculate the absolute value of a number.

```

function ABS(x)

if x > 0 then

return x

else

return x

end if

end function

```

$\triangleright$  Should be -x

Depending on the tool and the type defined for x, one might need to define a generator for x. For example, one alternative is that x should be any signed integer, another that x should be a double in the range [-100, 100]. For the sake of this example, we choose the second alternative as the input generator for x. A reasonable specification to test against for the absolute value could for example be  $\forall x \ x \ge 0$ . Very many test cases can be generated automatically, where the input of each test case is a random number according to the specified generator. Since approximately 50% of the generated input would fail the specification, the bug in the code would be found easily with random testing.

For the given example, the input is simply a random number, but input generation can easily be generalized to support *e.g.* random testing of simulated CPSs. For example, consider a model of a car, where the input defines how much to accelerate (a percentage of the full acceleration in the range [0, 100]). The input generator would then need to create a time-indexed vector, where for each time the input has a value in [0, 100]. Note, however, that it is probably not reasonable to simply generate a new random value for each time instance, independent of neighbouring values, as this would be an unrealistic scenario (nobody could push and release their foot on the accelerator pedal tens of times per second). To circumvent this, one could do one of the following (or a combination of both):

- Make sure that the input generator only generates smooth curves, *e.g.* by generating an appropriate start value and then randomly selecting a second derivative, which is then integrated twice to provide the final input (making sure that the twice integrated values are in the interval [0, 100]).

- Generate purely random values for each time, but *shrink* the generated

test case when a fail is found. Shrinking keeps simplifying the input of the test case as long as it keeps failing the specification, which could result in a physically reasonable input after the shrinking process finishes (for details, see e.g. [12]).

To summarize, random testing is a form of software testing that can be proficient at finding certain kind of bugs in code, given that the testing problem is set up properly. However, to automatically generate test cases for Cyber-Physical Systems requires several other considerations as well – something that is covered in more detail in Chapter 3.

# CHAPTER 3

# Optimization-based testing of cyber-physical systems

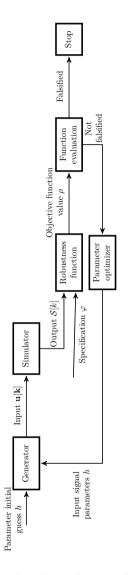

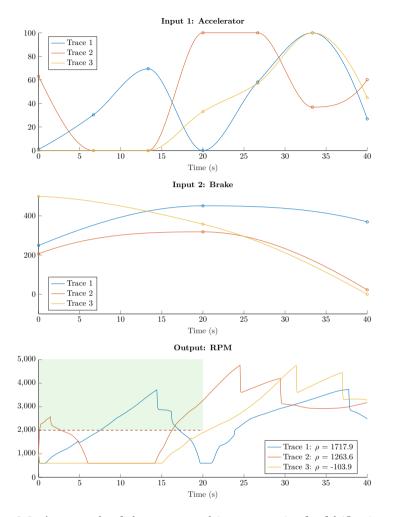

This chapter starts with a presentation of Cyber-Physical Systems in general and continues with the basics of falsification for CPSs. Falsification of CPSs is the main subject of papers B, C, D, and E. Included in this presentation is the definition of discrete-time signals, Signal Temporal Logic (STL), and the robust satisfaction of STL formulas. Finally, the whole falsification loop is summarized and explained in further detail.

# 3.1 Cyber-Physical Systems

Cyber-Physical Systems are systems that interact with the physical environment through the use of sensors (for acquiring information) and actuators (for affecting the physical surroundings) [13]. The main differences from mechatronic systems are that a CPS can be connected to and communicate with other CPSs, and a CPS consists of several different integrated subsystems [14]. As systems get larger and more complex, a CPS can be seen as part of the transition chain going from first a mechatronic system, then to a CPS, and then to a cloud-based system. As an example from the automotive domain, a drivetrain for a vehicle is considered a mechatronic system, while an entire car is considered to be a CPS.

#### **Requirements of CPSs**

CPSs are typically safety-critical, meaning that a failure in operation of the system can result in serious damage or injury. Therefore, there is much focus in research to make sure that CPSs conform to safety requirements<sup>1</sup> [15]. However, it is not trivial to formulate the requirements to be put on CPSs.

As an extended example, consider a hypothetical requirement on a specific CPS, namely a car. This is to help illustrate the kind of requirements that could exist in industry and therefore also inspire the transformation approach used in Paper D. However, as real industrial requirements are proprietary, only a discussion on hypothetical requirements can be included in this thesis. Consider therefore say that we have the following requirement on the car:

**Requirement 1.** The car should be comfortable to drive.

This requirement is very abstract. On one hand, many would be able to evaluate whether or not this requirement holds after driving the car a few hours. On the other hand, it is unclear how to formally specify this requirement, and specifically it is impossible to test that parts of the system, *e.g.* certain software, fulfills its part of the requirement.

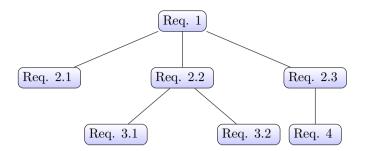

To make the requirement testable, it needs to be broken down into components. Of course, a requirement like the one presented can be interpreted in many different ways, and will be considered fulfilled in different ways depending on who is asking. Now, different attempts of refining the requirement will be performed; an overview of how the different requirements relate to each other are shown in Figure 3.1. The first refinement follows in Requirement 2:

**Requirement 2.** To be considered comfortable (and therefore fulfill Requirement 1), the car should fulfill all of the following: