# The dependence of the high-frequency performance of graphene field-effect transistors on channel transport properties

Downloaded from: https://research.chalmers.se, 2025-12-04 20:05 UTC

Citation for the original published paper (version of record):

Asad, M., Bonmann, M., Yang, X. et al (2020). The dependence of the high-frequency performance of graphene field-effect transistors on channel transport properties. IEEE Journal of the Electron Devices Society, 8: 457-464.

http://dx.doi.org/10.1109/JEDS.2020.2988630

N.B. When citing this work, cite the original published paper.

© 2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, or reuse of any copyrighted component of this work in other works.

Received 30 December 2019; revised 21 February 2020; accepted 12 April 2020. Date of publication 17 April 2020; date of current version 7 May 2020.

The review of this paper was arranged by Editor S. Vaziri.

Digital Object Identifier 10.1109/JEDS.2020.2988630

## The Dependence of the High-Frequency Performance of Graphene Field-Effect Transistors on Channel Transport Properties

MUHAMMAD ASAD<sup>®</sup> <sup>1</sup>, MARLENE BONMANN<sup>®</sup> <sup>1</sup>, XINXIN YANG<sup>®</sup> <sup>1</sup> (Graduate Student Member, IEEE), ANDREI VOROBIEV<sup>®</sup> <sup>1</sup> (Member, IEEE), KJELL JEPPSON<sup>®</sup> (Life Senior Member, IEEE), LUCA BANSZERUS<sup>2</sup>, MARTIN OTTO<sup>®</sup> <sup>3</sup>, CHRISTOPH STAMPFER<sup>2</sup>, DANIEL NEUMAIER<sup>3</sup>, AND JAN STAKE<sup>®</sup> <sup>1</sup> (Senior Member, IEEE)

1 Microtechnology and Nanoscience Department, Chalmers University of Technology, SE-41296 Gothenburg, Sweden 2 2nd Institute of Physics, RWTH Aachen University, 52074 Aachen, Germany 3 Advanced Microelectronic Center Aachen, AMO GmbH, 52074 Aachen, Germany

CORRESPONDING AUTHOR: M. ASAD (e-mail: asadmu@chalmers.se)

This work was supported in part by the European Union's Horizon 2020 Research and Innovation Program's Graphene Flagship (Graphene Core2) under Grant 785219, in part by the Swedish Foundation for Strategic Research under Grant SE13-0061, and in part by the Swedish Research Council under Grant 2017-04504.

**ABSTRACT** This paper addresses the high-frequency performance limitations of graphene field-effect transistors (GFETs) caused by material imperfections. To understand these limitations, we performed a comprehensive study of the relationship between the quality of graphene and surrounding materials and the high-frequency performance of GFETs fabricated on a silicon chip. We measured the transit frequency ( $f_T$ ) and the maximum frequency of oscillation ( $f_{max}$ ) for a set of GFETs across the chip, and as a measure of the material quality, we chose low-field carrier mobility. The low-field mobility varied across the chip from 600 cm<sup>2</sup>/Vs to 2000 cm<sup>2</sup>/Vs, while the  $f_T$  and  $f_{max}$  frequencies varied from 20 GHz to 37 GHz. The relationship between these frequencies and the low-field mobility was observed experimentally and explained using a methodology based on a small-signal equivalent circuit model with parameters extracted from the drain resistance model and the charge-carrier velocity saturation model. Sensitivity analysis clarified the effects of equivalent-circuit parameters on the  $f_T$  and  $f_{max}$  frequencies. To improve the GFET high-frequency performance, the transconductance was the most critical parameter, which could be improved by increasing the charge-carrier saturation velocity by selecting adjacent dielectric materials with optical phonon energies higher than that of SiO<sub>2</sub>.

**INDEX TERMS** Graphene, field-effect transistors, high frequency, transit frequency, maximum frequency of oscillation, microwave electronics, contact resistances, transconductance.

### I. INTRODUCTION

Owing to an extremely high intrinsic carrier mobility of up to  $10^5$  cm<sup>2</sup>/Vs at room temperature [1], [2], graphene is considered a promising new channel material allowing for the development of new generation of field-effect transistors [3] for advanced mm-wave and sub-terahertz amplifiers. However, the high-frequency performance of state-of-the-art graphene field-effect transistors (GFETs) is significantly reduced. The highest published extrinsic (measured) transit frequency ( $f_{\rm T}$ ) and maximum frequency of oscillation ( $f_{\rm max}$ ) of GFETs are typically below

100 GHz [4]. For comparison, the high electron-mobility transistors (HEMTs) based on III–V compounds, with low-field mobilities above  $10^4~\rm cm^2/Vs$ , reveal a  $f_{\rm T}$  and  $f_{\rm max}$  up to 1 THz at deep-sub- $\mu m$  gate lengths [5]. The high-frequency performance of GFETs is currently limited by a number of intrinsic and extrinsic factors. In particular, the intrinsic zero-bandgap in graphene results in relatively high drain conductance, which limits the extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  of the GFETs [6]. An approach has been proposed to realize the drain-current saturation in GFETs without a bandgap formation but via velocity saturation of charge

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

VOLUME 8, 2020 457

carriers at high fields [7]. This approach has recently been applied in the development of GFETs with a state-of-the-art high-frequency performance operating in the velocity saturation mode [4], [8]. Nevertheless, there is a need to improve material quality and fabrication processes to minimize the extrinsic factors to fully exploit graphene for high-frequency applications.

Extrinsic limitations of the  $f_T$  and  $f_{max}$  are associated with parasitic coupling and loss, in part affected by imperfections in the graphene, adjacent dielectrics and interfaces. The effects of imperfections on low-field dc graphene properties have been extensively studied experimentally [9]-[13] and theoretically [14]-[17] and are well understood. However, the carrier velocity at high field is a key parameter for the intrinsic performance at high frequencies. Theoretically, Monte Carlo simulations predict that the carrier velocity in graphene at high electric fields, i.e., up to 10<sup>4</sup> V/cm, should decrease with impurity concentration due to a decrease in the low-field mobility [18], [19]. In previous studies, it was shown that within a certain range of impurity concentrations, the charged impurities do not limit the saturation velocity directly by the phonon mechanism but act as traps emitting charge carriers at high fields, which prevents the current from saturation and thus potentially limits the extrinsic  $f_T$ and  $f_{\text{max}}$  [8]. Nevertheless, to the best of our knowledge, there are no published systematic studies on the dependencies between the quality of the graphene and adjacent dielectric materials and the high-frequency performance on the GFETs, which is important for further development of transistors for high-frequency applications.

In this work, we analyze the relationship between the graphene/dielectric material quality and the high-field high-frequency performance of GFETs, i.e., the extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  at drain fields above  $10^4$  V/cm. The low field mobility is used as the most appropriate parameter to represent the material quality. We exploit the surface distribution of the graphene/dielectric material quality in terms of low field mobility caused by the lateral inhomogeneities and variations across the silicon chip surface. The dependencies are analyzed by combining models of the drain resistance, carrier velocity, saturation velocity and small-signal equivalent circuit. In addition, a sensitivity analysis is provided to clarify the relative significance of the equivalent-circuit parameters, hence, identifying a promising approach for improving GFET high-frequency performance.

### II. METHOD

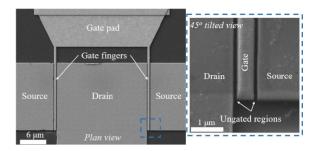

Fig. 1(a) shows an SEM image of a typical two-finger gate GFET fabricated and studied in this work. GFETs with a total gate width ( $W_g$ ) of 30  $\mu$ m and gate length ( $L_g$ ) ranging from 0.5  $\mu$ m to 2  $\mu$ m were studied. Fig. 1(b) shows a 45° tilted SEM image of the gate area. The length of the ungated regions is 0.1  $\mu$ m. Fig. 2 shows the main distinguishable stages (i-iv) of GFET fabrication. The GFETs are fabricated using high-quality chemical vapor deposition (CVD) graphene with measured Hall mobility up to 7000 cm²/Vs.

FIGURE 1. (a) SEM image of a GFET. (b) Magnified and 45° tilted view of the gate area in (a) corresponding to the dashed line box.

FIGURE 2. Main steps of the GFET fabrication. (i) Formation of the 1<sup>st</sup> dielectric layer, (ii) patterning of the dielectric/graphene mesa and formation of the source and drain contacts, (iii) deposition of the 2<sup>nd</sup> dielectric layer, and (iv) formation of the gate electrodes and source, along with the drain contact pads. Labels S, D and G indicate source, drain and gate electrodes, respectively.

The graphene film is transferred onto a high resistivity silicon/silicon oxide (Si/SiO<sub>2</sub>) substrate with a SiO<sub>2</sub> thickness of 1 µm. A relatively thick oxide layer allows for the reduction of parasitic-pad capacitances. In stage (i), the transferred graphene film is covered with a 5 nm thick Al<sub>2</sub>O<sub>3</sub> layer [4], as indicated by the 1st dielectric layer in Fig. 2. The 1st dielectric layer encapsulates graphene in the GFET channel and protects it from contamination during further processing, thereby reducing the concentration of impurities at the interface between the graphene and the gate dielectric [4]. In stage (ii), the graphene/dielectric mesa and, subsequently, the drain and source contacts are patterned. Notice that before metal deposition in the openings of the source and drain contact areas, the 1st dielectric layer, which separates the graphene from the lithographic resist, is etched off for metal/graphene ohmic contact formation. Apparently, this process allows for the effective removal of e-beam resist residues, providing a rather clean interface between the graphene and the metal and resulting in an extremely low specific-width contact resistivity of the graphene/metal junctions down to 15  $\Omega \cdot \mu m$ . In stage (iii), the 2<sup>nd</sup> dielectric layer is formed by an atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> that is 17 nm thick with a total gate dielectric thickness of 22 nm. The 2<sup>nd</sup> dielectric layer covers the graphene edges exposed at the mesa sidewalls and, hence, prevents short circuiting by the overlapping gate fingers. In stage (iv), the gate electrodes,

source and drain contact pads are formed. All lithographic steps were performed using e-beam lithography, and e-beam evaporation was used for metallization. To verify the specific width contact resistivity of the graphene/metal junctions, typical transfer line method (TLM) test structures were designed and fabricated simultaneously with GFETs on the same Si chip. Similar GFET and TLM test structures were located at different positions on the Si chip within an area of approximately 10 mm × 5 mm. Not one of the fabricated GFETs was removed from the analysis as a random outlier. The surface distribution of the graphene/dielectric material quality over the Si chip surface allowed us to study the relationships between the material quality, dc and high-frequency performance of the GFETs via comparative analysis of the performance of transistors located at different positions on the chip.

The dc and ac performance of the GFETs and TLM test structures are characterized at room temperature using a Keithley 2612B dual-channel source meter and an Agilent N5230A network analyzer, respectively. The dc and ac measurement methods were followed as published in [4]. The biasing conditions, i.e., the combination of the gatesource voltage  $(V_{GS})$  and the drain-source voltage  $(V_{DS})$ , are optimized by the highest measured  $f_T$  and  $f_{max}$  for each GFET. The output characteristics were recorded during the S-parameters measurements with a holding time of 30 s. According to our previous studies, this holding time is sufficient for stabilizing the capture and emission of charges due to traps at high fields [20]. Typically, the optimal  $V_{\rm DS} \approx -1.1~{

m V}$  corresponds to the intrinsic drain field  $E_{\rm int} \approx 1.5 \cdot 10^4 - 2 \cdot 10^4$  V/cm, at which the effective velocity of the charge carriers saturates [4], [8]. The optimal  $V_{GS}$  overdrive from the Dirac voltage  $(V_{Dir} - V_{GS})$  varies in the range of approximately 0-4.5 V and is higher for the lower material quality.

#### III. RESULTS AND DISCUSSION

### A. GRAPHENE QUALITY AND LOW-FIELD MOBILITY

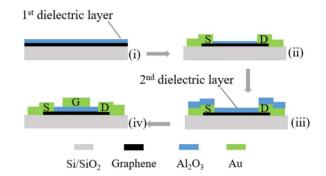

Fig. 3(a) shows the measured drain resistance  $(R_{DS})$  of two finger GFETs versus gate voltage. The drain resistance reveals a typical dependence with a maximum corresponding to the Dirac voltage  $(V_{Dir})$ . Therefore, we assume that Coulomb scattering dominates and that the mobility does not depend on the concentration of the charge carriers [12], [21]. This allows for finding the contact resistance  $(R_C)$ , low-field mobility  $(\mu_0)$  and residual concentration of charge carriers  $(n_0)$  as fitting parameters by applying the semi-empirical drain-resistance model [22]

$$R_{DS} = R_C + \frac{L_g}{W_g} \frac{1}{e\mu_0} \frac{1}{\sqrt{n_0^2 + \left( (V_{GS} - V_{Dir}) \frac{C_{ox}}{e} \right)^2}}$$

(1)

$$n = \sqrt{n_0^2 + \left( (V_{GS} - V_{Dir}) \frac{C_{ox}}{e} \right)^2}$$

(2)

$$n = \sqrt{n_0^2 + \left( (V_{GS} - V_{Dir}) \frac{C_{ox}}{e} \right)^2}$$

(2)

where e is the elementary charge and  $C_{ox}$  is the gate capacitance per unit area. The  $C_{ox}$  is calculated assuming the

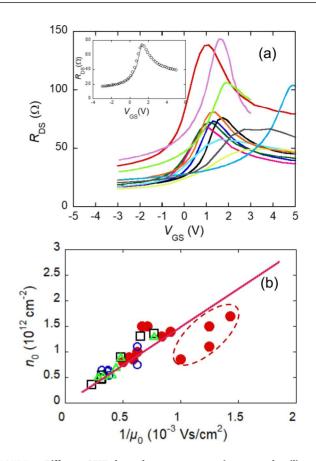

FIGURE 3. Different GFET channel transport properties across the silicon chip. (a) Drain resistance of the GFET's versus the gate voltage and inset shows the modelling results for the hole branch (line) of a GFET's. (b) Residual charge-carrier concentration versus inverse low-field mobility in the GFETs of gate lengths 0.5  $\mu$ m (filled circles), 0.75  $\mu$ m (open circles), 1  $\mu$ m (squares), and 2  $\mu$ m (triangles), located at different positions on the Si chip. The line corresponds to the product  $n_0 \cdot \mu_0 = 1.5 \cdot 10^{15} V^{-1} s^{-1} [14], [21], [25].$

dielectric constant of  $Al_2O_3$  is equal to 7.5 [23]. n is the total charge carrier density. It can be shown that the graphene quantum capacitance can be ignored. The R<sub>C</sub> includes the resistance of the ungated regions  $(R_{ung})$ , see Fig. 1, and the resistance of the graphene/metal junction ( $R_{\rm mg}$ ). As shown in Fig. 3(a), the  $R_{\rm DS}$  dependence on  $V_{\rm GS}$  is asymmetric. This can be explained by lower electron mobility and higher contact resistance due to the formation of the p-n barrier between the n-type gated channel and the p-type ungated region at a positive gate voltage overdrive [13], [24]. The solid line in the inset in Fig. 3(a) represents fitting by the drain-resistance model in the hole branch. Good agreement with the measured data confirms the assumption of Coulomb scattering and thus constant mobility. According to the self-consistent theory, the mobility limited by Coulomb scattering depends only on the charged impurity concentration and the dielectric constant of the substrate [14], [24]. The charged impurity concentration  $(n_{imp})$  plainly defines the residual concentration of the charge carriers as  $n_0 = 0.2 \times n_{\text{imp}}$  for graphene on  $SiO_2$  [21], [25]. Therefore,  $n_0$ , found via the drainresistance model, can be used as a material-quality parameter

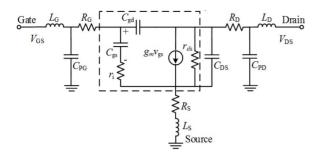

FIGURE 4. Small-signal equivalent circuit of a FET. The elements within the dashed line box represent the intrinsic part of the transistor [6].

when Coulomb scattering dominates [25]. The product of the low-field mobility and the residual-carrier concentration is constant, and for graphene on the SiO2 substrate, it is  $n_0.\mu_0 \approx 1.5 \cdot 10^{15} \text{ V}^{-1} \text{s}^{-1}$  [14]. Fig. 3(b) shows the residual charge-carrier concentration versus the inverse low-field mobility of the GFETs located at different positions on the Si chip for 4 different gate lengths. It can be seen that at mobilities above approximately 1000 cm<sup>2</sup>/Vs, the product  $n_0 \cdot \mu_0$  is close to the value of  $1.5 \cdot 10^{15} \text{ V}^{-1}\text{s}^{-1}$ . Hence, this indicates that the product  $n_0 \cdot \mu_0$  can be assumed constant. The mobilities below approximately 1000 cm<sup>2</sup>/Vs (data points within the dashed curve area) are reduced in comparison with those given by the product  $n_0 \cdot \mu_0 = 1.5 \cdot 10^{15} \text{ V}^{-1} \text{s}^{-1}$ , which was also observed previously [25]. This indicates additional contributions of the other charge-carrier scattering mechanisms, e.g., "short-range" or "resonant" scattering [12], [14]. The effective mobility, which includes all the scattering mechanisms, is given by Matthiessen's rule [26]. In this case, it is assumed that the more appropriate parameter for characterisation of the graphene and interfacial dielectric material quality is the low-field mobility derived from the drain-resistance model.

### B. TRANSIT FREQUENCY AND MAXIMUM FREQUENCY **OF OSCILLATION**

In the analysis below, we establish correlations between the high-frequency performance of the GFETs and the graphene/dielectric-material quality using  $\mu_0$  as the overall quality indicator. The high-frequency performance of FETs is usually characterized by the transit frequency and the maximum frequency of oscillation, which are parameters closely related to the transistor current and power gains, respectively. Analytical approximations for the extrinsic  $f_T$  and  $f_{\rm max}$  are derived from the FET small-signal equivalent circuit shown in Fig. 4. The elements within the dashed line box represent the intrinsic transistor [6].  $g_{\rm m}$  and  $r_{\rm ds}$  are the intrinsic transconductance and differential drain resistance, respectively,  $C_{gs}$  and  $C_{gd}$  are the gate-source and gate-drain capacitances, respectively,  $C_{PG}$ ,  $C_{PD}$  and  $C_{DS}$  are the external parasitic capacitances, respectively,  $R_G$ ,  $R_S$ ,  $R_D$  and  $r_i$  are the gate resistance, source series resistance, drain series resistance and charging resistance of the gate-source capacitance, respectively, and  $L_G$ ,  $L_D$  and  $L_S$  are the lead inductances.

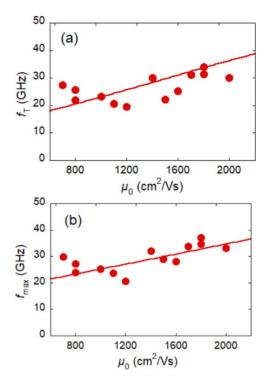

FIGURE 5. High frequency performance of different GFETs and the corresponding low field mobility. Extrinsic transit frequency  $(f_T)$  (a) and maximum frequency of oscillation  $(f_{max})$  (b) of the GFETs located at different positions on the Si chip, versus the corresponding values of low-field mobility ( $\mu_0$ ). The solid lines are the models given by Eqs. (3)-(4) and corresponding polynomial fit dependences of the  $g_{\rm m}$ ,  $g_{\rm ds}$ , and  $R_{\rm C}$ , from Figs. 7-9. The dotted lines are a linear fit of the models.

The extrinsic  $f_T$  and  $f_{max}$  can be approximated as [4], [26]

$$f_T = \frac{g_m}{2\pi \left(C_{gs} + C_{gd}\right)} \frac{1}{1 + g_{ds}R_C + \frac{C_{gd}g_mR_C}{C_{es} + C_{ed}} + \frac{C_{PG}}{C_{es} + C_{ed}}}, (3)$$

$$f_{T} = \frac{g_{m}}{2\pi \left(C_{gs} + C_{gd}\right)} \frac{1}{1 + g_{ds}R_{C} + \frac{C_{gd}g_{m}R_{C}}{C_{gs} + C_{gd}} + \frac{C_{PG}}{C_{gs} + C_{gd}}}, (3)$$

$$f_{\text{max}} = \frac{g_{\text{m}}}{4\pi C_{\text{gs}}} \frac{1}{\sqrt{g_{\text{ds}}(r_{i} + R_{\text{S}} + R_{\text{G}}) + g_{\text{m}}R_{\text{G}}\frac{C_{\text{gd}}}{C_{\text{gs}}}}}, (4)$$

where  $g_{ds} = 1/r_{ds}$  is the intrinsic differential-drain conductance. We estimated the capacitances as  $C_{\rm gs} = 0.5 C_{\rm ox} L_{\rm g} W_{\rm g}$ and  $C_{\rm gd} = kC_{\rm gs}$ , where  $C_{\rm ox} = 3$  fF  $\cdot \mu \rm m^{-2}$ ,  $W_{\rm g}$  is the gate width and k is the fitting parameter, taking into account the decrease in charge-carrier concentration at the drain side [4], [26], [27]. The estimated capacitance values  $C_{gs} = 0.47 \text{ fF}$  and  $C_{gd} = 0.23 \text{ fF}$  differ less than 5% from those found using S-parameters measurements in our previous work [28]. The resistances are estimated as  $R_S = R_C/2$ ,  $r_i = 1/(2g_m)$ ,  $R_G =$  $R_{\rm sh}W_{\rm g}/(3L_{\rm g})$  and  $R_{\rm sh}=0.08~\Omega$  for the gate electrodesheet resistance [4], [26]. The parasitic gate-pad capacitance formed between the gate pad and the low-conductive surface of Si was found by delay-time analysis to be  $C_{PG} \approx 8$  fF [4], [8]. Fig. 5 shows the extrinsic  $f_T$  and  $f_{max}$ of GFETs located at different positions on the Si chip versus the corresponding values of  $\mu_0$ . There are dependencies between the graphene quality and the high-frequency performance of the GFETs. In general,  $f_T$  and  $f_{max}$  increase

in the range of approx. 20-40 GHz with  $\mu_0$  varying in the range of approx. 600-2000 cm<sup>2</sup>/Vs, which is larger than the deviations from the corresponding modeled dependencies.

In the following sections, we analyze these relationships via the corresponding dependencies of the equivalent circuit and material parameters, i.e.,  $g_{\rm m}$ ,  $g_{\rm ds}$ ,  $R_{\rm C}$ , n and the effective velocity ( $\upsilon$ ) and saturation velocity ( $\upsilon_{\rm sat}$ ) of the charge carriers on the low-field mobility. The analysis allows for evaluation of the relative effects of each parameter and thus clarifies the paths for further improvement of the GFET high-frequency performance. The experimental dependencies of  $f_{\rm T}$  and  $f_{\rm max}$  on  $\mu_0$  can be fully explained by the corresponding dependencies of  $g_{\rm m}$ ,  $g_{\rm ds}$  and  $R_{\rm C}$  found via semi-empirical models. In the analysis below, we assume that the intrinsic and extrinsic capacitances are constant.

### C. VELOCITY, SATURATION VELOCITY AND TRANSCONDUCTANCE

The charge carrier velocity in the GFET channel starts to saturate around an intrinsic electric field  $(E_{int})$  of  $10^4$  V/cm [8], [29]. We apply a model that assumes that the saturation velocity is limited by the inelastic emission of optical phonons (OPs) and can be approximated as [8], [29]

$$\nu_{\text{sat}} = \frac{2}{\pi} \frac{\omega_{\text{OP}}}{\sqrt{\pi n}} \sqrt{1 - \frac{\omega_{\text{OP}}^2}{4\pi n \nu_F^2}} \frac{1}{N_{\text{OP}} + 1}$$

(5)

where  $\hbar\omega_{\mathrm{OP}}$  is the OP energy,  $N_{\mathrm{OP}}=1/[\exp(\hbar\omega_{\mathrm{OP}}/k_{\mathrm{B}}T)-1]$  is the phonon occupation,  $v_{\mathrm{F}}\approx 10^8$  cm/s is the Fermi velocity and  $k_B$  is Boltzmann's constant. We ignore the effects of self-heating and assume a constant ambient temperature of 295 K. We verified the velocity saturation model in our previous work (Ref. 4) via simulations of the extrinsic  $f_{\mathrm{T}}$  and  $f_{\mathrm{max}}$  of GFETs with different gate lengths in the range of 0.5-2  $\mu$ m, revealing good agreement with the experimental data.

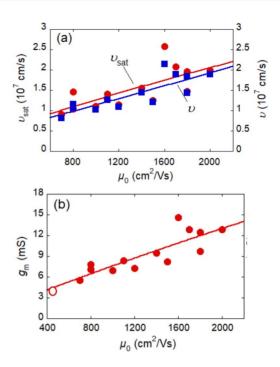

Fig. 6(a) shows the saturation velocity of the charge carriers in the GFETs, located at different positions on the Si chip, versus corresponding values of the low-field mobility. The saturation velocity is calculated using Eq. (5) and the n calculated using Eq. (2). It can be seen that the  $v_{\rm sat}$  increases from approximately  $1\cdot10^7$  cm/s to  $2.5\cdot10^7$  cm/s in the studied  $\mu_0$  range. The dependencies between  $v_{\rm sat}$  and  $\mu_0$  are in agreement with our previous observations, indicating that the effective saturation velocity is not directly limited by the OPs of the impurities but rather reduced due to the increased residual concentration of the charge in the GFETs with a higher-impurity concentration [8]. The effective velocity of the charge carriers is calculated as [30]

$$\upsilon = \frac{\mu_0 E_{\text{int}}}{\left[1 + (\mu_0 E_{\text{int}}/\upsilon_{\text{sat}})^{\gamma}\right]^{\frac{1}{\gamma}}} \tag{6}$$

where  $E_{\rm int} = (V_{\rm DS} - I_{\rm ds}R_{\rm C})/L_{\rm g}$ ,  $I_{\rm ds}$  is the drain-source current, and  $\gamma = 3$  is the fitting parameter for the  $\upsilon$  dependence on  $E_{\rm int}$  found via delay-time analysis [8]. Fig. 6(a) shows the velocity of the charge carriers in the GFETs, calculated

FIGURE 6. Higher saturation velocity and transconductance with improved lowfield mobility. (a) The saturation velocity ( $v_{sat}$ ) (circles), calculated using Eq. (5), and the carrier concentration calculated from Eq. (2) and the velocity (v) (squares), calculated using Eq. (6), versus the low-field mobility in the GFETs located at different positions on the Si chip. The lines are the polynomial fitting curves. (b) The transconductance, calculated using Eq. (7), versus low field mobility in the GFETs, located at different positions on the Si chip. The line is a second order polynomial fitting curve. The open circle is from previous studies after de-embedding [28].

using Eq. (6), versus the corresponding values of the low-field mobility. It can be seen that the difference between the  $v_{\rm sat}$  and v is less than 10% in the whole range of the low-field mobility. Therefore, one can assume that, in all the studied GFETs with different graphene quality and at a  $V_{\rm DS}$  corresponding to the highest measured  $f_{\rm T}$  and  $f_{\rm max}$ , the effective velocity is relatively saturated.

The intrinsic transconductance is calculated as [26]

$$g_{\rm m} = \frac{\upsilon \cdot \left(C_{\rm gs} + C_{\rm gd}\right)}{L_{\rm g}} \tag{7}$$

Fig. 6(b) shows the transconductance, calculated using Eq. (7), versus low-field mobility in the GFETs located at different positions on the Si chip.  $g_{\rm m}$  increases with  $\mu_0$ , following the  $\upsilon$  dependence, from approximately 6 mS to 14 mS. The solid line in Fig. 6(b) is the second-order polynomial fit of the calculated  $g_{\rm m}$  on the  $\mu_0$  dependence and is applied in the further analysis for the models of  $f_{\rm T}$  and  $f_{\rm max}$  versus  $\mu_0$  using Eqs. (3)-(4). Fig. 6(b) includes also a  $g_{\rm m}$  value found from S-parameters measurements scaled from our previous work using similar Theagreement with the dependence.

### D. DRAIN CONDUCTANCE

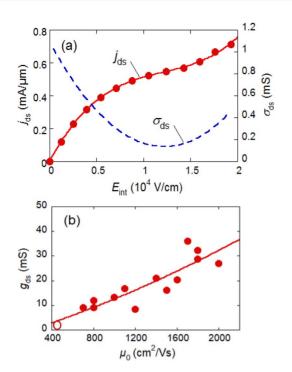

Fig. 7(a) shows the drain-current density, calculated as  $j_{ds} = I_{ds}/W_g$ , versus the intrinsic-drain field measured at

VOLUME 8, 2020 461

FIGURE 7. (a) The drain-current density (jds) and differential-drain conductivity ( $v_{\rm sat}$ ) versus the intrinsic-drain field measured at the GFET with  $\mu 0 = 1800 {\rm cm}^2/{\rm Vs}$ . The solid line is a third-order polynomial fitting curve. (b) The drain conductance versus the low-field mobility in the GFETs located at different positions on the Si chip. The line is a second-order polynomial fitting curve. The open circle is from previous studies after de-embedding [28].

the GFET with  $\mu_0 = 1800 \text{ cm}^2/\text{Vs}$  and highest  $f_T$  and  $f_{\text{max}}$ ; see Fig. 5. It can be seen that  $j_{\text{ds}}$  reveals a pronounced kink at the drain field of approximately  $10^4$  V/cm. We assume that the kink is associated with both the carrier velocity saturation, which typically occurs at the intrinsic drain fields of approximately  $10^4$  V/cm [8], [29], and the formation of a region with the residual concentration of the charge carriers at the drain side of the channel [6], [31], [32]. The field at the drain side corresponding to the kink voltage is large enough for velocity saturation [31]. Since the optimal field for the highest measured  $f_T$  and  $f_{\text{max}}$  is typically above that of the  $g_{\text{ds}}$  minimum, we assume that the velocity saturates at each point along the channel.

The complete drain-current saturation is prevented by channel ambipolarity due to a missing bandgap [6], [31]. The solid line in Fig. 7(a) is a third-order polynomial fitting curve, which is used to calculate the differential drain conductivity as  $\sigma_{\rm ds} = \partial j_{\rm ds}/\partial E_{\rm int}$ . Fig. 7(a) shows the corresponding dependence of  $\sigma_{\rm ds}$  on the intrinsic drain field. It can be seen that the  $\sigma_{\rm ds}$  dependence reveals a minimum corresponding to the kink on the  $j_{\rm ds}$  dependence. The optimal field for the highest measured  $f_{\rm T}$  and  $f_{\rm max}$  is typically above that of the  $\sigma_{\rm ds}$  minima, which can be explained by counterbalancing contributions of the other equivalent circuit parameters; see Eqs. (3)-(4). Fig. 7(b) shows the drain conductance, calculated as  $g_{\rm ds} = \sigma_{\rm ds} \cdot (W_{\rm g}/L_{\rm g})$  corresponding to the drain

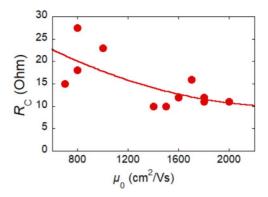

**FIGURE 8.** Lower contact resistance with improved quality of the graphene channel. The contact resistance ( $R_{\rm C}$ ) (the sum of metal/graphene junction resistances and ungated region resistances) versus low-field mobility in the GFETs located at different positions on the Si chip. The lines are second-order polynomial fitting curves.

fields of the highest measured  $f_{\rm T}$  and  $f_{\rm max}$ , versus the low-field mobility in the GFETs, located at different positions on the Si chip. As can be seen, the  $g_{\rm ds}$  increases with  $\mu_0$  in the studied mobility range. The solid line in Fig. 7(b) is the second-order polynomial fit, which is applied in the further analysis for the models of the  $f_{\rm T}$  and  $f_{\rm max}$  versus  $\mu_0$  using Eqs. (3)-(4). Fig. 7 (b) also includes a  $g_{\rm ds}$  value found from S-parameters measurements scaled from our previous work using similar technology and GFET design (Ref. 29). which is in very good agreement with the dependence.

### E. CONTACT RESISTANCE

Fig. 8 shows the sum of the source and drain contact resistance, evaluated via fitting the drain-resistance model, see Eq. (1), to the GFET transfer characteristics versus the low-field mobility in the GFETs located at different positions on the Si chip. The  $R_{\rm C}$  decreases with  $\mu_0$ , from approx. 30  $\Omega$  down to 10  $\Omega$ , in the studied mobility range. The solid line in Fig. 8 is the second-order polynomial fit, which is applied in the further analysis for the models of the  $f_{\rm T}$  and  $f_{\rm max}$  versus  $\mu_0$  using Eqs. (3)-(4).

In this work, the lowest measured  $R_{\rm C}\approx 10~\Omega$  corresponds to the specific width-contact resistivity  $\rho_{\rm c}=(R_{\rm C}/2)\cdot(W_{\rm g})\approx 150~\Omega\cdot\mu{\rm m}$ . In GFETs, the  $R_{\rm C}$  is the combination of the contact-resistance parts associated with those of the ungated regions and the graphene/metal junctions and is defined as:

$$R_{\rm C} = R_{\rm mg} + R_{\rm ung}, \tag{8}$$

where  $R_{\rm mg}$  is the metal/graphene junctions' resistance and  $R_{\rm ung}$  is the ungated region resistance. It can be shown, by separating the  $R_{\rm ung}$ , that the values of  $R_{\rm mg}$  are lower than those of the lowest previously published for both top and edge graphene/metal contacts, including perforated ones, which are typically above 100  $\Omega \cdot \mu$ m [33]–[36].

For comparison, the state-of-the-art silicon metal-oxide-semiconductor field-effect transistors (MOSFETs) require a contact resistivity of 80  $\Omega \cdot \mu m$  per contact, which is approximately 10% of the on-state resistance of the

transistor [37], [38]. In our GFETs with the lowest  $R_{\rm C}$ , the contact resistance per contact, i.e.,  $R_{\rm S}$  or  $R_{\rm D}$ , is approximately 5  $\Omega$ . As shown in Fig. 3(a), it is less than 10% of the  $R_{\rm DS}$  at approximately  $V_{\rm Dir}-0.5$  V, which is the gate voltage typical for the highest measured  $f_{\rm T}$  and  $f_{\rm max}$ . We confirmed the extremely low contact resistance in our GFETs by using the transfer-length method (TLM) and specifically designed and fabricated TLM test structures on the same Si chip (see Section II). The average specific width-contact resistivity found by the TLM analysis is approximately 95  $\Omega \cdot \mu m$ , which is in good agreement with that of the  $\rho_{\rm mg} = (R_{\rm mg}) \cdot (W_{\rm g}) \approx 90~\Omega \cdot \mu m$  calculated by separating the  $R_{\rm ung}$ .

So far, the increase in transconductance and differential-drain conductivity with mobility and a decrease in contact resistance with mobility have been observed. As shown in Fig. 5, an increase in  $f_{\rm T}$  and  $f_{\rm max}$  with mobility is observed owing to an increase in  $g_{\rm m}$  and a decrease in  $R_{\rm C}$ , but proportionate effects of these parameters on  $f_{\rm T}$  and  $f_{\rm max}$  are diminished owing to an increase in  $g_{\rm ds}$  with mobility. The solid lines in Fig. 5 represent the  $f_{\rm T}$  and  $f_{\rm max}$  values modeled using Eqs. (3)-(4) versus  $\mu_0$  and the corresponding polynomial functions of  $g_{\rm m}$ ,  $g_{\rm ds}$  and  $R_{\rm C}$  found as fits to the experimental data shown in Figs. 7-9. The good agreement between the experimental trends and modeled dependencies of  $f_{\rm T}$  and  $f_{\rm max}$  verify the analytical approximations given by Eqs. (3)-(4), as well as the models used for calculations of  $g_{\rm m}$ ,  $g_{\rm ds}$  and  $R_{\rm C}$ .

### F. GUIDELINES FOR IMPROVING THE HIGH FREQUENCY PERFORMANCE

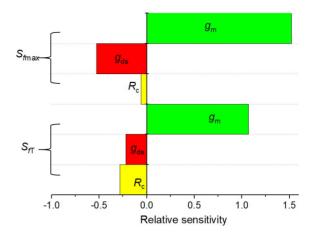

Finally, a relative sensitivity analysis was performed to determine the most influential equivalent circuit parameters for improving the current state-of-the-art GFET technology. The partial effects of the equivalent-circuit parameters on  $f_{\rm T}$  and  $f_{\rm max}$  are analyzed. The relative sensitivity is defined as the ratio of the relative change in the function to the relative change in the variable [39]

$$S_f = \left(\frac{\partial f}{f}\right) / \left(\frac{\partial p}{p}\right) \tag{9}$$

where  $S_f$  denotes the relative sensitivity, f denotes the  $f_T$  or  $f_{max}$  and p denotes the parameters  $g_m$ ,  $g_{ds}$  and  $R_C$ . The relative sensitivities are calculated using analytical expressions of partial derivatives of  $f_T$  and  $f_{max}$  given by Eqs. (3) and (4) and values of corresponding parameters given by fitting curves in Fig. 6-8. Fig. 9 shows a bar chart of the relative sensitivities of  $f_T$  and  $f_{max}$  to  $g_m$ ,  $g_{ds}$  and  $R_C$  at a low-field mobility of 2000 cm<sup>2</sup>/Vs. The variations in  $f_T$  and  $f_{max}$  are governed mainly by variations in  $g_m$ . The negative effects of  $g_{ds}$  and  $R_C$  on  $f_T$  are comparable and less than those of  $g_m$ . The effect of  $R_C$  on  $f_{max}$  is negligible. According to our analysis, the sensitivities show the same relationships in the whole studied mobility range and above the mobility of 2000 cm<sup>2</sup>/Vs. It is clear that the most effective way of increasing  $f_T$  and  $f_{max}$  is by increasing the transconductance.

**FIGURE 9.** Most critical equivalent circuit parameters. A bar chart presenting the relative sensitivity of extrinsic transit frequency  $(f_T)$  and maximum frequency of oscillation  $(f_{\max})$  to the equivalent-circuit parameters  $g_m$ ,  $g_{ds}$  and  $R_C$  at mobility of 2000 cm²/Vs. The transconductance is the most important parameter in order to improve the  $f_T$  and  $f_{\max}$ .

Since, according to our sensitivity analysis, the  $g_{\rm m}$  is the most influencing parameter, an effective way of increasing  $f_{\rm T}$  and  $f_{\rm max}$  is by increasing the transconductance. An approach of increasing  $g_{\rm m}$  in GFETs with the same design and dimensions is the selection of channel dielectric materials with higher optical phonon energies [7], [8], [31]. This will result in an increase in saturation velocity and thus  $g_{\rm m}$ ; see Eqs. (5)-(7). For example, the Al<sub>2</sub>O<sub>3</sub> and hBN optical phonon energies are 87 meV and 100 meV, respectively [7], [18]. According to our calculations, replacing SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> or hBN will result in an increase in saturation velocities up to 3.10<sup>7</sup> cm/s and 5.10<sup>7</sup> cm/s and  $f_{\rm max}$  of the GFETs up to 100 GHz and 150 GHz, respectively, at the same  $L_{\rm g}=0.5\mu{\rm m}$  [7], [8]. According to our analysis, the differential drain conductivity  $g_{ds}$ , in the velocity saturation mode, should not increase much in the GFETs with higher saturation velocity.

### **IV. CONCLUSION**

In conclusion, we have performed a comprehensive study of the relationship of the high-frequency performance of GFETs to the channel transport properties. The latter is to a large extent affected by the quality of the graphene and surrounding materials. An almost linear relationship between the high-frequency parameters of GFETs and low-field mobility was observed and is explained theoretically using a methodology based on the small-signal equivalent circuit model with parameters extracted from the low-field drain resistance model and the charge-carrier velocity saturation model. The relationship observed was governed mainly by the transconductance and the drain output conductance, while the contact resistance appeared to have a rather weak influence. The results indicate that the most promising approach for improving GFET high-frequency performance is by increasing the transconductance. In particular, the relatively high drain conductance in GFETs can be counterbalanced by achieving

VOLUME 8, 2020 463

high transconductance. In addition to scaling the gate length, an approach for increasing  $f_{\rm T}$  and  $f_{\rm max}$  is by encapsulating the graphene channel with dielectric material with reduced charged-impurity density and higher optical-phonon energy than that of SiO<sub>2</sub>, resulting in higher saturation velocity and thus higher transconductance.

#### **REFERENCES**

- K. I. Bolotin, K. J. Sikes, J. Hone, H. L. Stormer, and P. Kim, "Temperature-dependent transport in suspended graphene," *Phys. Rev. Lett.*, vol. 101, no. 9, Aug. 2008, Art. no. 096802, doi: 10.1103/PhysRevLett.101.096802.

- [2] L. Banszerus et al., "Ultrahigh-mobility graphene devices from chemical vapor deposition on reusable copper," Sci. Adv., vol. 1, no. 6, Jul. 2015, Art. no. e1500222, doi: 10.1126/sciadv.1500222.

- [3] M. C. Lemme, T. J. Echtermeyer, M. Baus, and H. Kurz, "A graphene field-effect device," *IEEE Electron Device Lett.*, vol. 28, no. 4, pp. 282–284, Apr. 2007, doi: 10.1109/LED.2007.891668.

- [4] M. Bonmann *et al.*, "Graphene field-effect transistors with high extrinsic f<sub>T</sub> and f<sub>max</sub>," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 131–134, Jan. 2019, doi: 10.1109/LED.2018.2884054.

- [5] R. Lai et al., "Sub 50 nm InP HEMT device with f<sub>max</sub> greater than 1 THz," in Proc. IEEE Int. Electron Devices Meeting, 2007, pp. 609–611, doi: 10.1109/IEDM.2007.4419013.

- [6] F. Schwierz, "Graphene transistors: Status, prospects, and problems," *Proc. IEEE*, vol. 101, no. 7, pp. 1567–1584, Jul. 2013, doi: 10.1109/JPROC.2013.2257633.

- [7] A. Vorobiev et al., "Graphene field-effect transistors for millimeter wave amplifiers," Proc. IEEE Int. Conf. Infrared Millimeter Terahertz Waves (IRMMW-THz), 2019, pp. 1–2, doi: 10.1109/IRMMW-THz.2019.8874149

- [8] M. Bonmann, A. Vorobiev, M. A. Andersson, and J. Stake, "Charge carrier velocity in graphene field-effect transistors," *Appl. Phys. Lett.*, vol. 111, no. 23, Dec. 2017, Art. no. 233505, doi: 10.1063/1.5003684.

- [9] Z. Cheng, Q. Zhou, C. Wang, Q. Li, C. Wang, and Y. Fang, "Toward intrinsic graphene surfaces: A systematic study on thermal annealing and wet-chemical treatment of SiO<sub>2</sub>-supported graphene devices," *Nano Lett.*, vol. 11, no. 2, pp. 767–771, 2011, doi: 10.1021/nl103977d.

- [10] C. A. Chavarin, A. A. Sagade, D. Neumaier, G. Bacher, and W. Mertin, "On the origin of contact resistances in graphene devices fabricated by optical lithography," *Appl. Phys. A, Solids Surf.*, vol. 122, no. 2, p. 58, 2016, doi: 10.1007/s00339-015-9582-5.

- [11] I. Meric et al., "Graphene field-effect transistors based on boronnitride gate dielectrics," in *Int. Electron Devices Meeting Tech. Dig.*, 2010, pp. 556–559, doi: 10.1109/JPROC.2013.2257634.

- [12] F. Giannazzo, S. Sonde, R. L. Nigro, E. Rimini, and V. Raineri, "Mapping the density of scattering centers limiting the electron mean free path in graphene," *Nano Lett.*, vol. 11, no. 11, pp. 4612–4618, 2011, doi: 10.1021/nl2020922.

- [13] O. Habibpour, J. Vukusic, and J. Stake, "A large-signal graphene FET model," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 968–975, Apr. 2012, doi: 10.1109/TED.2012.2182675.

- [14] S. Adam, E. H. Hwang, and S. D. Sarma, "Scattering mechanisms and Boltzmann transport in graphene," *Physica E, Low-Dimensional Syst. Nanostruct.*, vol. 40, no. 5, pp. 1022–1025, Mar. 2008, doi: 10.1016/j.physe.2007.09.064.

- [15] D. Liu, S. J. Clark, and J. Robertson, "Oxygen vacancy levels and electron transport in Al<sub>2</sub>O<sub>3</sub>," Appl. Phys. Lett., vol. 96, no. 3, pp. 1–3, Jan. 2010, doi: 10.1063/1.3293440.

- [16] T. O. Wehling, S. Yuan, A. I. Lichtenstein, A. K. Geim, and M. Katsnelson, "Resonant scattering by realistic impurities in graphene," *Phys. Rev. Lett.*, vol. 105, Nov. 2010, Art. no. 056802, doi: 10.1103/PhysRevLett.105.056802.

- [17] T. Ando, "Screening effect and impurity scattering in monolayer graphene," J. Phys. Soc. Japan, vol. 75, no. 7, 2006, Art. no. 074716, doi: 10.1143/jpsj.75.074716.

- [18] J. Chauhan and J. Guo, "High-field transport and velocity saturation in graphene," Appl. Phys. Lett., vol. 95, no. 2, Jul. 2009, Art. no. 023120, doi: 10.1063/1.3182740.

- [19] P. C. Feijoo et al., "Scaling of graphene field-effect transistors supported on hexagonal boron nitride: Radio-frequency stability as a limiting factor," *Nanotechnology*, vol. 28, no. 48, Nov. 2017, Art. no. 485203, doi: 10.1088/1361-6528/aa9094.

- [20] M. Bonmann, A. Vorobiev, J. Stake, and O. Engstrom, "Effect of oxide traps on channel transport characteristics in graphene field effect transistors," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 35, no. 1, 2017, Art. no. 01A115, doi: 10.1116/1.4973904.

- [21] S. Adam, E. H. Hwang, V. M. Galitski, and S. D. Sarma, "A self-consistent theory for graphene transport," *Proc. Nat. Acad. Sci. USA*, vol. 104, no. 47, pp. 18392–18397, Nov. 2007, doi: 10.1073/pnas.0704772104.

- [22] S. Kim et al., "Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," Appl. Phys. Lett., vol. 94, no. 6, Feb. 2009, Art. no. 062107, doi: 10.1063/1.3077021.

- [23] M. D. Groner, J. W. Elam, F. H. Fabreguette, and S. M. George, "Electrical characterization of thin Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition on silicon and various metal substrates," *Thin Solid Films*, vol. 413, nos. 1–2, pp. 186–197, Jun. 2002, doi: 10.1016/S0040-6090(02)00438-8.

- [24] J.-H. Chen, C. Jang, S. Adam, M. S. Fuhrer, E. D. Williams, and M. Ishigami, "Charged-impurity scattering in graphene," *Nat. Phys.*, vol. 4, no. 5, pp. 377–381, May 2008, doi: 10.1038/nphys935.

- [25] J. Chan et al., "Reducing extrinsic performance-limiting factors in graphene grown by chemical vapor deposition," ACS Nano, vol. 6, no. 4, pp. 3224–3229, 2012, doi: 10.1021/nn300107f.

- [26] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices. Hoboken, NJ, USA: Wiley, 2007, pp. 308–309.

- [27] I. Meric et al., "High-frequency performance of graphene field effect transistors with saturating IV-characteristics," in *Int. Electron Devices Meeting (IEDM) Tech. Dig.*, Washington, DC, USA, Dec. 2011, pp. 1–4, doi: 10.1109/IEDM.2011.6131472.

- [28] M. Tanzid, M. A. Andersson, J. Sun, and J. Stake, "Microwave noise characterization of graphene field effect transistors," *Appl. Phys. Lett.*, vol. 104, no. 1, pp. 1–4, 2014.

- [29] V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 97, no. 8, 2010, Art. no. 082112, doi: 10.1063/1.3483130.

- [30] D. M. Caughcy and R. E. Thomas, "Carrier mobilities in silicon empirically related to doping and field," *Proc. IEEE*, vol. 55, no. 12, pp. 2192–2193, Dec. 1967, doi: 10.1109/PROC.1967.6123.

- [31] I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," *Nat. Nanotechnol.*, vol. 3, no. 11, pp. 654–659, Nov. 2008, doi: 10.1038/nnano.2008.268.

- [32] D. Jimenez and O. Moldovan, "Explicit drain-current model of graphene field-effect transistors targeting analog and radio-frequency applications," *IEEE Trans. Electron Devices*, vol. 58, no. 11, pp. 4049–4052, Nov. 2011, doi: 10.1109/TED.2011.2163517.

- [33] W. S. Leong, H. Gong, and J. T. L. Thong, "Low-contact-resistance graphene devices with nickel-etched-graphene contacts," ACS Nano, vol. 8, no. 1, pp. 994–1001, 2014, doi: 10.1021/nn405834b.

- [34] L. Wang et al., "One-dimensional electrical contact to a two-dimensional material," Science, vol. 342, no. 6158, pp. 614–617, Nov. 2013, doi: 10.1126/science.1244358.

- [35] H. Zhong et al., "Realization of low contact resistance close to theoretical limit in graphene transistors," Nano Res., vol. 8, pp. 1–11, Mar. 2015, doi: 10.1007/s12274-014-0656-z.

- [36] M. Shaygan et al., "Low resistive edge contacts to CVD-grown graphene using a CMOS compatible metal," Annalen der Physik, vol. 529, no. 11, Nov. 2017, Art. no. 1600410, doi: 10.1002/andp.201600410.

- [37] J. T. Smith, A. D. Franklin, D. B. Farmer, and C. D. Dimitrakopulos, "Reducing contact resistance in graphene devices through contact area patterning," ACS Nano, vol. 7, no. 4, pp. 3661–3667, 2013, doi: 10.1021/nn400671z.

- [38] The National Technology Roadmap for Semiconductors, Semicond. Ind. Assoc., San Jose, CA, USA, 2010.

- [39] D. G. Cacuci, "Sensitivity and uncertainty analysis," in Sensitivity Analysis. London, U.K.: Chapman & Hall, 2003, pp. 241–242.