## Investigation of power amplifier performance under load mismatch conditions

Downloaded from: https://research.chalmers.se, 2025-12-05 04:39 UTC

Citation for the original published paper (version of record):

Argaez Ramirez, R., Perez-Cisneros, J., Fager, C. (2021). Investigation of power amplifier performance under load mismatch conditions. 2021 IEEE Topical Conference on RF/Microwave Power Amplifiers for Radio and Wireless Applications, PAWR 2021: 41-43. http://dx.doi.org/10.1109/PAWR51852.2021.9375507

N.B. When citing this work, cite the original published paper.

© 2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, or reuse of any copyrighted component of this work in other works.

# Investigation of power amplifier performance under load mismatch conditions

Roger Argaez-Ramirez, Jose-Ramon Perez-Cisneros, Christian Fager Chalmers University of Technology, SE-412 96 Gothenburg, Sweden {roger.argaez.ramirez, jospere, christian.fager}@chalmers.se

Abstract—The time-varying loading conditions that power amplifiers (PAs) experience in active antenna systems degrade their overall performance. Consequently, the design of linear and highly-efficient PAs under mismatch is more important than ever. In this paper, different common and promising PA architectures, i.e. class-B, balanced, Doherty (DPA) and load-modulated-power-amplifier (LMBA), are analyzed under mismatch. Their sensitivity in terms of linearity, efficiency and output power is compared under a LTE signal excitation. Average drain efficiency (DE), average output power, normalized-mean-square-error (NMSE) as well as maximum output power variations are presented for each architecture as function of the voltage-standing-waveratio (VSWR). Thereby, the most suitable PA architecture to be integrated in active antenna systems may be identified.

*Index Terms*—active antenna system, power amplifier, class-B, Doherty, load modulated balanced amplifier, mismatch, linearity, efficiency.

#### I. Introduction

The use of large active antenna arrays for multiple-input multiple-output (MIMO) and beamforming systems in the upcoming 5G technology brings several challenges to power amplifier (PA) designers. It has been shown that PA linearity and efficiency will be affected by load variations due to mutual coupling and crosstalk in active antenna transmitters [1].

From the PA perspective, there are different mechanisms to compensate the degrading effect due to load variations [2]. These can be arranged in three main categories: 1) circulators/isolators which eliminate PA-antenna interactions and impose a one-directional signal flow; 2) tunable matching networks (TMNs) and resistance compression networks; 3) load insensitivity PA topologies. Even though TMNs seem to be a very promising solution, the necessary prior knowledge of the varying load together with losses associated to tuning components complicate its implementation. Therefore, load insensitive PA architectures have received increased attention in the last years. A method to calculate the load reflection coefficient without losses is proposed in [3].

In [4], a reconfigurable Doherty power amplifier (DPA) capable of working under different operation modes depending on the antenna voltage-standing-wave-ratio (VSWR) has been introduced. In addition, the authors in [5] proposed a method, by exploiting active load pulling in a multi-port combiner, to synthesize optimal impedance conditions not only for broadband peak and back-off operation but also to mitigate VSWR events at peak power. However, the major drawback of these architectures is that they also require knowledge of the

reflection coefficient to be compensated. However, this task is very challenging when these PA architectures are integrated in an active antenna system with coupled antenna elements [6].

Various PA topologies have been studied under mismatch. The DPA has been simulated in [7] and even compared with a class-AB amplifier in [8] for different reflection coefficients. Furthermore, a DPA was implemented and tested in a  $8\times1$  transmitting array under beam-steering mismatch [9]. On the other hand, the load modulated balanced amplifier (LMBA) has also been studied under mismatch and even a VSWR immune topology has been proposed in [10]. Nevertheless, most of the previous works only demonstrate the performance under mismatch when the PA architecture is driven by a continuous wave (CW).

This work aims to identify the most suitable PA architecture to be integrated in active antenna systems. Implementation of idealized Class-B, balanced PA, conventional DPA and LMBA have therefore been considered. A performance comparison under mismatch by using a typical modulated signal excitation is provided. The linearity, the average efficiency as well as the maximum and average output power performance of the different PA architectures are presented and compared at different ranges of VSWR.

### II. POWER AMPLIFIER ARCHITECTURES

It is well-known that each PA architecture offers different relevant properties. The class-B operation mode is a good reference of comparison, both in terms of linearity, efficiency and load sensitivity. The balanced architecture has good linearity and better mismatch tolerance than class-B due to the output hybrid coupler [11]. The DPA achieves moderate linearity and high-efficiency at backoff (BO) [12] by exploiting the load-modulation technique. Finally, the recently proposed LMBA obtains similar efficiency performance to the DPA, despite compromising linearity, by using a balanced structure [13]. Hence, the LMBA is a candidate for efficient and mismatch tolerant applications.

A very simple FET transistor model, based on a linear and a hyperbolic tangent function, is employed in this work.

$$I_{\rm DS} = f_{\rm GS}(v_{\rm GS}) \left[ \frac{I_{\rm MAX}}{2} \tanh(\alpha v_{\rm DS}) \right] \tag{1}$$

with

$$f_{\rm GS}(v_{\rm GS}) = \begin{cases} 0 & if & v_{\rm GS} < V_{\rm TH} \\ {\rm gm}(v_{\rm GS} - V_{\rm TH}) & if & V_{\rm TH} \le v_{\rm GS} \le V_{\rm SAT} \\ I_{\rm MAX} & if & V_{\rm SAT} < v_{\rm GS} \end{cases} \eqno(2)$$

where  $\alpha=1/(R_{\rm ON}*I_{\rm MAX}/2)$ ,  $I_{\rm MAX}={\rm gm}(V_{\rm SAT}-V_{\rm TH})$ .  $v_{\rm GS}$  and  $v_{\rm DS}$  are the gate and drain voltages, the  $R_{\rm ON}$  is the on resistance of the transistor and  $I_{\rm MAX}$  the maximum saturated current. The design parameters were:  $R_{\rm ON}=0.1,{\rm gm}=0.25,V_{\rm SAT}=0.5,V_{\rm TH}=-3.5$ .

The class-B amplifier will serve as a reference and building block for the remaining architectures. It is designed for a nominal  $R_{\rm opt}$  of 50  $\Omega$  load whilst both higher harmonics and the low frequency terms are short circuited in the output section.

For the balanced architecture, two of the above class-B PAs are connected by using ideal quadrature hybrid couplers at input and output sections. The isolation port is terminated by a 50  $\Omega$  resistance to dissipate the reflected waves from the load.

In this work, an ideal DPA is considered consisting of two independently-driven class-B PAs where the auxiliary one has an input phase delay of -90 degree and a modified drive profile to turn it on at 6 dB BO. The output combiner network consists of a quarter-wave transformer and a resistive 25  $\Omega$  nominal load, which have been calculated from the transistor parameters and the intended 6 dB BO operation.

Finally, the LMBA is derived from the balanced amplifier architecture. It consists of three amplifiers connected at the output by means of a hybrid coupler. Two of the amplifiers act as main amplifiers and the third one serves as a control signal to impose the load modulation in the ports where the main amplifiers are connected. The main amplifiers section works as a regular balanced amplifier, but when this reaches its saturation point, the third amplifier injects a signal to modulate the balanced ports achieving the optimal impedance of the main amplifiers and thus the overall efficiency is enhanced. The design equations for the LMBA at 6 dB output BO operation can be found in [13].

### III. PERFORMANCE COMPARISON UNDER LOAD MISMATCH USING MODULATED SIGNALS

The main objective of this work is to investigate the mismatch performance of the PA architectures above in a typical 20 MHz LTE application scenario. The four PA architectures were designed and simulated for the optimal load condition. The evaluation is then performed in terms of linearity, average drain efficiency, and output power degradation vs mismatch. Some of the architectures are inherently nonlinear. An ideal static pre-distorter, designed to compensate for the non-linearity at the nominal load, is therefore applied. The predistorter is fixed and not updated as the load is changed.

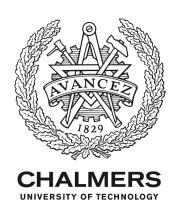

First, Fig. 1 compares the average efficiency for the four PA architectures. The highest average DE is located in an impedance different to the optimal load, except in the balanced PA, where its efficiency is symmetrical with respect to the center of the Smith-chart. It is important to note that, an excessive average can be explained by an oversaturated and hence very non-linear operation. The DPA and LMBA show a similar tendency of high average DE at smaller impedances whilst the class-B PA at larger impedances.

Fig. 1. Average drain efficiency in % with respect to the load impedance variations.

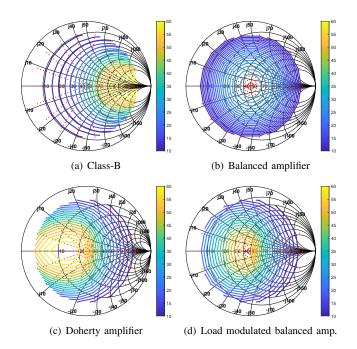

Fig. 2. NMSE in dB with respect to the load impedance variations, some regions are not showing a value, the reason is that it is below the -50 dB contour level.

Fig. 2 compares the linearity in terms of NMSE for the four PA architectures. The results demonstrates that, in general, high linearity can be found opposite to the location of high efficiency, except for the balanced PA, which is centered to the optimal load. A fair comparison is complicated with such information. As linearity and efficiency are competing goals, in many cases a trade-off must be achieved. In addition, the mismatch effect is not the same for all the architectures, due

to the different output combining and isolation mechanisms.

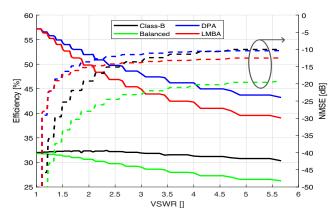

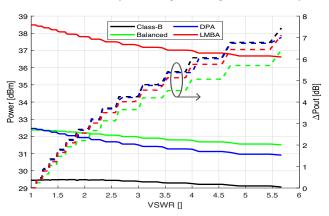

Fig. 3 presents a comparison of the PA architectures vs mismatch, where the performance from Fig. 1 and Fig. 2 has been evaluated within concentric circles in the Smith chart, corresponding to increasing VSWR values. The average efficiency and the average output power were averaged for increasing VSWR circles, whereas for the linearity, the worst case was obtained. Furthermore, the  $\Delta P_{OUT}$  was calculated as maximum - minimum output power values from such VSWR regions.

(a) Worst case linearity and average of average Drain Efficiency

(b) Average and  $\Delta P_{OUT}$  output power

Fig. 3. Performance parameters under mismatch

In Fig. 3(a) is clear that the balanced PA has the highest protection against mismatch in terms of linearity, whereas the DPA and the LMBA present similar response. Furthermore, the efficiency that the DPA and the LMBA can reach is comparable. Between the DPA and the LMBA, when the VSWR increases, the performance degradation of the LMBA is larger than the DPA. Fig. 3(b) shows how the power varies. The  $\Delta P_{OUT}$  is quite similar in the four architectures, with the balanced PA being slightly better. The LMBA reaches the higher output power as the output combines all the signals when present.

### IV. CONCLUSIONS

This work compares the performance of four common PA architectures under mismatch conditions. Although idealized

circuit implementations have been used, the comparison can give useful insights in the fundamental load-sensitivity of different PA architectures. For instance, both the DPA and the LMBA performed similarly regarding a high average DE. However, as the VSWR increases, a larger degradation in linearity is observed, making them suitable in weakly coupled active antenna systems. In contrast, the balanced PA performed best in maintaining its linearity under larger VSWR. A decision on a suitable architecture can only be based on the specific application requirements.

### ACKNOWLEDGMENT

This project has received funding from the European Union's Horizon 2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 860023. The authors would like to thank O. Iupikov from the Chalmers University of Technology, Gothenburg, Sweden, for providing the interface between MATLAB and ADS used in the simulations to get the tabulated data.

### REFERENCES

- [1] C. Fager et al., "Linearity and Efficiency in 5G Transmitters: New Techniques for Analyzing Efficiency, Linearity, and Linearization in a 5G Active Antenna Transmitter Context," in *IEEE Microw. Mag.*, vol. 20, no. 5, pp. 35-49, May 2019.

- [2] C. F. Gonçalves et al., "Switch-Based Variable Length Stubs Network for PA Load Sensitivity Reduction," in *IEEE Access*, vol. 7, pp. 152576-152584, 2019.

- [3] D. T. Donahue, P. Enrico de Falco and T. W. Barton, "Power Amplifier With Load Impedance Sensing Incorporated Into the Output Matching Network," in *IEEE Trans. Circuits Syst. I, Reg. Papers*.

- [4] N. S. Mannem et al., "24.2 A Reconfigurable Series/Parallel Quadrature-Coupler-Based Doherty PA in CMOS SOI with VSWR Resilient Linearity and Back-Off PAE for 5G MIMO Arrays," 2020 IEEE ISSCC, San Francisco, CA, USA, 2020, pp. 364-366.

- [5] C. R. Chappidi et al., "Multi-port Active Load Pulling for mm-Wave 5G Power Amplifiers: Bandwidth, Back-Off Efficiency, and VSWR Tolerance," in *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 7, pp. 2998-3016, July 2020.

- [6] D. Ji et al., "A Novel Load Mismatch Detection and Correction Technique for 3G/4G Load Insensitive Power Amplifier Application," in *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 5, pp. 1530-1543, May 2015.

- [7] O. Hammi et al., "Design and performance analysis of mismatched Doherty amplifiers using an accurate load-pull-based model," in *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 8, pp. 3246-3254, Aug. 2006.

- [8] N. Messaoudi et al., "A Comparative Study of Power Amplifiers' Sensitivity to Load Mismatch: Single Branch vs. Doherty Architectures," 2007 IEEE CCECE, Vancouver, BC, 2007, pp. 1543-1546.

- [9] B. Gashi et al., "Investigations of Active Antenna Doherty Power Amplifier Modules Under Beam-Steering Mismatch," in *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 10, pp. 930-932, Oct. 2018.

- [10] K. Vivien et al., "A Novel Double Balanced Architecture with VSWR Immunity for High Efficiency Power Amplifier," 2019 IEEE COMCAS, Tel-Aviv, Israel, 2019, pp. 1-5.

- [11] G. Berretta et al., "A balanced cdma2000 SiGe HBT load insensitive power amplifier," 2006 IEEE Radio and Wireless Symposium, San Diego, CA, 2006, pp. 523-526.

- [12] W. H. Doherty, "A new high-efficiency power amplifier for modulated waves," in *The Bell System Technical Journal*, vol. 15, no. 3, pp. 469-475, July 1936.

- [13] R. Quaglia and S. Cripps, "A Load Modulated Balanced Amplifier for Telecom Applications," in *IEEE IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 3, pp. 1328-1338, March 2018.