THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ENGINEERING

### Impact of adjacent dielectrics on the high-frequency performance of graphene field-effect transistors

Muhammad Asad

Terahertz and Millimetre Wave Laboratory Department of Microtechnology and Nanoscience - MC2 Chalmers University of Technology Gothenburg, Sweden 2021 Impact of adjacent dielectrics on the high-frequency performance of graphene field-effect transistors

Muhammad Asad

© Muhammad Asad, 2021 ORCID: https://orcid.org/0000-0002-5204-932X Terahertz and Millimetre Wave Laboratory Department of Microtechnology and Nanoscience - MC2 Chalmers University of Technology SE-412 96 Gothenburg, Sweden + 46 (0)31-772 1000

ISSN 1652-0769 Technical report MC2-423 Cover: A schematic of graphene field-effect transistor on single crystal diamond substrate.

Printed by Chalmers Reproservice Gothenburg, Sweden May 2021

# Abstract

Transistors operating at high frequencies are the basic building blocks of millimeter wave communication and sensor systems. The high velocity and mobility of carriers in graphene can open ways for development of ultrafast group IV transistors with similar or even better performance than that achieved with III-V based semiconductors. However, the progress of highspeed graphene transistors has been hampered by limitations associated with fabrication, influence of adjacent materials and self-heating effects.

This thesis work presents results of the comprehensive analysis of the influence of material imperfections, self-heating and limitations of the charge carrier velocity, imposed by adjacent dielectrics, on the transit frequency,  $f_{\rm T}$ , and the maximum frequency of oscillation,  $f_{\rm max}$ , of graphene field-effect transistors (GFETs). The analysis allowed for better understanding and developing a strategy for addressing the limitations.

In particular, it was shown that the GFET high-frequency performance can be enhanced by utilizing the gate and substrate dielectric materials with higher optical phonon (OP) energy, allowing for higher saturation velocity and, hence, higher  $f_{\rm T}$  and  $f_{\rm max}$ . This approach was experimentally verified by demonstration of enhancement in the  $f_{\rm T}$  and  $f_{\rm max}$  in GFETs with graphene channel encapsulated by the Al<sub>2</sub>O<sub>3</sub> layers. As a further step, GFETs on diamond, material with highest OP energy and thermal conductivity, were introduced, developed and fabricated, showing the extrinsic  $f_{\rm max}$  up to 50 GHz, at the gate length of 0.5  $\mu$ m, which is highest reported so far among the best published graphene and semiconductor counterparts.

The main achievements of this thesis work are as follows: (i) comprehensive study of correlations between graphene-dielectric material quality, small-signal equivalent circuit parameters and high-frequency performance of the GFETs; (ii) experimental verification of the concept of improving the GFET highfrequency performance via selection of adjacent dielectric materials with high OP energy; (iii) introducing the diamond as a most promising dielectric material for high-frequency GFETs; (iv) development of technology and demonstration of fully integrated X and Ku band GFET IC amplifiers with state-of-the art performance.

In conclusion, the routes of future development depicted in this thesis work may allow for enhancing the high-frequency performance of GFETs up to the level or even higher than that of the modern III-V semiconductor counterparts. **Keywords:** Graphene, field-effect transistors, high-frequency electronics, transit frequency, maximum frequency of oscillation, contact resistance, drift velocity, saturation velocity, diamond.

# List of publications

### Appended papers

This thesis is based on the following papers:

- [A] M. Asad, M. Bonmann, X. Yang, A. Vorobiev, K. Jeppson, L. Banszerus, M. Otto, C. Stampfer, D. Neumaier and J. Stake, "The dependence of the high-frequency performance of graphene field-effect transistors on channel transport properties", *IEEE J. Electron Devices Society*, 8, 457–464, 2020, doi: 10.1109/JEDS.2020.2988630.

- [B] M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier and J. Stake, "Graphene field-effect transistors with high extrinsic f<sub>T</sub> and f<sub>max</sub>", *IEEE Electron Device Letters*, 40, 131-134, 2019, doi: 10.1109/LED.2018.2884054.

- [C] M. Asad, K. Jeppson, A. Vorobiev, M. Bonmann, J. Stake "Enhanced High-Frequency Performance of Top-Gated Graphene FETs Due to Substrate-Induced Improvements in Charge Carrier Saturation Velocity", *IEEE Transactions on Electron Devices*, 68, 899-902, 2021, doi: 10.1109/TED.2020.3046172.

- [D] M. Asad, S. Majdi, A. Vorobiev, K. Jeppson, J. Isberg and J. Stake "Graphene FET on diamond for high frequency electronics", *Manuscript*, May 2021.

- [E] P. C. Feijoo, F. Pasadas, M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, D. Neumaier, J. Stake and D. Jim´enez. "Does carrier velocity saturation help to enhance f<sub>max</sub> in graphene field-effect transistors?", *Nanoscale Advances*, 2, 4179–4186, 2020, doi: 10.1109/TED.2021.3074479.

- [F] K. Jeppson, M. Asad, J. Stake "Mobility degradation and series resistance in graphene field-effect transistor", *IEEE Transactions on Electron Devices*, 2021, doi: 10.1039/c9na00733d.

- [G] A. Gareeb, M. Asad, M. -D .Wei, A. Vorobiev, J. Stake and R. Negra "Integrated 10-GHz Graphene FET Amplifier", Submitted to IEEE Journal of Microwaves, May 2021.

# Notations and abbreviations

### Notations

| $C_{ds}$       | Drain-source capacitance                          |

|----------------|---------------------------------------------------|

| $C_{gd}$       | Gate-drain capacitance                            |

| $C_{ox}$       | Gate oxide capacitance per unit area              |

| $E_F$          | Fermi energy                                      |

| $E_g$          | Band gap energy                                   |

| $E_{int}$      | Intrinsic electric field                          |

| E              | Applied electric field                            |

| $f_{max}$      | Extrinsic maximum frequency of oscillation        |

| $f_T$          | Extrinsic transit frequency                       |

| $f_{max-int}$  | Intrinsic maximum frequency of oscillation        |

| $f_{T-int}$    | Intrinsic transit frequency                       |

| $g_{ds}$       | Drain conductance                                 |

| $g_m$          | Transconductance                                  |

| h              | Planck's constant                                 |

| $h_{21}$       | Current gain                                      |

| $\hbar$        | Reduced Planck's constant                         |

| $j_D$          | Drain current density                             |

| $k_B$          | Boltzmann's constant                              |

| $L_d$          | Drain conductance                                 |

| L              | Gate length                                       |

| $L_{acc}$      | Access length                                     |

| $m^*$          | Carrier effective mass                            |

| $\mu_0$        | Low field mobility                                |

| $\mu_{eff}$    | Effective mobility                                |

| n              | Total carrier concentration                       |

| $n_0$          | Residual carrier concentration                    |

| $n_{eff}$      | Effective carrier concentration                   |

| $n_{m,doping}$ | Metal induced doping concentration                |

| $n_{mg}$       | Carrier concentration in graphene under the metal |

| p              | Hole concentration                                |

| q              | Elementary charge                                 |

| R              | Resistance                                        |

| $R_C$          | Total source and drain series resistance          |

|                |                                                   |

| $R_{mg}$       | Metal-graphene junction resistance |

|----------------|------------------------------------|

| $R_{ung}$      | Ungated contact resistance         |

| $R_D$          | Drain parasitic resistance         |

| $R_{DS}$       | Drain to source channel resistance |

| $R_G$          | Gate resistance                    |

| $R_i$          | Intrinsic gate source resistance   |

| $R_{pd}$       | Drain pad resistance               |

| $\hat{R_{pg}}$ | Gate pad resistance                |

| $R_S$          | Source parasitic resistance        |

| $R_{sh}$       | Sheet resistance                   |

| $ ho_C$        | Specific width contact resistivity |

| $\sigma_C$     | Conductivity                       |

| $\sigma_{min}$ | Minimum conductivity               |

| au             | Scattering time                    |

| $	au_{int}$    | Intrinsic transit time             |

| U              | Mason's unilateral gain            |

| $V_{Dir}$      | Dirac voltage                      |

| $V_{DS}$       | Drain to source voltage            |

| $v_d$          | Drift carrier velocity             |

| $v_F$          | Fermi velocity                     |

| $V_G$          | Gate voltage                       |

| $v_{sat}$      | Saturation velocity                |

| W              | Gate width                         |

### Abbreviations

| Al <sub>2</sub> O <sub>3</sub><br>Al<br>Au | Aluminum oxide<br>Aluminum<br>Gold |

|--------------------------------------------|------------------------------------|

| BOE                                        | Buffer oxide etchant               |

| BP                                         | Black phosphorus                   |

| Cu                                         | Copper                             |

| CVD                                        | Chemical vapor deposition          |

| CNT                                        | Carbon nanotube                    |

| DLC                                        | Diamond-like carbon                |

| FET                                        | Field-effect transistor            |

| FOM                                        | Figure of merit                    |

| FWHM                                       | Full width at half maximum         |

| GaAs                                       | Gallium arsenide                   |

| GFET                                       | Graphene field-effect transistor   |

| GHz                                        | Gigahertz                          |

| hBN                                        | Hexagonal boron nitride            |

| HEMT                                       | High electron mobility transistor  |

| HBT                                        | Heterojunction bipolar transistor  |

| IC                                         | Integrated circuit                 |

| InP                                        | Indium phosphide                   |

| LNA                                        | Low noise amplifier                |

| MAG           | Maximum available gain                      |

|---------------|---------------------------------------------|

| MESFET        | Metal-semiconductor field-effect transistor |

| $MoS_2$       | Molybdenum disulfide                        |

| Ni            | Nickel                                      |

| OP            | Optical phonon                              |

| Pd            | Palladium                                   |

| Pt            | Platinum                                    |

| $\mathbf{RF}$ | Radio frequency                             |

| SEM           | Scanning electron microscope                |

| $SiO_2$       | Silicon dioxide                             |

| $SrTiO_3$     | Strontium titanate                          |

| Т             | Temperature                                 |

| THz           | Terahertz                                   |

| Ti            | Titanium                                    |

| TLM           | Transfer length method                      |

| Si            | Silicon                                     |

# Contents

| A        | bstra | $\mathbf{ct}$                                      |                                                           | iii          |  |  |

|----------|-------|----------------------------------------------------|-----------------------------------------------------------|--------------|--|--|

| Li       | st of | public                                             | cations                                                   | $\mathbf{v}$ |  |  |

| N        | otati | ons an                                             | d abbreviations                                           | vii          |  |  |

| 1        | Intr  | oduct                                              | ion                                                       | 3            |  |  |

| <b>2</b> | Tra   | nsport                                             | properties of graphene                                    | 9            |  |  |

|          | 2.1   | Crysta                                             | al structure and electronic band structure                | 9            |  |  |

|          |       | 2.1.1                                              | Graphene electronic band structure                        | 10           |  |  |

|          |       | 2.1.2                                              | Graphene density of states and carrier concentration      | 11           |  |  |

|          |       | 2.1.3                                              | Intrinsic and extrinsic carrier concentration             | 12           |  |  |

|          | 2.2   | Carrie                                             | er transport in graphene and material imperfections       | 13           |  |  |

|          |       | 2.2.1                                              | Low-field mobility and high-field charge carrier velocity | 13           |  |  |

|          |       | 2.2.2                                              | Material imperfections                                    | 15           |  |  |

| 3        | Hig   | h-freq                                             | uency graphene field-effect transistors                   | 19           |  |  |

|          | 3.1   | -                                                  | and fabrication of high-frequency GFETs                   | 19           |  |  |

|          |       | 3.1.1                                              | High-frequency aspects of design                          | 19           |  |  |

|          |       | 3.1.2                                              | CVD graphene selected for high-frequency GFETs            | 21           |  |  |

|          |       | 3.1.3                                              | Fabrication development                                   | 22           |  |  |

|          |       | 3.1.4                                              | Low resistive graphene-metal junctions                    | 24           |  |  |

|          | 3.2   | DC pe                                              | erformance and models of GFETs                            | 25           |  |  |

|          |       | 3.2.1                                              | Transfer characteristics and drain resistance model       | 25           |  |  |

|          |       | 3.2.2                                              | Output characteristics, drain current and drift velocity  |              |  |  |

|          |       |                                                    | models                                                    | 26           |  |  |

|          | 3.3   | Mobil                                              | ity degradation                                           | 27           |  |  |

|          | 3.4   | B.4 High-frequency performance and models of GFETs |                                                           |              |  |  |

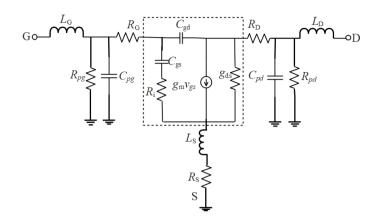

|          |       | 3.4.1                                              | Small-signal equivalent circuit model                     | 27           |  |  |

|          |       | 3.4.2                                              | Modelling of the $f_{\rm T}$ and $f_{\rm max}$            | 28           |  |  |

|          |       | 3.4.3                                              | Delay time analysis concept                               | 30           |  |  |

|          | 3.5   | Effect                                             | of self-heating on DC and high-frequency performance of   |              |  |  |

|          |       | GFET                                               | S                                                         | 31           |  |  |

| 4            |                                                                                                                                  | er-  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|------|

|              | formance of GFETs                                                                                                                | 33   |

|              | 4.1 Factors limiting the high-frequency performance of GFETs $$ .                                                                | . 33 |

|              | 4.1.1 Intrinsic limitations                                                                                                      |      |

|              | 4.1.2 Extrinsic limitations                                                                                                      | . 34 |

|              | 4.2 Dependence of high-frequency performance of GFETs on channel                                                                 | . 37 |

|              | <ul> <li>transport properties</li></ul>                                                                                          | ,    |

|              | 4.2.2 Effects of material imperfections on the high-field drift velocity                                                         |      |

| 5            | Impact of adjacent dielectrics on the high-frequency perfe                                                                       |      |

| 0            | mance of GFETs                                                                                                                   | 41   |

|              | 5.1 Effects of adjacent dielectrics on $f_{\rm T}$ and $f_{\rm max}$                                                             |      |

|              | 5.2 Dielectric materials with high optical phonon energy for high-                                                               | -    |

|              | frequency GFETs                                                                                                                  |      |

|              | 5.3 GFETs with graphene channel encapsulated by $Al_2O_3$ layers<br>5.4 GFETs on diamond substrates with enhanced high-frequency |      |

|              | performance                                                                                                                      |      |

|              | 5.4.1 GFETs on diamond-like carbon                                                                                               |      |

|              | 5.4.2 GFETs on single crystal diamond                                                                                            |      |

|              | 5.4.3 State-of-the-art GFETs                                                                                                     | . 46 |

| 6            | GFET IC amplifiers                                                                                                               | 49   |

|              | <ul><li>6.1 GFET RF amplifiers: status and perspectives</li></ul>                                                                |      |

|              | formance                                                                                                                         | . 50 |

|              | 6.2.1 Technology tolerances and matching network design .                                                                        | . 50 |

|              | 6.2.2 Technology development                                                                                                     | . 52 |

|              | 6.2.3 Characteristics of GFET IC amplifiers                                                                                      | . 53 |

| 7            | Conclusions and future outlook                                                                                                   | 55   |

| 8            | Summary of appended papers                                                                                                       | 59   |

| 9            | Appendix                                                                                                                         | 63   |

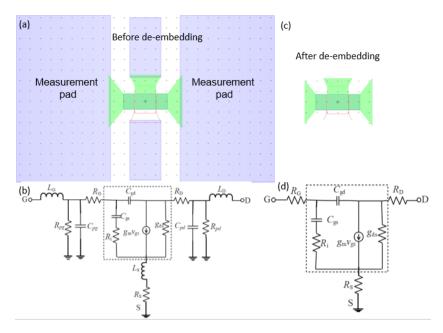

| U            | 9.1 S-parameter measurements                                                                                                     |      |

|              | 9.2 De-embedding                                                                                                                 |      |

|              | 9.3 Figures of merit of RF GFETs                                                                                                 |      |

|              | 9.4 Fabrication of GFETs and passive IC components                                                                               |      |

| •            |                                                                                                                                  |      |

|              | cknowledgments                                                                                                                   | 67   |

| Bi           | bliography                                                                                                                       | 69   |

| $\mathbf{A}$ | opended papers                                                                                                                   | 83   |

# Chapter 1 Introduction

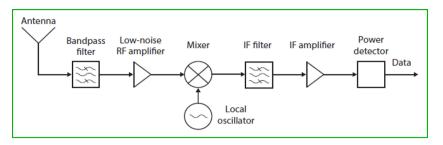

Ever since the very first field-effect transistor was fabricated by Shockley and Morgan in the Bell Labs [1], it brought revolution in semiconductor electronic technology. Transistors are the basis of all electronic equipment that is the part of our routine life, including computers, radios, mobile phones, displays, sensors and more. Continuous effort on scaling down the transistors to miniaturise the electronic equipment for the ease of consumers, resulted in new device concepts like laptops, tablets, smartphones and other handheld devices. The number of users of wireless devices has increased over the years. According to recent statistics, the number of mobile users worldwide at the end of 2020 has reached almost 5 billion, which means that billions of devices are connected through the Internet and exchange vast amounts of information in the form of text messages, pictures and videos with very high data rates [2]. With the current 4G technology, today's wireless networks operate at hundreds to thousands of Mbit/sec. The ongoing and upcoming 5G-6G revolution, is expected to connect billions more devices through Internet and wireless connections which operate at multi-Gbit/sec [3, 4]. All of these advancements in wireless communications is demanding high efficiency and bandwidth from the analog/radio frequency (RF) components. To cope with increasingly high data rates, it is necessary to develop analog front-ends of communication systems with high-speed transistors operating in millimeter wave bands and allowing for multi-gigabit data rates.

Up till now, the RF electronics industry demands have been fulfilled by Si-based transistors such as Si metal–oxide–semiconductor field-effect transistors (MOSFETs), SiGe heterojunction bipolar transistors (HBTs) and III-V compound metal-semiconductor field-effect transistors (MESFETs) and high electron mobility transistors (HEMTs) [5,6]. A general problem with current Si MOSFET and III-V HEMT technology is the continuous scaling down to meet the industrial demands, where field-effect transistors (FETs) have already reached their best performance, and no further significant improvement in performance can be expected in future [7]. One reason for this is the continuous development toward down-scaling led to extremely short gates, very thin gate dielectric, extremely thin channel thickness and, therefore, the related problems, such as short channel effects, low breakdown voltage, low operating voltage, large surface scattering and threshold voltage variations [5, 6, 8, 9].

Further advancement in RF electronics requires extremely small dimensions

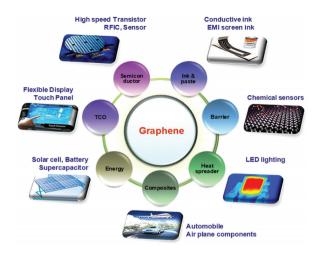

Figure 1.1: Scope of graphene in different research sectors [12].

and new material concepts. The choices are 2D materials such as graphene, Molybdenum disulfide ( $MoS_2$ ) and black phosphorus (BP). These are the potential candidates for new channel materials for RF transistors. Graphene is a promising candidate for next generation of FETs for modern high-frequency applications. Graphene was first demonstrated by Andre Geim and Konstantin Novoselov in 2004 via separation from graphite by mechanical exfoliation [10,11]. Over the years, scientists have explored many applications of graphene in different areas of science as shown in Fig. 1.1 [12]. However, transistor which are used for high-speed/high-frequency applications require fast charge carriers in the channel, which can react quickly to an applied electric field.

Graphene has exceptional charge carrier transport properties with intrinsic high mobility over  $10^5 \text{ cm}^2/Vs$  at room temperature [13,14], which is 100 times higher than that of Si, and charge carriers saturation velocity  $5 \times 10^5 \text{ cm/s}$  [15], which is about five times higher than that of Si. With these exciting features, graphene is a strong candidate for future RF electronics.

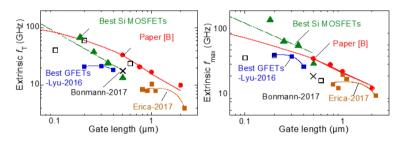

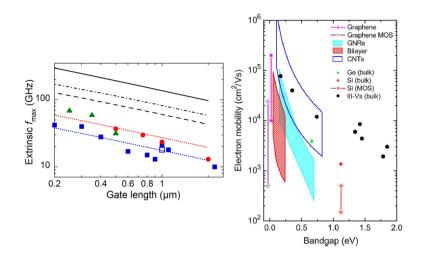

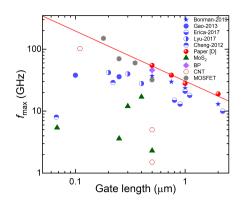

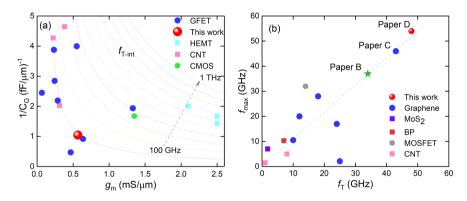

Attempts have been made realising graphene-based RF/microwave circuits such as frequency conversions [16, 17], phase shifters [18], frequency multipliers [19,20], power detectors [21,22], rectifiers [23], as well as amplifiers [24-27]. One of the most appealing applications of graphene transistors are the amplifiers, which are vet challenging only by a few published studies [25, 27, 28]. The highfrequency performance of the FETs is usually characterised by the two main figures of merit (FOMs), the transit frequency  $f_{\rm T}$  and the maximum frequency of oscillation  $f_{\rm max}$ , defined as the frequencies at which current gain and unilateral power gain drop to unity, respectively. A comprehensive review study made by Frank Schweirz in 2013 on RF graphene field-effect transistors (GFET) shows that the  $f_{\rm T}$  of GFET reveals scaling behaviour and even competes well with other conventional RF FETs [29]. On the other hand, the maximum frequency of oscillation  $f_{\text{max}}$ , which is an important FOM for RF analog front-ends, is reported to be consistently lower and does not scale with the gate length [29]. Analysis of previous studies indicates that the high-frequency performance in GFETs is limited by number of intrinsic and extrinsic factors [29–38]. The

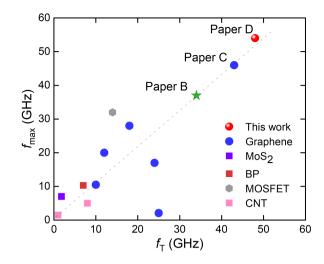

Figure 1.2: Benchmarking the different RF FET technologies by extrinsic maximum frequency of oscillation  $(f_{\text{max}})$  and transit frequency  $(f_{\text{T}})$  at similar gate lengths. Extrinsic  $f_{\text{max}}$  versus  $f_{\text{T}}$  of GFETs developed in this work is shown for 0.5  $\mu$ m gate length [42,43]. It is compared with other GFET using CVD, epitaxial and exfoliated graphene [30,32,35,44,45]. It is also compared with the FETs of other 2D materials including BP and MoS<sub>2</sub> [46,47], CNT [48,49] and MOSFET [50] at similar gate lengths.

intrinsic factor hindering realisation of competitive high-frequency GFETs is associated with zero-bandgap in monolayer graphene and, hence, lack of drain current saturation, which results in relatively high drain conductance  $(g_{\rm ds})$  and lower  $f_{\rm max}$  [29]. An approach for addressing the issue by inducing bandgap in graphene turned out to be not promising, because it resulted in simultaneous reduction in the carrier mobility [29,31,39]. An alternative approach to address the high  $g_{\rm ds}$  is the increase in the charge carrier velocity in GFETs by proper selection of the adjacent dielectric materials with relatively high optical phonons (OPs) energies [37, 40, 41].

Extrinsic limitations of the charge carrier transport in GFETs, degrading the high-frequency performance, are associated, mainly, with imperfections in graphene, interfaces and adjacent dielectrics, including the remote phonon scattering. In this thesis work, the focus was on addressing and overcoming the extrinsic limitations, which allowed for using efficiently the graphene superior electronic properties and enabling the high-frequency electronics applications. Fig. 1.2 shows the extrinsic  $f_{\text{max}}$  versus  $f_{\text{T}}$  reported in this work in comparison with other RF GFETs and RF transistors of 2D materials and carbon nanotube as well as MOSFETs for similar gate length. As it can be seen, this work represents state-of-the-art technology of high-frequency graphene field-effect transistors.

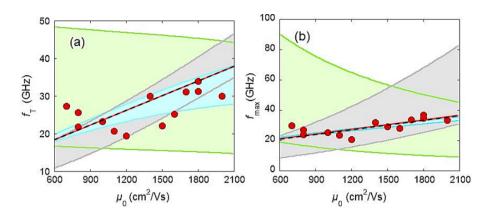

In this thesis work, first, efforts have been made for better understanding the high-frequency performance limitations caused by the graphene quality, see Paper [A]. The low-field carrier mobility was selected as the most appropriate material-quality parameter because of its combined response to different types of material imperfections. The correlations between low-field mobility and high-frequency performance of GFETs are observed, analysed and explained by using and combining the semi-empirical models of drain resistance, charge carrier velocity, velocity saturation and small-signal equivalent circuits model. It was found that a promising approach for improving the GFET high-frequency performance is the selection of adjacent dielectric materials with OP energy higher than that of SiO<sub>2</sub>, i.e. 55 meV, allowing for higher saturation velocity and, hence, higher  $f_{\rm T}$  and  $f_{\rm max}$ .

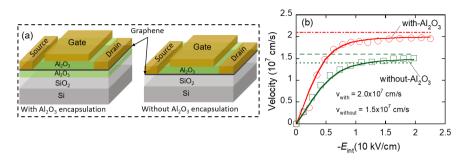

Paper [B] reports on GFETs still fabricated on SiO<sub>2</sub> substrate and with Al<sub>2</sub>O<sub>3</sub> gate dielectric, but with improved quality of the graphene and adjacent dielectrics, which allowed for minimising emission of carriers from traps and, hence, achieving the drain current saturation trend following that of the velocity. This resulted in state-of-the-art extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  up to 40 GHz at the 0.5  $\mu$ m gate length, which is comparable or even better than those of the best published Si MOSFETs. However,  $f_{\rm T}$  and  $f_{\rm max}$  of the GFETs are still limited by the inelastic carrier-phonons interactions of the graphene and adjacent dielectrics. In this work, it was suggested replacing the SiO<sub>2</sub> by Al<sub>2</sub>O<sub>3</sub> with higher OPs energy of 87 meV, since it can be readily realised with the developed technology.

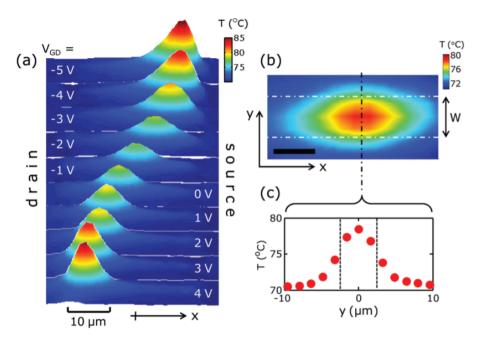

The proposed concept of encapsulation of the graphene channel by dielectric layers with relatively high OP energy was realised experimentally in Paper [C]. The GFETs with  $Al_2O_3$  gate dielectric and  $Al_2O_3$  buffer layer between the graphene channel and  $SiO_2/Si$  substrate were fabricated and characterised. The GFETs reveals extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  up to 43 and 46 GHz, respectively, at 0.5  $\mu$ m gate length, which were again higher than those of the best published GFETs with similar gate length. Paper [E], presented in collaboration with Barcelona University, reports on comprehensive modelling of the charge carrier transport and high-frequency performance of GFETs presented in Paper [B]. In particular, it was shown that high thermal conductivity of substrate is a crucial property of GFETs for high-frequency applications. At relatively high drain fields, above approx. 1 V/ $\mu$ m, required for the carrier velocity saturation, the channel temperature in GFET on  $SiO_2/Si$  substrate can be as high as 600 K, due to intensive Joule heating provoked by the low thermal conductivity of the  $SiO_2$  layer. The increase in the channel temperature induces thermally generated carriers, which result in the reduction of the saturation velocity and, hence, degradation of the  $f_{\rm T}$ . On the other hand, it is shown that the above effect allows for relative saturation of the drain current resulting in reduced drain conductance and, hence enhanced  $f_{\text{max}}$ .

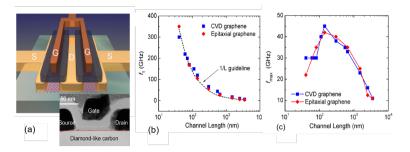

Paper [D] presents results of further development of the approach of enhancing the high-frequency performance of GFETs by selecting the adjacent dielectric materials with relatively high OP energy. Analysis indicates that most suitable candidate is the diamond, since its OPs energy can be as high as 165 meV, which is comparable with that of the graphene zone-edge OPs. In this case, the carrier velocity in GFETs is entirely defined by the intrinsic graphene OPs. The GFETs on diamond substrates were fabricated and characterised. The saturation velocity of  $3.7 \cdot 10^7$  cm/s and state-of-the-art extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  up to 55 GHz at 0.5  $\mu$ m gate length, were demonstrated with promising scaling down behaviour. These  $f_{\rm T}$  and  $f_{\rm max}$  values are highest reported so far for GFETs with similar gate length. In Paper [F] a first-order mobility degradation model is used to separate information about mobility degradation and series resistance for a set of GFETs of different channel lengths. Mobility degradation behaviour was observed for GFET devices with the mobility being reduced to half for a voltage-induced charge carrier density of  $10^{13}$  cm<sup>-2</sup>. The model is important for accurate extraction of parameters and characterising the GFETs.

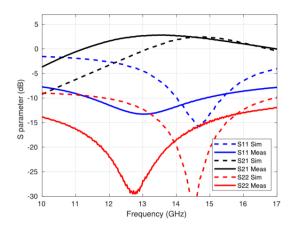

Finally, Paper [G] presents the X and Ku band fully-integrated GFET IC amplifiers designed, in collaboration with Aachen University, fabricated and measured. The amplifiers utilise the GFETs with the state-of-the-art high-frequency performance developed and presented in Papers [A]-[D]. Peak gains of 4.2 dB and 2.9 dB at 10.6 GHz and 13.6 GHz were measured, respectively, for each GFET amplifier. The achieved gain values are higher than those reported so far for the GFET IC amplifiers.

The thesis outline is as follows. In chapter 2, graphene's electronic properties relevant for the high-frequency electronics applications are considered. Chapter 3 describes the specifics of the high-frequency GFET's designs, fabrication, DC and RF models and performances, as well as effects of the self-heating. In chapter 4, the effects of material imperfections on the high-frequency performance of GFETs are analysed. Chapter 5 describes the GFETs with enhanced highfrequency performance utilising dielectric materials with high optical phonon energy. Chapter 6 reviews current status of GFET IC amplifiers and presents the developed and fabricated Ku-band IC amplifier based on high performance GFETs. Finally, the thesis is concluded with a summary and future outlook.

## Chapter 2

# Transport properties of graphene

The analog front-ends of advanced communication systems require high speed transistors operating at mmWave frequencies and providing a large bandwidth. Two main figures of the merit of RF transistors are the  $f_{\rm T}$  and  $f_{\rm max}$ , and both depend on the charge carrier velocity in the channel. Thus, materials with high mobility and high charge carrier saturation velocity are required as channel material in order to realise such RF transistor devices. In this context, monolayer graphene is a promising candidate with intrinsically high mobility and charge carrier saturation velocity. This chapter describes the basic properties of graphene which make it qualified for high-frequency analog applications. The specific graphene properties such as V-shaped band structure, charge carrier density, material imperfections and low- and high-field charge carrier transport will be discussed. It begins with the quote of Nobel laureate Andre Geim: 'Graphene opened up a material world we didn't even know existed.'

### 2.1 Crystal structure and electronic band structure

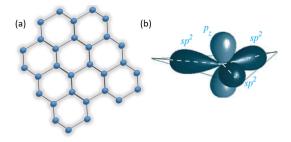

The existence of a single sheet of atoms was not considered probably due to the atom's thermodynamic instability [51], until the present century, when scientists managed to peel off a 2D monolayer of carbon atoms from bulk graphite [10, 11]. Fig. 2.1(a) shows the sheet composed in a tightly bonded honeycomb-like hexagonal structure of carbon atoms also called 'graphene' [52]. Carbon is a material in Group-IV of the periodic table and has four valence electrons in its outermost shell. Carbon atoms have the tendency to form three symmetrical covalent bonds because the 2s,  $2p_x$  and  $2p_y$  orbitals can be transformed into three symmetric  $sp^2$  hybrid orbitals with planar symmetry as shown in Fig. 2.1 (b). Notice that the  $p_z$  orbital remains unhybridised. These  $sp^2$ -hybridised carbon atoms with triangular planar structure form  $\sigma$ -bonding with the neighbouring carbon atoms and replicate the process to form a 2D crystal structure, earlier defined as a graphene sheet. The distance to the

Figure 2.1: (a) The graphene crystal structure. (b) The symmetrical covalent bonding of carbon atoms and the tetrahedral symmetry of  $sp^3$  hybrid orbital [53].

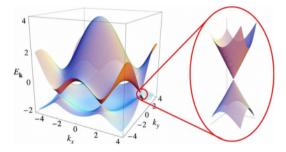

Figure 2.2: Electronic dispersion in the honeycomb graphene lattice calculated using tight-binding approximation. The conductance band touches the valence band at the points named Dirac points [54].

nearest neighbouring carbon atom is 0.142 nm. The graphene sheet shows strong mechanical strength and very high electrical conductivity. Now the question is: Where does this mechanical strength and electrical conductivity come from? The strong  $\sigma$ -bondings in the planar structure provide the mechanical strength to the material, and the excellent electrical conductivity originates from the unhybridised  $p_z$  orbital, which forms much weaker  $\pi$ -bonding with its neighbouring atoms. Below, we are focussing on the electronic transport properties of graphene.

### 2.1.1 Graphene electronic band structure

To understand the electronic transport properties of graphene, it is important to understand its electronic band structure. Theoretically, the concept of graphene electronic band structure was studied a long time ago in order to explain the properties of graphite. A simplified energy-momentum relation using theoretical argument, the tight-binding approximation for graphene lattice is described by assuming that the electrons can jump to the three nearest neighbouring atoms as [54]

$$E(k)^{\pm} = \pm \alpha \sqrt{1 + 4\cos\frac{\sqrt{3}a}{2}k_x\cos\frac{a}{2}k_y + 4\cos^2\frac{a}{2}k_y}.$$

(2.1)

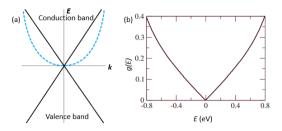

Here,  $\alpha$  is a fitting parameter and k is the wave vector. The (+) and the (-) signs correspond to the conduction and valence bands, respectively. The band structure calculated using eq.(2.1) is shown in Fig. 2.2. The conduction

Figure 2.3: (a) Energy dispersion relation in conventional semiconductors (dashed line) and in graphene (solid line) close to the Dirac point. (b) The graphene density of state close to the Dirac point [54].

and valence bands touch at the conjugate K-points called the Dirac points. The Dirac points, also known as the charge neutrality points, express a key feature of graphene, i.e. zero-bandgap nature of monolayer graphene. The zero bandgap nature of graphene in the context of graphene transistor is a very important phenomenon and is the key to understanding the electrical characteristics of graphene transistors. In conventional semiconductors, the energy and momentum relation involves reduced mass of the free carriers and can be expressed as:

$$E(k) = \frac{\hbar^2 k^2}{2m^*}.$$

Here,  $\hbar$  is the Planck's constant, k is a wave vector and  $m^*$  is the effective mass of the charge carrier. Both electrons and holes experience different effective mass in a semiconductor, which result in different total energy; thus, holes and electrons behave differently. Zooming in close to the Dirac point in Fig. 2.2 reveals the highly symmetrical nature of the dispersion relation in the vicinity of the Dirac point. According to the tight-binding approximation, the graphene quasi particles exhibit a linear energy dispersion relation. A linear conical dispersion relation in the vicinity of the Dirac point is described in terms of the Fermi velocity  $(v_F)$  as:

$$E(k) = \pm \hbar v_F \sqrt{k_x^2 + k_y^2}.$$

(2.2)

Fig. 2.3 shows the parabolic relation of E versus k for common semiconductors in comparison with graphene shown by the linear curve. The linear dispersion relation indicates a massless nature of graphene charge carriers. Normally, massless particles like fermions governed by the Dirac equation are described by the Fermi velocity instead of the velocity of light. This means that both electrons and holes in graphene exhibit a constant Fermi velocity  $v_{\rm F} = 10^6$ m/s, irrespective in momentum, which indicates the origin of superior carrier transport properties of graphene. It further shows that, theoretically, the transport properties of electrons and holes are the same in graphene.

### 2.1.2 Graphene density of states and carrier concentration

The density of states is another important aspect of the electronic band structure since it defines the carrier concentration. The density of states (number of states per unit energy interval) in graphene close to the Dirac point is derived from the momentum energy relation as:

$$g(E) = \frac{2|E|}{\pi(\hbar v_f^2)}.$$

(2.3)

The density of states is zero at zero Fermi energy. Zero density of states makes graphene a semiconductor-like material, while zero-bandgap attributes' resemblance to graphene is a semi-metal-like material. The density of states derived from eq. (2.3) is shown in Fig. 2.3(b). It can be seen that the density of states increases as the Fermi energy level moves away from the charge neutrality point.

The charge carrier concentration is defined by the carrier distribution in the valence or conduction band and is given by the density of state (g) times the probability (f) that a state is occupied or empty:

$$n = g(E) \cdot f_f(E). \tag{2.4}$$

Here  $f_f(E)$  is the Fermi-Dirac probability function. The carrier concentration for the volume of a given system is obtained by taking the integral of eq. (2.4). Solving the integral of the above equation gives a simple analytical expression relating the charge carrier concentration in graphene directly to the Fermi level:

$$n = \frac{g}{4 \cdot \pi} \left(\frac{E_f}{\hbar v_f}\right)^2. \tag{2.5}$$

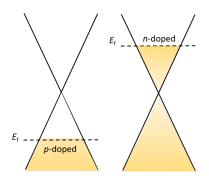

The position of the Fermi energy  $(E_{\rm f})$  level is determined by the carrier type and the density in the graphene sheet. In conventional semiconductors, according to energy band theory, when the Fermi energy level lies at the midgap, the semiconductor is called the intrinsic semiconductor. In the pdoped semiconductor, the  $E_{\rm f}$  moves closer to valence band, and in the n-doped semiconductor, the  $E_{\rm f}$  moves closer to the conduction band. Quite similar but in monolayer graphene where bandgap does not exist, we see the Fermi energy level movement with reference to the Dirac point. So in cases when  $E_{\rm f}$  is higher than the Dirac point and lie within the conduction band, the graphene is n-doped, and when  $E_{\rm f}$  is below the Dirac point into the valence band region, the graphene is p-doped. Fig. 2.4 shows the simplified illustration of the above mentioned two situation when the  $E_{\rm f}$  is in the valence band and in the conduction band.

#### 2.1.3 Intrinsic and extrinsic carrier concentration

At this stage, it is important to distinguish between intrinsic and extrinsic graphene properties. Graphene can be defined as being of intrinsic nature, when the Fermi energy level lies exactly at the Dirac point, which means that there is no external doping. In such a system, at T = 0 K the conduction band is completely empty and the valence band is completely filled, and the Fermi level lies at the Dirac point [55]. With this definition in mind, the graphene used in all practical applications is extrinsic in nature. At temperature T > 0, there are thermally generated carriers present at all times in the system. The

Figure 2.4: Simplified illustration of Fermi energy level in p-doped and n-doped graphene.

temperature dependent thermally generated carrier density is given by [56]:

$$n_{th} = \frac{\pi}{6} \left(\frac{k_B T}{\hbar v_f}\right)^2 \tag{2.6}$$

where  $k_B$  is the Boltzman constant. In the absence of external doping, one can say that  $n_{th}$  is the intrinsic carrier concentration of graphene at a given temperature. When the graphene is transferred onto a foreign substrate, usually the charged impurities at the interface or in the substrate oxide induce the so-called residual charge carrier concentration  $(n_i)$  in the graphene. Considering graphene in a transistor configuration, where it acts as the transistor channel, one can make graphene extrinsic via doping by applying positive or negative gate voltage. The net charge carrier concentration in the extrinsic graphene is given as:

$$n = \sqrt{n_0^2 + (C_{ox} \cdot (V_G - V_{Dir})/q)^2}$$

(2.7)

Here,  $n_0 = \sqrt{n_i^2 + n_{th}^2}$  is minimum carrier density,  $C_{ox}$  is gate oxide capacitance per unit area,  $V_G$  is the gate voltage and q is the elementary charge.

# 2.2 Carrier transport in graphene and material imperfections

The high-frequency performance of graphene transistors depends on the charge carrier transport properties of graphene. The charge carrier transport occurs in the graphene sheet under the influence of an external electric field and is characterised by the low-field mobility and high-field carrier velocity.

### 2.2.1 Low-field mobility and high-field charge carrier velocity

The way the charge carrier responds to the electrical field is characterised by the low-field mobility and the high-field charge carrier velocity. Charge carrier mobility is an important material parameter at the lower field and is fundamental in describing the electrical conductivity, the resistivity and velocity of the charge carrier in that material. The mobility in this work is, typically,

|                                  | Si   | InAs | GaN | GaAs | $MOS_2$  | BP     | graphene |

|----------------------------------|------|------|-----|------|----------|--------|----------|

| Mobility $(10^3 \text{cm}^2/Vs)$ | 1.4  | 33   | 1.6 | 8    | 0.2 [58] | 1 [59] | 100 [13] |

| $E_{g}(eV)$                      | 1.12 | 0.36 | 3.4 | 1.43 | 1.8      | 2      | 0        |

Table 2.1: COMPARISON OF GRAPHENE MOBILITY WITH OTHER 2D MATERIALS AND SEMICON-DUCTORS.

extracted from the transfer characteristic of the GFET or from the output characteristics at a low electric field. As mentioned above, graphene possess high intrinsic carrier mobility. Table 6.1 shows the mobility of the graphene in comparison with other 2D materials and conventional semiconductors at room temperature. However, the RF transistors operate at very high electric field, where the charge carrier velocity is considered to be the more appropriate parameter. In particular, the intrinsic transit frequency of a FET device is defined by the velocity as  $f_{\rm T} \approx v_{\rm d}/(2\pi L)$ , where  $v_{\rm d}$  is the charge carrier velocity and L is the gate length. Charge carrier drift velocity under the applied electric field is modelled by [57]:

$$v_d = \frac{\mu_{eff} E_{int}}{(1 + (\frac{\mu_{eff} E_{int}}{v_{sat}})^{\beta})^{1/\beta}}.$$

(2.8)

Here,  $\mu_{\rm eff}$  is the effective low-field mobility,  $v_{\rm sat}$  is the saturation velocity,  $\beta$  is a fitting parameter and  $E_{\rm int}$  is the intrinsic electric field along the channel. From eq. (2.8), it can be seen that the velocity is directly proportional to the electric field. With increasing the electric field the velocity of the charge carriers increases and continue to increase until it becomes insensitive to further increase in the applied field and becomes saturated, approaching the value called 'saturation velocity'. The charge carrier velocity in the FETs channel can be evaluated from the drain current and also from the RF transit frequency  $f_{\rm T}$  by using the delay time analysis. These methods will be considered in detail in the next chapters. Saturation velocity can also be evaluated theoretically by using the model which assumes that  $v_{\rm sat}$  is limited by inelastic emission of optical phonons [44, 56]:

$$v_{sat} = \frac{2}{\pi} \frac{w_{OP}}{\sqrt{\pi n}} \sqrt{1 - \frac{w_{OP}^2}{4\pi n v_f^2}} \frac{1}{N_{OP} + 1}.$$

(2.9)

Here,  $\hbar w_{OP}$  is the optical phonon energy,  $N_{OP} = 1/[exp(\hbar w_{OP}/kT) + 1]$  is the phonon occupation and n is the charge carrier concentration. The above equation takes into account the temperature dependence of  $v_{\text{sat}}$  also. By assuming a negligible effect of temperature on  $v_{\text{sat}}$ , a more simple approximation of  $v_{\text{sat}}$  can be used [40]:

$$v_{sat} = \frac{2}{\pi} \frac{w_{OP}}{\sqrt{\pi n}},\tag{2.10}$$

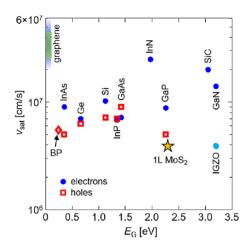

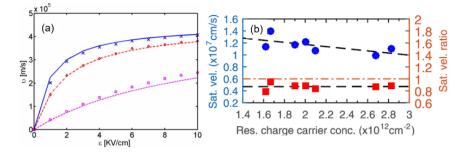

which indicates that for a given total carrier concentration n, the  $v_{\text{sat}}$  is defined by the optical phonon energy  $\hbar w_{\text{OP}}$  of the material. The  $v_{\text{sat}}$  for graphene on SiO<sub>2</sub> substrate was recorded to be in the range of  $1-2 \times 10^7$  cm/s and is limited by the relatively low surface optical phonon energy  $\hbar w_{\text{OP}} = 55$ meV of SiO<sub>2</sub> [44,56]. In Paper [C] and [D], we systematically investigated

Figure 2.5: Charge carrier saturation velocity of graphene at room temperature in comparison with that of conventional semiconductors [60]. Note: The green bar overlapping the blue bar represents the velocity measured in this work by using CVD graphene on different substrate materials.

the effects of  $\hbar w_{\rm OP}$  of substrate dielectrics on the  $v_{\rm sat}$  and the GFET highfrequency performance. Fig. 2.5 shows the saturation velocity of the graphene in comparison with other 2D materials and semiconductors. It can be seen that graphene is the material with the highest  $v_{\rm sat}$  making it graphene a promising channel material for RF electronics. The  $v_{\rm sat}$  measured in hexagonal boron nitride (hBN) encapsulation graphene Hall bar devices is in the range of 3-6  $\times 10^7$  cm/s [15], because the hBN  $\hbar w_{\rm OP}$  is more than 100 meV. As reported in Paper [D], the saturation velocity measured in the top-gated two finger GFETs on diamond, which is material with highest OP energy, can be as high as  $v_{\rm sat}=3.3 \times 10^7$  cm/s.

#### 2.2.2 Material imperfections

As mentioned above, graphene possesses an extremely high intrinsic mobility of charge carriers. However, graphene is atomically thin layer of atoms and is very sensitive to its surrounding materials. In practical devices, the graphene mobility drops to several fold due to the number of extrinsic factors. For instance, the very first paper studying the field-effect phenomenon in a graphene sheet was submitted by Novoselov [10] in 2004, where he reported the mobility up to  $10^4 \text{ cm}^2/\text{Vs}$  at room temperature. A few years later, Bolotin et al. reported that the carrier mobility in graphene can be as high as  $10^5 \text{ cm}^2/\text{Vs}$ at room temperature [13]. The reasons for such difference is that Novoselov et al. prepared the graphene devices on a  $SiO_2$  substrate where the charge carrier impurities at the interface and in the oxide limit the charge carrier mobility. In contrast, the paper by Bolotin et al. reports on devices fabricated by using suspended single layer graphene. Free standing graphene preserves its high quality close to ideality and the mobility in such super clean graphene sheet is neither limited by lattice acoustic phonons scattering at high temperature nor by the impurity scattering [61-63]. However, the freestanding graphene is not viable from the device fabrication point of view. Graphene in devices is

inevitably have to be contact with foreign materials and dielectric substrates for real electronic applications. As the graphene is transferred onto a dielectric substrate, its intrinsic superior properties degrade dramatically. This is because carrier scattering rate increases many fold due to the number of different extrinsic scattering mechanisms such as remote interfacial phonon scattering, charged impurity scattering, scattering by ripples, neutral defect scattering and resonant scattering [64]. When various scattering mechanisms are involved, their relative contributions to the net mobility can be counted using Matthiessen's rule as [65]:

$$\tau^{-1} = \tau_{cl}^{-1} + \tau_{sr}^{-1} + \tau_{op}^{-1} + \tau_{LA}^{-1} + \tau_{corr}^{-1} = \sum \tau_x^{-1}.$$

(2.11)

Here,  $\tau$  is the scattering time between two scattering events, and the subscript (cl) represents Coulomb scattering, i.e. by charged impurities, (sr) represents short-range scattering, i.e. scattering by neutral defect, (op) indicates remote optical phonon scattering, (LA) longitudinal acoustic phonons, and (corr) is for corrugations or graphene ripple scattering. All these scattering mechanisms contribute to mobility through the expression [66, 67]:

$$\mu = \frac{qv_F^2\tau}{E},\tag{2.12}$$

where E is the electric field. Coulomb scattering is the long-range scattering mechanism associated with the charged impurities at the interface and in the gate or substrate dielectrics. Long-range scattering is considered to be the main scattering mechanism controlling the carrier transport in graphene FET devices at relatively low carrier concentration [55]. Short-range scattering is also present in graphene and associated mainly with the lattice defects. It dominates at relatively high carrier concentration and in cleaner samples. Another extrinsic scattering mechanism is the remote OPs at low temperature and is inversely proportional to the carrier concentration simply because higher carriers densities lead to a higher scattering rate [61]. The other significant scattering effects can be due to the ripples in graphene and is partially related to the substrate roughness [68]. To bring graphene-based technology to a higher level, it is necessary to overcome the limitations of extrinsic scattering mechanisms.

In this context, an endeavor to reach the intrinsic graphene transport properties comes with the approach of using an exfoliated hBN layers as the substrate material. The hBN is a wide bandgap material. It has hexagonal lattice symmetry like graphene crystal and has a lattice mismatch of 2.0%. Recently, room temperature mobility well above  $70 \times 10^4$  cm<sup>2</sup>/Vs was reported for hBN encapsulated graphene Hall bar devices [14,69], indicating that hBN is a promising dielectric material for graphene devices. However, it is not yet feasible for wafer scale device fabrication.

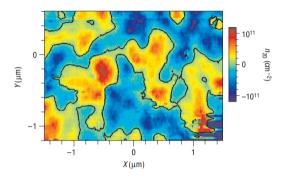

An inevitable feature associated with material imperfections is spatially inhomogeneous screened Coulomb potential created by charged impurities in the dielectric layers adjacent to the graphene sheet. The charged impurities are typically associated with the oxygen vacancies in the adjacent dielectrics and/or water molecules trapped at the graphene-dielectric interfaces [71,72]. This causes a spatially inhomogeneous random network of two dimensional

Figure 2.6: Mapping of the charge carrier density measured at the Dirac point [70].

electrons and holes puddles in the graphene sheet as shown in Fig. 2.6. These laterally inhomogeneous densities of charged impurities have been reported in many studies [62–64, 66, 73]. The inhomogeneous electron and hole puddles define the minimum conductivity, measured at the Dirac point.

The variations of the GFET performance from device to device over the chip surface, observed in this thesis work, is largely attributed to the spatially inhomogeneous material quality. We exploited this largely distributed material quality over the chip as a tool to study the effect of charge carrier transport in a channel on the high-frequency performance of GFETs in Paper [A]. Furthermore, we also take into consideration the variations in GFET performance when designing GFET IC amplifiers, as discussed in Paper [G].

## Chapter 3

# High-frequency graphene field-effect transistors

In this chapter, features of the design, fabrication and operation of the highfrequency GFETs are considered, including modeling of the charge carrier transport and high-frequency performance. General operational principles of GFET are similar to that of MOSFET, however, there are some distinguishable features associated, first of all with zero bandgap in monolayer graphene which results, in particular, the ambipolar transport in the GFET channel.

### 3.1 Design and fabrication of high-frequency GFETs

### 3.1.1 High-frequency aspects of design

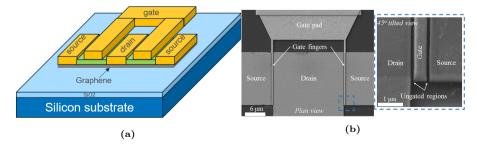

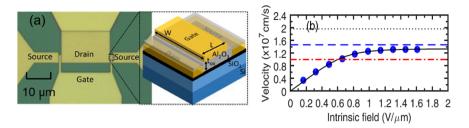

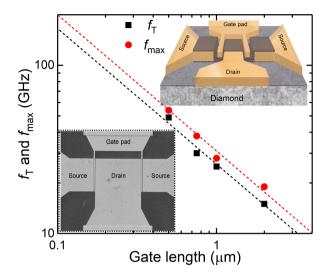

In this work, the GFETs in the planar top-gate configuration and two gate fingers design were developed and optimized for the highest high-frequency performance, as shown in Fig. 3.1. The high-frequency performance of RF FETs are characterised using the FOMs, which are the transit frequency  $f_{\rm T}$ and maximum frequency of oscillation  $f_{\rm max}$  and can be expressed using the

Figure 3.1: (a) A schematic cross-section view of the GFET. (b) SEM of a two fingers GFET with two source, a drain and gate electrodes. Magnified planar and  $45^{\circ}$  tilted view of the gate area in (b) corresponding to the dashed line box.

small-signal equivalent circuit model as [74]:

$$f_T = \frac{f_{T-int}}{1 + g_{ds}R_C + \frac{C_{gd} \cdot g_m \cdot R_C}{C_{gs} + C_{gd}} + \frac{C_{GP}}{C_{gs} + C_{gd}}},$$

(3.1)

$$f_{\max} = \frac{g_m}{4\pi C_{gs}} \frac{1}{\sqrt{g_{ds} \left(R_i + \frac{R_C}{2} + R_G\right) + g_m R_G \frac{C_{gd}}{C_{gs}}}},$$

(3.2)

where,  $g_{\rm m}$  is the transconductance and  $g_{\rm ds}$  is the drain conductance.  $R_{\rm C}$  is the contact resistance,  $R_{\rm i}$  is the charging resistance of the gate-source capacitance and  $R_{\rm G}$  is the gate resistance. The  $C_{\rm gs}$  and  $C_{\rm ds}$  are the gate-source and gate-drain capacitances, and  $C_{\rm GP}$  is the gate-pad capacitance. The  $f_{\rm T-int} = g_{\rm m}/2\pi(C_{\rm gs} + C_{\rm gd})$  is the intrinsic transit frequency. To achieve high FOMs, the GFETs are designed taking into account the following considerations and conditions.

• The intrinsic  $f_{\rm T}$  and  $f_{\rm max}$  can be expressed via gate length as [75]:

$$f_{T-int} = \frac{1}{2\pi\tau_{int}} = \frac{v_d}{2\pi L},$$

(3.3)

$$f_{max-int} \approx \frac{f_{T-int}}{\sqrt{R_i g_{ds}}},\tag{3.4}$$

where  $\tau_{\text{int}}$  is the intrinsic transit time, i.e. the time of drift of charge carriers between source and drain. It can be seen from eqs. (3.1) and (3.2), that for highest  $f_{\text{T}}$  and  $f_{\text{max}}$  the gate length should be as short as possible. On the other hand, at relatively short gate length, the contact resistance associated with ungated regions starts to limit the high-frequency performance. In the current design/technology optimal L is approx. 0.5  $\mu$ m.

• Analysis indicates that, relatively large gate width and two gate fingers should be used to minimise the effects of the pad capacitances. It follows from a simplified expression for the time delay in the GFET as: [75]

$$\tau = \frac{1}{2\pi f_T} = \tau_{int} + \tau_{pad},\tag{3.5}$$

and

$$\tau_{pad} = \frac{C_{PG}}{g_m \cdot W}$$

where  $\tau_{\rm pad}$  is the delay associated with discharging of the gate pad capacitance. As it can be seen that the effect of  $\tau_{\rm pad}$  can be reduced by increasing the gate width. Current optimal design / technology utilises the two gate fingers with total W=30  $\mu$ m as shown in Fig. 3.1 (b).

• Consideration of eqs. (3.1) and (3.2) indicates that the ungated regions should be as short as possible to minimise the effect of total contact resistance as shown in zoom Fig. 3.1 (b). With current technology the ungated region length  $L_{\rm acc}=100$  nm, which is the lower limit defined by the e-beam lithography in this fabrication process flow. To get rid of the access area and related resistance, in the future generation of GFETs the self-aligned gate technology can be pursued.

• The top-gate configuration is used with the aim to minimise the parasitic

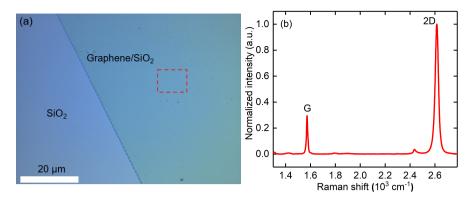

Figure 3.2: (a) Optical micrograph of the monolayer graphene transferred on  $Si/SiO_2$ . (b) The Raman spectrum taken at marked dashed box in (a).

gate-source and gate-drain capacitances.

• In the planar gate technology, rather thick gate electrode of 0.3  $\mu$ m Ti/Au is used to minimise the limiting effect of the  $R_{\rm G}$  on extrinsic  $f_{\rm max}$  as follows from eq. (3.2).

#### 3.1.2 CVD graphene selected for high-frequency GFETs

The GFETs with state-of-the-art high-frequency performance demonstrated so far utilise graphene fabricated by using three basic technologies: i) mechanical exfoliation, ii) epitaxial growth on SiC substrates and iii) chemical vapour deposition (CVD) [24,27,30,34,48,76]. The mechanical exfoliation from graphite inherently provides the highest quality graphene, because of the fewer defects, less impurity residuals and no grain boundaries. The exfoliated graphene demonstrates room temperature mobility over  $1 \cdot 10^5 \text{ cm}^2/\text{Vs}$  and saturation velocity up to  $6 \cdot 10^7$  cm/s [13, 15, 69]. However, the exfoliated graphene flakes are limited in size of typically few tens  $\mu m^2$ , and the technology is not compatible with the standard high-volume, large-scale CMOS processes. The epitaxial graphene can be obtained on the large area SiC substrates and with rather high quality [77, 78]. However, the drawback of this technique is the limited possibility of integration on the common grade semiconductor substrates. The CVD graphene can be grown on large areas and transferred onto arbitrary substrates. From this point of view, the CVD graphene is the technology of choice for the development of high performance high-frequency electronics based on GFETs. Recent advances in the CVD technology allowed for fabrication of graphene with mobility comparable to that of the exfoliated graphene encapsulated by hBN [14]. The CVD graphene is typically grown on a Cu foil, acting as a catalyst, using precursors gas flows. In the next step, graphene is transferred onto a substrate for subsequent device processing [79]. The GFETs and devices developed in this work were fabricated using CVD graphene with low-field mobility up to  $2500 \text{ cm}^2/\text{Vs}$ . The CVD graphene used in Papers [A] to [C] were grown and transferred onto  $SiO_2/Si$  substrates by AMO and Aachen University. Graphene used in Papers [D] to [G] is supplied by Graphenea and transferred using the 'easy transfer' method developed by

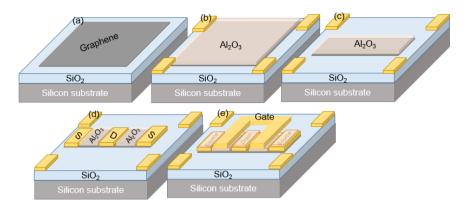

Figure 3.3: Schematic of the fabrication steps of two fingers top-gate GFET.

the company. The monolayer graphene was used due to its superior electron transport properties, better than that of the bilayer or multilayers graphene. Fig. 3.2(a) shows the optical micrograph of a CVD graphene transferred onto a SiO<sub>2</sub>/Si substrate. Fig. 3.2(b) shows the Raman spectrum taken from the region marked by the dashed line in Fig. 3.2(a).

### 3.1.3 Fabrication development

The fabrication process, developed for GFETs reported in Papers [A]-[C], [E] and [G], starts with transfer of the graphene onto a high-resistive Si substrate covered by 1  $\mu$ m thick SiO<sub>2</sub> layer grown by wet oxidation, as shown in Fig. 3.3(a). Relatively thicker SiO<sub>2</sub> was used with the aim to reduce the parasitic pad capacitances in the GFETs. A modified fabrication process was adopted for the GFET fabrication with an aim to preserve the graphene from contamination during fabrication. As a first step, the graphene sheet was covered with a dielectric layer as shown in Fig. 3.3(b), in Paper [A] to [G] it was Al<sub>2</sub>O<sub>3</sub> and in Paper [E] it was Ti/TiO<sub>2</sub>. This modification, in comparison with previously used process, serves two important purposes:

• It provides a cleaner metal-graphene interface under the contact electrode.

• It provides a cleaner interface between the top-gate dielectric and graphene channel.

In contrast, the previously used GFET fabrication process started with the formation of source and drain contacts and thus does not protect the graphene channel from contamination by residues of e-beam resists, adsorbent molecules and other processing chemicals [63, 72, 80]. The next step of the modified fabrication process was defining the mesa structure, as shown in Fig. 3.3(c). Ohmic contacts were formed by patterning the contact area using e-beam lithography, followed by etching the protective oxide layer by buffer oxide etchant (BOE) and finally depositing Ti/Pd/Au (1 nm/15 nm/250 nm) metal layers, see Fig. 3.3(d). It has been found via Raman spectra analysis that etching the oxide layer with BOE allows for the effective removal of polymer residues from the graphene surface. More details are given in the next sections. The next processing step was the deposition of a second layer of Al<sub>2</sub>O<sub>3</sub> gate

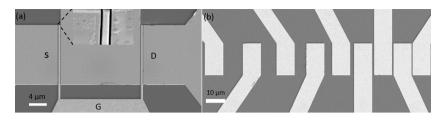

Figure 3.4: SEM micrographs of (a) two finger top-gate GFET (b) TLM test structure.

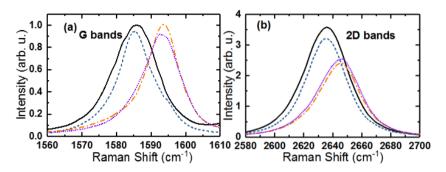

Figure 3.5: Raman spectra of the G bands (a) and 2D bands (b) of graphene as transferred (solid line) and after patterning with  $Al_2O_3$  using MMA-EL6 (dashed line), without  $Al_2O_3$  using PMMA (dashed dotted line), and without  $Al_2O_3$  using MMA-EL6 (dotted line).

dielectric using an atomic layer deposition technique, where the first few Al layers were deposited by e-beam evaporation and then thermally oxidized served as a seed layer. Next, gate fingers were patterned, and a metal stack of Ti/Au (10 nm/270 nm) was deposited, Fig. 3.3(e). The final processing step was the formation of contact pads for microprobes. All processing steps were carried out using e-beam lithography and e-beam evaporation. Typical SEM micrographs of top-gated double gate finger GFET and transfer length method (TLM) test structures are shown in Fig. 3.4.

#### Control removal of polymer residue

Raman spectroscopy was used for monitoring the graphene quality in response to development/modification of fabrication technology. In particular, analysis of the Raman spectra in Fig. 3.5 allows for evaluation of the doping effect caused by resist residues and verifying the effective removal of polymer residues in the modified fabrication technique. To verify the effective removal of e-beam resist residues in the modified fabrication method, the following test samples were prepared on Si/SiO<sub>2</sub> substrates and analysed using Raman spectroscopy: i) graphene with  $Al_2O_3$  layer after developing the MMA-EL6 e-beam resist followed by patterning the  $Al_2O_3$  layer, which represents the modified technology; ii) graphene without  $Al_2O_3$  layer after developing by MMA-EL6 and PMMA e-beam resists, which represents the previously used technology [24, 25]; iii) as-transferred graphene used as a reference.

As can be seen in Fig. 3.5, the positions and intensities of the G and 2D peaks corresponding to patterning with  $Al_2O_3$  using MMA-EL6 match

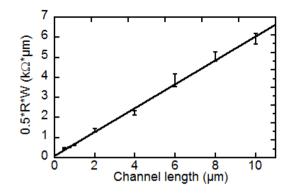

Figure 3.6: The  $0.5 \times R \times W$  of a TLM tests structure versus channel length.

closely to those of the as-transferred graphene. The positions of the peaks corresponding to patterning without Al<sub>2</sub>O<sub>3</sub>, using both MMA-EL6 and PMMA are upshifted, and the intensities of the 2D peaks are reduced. It was shown that the positions of the G and 2D peaks are defined by concentration of charge carriers and strain [81,82]. The 2D to G peak intensity ratio, I(2D)/I(G), is a strong function of the charge carrier concentration and does not depend on the strain [81–83]. The downshifts of the G and 2D bands positions, reported in [84] for PMMA-covered graphene, are not accompanied by remarkable changes in the I(2D)/I(G) ratio and, hence, are explained by the tensile strain produced by PMMA. The upshifts and decrease in the I(2D)/I(G) ratio caused by removing polymer residues via post-annealing, reported in [85, 86], are explained by formation of charged defects resulting in hole doping. Our analysis indicates that the upshifts and the I(2D)/I(G) reduction observed in our experiments corresponding to patterning without Al<sub>2</sub>O<sub>3</sub>, using both MMA-EL6 and PMMA (see Fig. 3.5) can only be explained by hole doping [81], apparently caused by residues of polymers. The matching of positions and intensities of the G and 2D peaks corresponding to patterning with Al<sub>2</sub>O<sub>3</sub> using MMA-EL6 confirms that, in the case of the modified technique, the polymer residues are effectively removed.

#### 3.1.4 Low resistive graphene-metal junctions

Realisation of low resistive metal-graphene junctions is a challenging task for researchers working with graphene device technology. There are basically two methods of contact formation in GFET technology: (i) the conventional top or planar type contacts and (ii) the side or edge type contacts [49]. In this study, planar contacts with very low specific width contact resistivity  $\rho_{\rm C}$  down to 90  $\Omega \times \mu$ m have been demonstrated. For contact resistance measurements, multiterminals technique of the TLM was implemented [87,88]. The TLM is the most commonly applied method to extract the contact resistance, in particular, because it takes into account the edge effect and current crowding [89,90]. The parameter characterising the metal-graphene contact is the specific width contact resistivity  $\rho_{\rm C} = R_{\rm C} \times W$  [91]. A TLM test structure is shown in Fig. 3.2(b). In TLM methods, a chain of identical contacts are fabricated with different channel lengths between them. The total resistance R between

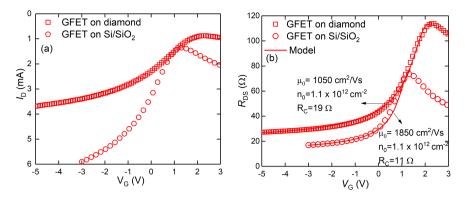

Figure 3.7: Typical transfer characteristics (a) and corresponding dependences of the drain resistance  $(R_{\rm DS})$  on the gate voltage  $(V_{\rm G})$  (b) of the GFETs on diamond and Si/SiO<sub>2</sub> substrates. The solid lines represent fitting by the drain resistance model using eqs. (3.8).

the contacts is measured by using DC IV characterisation. The R measured between the two contacts is a combination of contact resistance  $R_{\rm C}$ , and the graphene sheet resistance  $R_{\rm sh}$  and can be expressed as:

$$R = 2R_C + \frac{R_{sh}L}{W}.$$

(3.6)

Where L is the graphene channel length and W is the channel width. The total measured R multiplied by 0.5W for different channel spacings are then plotted versus L as shown in Fig. 3.6. The slope gives the sheet resistance of the graphene while  $R_{\rm C}$  is obtained from y-intercept at L = 0. The measured  $\rho_{\rm C}$  in this way is 90  $\Omega \times \mu$ m, which is lower than the edge type contacts and is close to the theoretical limit of 88  $\Omega \times \mu$ m [92].

### 3.2 DC performance and models of GFETs

### 3.2.1 Transfer characteristics and drain resistance model

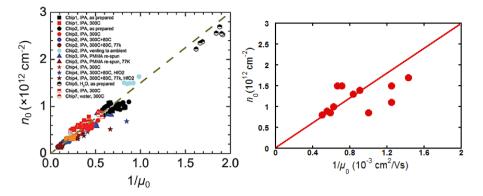

Typical transfer characteristics of GFETs on diamond and  $Si/SiO_2$  substrates and corresponding dependences of the drain resistance on gate voltage are shown in Fig. 3.7. The dependences reveal characteristic minimum conductivity at Dirac voltage manifesting the graphene's ambipolarity. The minimum conductivity is defined mainly by the impurities in the system as in [63,73]:

$$\sigma_{min} = \mu_0 n_0 q \tag{3.7}$$

where  $\mu_0$  is the low-field mobility and  $n_0$  is the residual carrier concentration defined by the spatially inhomogeneous screened Coulomb potential by neglecting the concentration of the thermally generated carriers [73]. The  $n_0$  can be found using the random phase approximation formalism [73]. Alternatively,  $n_0$ and  $\mu_0$  can be evaluated via fitting the drain resistance model [93]:

$$R_{DS} = R_C + \frac{L}{qW\mu_0 n} \tag{3.8}$$

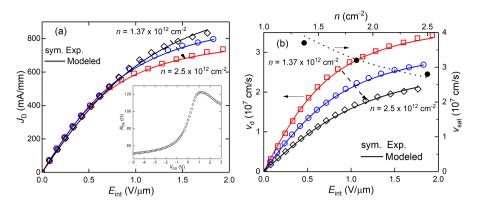

Figure 3.8: Saturation of the drift velocity (a) Drain current density  $(J_D)$  vs. intrinsic drain field  $(E_{int})$  of the GFET on diamond substrate with 0.75  $\mu$ m gate length at different gate voltages of  $V_G=1$ , 0.5, 0 V increasing in the arrow's direction. Shown are also corresponding total concentrations of the charge carriers. Inset shows the drain resistance dependence on the gate voltage. The lines represent the drain current density modelled using eqs. (2.8), (3.9) and (3.10). (b) The effective drift velocity of the charge carriers  $(v_d)$  vs. intrinsic drain field calculated from dependences shown in (a) using eqs. (3.9), (3.10). The solid lines represent the drift velocity calculated using the drift velocity model, eq. (2.8). The dashed line represents the saturation velocity dependence on concentration calculated using the saturation velocity model, eq. (2.10).

where  $R_{\rm C}$  is the total source and drain series resistance including a graphenemetal junction resistance and resistance associated with ungated regions of the channel, n is the total carrier concentration as defined in eq. (2.7), L is the gate length, W is the gate width and n is the total carrier concentrations,  $C_{\rm ox}$ is the gate capacitance per unit area. Fig. 3.7 shows the  $R_{\rm DS}$  vs.  $V_{\rm G}$  of the GFETs together with fitting curves of the model and corresponding values of the  $\mu_0$ ,  $n_0$  and  $R_{\rm C}$  found as fitting parameters.

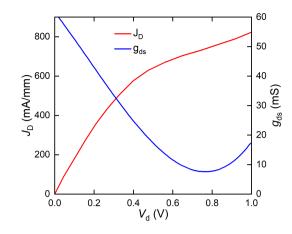

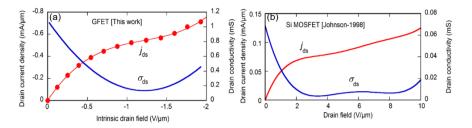

### 3.2.2 Output characteristics, drain current and drift velocity models

Fig. 3.8(a) shows the drain current densisty  $(J_{\rm D})$  versus intrinsic drain field  $(E_{\rm int})$  of a GFET on diamond substrate with 0.75  $\mu$ m gate length at different gate voltages of  $V_{\rm G}$ =1, 0.5, 0 V increasing in the arrow's direction. Shown are also corresponding total concentrations of the charge carriers. The drain current density and intrinsic drain field are calculated as  $J_{\rm D}=I_{\rm D}/{\rm W}$  and  $E_{\rm int} = (V_{\rm D} - I_{\rm D}R_{\rm C})/L$ . The drain current density can be expressed as:

$$J_D = q n_{eff} \mu_{eff} E_{int} = q n_{eff} v_d \tag{3.9}$$

where  $v_{\rm d}$  is the effective drift velocity of the charge carriers and  $n_{\rm eff}$  is the effective carrier concentration by taking into account of the effects of depletion at the drain side and thermal generation of carriers due to self-heating at relatively high drain fields. The  $n_{\rm eff}$  can be expressed as [15]:

$$n_{eff} = \sqrt{n_0^2 + (C_{ox}/q(V_G - V_{Dir} + V_d/2))^2}$$

(3.10)

where  $V_{\rm G}$ ,  $V_{\rm Dir}$  and  $V_{\rm d}$  are intrinsic gate, Dirac and drain voltages, respectively. The  $n_0$  is the residual carrier concentration at elevated temperature caused by self-heating and calculated as:  $n_0 = \sqrt{n_i^2 + n_{th}^2}$  [56]. The  $n_i$  can be found using the drain resistance model and  $n_{th}$  calculated using the thermal resistance model [56]. The effective drift velocity  $v_d$  can be obtained using eq. (2.8). The  $\mu_{eff}$  can be found from the output characteristics as  $\mu_{eff} = g_{ds}L/neW$  [90]. The lines in Fig. 3.8(a) represent the drain current density modelled using eqs. (2.8), (3.9) and (3.10). Fig. 3.8(b) shows the drift velocity calculated using the measured current density shown in Fig. 3.8(a) and eqs. (3.9) and (3.10). The solid lines represent the drift velocity calculated using the drift velocity model given by eq. (2.8) with  $v_{sat}$  as a fitting parameter. The  $v_{sat}$  is shown in Fig. 3.8(b) versus carrier concentration for the corresponding three different gate voltages. The dashed line represents the saturation velocity dependence on concentration, calculated using eq. (2.10) [15,56]. As it can be seen, there are good agreements between the experimental measurements and the simulations in all dependences in Fig. 3.8(a) and Fig. 3.8(b).

### 3.3 Mobility degradation

Mobility modelling including appropriate low-field mobility and saturation velocity models are of utmost importance for characterising GFETs and for predicting their performance in circuit applications. Several GFET IV-models pay attention to velocity saturation effects at high electric fields, but low-field mobility degradation at high carrier concentrations is neglected in most models despite being observed already in early work. In Paper [F] a GFET low-field mobility model was proposed that includes mobility degradation due to an increasing number of charge carriers induced by the gate voltage. By using this mobility model, one can show that series resistance values extracted by using widely accepted resistance models overestimate the real series resistance because of the effects of mobility degradation. An effort were made to separate the two effects by examining the gate length dependence of the resistance values extracted from measurements on a set of GFETs of different gate length. A detail mathematical expression and discussion is given in Paper [F].

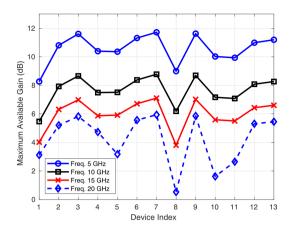

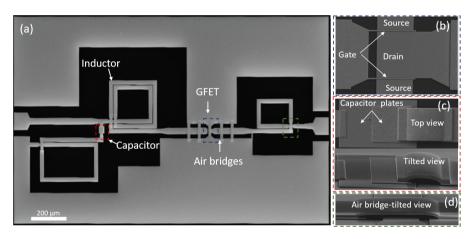

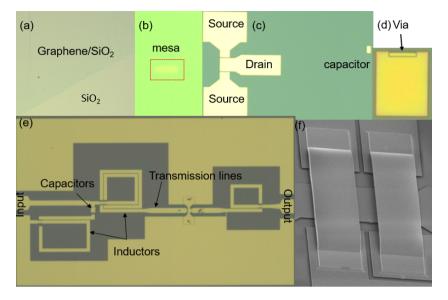

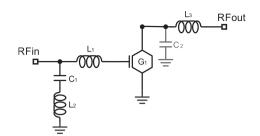

## 3.4 High-frequency performance and models of GFETs