### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Dual Data Rate Network-on-Chip Architectures

AHSEN EJAZ

Division of Computer Engineering

Department of Computer Science & Engineering

Chalmers University of Technology

Göteborg, Sweden, 2021

### **Dual Data Rate Network-on-Chip Architectures**

AHSEN EJAZ

**Advisor:** Ioannis Sourdis, Professor at Chalmers University of Technology **Co-Advisor:** Vassilios Papaefstathiou, Researcher at FORTH-ICS, Greece

Examiner: Per Stenström, Professor at Chalmers University of Technology

#### **Thesis Opponent:**

Tushar Krishna, Assistant Professor at Georgia Institute of Technology, USA

#### **Grading Committee:**

Giorgos Dimitrakopoulos, Associate Professor at Democritus Univ. of Thrace, Greece Boris Grot, Associate Professor at University of Edinburgh, UK Jens Sparsø, Professor at Technical University of Denmark, Denmark Lars Svensson, Senior Lecturer at Chalmers Univ. of Technology (deputy member)

Copyright ©2021 Ahsen Ejaz except where otherwise stated. All rights reserved.

ISBN: 978-91-7905-497-7

Doktorsavhandlingar vid Chalmers tekniska högskola.

Series number: 4964 ISSN: 0346-718X

Technical report number: 197D

Department of Computer Science & Engineering Division of Computer Engineering Chalmers University of Technology Göteborg, Sweden

This thesis has been prepared using LATEX. Printed by Chalmers Reproservice, Göteborg, Sweden 2021.

### **Abstract**

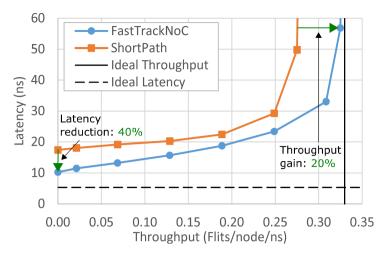

Networks-on-Chip (NoCs) are becoming increasing important for the performance of modern multi-core systems-on-chip. The performance of current NoCs is limited, among others, by two factors: their limited clock frequency and long router pipeline. The clock frequency of a network defines the limits of its saturation throughput. However, for high throughput routers, clock is constrained by the control logic (for virtual channel and switch allocation) whereas the datapath (crossbar switch and links) possesses significant slack. This slack in the datapath wastes network throughput potential. Secondly, routers require flits to go through a large number of pipeline stages increasing packet latency at low traffic loads. These stages include router resource allocation, switch traversal (ST) and link traversal (LT). The allocation stages are used to manage contention among flits attempting to simultaneously access switch and links, and the ST stage is needed to change the routing dimension. In some cases, these stages are not needed and then requiring flits to go through them increases packet latency. The aim of this thesis is to improve NoC performance, in terms of network throughput, by removing the slack in the router datapath, and in terms of average packet latency, by enabling incoming flits to bypass, when possible, allocation and ST stages. More precisely, this thesis introduces Dual Data-Rate (DDR) NoC architectures which exploit the slack present in the NoC datapath to operate it at DDR. This requires a clock with period twice the datapath delay and removes the control logic from the critical path. DDR datapaths enable throughput higher than existing single data-rate (SDR) networks where the clock period is defined by the control logic. Additionally, this thesis supplements DDR NoC architectures with varying levels of pipeline stage bypassing capabilities to reduce low-load packet latency. In order to avoid complex logic required for bypassing from all inputs to all outputs, this thesis implements and evaluates a simplified bypassing approach. DDR NoC routers support bypassing of the allocation stage for flits propagating an in-network straight hop (i.e. East to West, North to South and vice versa) and when entering or exiting the network. Disabling bypassing during XY-turns limits its benefits, but, for most routing algorithms under low traffic loads, flits encounter at most one XY-turn on their way to the destination. Bypassing allocation stage enables incoming flits to directly initiate ST, when required conditions are met, and propagate at one cycle per hop. Furthermore, DDR NoC routers allow flits to bypass the ST stage when propagating a straight hop from the head of a specific input VC. Restricting ST bypassing from a specific VC further simplifies check logic to have clock period defined by datapath delays. Bypassing ST requires dedicated bypass paths from non-local input ports to opposite output ports. It enables flits to propagate half a cycle per hop. This thesis shows that compared to current state-of-the-art SDR NoCs, operating router's datapath at DDR improves throughput by up to 20%. Adding to a DDR NoC an allocation bypassing mechanism for straight hops reduces its packet latency by up to 45%, while maintaining the DDR throughput advantage. Enhancing allocation bypassing to include flits entering and exiting the network further reduces latency by another 24%. Finally, adding ST bypassing further reduces latency by another 32%. Overall, DDR NoCs offer up to 40% lower latency and about 20% higher throughput compared to the SDR networks.

#### **Keywords**

Network-on-Chip, On-Chip Interconnect, System-on-Chip, Dual Data-Rate, Multiprocessor System-on-Chip, Chip Multiprocessors

# Acknowledgment

First of all, I would like to express my gratitude to my PhD supervisor Ioannis Sourdis for giving me the opportunity to pursue a PhD degree under his supervision. Ioannis has been very patient and supportive during my research and has kept me motivated since I started on this path to a PhD degree.

I am also grateful to my co-supervisor, Vassilis Papaefstathiou, for his valuable comments and feedback based on his deep insight of the field, during our meetings.

I would also like to thank my PhD research examiner, Per Stenström, and PhD follow-up committee members Jan Jonsson, Agneta Nilsson, Wolfgang Ahrendt and Nir Piterman, for their constructive feedback and support over the years.

I am also very grateful to Lars Svensson for his useful critiques of my research and for his support with setting up the physical design tools I needed.

Place-and-Route of the networks I designed had been a daunting and time consuming task, and it would have taken much longer had it not been for the useful impromptu discussions with Kevin Cushon, Christoffer Fougstedt, Erik Ryman and Victor Åberg. Thanks guys.

I would also like to thank the administrative staff of the department, Eva Axelsson, Monica Månhammar, Marianne Pleen-Schreiber, Nadja Johansson, Lars Norén, Michael Morin and Rune Ljungbjörn for their help and support.

I am also thankful to my colleagues in the Department of Computer Science and Engineering, Muhammad Waqar Azhar, Evangelos Vasilakis, Prajith Ramakrishnan Geethakumari, Albin Eldstal-Damlin, Stefano Ribes, Mehrzad Nejat, Petros Voudouris, Bhavishya Goel, Madhavan Manivannan and Pedro Petersen Moura Trancoso for our various discussions and for creating a positive work environment.

I would also like to thank my office mates over the long years, Alirad Malek, Stavros Tzilis and Piyumal Ranawaka for keeping me motivated and entertained.

This work has been partly funded by EUROSERVER project (grant agreement 610456), EuroLab-4-HPC project (grant agreement 371610) and Horizon 2020 Programme ECOSCALE project (grant agreement 671632).

Finally, none of this would have been possible without the unfaltering support, encouragement and prayers of my parents, my siblings and my wife. I am really grateful to have them by my side.

Ahsen Ejaz Göteborg, May 2021

# **List of Publications**

This thesis is based on the following publications:

- 1. **Ahsen Ejaz**, Vassilios Papaefstathiou and Ioannis Sourdis, "DDRNoC: Dual Data-Rate Network-on-Chip", *ACM Transactions on Architecture and Code Optimization (TACO)*, vol. 15, no. 2, June 2018.

- 2. **Ahsen Ejaz**, Vassilios Papaefstathiou and Ioannis Sourdis, "FreewayNoC: a DDR NoC with Pipeline Bypassing", *IEEE/ACM International Symposium on Networks-on-Chip*, 2018.

- 3. **Ahsen Ejaz**, Vassilios Papaefstathiou and Ioannis Sourdis, "HighwayNoC: Approaching Ideal NoC Performance With Dual Data Rate Routers", *IEEE/ACM Transactions on Networking*, vol. 29, no. 1, pp. 318-331, 2021.

- 4. **Ahsen Ejaz** and Ioannis Sourdis, "FastTrackNoC: A NoC with FastTrack Router Datapaths", *Under submission*, 2021.

# **Contents**

| Al | ostrac  | et          |           |                                                 | iii     |

|----|---------|-------------|-----------|-------------------------------------------------|---------|

| A  | cknow   | ledgem      | ent       |                                                 | v       |

| Li | st of l | Publicat    | tions     |                                                 | vii     |

| 1  | Intr    | oductio     | n         |                                                 | 1       |

|    | 1.1     | Proble      | m Stateme | ent                                             | 2       |

|    |         | 1.1.1       |           | Control Logic Limits NoC Throughput             | 2       |

|    |         | 1.1.2       |           | outer Pipeline Increases Packet Latency         | 3       |

|    | 1.2     | Thesis      | -         | es                                              | 3       |

|    |         | 1.2.1       |           | ng NoC Throughput                               | 3       |

|    |         |             | 1.2.1.1   | Related Work                                    | 3       |

|    |         |             | 1.2.1.2   | Objective 1: Increase Network Throughput with   |         |

|    |         |             |           | DDR Datapath                                    | 4       |

|    |         | 1.2.2       | Reducin   | g NoC Packet Latency                            | 5       |

|    |         |             | 1.2.2.1   | Related Work                                    | 6       |

|    |         |             | 1.2.2.2   | Objective 2: Reduce Packet Latency with Control |         |

|    |         |             |           | Forwarding in a DDR Router                      | 6       |

|    |         |             | 1.2.2.3   | Objective 3: Reduce Packet Latency with Alloca- |         |

|    |         |             |           | tion Bypassing in a DDR Router                  | 6       |

|    |         |             | 1.2.2.4   | Objective 4: Reduce Packet Latency with ST By-  |         |

|    |         |             |           | passing                                         | 8       |

|    | 1.3     | Thesis      | Outline . |                                                 | 8       |

| •  | D.1.    | 4 - 3 337 - | 1_        |                                                 | 9       |

| 2  |         | ted Wo      |           | Thursday                                        | 9       |

|    | 2.1 2.2 |             | -         | Throughput                                      | 9<br>11 |

|    | 2.2     |             | _         | •                                               | 14      |

|    | 2.3     | Sullilli    | ary       |                                                 | 14      |

| 3  | The     | DDRN        | oC Archit | tecture                                         | 15      |

|    | 3.1     | Router      | Datapath  |                                                 | 15      |

|    | 3.2     | Timing      | g         |                                                 | 17      |

|    | 3.3     |             |           | ncy Analysis                                    | 19      |

|    | 3.4     |             |           | ol                                              | 20      |

|    |         | 3.4.1       | Virtual C | Channel Allocation                              | 20      |

|    |         | 3.4.2       | Switch A  | Allocation                                      | 20      |

|    |         | 3.4.3       | Flow Co   | entrol and Minimum Buffer Size                  | 21      |

X CONTENTS

|   | 3.5        | Discussion                                    | 2 |

|---|------------|-----------------------------------------------|---|

|   | 3.6        | Summary                                       | 2 |

| 4 | The        | FreewayNoC Architecture 23                    | 3 |

|   | 4.1        | Router Datapath                               | 1 |

|   |            | 4.1.1 DDR Flit Datapath                       | 1 |

|   |            | 4.1.2 Datapath of Forwarded Control signals   | 5 |

|   | 4.2        | Timing Example                                | 5 |

|   | 4.3        | Zero-Load Latency Analysis                    | 5 |

|   | 4.4        | Router Control                                | 7 |

|   |            | 4.4.1 Combined VC and Switch Allocation       | 7 |

|   |            | 4.4.2 Allocation Bypassing                    | ) |

|   |            | 4.4.3 Next Route Computation                  | ) |

|   |            | 4.4.4 Flow Control and Minimum Buffer Size    | ) |

|   |            | 4.4.5 Control Path Analysis                   | 1 |

|   | 4.5        | Summary                                       | 1 |

| _ | The        | HighwayNoC Architecture 33                    | , |

| 5 | 5.1        | <i>v</i>                                      |   |

|   | 3.1        | - m-F m mF m                                  | - |

|   |            | 5.1.1 DDR Flit Datapath                       |   |

|   | <i>5</i> 2 |                                               |   |

|   | 5.2        | e                                             |   |

|   | 5.3        | Zero-Load Latency Analysis                    |   |

|   | 5.4        | Router Control                                |   |

|   |            | 5.4.1 Combined VC and Switch Allocation       |   |

|   |            | 5.4.2 Allocation Bypassing                    |   |

|   |            | 5.4.3 Next Route Computation                  |   |

|   |            | 5.4.4 Flow Control and Minimum Buffer Size    |   |

|   |            | 5.4.5 Control Path Analysis                   |   |

|   | 5.5        | Summary                                       | ) |

| 6 | The        | FastTrackNoC Architecture 47                  | 7 |

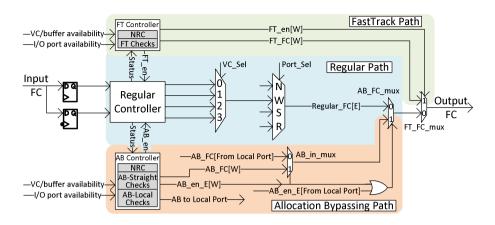

|   | 6.1        | Router Datapath                               | 3 |

|   |            | 6.1.1 DDR Flit Datapath                       | ) |

|   |            | 6.1.2 Datapath of Forwarded Control Signals   | ) |

|   | 6.2        | Router Control                                | 2 |

|   |            | 6.2.1 Combined VC and Switch Allocation       | 2 |

|   |            | 6.2.2 Allocation Bypassing Controller         | 3 |

|   |            | 6.2.3 FastTrack Controller                    | 3 |

|   |            | 6.2.4 Next Route Computation                  | 5 |

|   |            | 6.2.5 Flow Control and Minimum Buffer Size 55 | 5 |

|   | 6.3        | Zero-Load Latency Analysis                    |   |

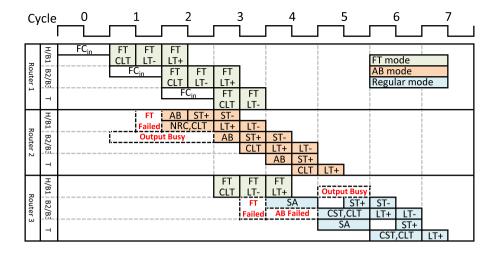

|   | 6.4        | Timing Example                                |   |

|   | 6.5        | Summary                                       |   |

|   |            |                                               |   |

CONTENTS Xi

| 7  | Eval   | luation |                                                        | 61 |

|----|--------|---------|--------------------------------------------------------|----|

|    | 7.1    | Experi  | imental Setup                                          | 61 |

|    | 7.2    |         | mentation Results                                      | 63 |

|    | 7.3    | Perfor  | mance Evaluation                                       | 65 |

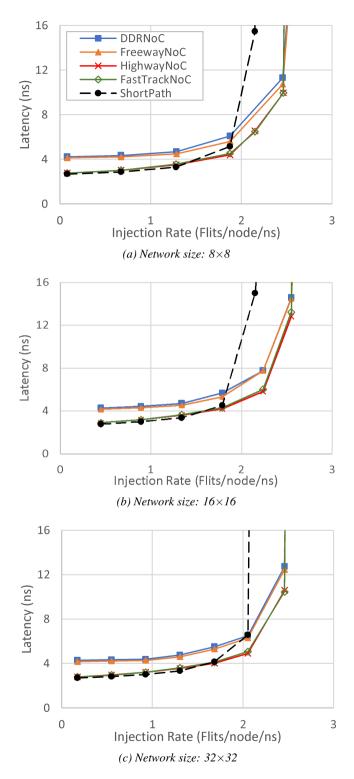

|    |        | 7.3.1   | Performance with Synthetic Traffic                     |    |

|    |        | 7.3.2   | Performance Comparison against Networks with Longer    |    |

|    |        |         | Links                                                  | 66 |

|    |        | 7.3.3   | Performance Comparison against Networks with DDR       |    |

|    |        |         | Links                                                  | 74 |

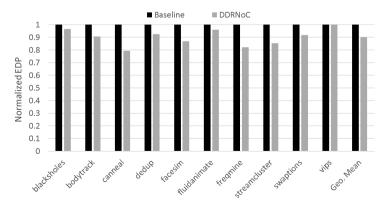

|    |        | 7.3.4   | Energy Efficiency                                      | 74 |

|    |        | 7.3.5   | Trading DDRNoC Performance Advantage for Energy        |    |

|    |        |         | Efficiency                                             | 77 |

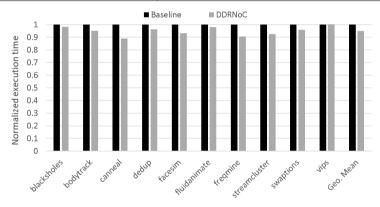

|    |        | 7.3.6   | Evaluation with Application Driven Traffic             | 79 |

|    |        | 7.3.7   | Measuring the Impact of DDRNoC Throughput Gain on Sys- |    |

|    |        |         | tem Performance                                        | 80 |

|    | 7.4    | Summ    | ary                                                    | 82 |

| 8  | Con    | clusion | s                                                      | 83 |

|    | 8.1    | Summ    | ary                                                    | 83 |

|    | 8.2    | Contri  | butions                                                | 84 |

|    | 8.3    | Future  | Work                                                   | 86 |

| Bi | bliogi | raphy   |                                                        | 89 |

XII CONTENTS

# Chapter 1

## Introduction

Chip Multiprocessors (CMP) are one of the most promising solutions for supporting the continuous need for single chip performance improvement. Shrinking transistor geometries still allow more cores to be integrated on a die [1–3]. The increasing number of cores as well as the increasingly complex workloads place stringent requirements over the underlying communication fabric. On one hand, applications that exhibit small transfers at low loads are often more sensitive to network latency [4]. On the other hand, systems that run concurrent scale-out applications are more demanding, push the network close to its saturation point, and are more sensitive to network throughput [4,5]. Moreover, power constraints prevent chips from fully utilizing all these cores at their maximum performance potential [6]. The on-chip interconnection network is a critical component for power efficiency as well [7] since roughly a sixth of the available chip power budget, if not more, goes to its interconnects [8–14]. As a consequence, the design of high-performance and low-power networks-on-chip (NoCs) is essential for many-core scaling.

In the past decades, NoC designs have improved their performance substantially, both in terms of throughput and in terms of latency.

Network throughput has increased with the use of better topologies [15] and multiple sub-networks [16,17] as well as with improvements in allocation [18]. Higher throughput is also achieved by splitting switch traversal (ST) and link traversal (LT) into two pipeline stages. Currently, NoCs require complex control logic to implement various allocation schemes which allocate available network resources to propagating packets and flits. For high throughput networks, the delay of their control is longer than the datapath, which then leads to define the NoC clock period [18–21]. The datapath in such a case possesses some slack, which essentially wastes bandwidth. Compared to an ideal network which would operate at a clock rate defined only by the datapath delay, current 2D-mesh NoC architectures with virtual channel (VC) flow control still offer lower throughput. This is because an ideal network would deliver more packets per node as a consequence of improved datapath utilization achieved by removing the slack present in the datapath. Higher network throughput obtained from increased datapath utilization would also improve the performance of the entire system.

Furthermore, packet latency has previously been reduced with improvements in the network topology [22], the routing algorithm [23] and the router architecture [24, 25]. In theory, the latency for a single hop, i.e., crossing a tile, can be as short as the (register

2 CHAPTER 1. INTRODUCTION

to register) delay of a link that traverses the tile dimension. Some existing networks such as single-cycle multi-hop routers [26], routers with express links [22, 27], or routerless rings [28] offer low latency, but sacrifice substantially their throughput. Current high throughput NoC routers have reduced their minimum hop latency to the time spent for ST + LT [13, 29, 30]. This is achieved by a combination of techniques, such as precomputed routing [24], speculative switch allocation (SA) [25], lookahead control signalling [13, 29], and allocation bypassing [13, 30]. Then, considering that ST and LT are pipelined and their delays are split evenly, the minimum hop latency of current NoC routers [30] is roughly twice the above theoretical minimum, i.e.  $2 \times LT$ .

This introductory Chapter provides a brief overview of the work presented in this thesis. The remainder of this Chapter is organized as follows: Section 1.1 presents the main problem statement of this research. Section 1.2 discusses the key objectives of this thesis.

### 1.1 Problem Statement

A NoC router has two sets of components: router datapath and control logic. Router datapath is composed of input/output link wires, VC buffers, crossbar and output registers. It is used to either store flits in NoC routers due to contention or unavailability of required resources, or to move them forward through the network towards their destination. The control logic, on the other hand, is responsible for managing the flow of flits propagating through the network by allocating router datapath resources to them. It also resolves contention among flits competing to use shared router resources at the same time. It comprises next route computation (NRC) logic, VC allocators (VA) and switch allocators (SA). In order to increase network clock frequency, the control logic and the datapath of NoC routers are divided into smaller and faster pipeline stages. The delay of the control stages is longer than the datapath stages because of greater complexity of allocators. This leads to an imbalance in router pipeline which limits network's clock frequency and prevents it from achieving throughput close to an ideal network with a balanced router pipeline. Furthermore, a flit must go through many pipeline stages to traverse a router. Traversing pipeline stages when they are not needed delays packets and increases average packet latency unnecessarily. These two inefficiencies are further discussed below.

### 1.1.1 Router Control Logic Limits NoC Throughput

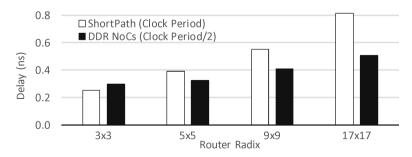

As shown in literature and confirmed by our experiments, the critical path of existing 2D-mesh routers with multiple VCs, is in its control logic [18, 19, 21, 24]. More specifically, the clock period of a typical 3-stage (NRC/VA/SA, switch traversal (ST), link traversal (LT)) router [24] is dictated by the VA/SA stage of the router pipeline. Even for one of the fastest state-of-the-art NoC routers with VC-flow control, ShortPath [30], a significant fraction (about 20%) of the clock period is reserved for router control. Consequently, the datapath possesses considerable slack and is used only for a fraction of the clock cycle to forward the flit and remains idle otherwise. This reduces network datapath utilization, wastes link bandwidth and hinders the NoC from achieving its maximum performance potential by limiting its saturation throughput and increasing packet latency.

1.2. THESIS OBJECTIVES 3

### 1.1.2 Deep Router Pipeline Increases Packet Latency

Conventional NoC routers have three pipeline stages: (i) VA/SA, (ii) ST and (ii) LT, but going through all these stages is not always necessary. For example, the VA/SA stage, which allocates switch resources to flits, is not needed in the absence of competing flits and can be bypassed. Similarly, ST stage is needed for changing the routing dimension but it could be bypassed when propagating in a single dimension. Many previous NoC architectures allow incoming flits to bypass the SA stage and save a clock cycle per hop [13,29,30]. These networks, however, do not allow flits to bypass the ST stage, which could further reduce packet latency.

## 1.2 Thesis Objectives

In this thesis, we target the slack in the datapath as well as long pipeline of NoC routers. VC based 2D-mesh NoC architectures are targeted aiming to increase NoC datapath utilization and to avoid delays caused by deep router pipeline. We aim at designing a NoC router architecture capable of achieving throughput defined solely by the network datapath delays and minimum hop latency close to the LT delay. The implications of such a network on throughput and latency are presented below along with a brief description of related works.

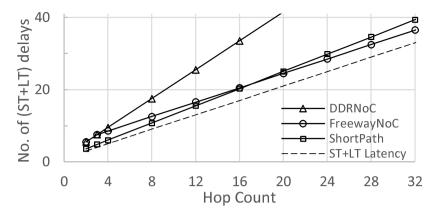

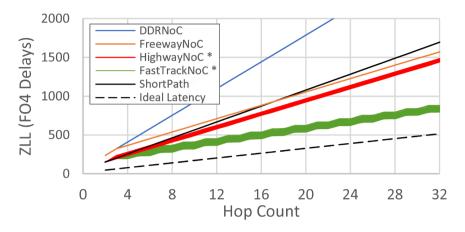

### 1.2.1 Improving NoC Throughput

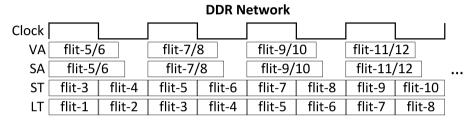

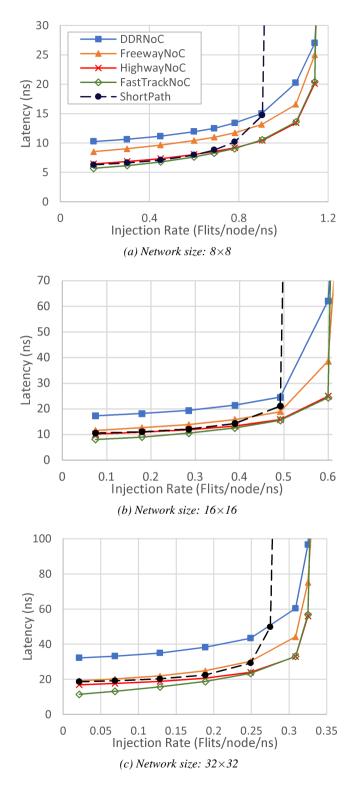

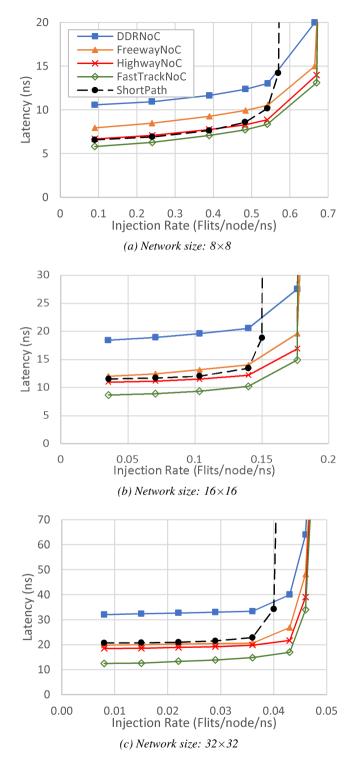

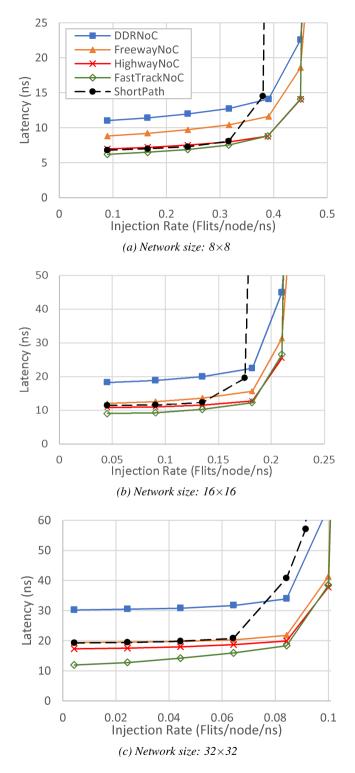

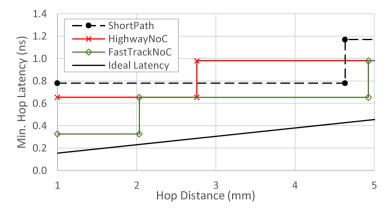

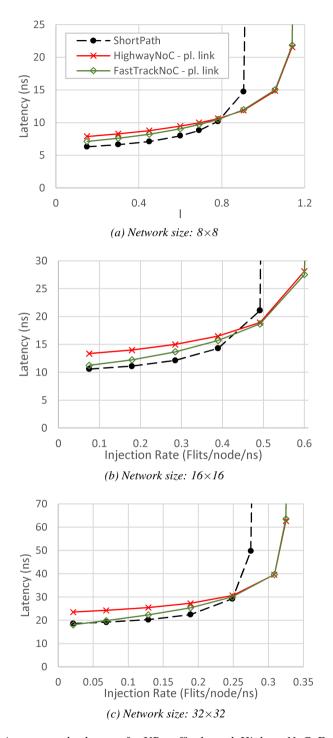

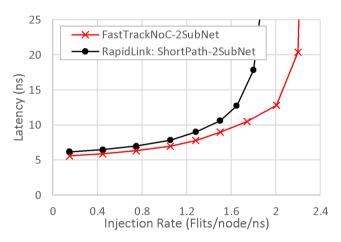

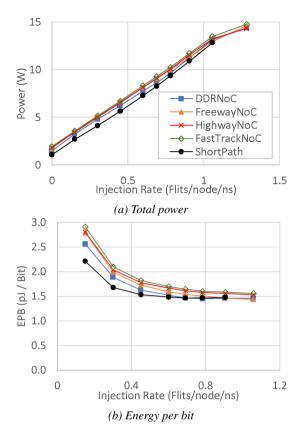

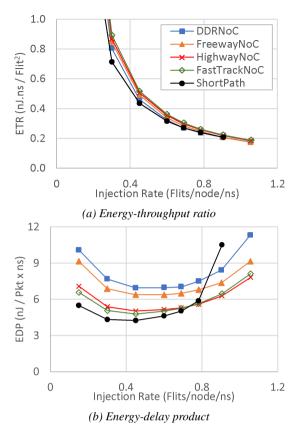

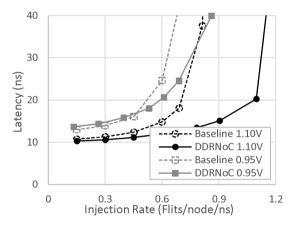

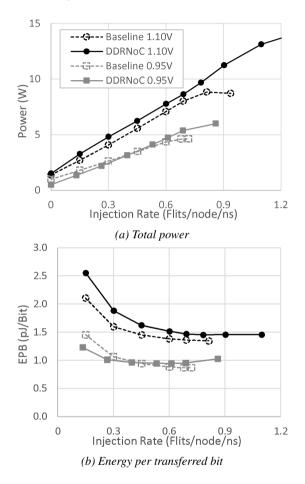

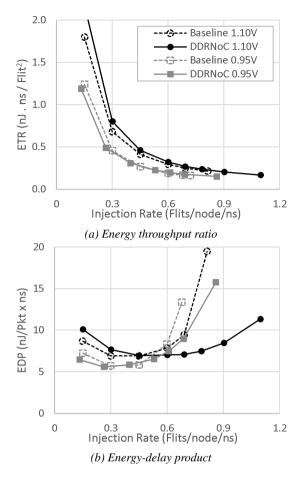

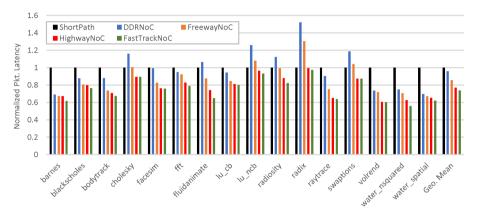

One of the factors limiting the throughput of high performance single data-rate (SDR) networks is the under-utilization of its datapath during a clock cycle. It is caused by an imbalance in the datapath and the control logic path delays of SDR NoC routers, as shown in Figure 1.1. This imbalance exists because the complex allocation schemes employed to control these routers are substantially slower than the datapath. Then the clock period of the resulting NoC router is longer than the datapath delay and leads to datapath under-utilization during the cycle. We analyze the throughput of one of the fastest state-of-the-art SDR NoC architectures, called the ShortPath network [30] and compare it to the throughput of an ideal (ShortPath) network with clock period defined purely by datapath delays. The results for 32×32 2D-mesh networks with uniform random traffic of 1 and 5 flit packets, presented in Figure 1.2, indicate about 20% throughput gap between the ShortPath network operated at its maximum clock frequency versus the clock frequency defined by its datapath delays. This is because clock period for ShortPath routers is shared by both its datapath and control logic making it about 20% longer than the datapath delays.

#### 1.2.1.1 Related Work

Existing NoC architectures attempt to either reduce or exploit the imbalance between the router datapath and control aiming to improve performance. Many architectural techniques try to simplify VA and SA to reduce allocation complexity and thereby the router critical path delay [13,30]. Others employ low level implementation techniques like time stealing (or retiming), currently supported by CAD tools, to balance the pipeline of a router and have a clock period equal to the average delay of all router stages [20]. Nevertheless, for all these techniques, the control logic either ends up with a delay larger than the datapath delay or it adds to the datapath delay causing a

4 CHAPTER 1. INTRODUCTION

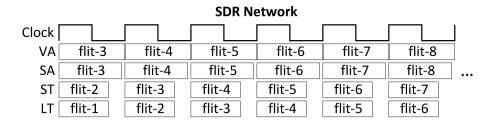

Figure 1.1: For a conventional SDR network, the clock period is completely (or partly) determined by the control logic. The DDR network extends the clock period to twice the datapath delay, implements control logic capable of allocating datapath resources to two flits per cycle per port and also enables the datapath (ST and LT) to propagate two flits per cycle. The clock period is now defined only by the datapath delays. This improves datapath utilization and enhances network throughput.

single clock cycle to be sequentially shared by a part of both the control logic and the datapath. Both these cases result in a router critical path which includes some control logic, require a clock with a period larger than the datapath delay and lead to NoC datapath under-utilization. The router architecture we present in this thesis minimizes the share of the control logic in the network clock period by using DDR datapaths.

In the past, NoC research community has proposed router architectures which employ DDR flit traversal but only in parts of a NoC. Such NoC routers either use double-pumped crossbars [9] or DDR links [17,31,32]. These designs employ DDR over a part of the router's datapath to improve either area, power or performance but they do not eliminate the slack in the router datapath, so they still allow its under-utilization. Contrary to these works, our approach increases network throughput by enabling DDR flit propagation over all parts of the router datapath to route flits at a rate determined by the datapath delays rather than by the control logic delays.

### 1.2.1.2 Objective 1: Increase Network Throughput with DDR Datapath

The first objective of this thesis is to improve NoC throughput by removing the slack present in the router's datapath and having its clock frequency defined by datapath delays. Figure 1.2 shows the targeted gap in the throughput of ShortPath [30], one of the fastest SDR NoCs, when operated at its maximum clock frequency versus the clock frequency defined solely by its datapath delays. In order to cover this throughput gap, this thesis proposes the DDRNoC architecture, presented in Chapter 3, which operates the router datapath at DDR allowing two flits to propagate in a single cycle as shown in Figure 1.1. Contrary to current SDR routers which have clock period defined by slow control logic, the clock period of DDRNoC is equal to twice the delay of the

1.2. THESIS OBJECTIVES 5

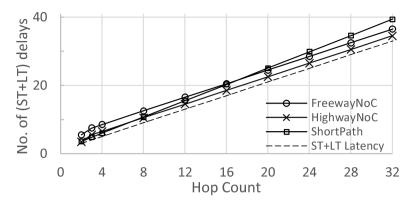

Figure 1.2: Throughput and latency of one of the fastest SDR networks, called the ShortPath network [30], is presented in comparison to the ideal network throughput and latency. Network size of  $32 \times 32$  is considered with uniform random traffic of 1 and 5 flit packets. Ideal throughput is the saturation throughput of the ShortPath network when operated at a clock frequency defined solely by the datapath (ST and LT) delays. Ideal latency is for a (pipelined) direct connection between the source and the destination nodes, separated by a hop distance equal to the average hop count with uniform random traffic in a  $32 \times 32$  2D-mesh network. The link for this direct connection is pipelined considering tile dimensions similar to ShortPath and it considers a packet containing 3 flits. All networks are operated at their maximum clock frequency.

slowest datapath stage  $(2 \times max(ST,LT))$ . DDR transmission of flits in the network ensures that the datapath can potentially be utilized for the complete duration of a cycle, serving a flit during both high and low clock phases. For a balanced router datapath, where the ST and LT delays are almost the same, this removes the slack from the router datapath and shifts it to the control logic as shown in Figure 1.1. DDRNoC uses this slack to modify the SA of the router to allocate input and output ports of the crossbar switch to up to two flits in a clock cycle. It is important to note that whereas the datapath of the DDRNoC (crossbar and link) can be used twice in a single cycle, the control logic (VA and SA) uses a complete cycle to make allocation decisions. The logic delay of VA and SA is less than twice the delay of the longest datapath stage (ST or LT), so the NoC routers can operate at a rate defined by datapath delays and achieve higher throughput.

## 1.2.2 Reducing NoC Packet Latency

Although the DDR traversal of flits over the NoC datapath significantly improves the throughput of the network compared to SDR networks, the latency of packets in the network suffers because the network operates at a lower clock frequency (although at DDR). In order to improve packet latency this thesis supplements the DDR flit traversal in a router with techniques that reduce average packet latency.

6 CHAPTER 1. INTRODUCTION

#### 1.2.2.1 Related Work

On the packet latency front, previous NoC designs use control forwarding (also called lookahead signaling) to inform the downstream router of incoming flits one clock cycle earlier. This enables the downstream router to complete VA and SA for incoming flits before their arrival [13, 33, 34], effectively hiding the cycle required for these allocation stages for each hop. Moreover, networks which allow flits to bypass allocation stages in the absence of contention, usually under low network load, have also been proposed [29, 30, 34]. These networks enable incoming flits to bypass the allocation stages when no competing requests exist. We analyze the performance of the ShortPath network [30], one of the fastest SDR networks which enables incoming flits to bypass allocation stages, when required conditions are met, and compare its average packet latency to that of an ideal pipelined connection between source and destination nodes. The results, presented in Figure 1.2, demonstrate that ShortPath has 3.3× higher packet latency compared to the ideal at low loads. This is because of two reasons: (i) all flits must spend at least 2 cycles per hop to go through ST and LT stages and (ii) clock period of the ShortPath network is about 20% longer than its ST delay which not only increases packet latency but also wastes datapath bandwidth. Our aim is to reduce the low-load packet latency gap by utilizing control forwarding and bypassing both SA and ST stages when possible. We analyze the application of these techniques in routers where both the control and the datapath allow flits to be routed at DDR. Moreover, we implement these techniques while ensuring that the critical path remains with in the datapath of the router.

# 1.2.2.2 Objective 2: Reduce Packet Latency with Control Forwarding in a DDR Router

The second objective of this thesis is to implement control forwarding in DDR NoC routers, to reduce packet latency. Control forwarding is used to transmit and register control signals at the downstream router one cycle before their corresponding flits are received. This enables the downstream router to initiate VA/SA in advance and to prepare the input VC registers to register the (up to) two incoming flits at the proper clock edge (negative clock edge for the flit propagating link during the high clock phase and vice versa). By the time the (up to) two incoming flits (per input port) are registered in the input VC buffers of the downstream router, their allocation decisions are already made, which, if successful, allow the flits to initiate ST without any allocation overhead. Control forwarding overlaps LT stage of the current router with VA/SA stage of the downstream router and hides the cycle a flit needs at each hop for allocation. For DDR NoC architectures, control forwarding reduces packet zero-load latency by one cycle per hop. It is implemented using dedicated crossbar switches (for control switch traversal), link wires (for control link traversal) and bypass paths which are separate from the flit datapath. Control forwarding is described in more detail in Chapter 3 of this thesis for the DDRNoC architecture.

# 1.2.2.3 Objective 3: Reduce Packet Latency with Allocation Bypassing in a DDR Router

The third objective of this thesis is to allow incoming flits in a DDR router to bypass the SA pipeline stage, when required network resources available and free from contention, and immediately initiate ST, followed by LT, in order to reduce packet

1.2. THESIS OBJECTIVES 7

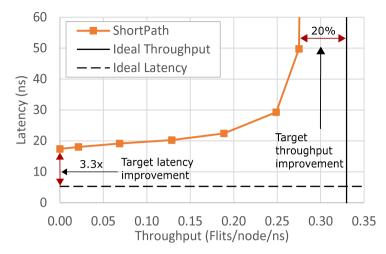

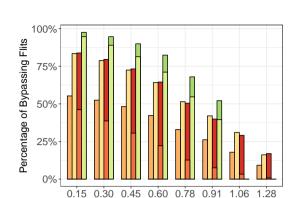

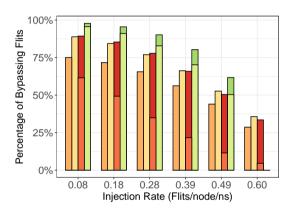

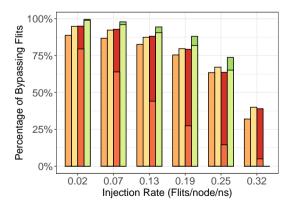

Figure 1.3: Percentage of non-turning hops in 2D-mesh networks of size  $N \times N$  with dimension order routing for uniform random traffic.

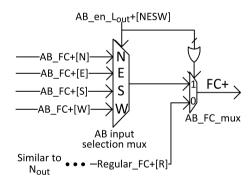

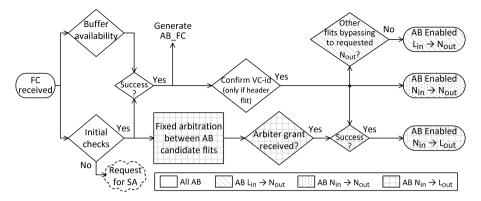

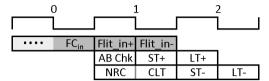

latency. Allocation bypassing targets end-to-end packet latency at low traffic loads when packets encounter reduced contention on their way to the destination. By allowing the incoming flits at a router input port to bypass the allocation stage, in the absence of contention, and immediately undergo ST, followed by LT, if downstream buffer resources are available, the amount of time a flit spends in the network is significantly reduced. To this end, this thesis proposes the FreewayNoC (described in Chapter 4) and the HighwayNoC (described in Chapter 5) router architectures which improve over the DDRNoC, by implementing allocation bypassing at different levels, in order to reduce zero-load packet latency.

The FreewayNoC architecture, which implements the simplest form of allocation bypassing, allows incoming flits to bypass the SA stage when propagating straight through a router (i.e. N to S, E to W and vice versa). Here, SA bypassing is supported only for straight flits because offering complete bypassing, from all inputs to all outputs, would require complex checks to ensure conflict-free ST and LT. The delay of these checks is prohibitively large and it would reduce the clock frequency of the network. So, FreewayNoC reduces the complexity of bypassing check logic by only enabling flits propagating a straight hop to bypass SA stage. This reduces the benefit of allocation bypassing, however, for most routing algorithms for 2D mesh networks, the number of turns a flit takes during its journey under low network loads are only two or three (to/from local port and an XY turn). Moreover, as shown in Figure 1.3, within the network, non-turning hops are more common than turning hops for uniform random traffic, specially for larger 2D-mesh network sizes. Further details of the FreewayNoC architecture are presented in Chapter 4 of this thesis.

The HighwayNoC improves over the FreewayNoC by enhancing the allocation bypassing support. In addition to allowing flits to bypass the allocation stage when propagating a straight hop, HighwayNoC further allows flits entering or exiting the network to bypass allocation as well. Flits entering through the local port and attempting to bypass to a non-local output can face competition from flits already in the network which are also trying to bypass to the same non-local output. HighwayNoC resolves this contention by always giving priority to in-network bypassing flits and requiring competing flits entering through the local input to request SA. Similarly, a router can simultaneously receive flits at multiple non-local inputs attempting to bypass to the local output port. In order to resolve contention in this case, HighwayNoC uses a simple fixed priority arbiter which selects the non-local input port which will be allowed to bypass allocation and directly switch incoming flits to the local output port. Other competing flits have to request allocation. HighwayNoC tolerates bypassing

8 CHAPTER 1. INTRODUCTION

check logic delays at the local port by utilizing the fact that there is a shorter link (relative to inter-router links) connecting the local port of a router to the network interface. Further details of the HighwayNoC architecture are presented in Chapter 5 of this thesis.

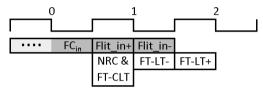

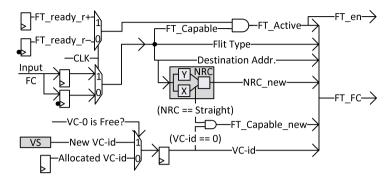

#### 1.2.2.4 Objective 4: Reduce Packet Latency with ST Bypassing

The fourth objective of this thesis is to enable incoming flits in a DDR NoC router to bypass the ST stage, in addition to the SA stage, when required network resources are available and free from contention, and immediately initiate LT, in order to reduce packet latency. To this end, this thesis proposes the FastTrackNoC architecture which improves over the HighwayNoC and allows incoming flits propagating an in-network straight hop to bypass the ST stage as well as the SA stage and directly initiate LT, in half a clock cycle. It utilizes dedicated intra-router bypass paths which allow both the data and the forwarded control information to bypass the crossbar switch in order to initiate LT. To reduce complexity of the bypass paths and satisfy tight timing constraints, ST bypassing requires pre-computation of the required checks and is restricted to flits at the head of a specific input VC propagating an in-network straight hop. As a result, FastTrackNoC maintains the clock period of previously described DDR NoC routers which do not offer ST bypassing and is able to reduce the low-load packet latency gap to ideal, shown in Figure 1.2. Further details on the FastTrackNoC architecture are presented in Chapter 6 of this thesis.

The contributions of this thesis towards the above mentioned objectives are presented at the end of this thesis, in Section 8.2.

### 1.3 Thesis Outline

The remainder of this thesis is organized as follows: Chapter 2 discusses the related work. Chapter 3 describes the design details of the DDRNoC network architecture which implements DDR datapaths to improve network throughput. Chapter 4 describes the design details of the FreewayNoC network architecture which enables incoming flits propagating an in-network straight hop to bypass allocation stage of the DDR router to reduce packet latency. Chapter 5 describes the design details of the HighwayNoC network architecture which extends allocation bypassing support offered in the FreewayNoC to also include flits entering and exiting through the local port, in order to further reduce packet latency. Chapter 6 describes the design details of the FastTrackNoC network architecture which enhances the HighwayNoC architecture by enabling incoming flits to bypass the ST stage as well as the allocation stage, in order to further improve packet latency. Chapter 7 presents the implementation, performance, power and energy efficiency results of the four DDR networks and compares them to relevant related work. Chapter 8 offers concluding remarks and possible directions for future work.

## Chapter 2

# **Related Work**

This Chapter presents an overview of techniques in the router architecture for increasing network throughput and reducing packet latency. The switching rate and minimum hop latency, define the limits for network throughput and packet latency, respectively. At the end of this Chapter, we report these two parameters for various state-of-the-art NoC routers measured in FO4 delays as reported in the published articles and confirmed by our post place and router (P&R) implementations.

## 2.1 Increasing NoC Throughput

There are three main approaches of improving throughput of single data rate (SDR) networks. They are: (i) use path diversity [35] and flow control to avoid congestion [36–38], (ii) improve matching quality of VC and switch allocators [18, 39, 40] and (iii) increase network switching rate by increasing network clock frequency. On one hand, the first two approaches improve the utilization per cycle of the network datapath resources to increase throughput and are orthogonal to the proposed DDR NoCs. On the other hand, the third approach enables the NoC datapath to propagate flits at a faster rate and increase network throughput. Previous NoC architectures have improved network clock frequency, and thereby the switching rate of their datapath, by increasing router pipeline depth, balancing the delay of different pipeline stages and simplifying or pipelining control (allocation) stages of a router.

A first step towards increasing clock frequency is to *pipeline router's datapath*. Typically, the datapath of a NoC router is divided into two stages, namely, the switch and the link traversal stages (ST and LT). Deeper pipelining of the datapath can further improve clock frequency at the cost of packet latency. One such example is Intel's full custom input buffered wormhole-switched NoC router which splits ST into two stages [9]. It achieves higher clock frequency by simplifying the datapath and the control stages and using a deeper pipeline with 6 stages per hop. Its simple datapath is only 32 bits wide and it has only two lanes (VCs) per input port to reduce the delay and complexity of the crossbar. It uses a crossbar of half the datapath width to save area, but operates it at DDR to maintain full throughput. Furthermore, it statically assigns VCs to packets and determines the route a packet will take in the network at the source node in order to avoid VC allocation and route computation, respectively, in the routers. This enables it to achieve a clock period of 15 FO4 delays and deliver

10 CHAPTER 2. RELATED WORK

high throughput. However, this comes at a high cost of minimum hop latency of 90 FO4 delays per hop, as presented in Table 2.1.

In order to avoid the high hop latency overhead of many pipeline stages, a router's datapath is typically split into two stages, ST and LT. Although this offers reasonably high clock frequency, it places router's control in the critical path and leads to wasteful slack in the datapath stages [18, 20]. This creates an imbalance in the router's pipeline stages because of which the control of the router (and not its datapath) defines the network clock frequency and the rate at which flits are switched. This reduces the throughput potential of the network because of the slack introduced in the datapath stages. This slack can be reduced, and the network throughput increased, by either retiming the router's pipeline stages or pipelining and simplifying its control logic.

Time stealing (or automatic retiming), currently supported by CAD tools, can be used to balance the pipeline of a router. Mishra et al. used time stealing to boost routers performance [20]. In doing so, a router would have a clock period equal to the average of all router stages. Although time stealing improves baseline operating frequency and throughput by up to 25%, by reducing the slack present in the datapath, there is room for improvement because the clock period is still longer than than the datapath delays.

Next step towards increasing network clock frequency is to either pipeline or simplify the control (allocation) stages of a router. An SDR NoC which *pipelines switch allocation* (SA) into two stages and improves clock frequency is SCORPIO [13]. It also utilizes several other architectural techniques, which include *combined VC and switch allocation* [41], *control forwarding* (also called *lookahead signaling*) [42] and *allocation bypassing*, to improve network performance. Implemented on a 36-core chip, SCORPIO demonstrates low latency and short cycle time of 28 FO4 delays.

More recently, ShortPath [30] was proposed, the fastest previous SDR NoC architecture. ShortPath not only splits SA into two pipeline stages, but also simplifies it by using *allocation request queues* to reduce the number of simultaneous allocation request from each input port. It also pipelines its datapath into two stages (ST and LT). ShortPath employs a dynamic allocation bypassing mechanism, but as opposed to SCORPIO, without relying on speculation or control forwarding and it operates at a higher clock frequency compared to SCORPIO. Considering 2D mesh topology and 4 VCs, the critical path of ShortPath is shared by part of its control logic and ST and is estimated to be 25 FO4 delays, which is still about 20% slower than its ST delay. As a consequence, ShortPath offers about 20% lower throughput than what could be achieved if the critical path was on the ST stage.

Trying to gain more throughput by further simplifying allocation to improve network clock frequency does not offer significant benefit because deteriorating matching quality of simple allocators reduces datapath utilization at high traffic [24]. One way to move beyond this limitation is to operate some parts of the router's datapath, which have sufficient slack, at DDR to improve their throughput. In the past, *DDR datapaths* have been used in isolated parts of NoC routers (crossbars or links), primarily to reduce area and power cost of the datapath. For example, Intel's full custom NoC router [9], described above, used a single *DDR crossbar* to support two network lanes. Xu et al. built DDR Wave-Pipelined (DWP) links interconnecting asynchronously NoC router ports to reduce the number of link-wires [31]. A router converts the data to be transmitted through a DWP link from SDR to DDR format by sending odd bits on the positive level of the clock and even bits on the negative level of the clock. NMOS transmission gates are used for this purpose. A separate wire is used to transmit a

reference clock signal to the downstream router, along with the data. This clock signal is used by the semi-static double-edge-triggered-flip-flops (SDETFFs) located at the input of the downstream router to latch the incoming data at both rising and falling edges of the clock. Since this data is being transmitted in DDR mode, the transmitted clock signal needs to toggle at the rate of data transmission.

More recently, RapidLink was proposed which used *DDR links* in a NoC architecture [32], based on the consideration that links can operate at double the frequency of a router. RapidLink improves throughput and latency because of two underlying mechanisms. Firstly, it splits a 4-VC NoC in to two *parallel physical sub-networks*, of 2 VCs each, which share common links. In effect, RapidLink achieves the throughput of two sub-networks that have separate links at half the link cost [16, 43]. Secondly, consecutive sub-routers operate at different clock edges allowing them to perform LT in half a cycle and therefore reduce per hop latency. In Rapidlink, link contention between the two sub-networks is avoided, however, contention within a sub-network router is not addressed. On the contrary, our DDR NoC routers allow all parts of a NoC datapath (input VC buffers, input and output port multiplexers and links) to operate at DDR. This enables DDR NoCs to route at DDR flits of the same or of different packets (stored in VCs of the same or different input ports) rather than only flits of two different sub-networks. RapidLink requires links to have limited length to be twice as fast as the routers.

This last limitation of RapidLink was addressed by the authors in their recent design (henceforth called Rapidlink2) where they proposed to pipeline the network links using *Dual Stream (DS) elastic buffers* with support for VCs and consider them as part of VC buffers [17]. Thereby, links are no longer in the critical path. However, according to our experiments the energy cost for transmitting a bit (for 128 bits wide flit) over a link that is pipelined using one or two sets of DS elastic buffers with support for 4 VCs increases versus a non-pipelined one by  $1.8 \times$  and  $2.5 \times$ , respectively. This is because a register is needed per VC, along with a 4-to-1 mux and an arbiter for each pipeline stage. In any case, DDR NoC routers with similar datapath modifications –router split in two sub-networks and replicated, rather than pipelined, links— can achieve better throughput than RapidLink2, as presented in the Section 7.3.3.

The DDR NoC architectures we propose in this thesis utilize the slack present in the router's datapath to improve network throughput, by operating the complete datapath at DDR. Then, the control has an entire, longer than ShortPath, cycle available to make allocation decisions. The clock period of a DDR NoC is 42 FO4 delays, twice its ST delay, and the switching rate of its datapath is half of that, i.e., 21 FO4 delays. As a consequence, the control logic is not in the critical path of a DDR NoC router and the ST delay defines the switching rate, which is about 20% higher than the fastest SDR NoC router, ShortPath.

## 2.2 Reducing NoC Packet Latency

There is a plethora of designs that aim at minimizing packet latency of SDR NoCs. Other than the strategies presented in the previous Section to increase network clock frequency (which will also reduce packet latency), there are four main approaches of reducing packet latency. They are: (i) deploying NoCs with low diameter topologies (i.e. with low maximum distance to other nodes), (ii) transferring flits across multiple hops or tiles in a single cycle, (iii) using routers with simpler datapaths to increase

12 CHAPTER 2. RELATED WORK

clock frequency and (iv) reducing the number of pipeline stages a flit must traverse per hop. These approaches are further discussed below.

In the past, various networks have exploited a lower, relative to the router, link delay to transfer flits across multiple hops. This has been supported by *richer topologies* with longer links to non-neighboring routers, e.g. 2D-torus, flattened butterfly topology [15,44], multidrop express channels (MECS) [22], and express links [4,27,45]. Such low diameter topologies require high radix routers and long inter-router links spanning multiple hops. But, routers with high radix require complex allocators and larger crossbar switches which reduces their clock frequency and throughput. Long interrouter links, if not pipelined, increase LT delay and reduce network clock frequency. Moreover, such topological changes can be considered orthogonal to the techniques incorporated by the proposed DDR NoC router architectures to reduce packet latency.

Another way to reduce packet latency is to transfer flits across multiple hops in a single cycle, as implemented in SMART NoC [26]. SMART NoC exploits low link delay to transfer flits across multiple hops in a single cycle using intra-router bypass paths across input VC buffers. Although such  $multi-hop\ links$  enable SMART networks to offer minimum latency per hop close to ST+LT, fitting multiple hops in a single cycle slows down network clock frequency and reduces offered throughput. It also requires complex allocators with inputs from neighboring routers for multi-hop setup requests.

One way to increase NoC clock frequency while also reducing its area is to simplify its datapath. More precisely, *bufferless NoCs* remove input VCs and FIFO buffers from routers to simplify datapath and control logic and increase clock frequency [46, 47]. In the best case (if control logic is not in the critical path), bufferless network can offer minimum hop latency of ST + LT, with ST delay equal to a (P-1):1 multiplexer compared to  $((P-1) \times V \times B):1$  multiplexer for a network with VC based flow control with P ports per router, V VCs per port and P flit registers per VC buffer. However, bufferless networks offer lower throughput compared to buffered networks because of deflection routing [47–49] or dropping flits at high load, making them unsuitable for applications with high throughput requirements.

More recently proposed *Routerless NoC* removes the router from NoC and uses on-chip wiring resources to create loops (rings) to connect its nodes. It can operate at a very high clock frequency and offer minimum hop latency equal to the delay of the inter-router link plus a 2:1 multiplexer. Compared to the proposed DDR NoC architecture which offers bypassing of SA and ST stages (called the FastTrackNoC), the Routerless NoC minimum hop latency is one 2:1 multiplexer delay less. However, the Routerless NoC has several significant disadvantages. Using fixed loops limits the routing options. The Routerless NoC alleviates this problem by using n overlapping loops in an  $n \times n$  network. However, this requires partitioning of the wire resources to n paths that are n times narrower substantially limiting throughput compared to conventional 2D-mesh networks with the equal wire resources. Moreover, Routerless NoC requires large buffers at their network interface to fit an entire packet in order to resolve conflicts. In turn, Routerless NoCs can offer slightly lower latency than the FastTrackNoC described in Chapter 6, however, their fixed loops either limit routing options and thus increase latency, or call for multiple overlapping loops which limit throughput considering equal wire resources.

Packet latency can also be reduced by reducing the number of pipeline stages a flit needs to go through to traverse a hop. Typically, NoC routers require flits to go through five stages per hop, which are: route computation (RC), VC allocation (VA), switch

allocation (SA), switch traversal (ST) and link traversal (LT). Pre-configured routing speculatively forwards incoming flits in preferred output directions without waiting for the result of allocation stage, saving one cycle per hop [50]. However, it has to tolerate misrouted, eagerly forwarded, dead flits. Similarly, XOR-based crossbars also allow switching to be performed without waiting for the arbitration result but require router datapath to be modified to encode and decode flits [51]. Less wasteful approaches have been the backbone of current state-of-the-art NoC routers. Lookahead routing allows to perform VC and switch allocation immediately after a header flit arrives as the route of the flit has already been computed by the upstream router [24]. Combined allocation [41] allows VA and SA to be performed in parallel and saves a cycle in the router pipeline [25]. Control forwarding enables allocation to start before the incoming flit is received [13, 29]. It is inspired by off-chip network designs [42] and uses a separate, narrow link to forward the control of a flit a cycle ahead of the data enabling the downstream router to process it one cycle earlier [13,29]. Finally, pipeline stage bypassing allows incoming flits which do not encounter any contention in a router to bypass some or all control stages of that router and proceed faster to the switch traversal stage [13, 30, 52].

ShortPath [30], described in the previous Section, utilizes, among others, lookahead routing and allocation bypassing (of VA and SA stages) to offer minimum hop latency of ST + LT stages i.e., 50 FO4 delays, as presented in Table 2.1. Since the clock period of ShortPath (25 FO4 delays) is defined by the router's control delays and is longer than its ST delays, there is potential to further reduce minimum latency by eliminating the slack present in the datapath stages (ST and LT) and operating it at a faster rate.

On the contrary, the DDR NoC architectures described in this thesis have a clock period defined by the datapath (ST) delays and they also implement lookahead routing, control forwarding, combined allocation and pipeline bypassing of the allocation stage to offer minimum hop latency of ST + LT delays, i.e., 42 FO4 delays. It is important to note that, although, minimum hop latency for ShortPath and proposed DDR NoCs (which do not offer ST bypassing) is ST + LT, DDR NoCs offer lower latency because of their faster switching rate, as presented in Table 2.1. Furthermore, our best proposed DDR NoC architecture, called the FastTrackNoC, enhances the bypassing capabilities of previous networks and allows incoming flits to bypass ST as well as SA stages, when required conditions are met, and directly initiate LT in half a clock cycle. Consequently, it can offer minimum hop latency of only 21 FO4 delays.

The challenge of supporting pipeline bypassing in a DDR router is that it adds complexity to the datapath of the router and this in turn affects throughput by reducing network clock frequency. More precisely, an incoming flit candidate for bypassing would need to compete with other concurrently arriving candidate flits, so checking whether the path is free adds logic to the ST and LT stages. On the other hand, the main performance advantage of DDR router relies on the fact that its critical path, which determines the rate at which flits are routed, is defined by the ST (or LT) delay without any additional control overhead. So, our proposed DDR NoC architectures need to preserve this throughput advantage by not offering allocation bypassing options to in-network turning flits (i.e., xy and yx turns), while, only offering ST bypassing to flits propagating an in-network straight hop (i.e. north to south, east to west and vice versa) from the head of a particular input VC. This significantly reduces contention among flits competing to bypass SA or ST stages at the same time as well as the overhead of bypass paths needed to support bypassing. The FreewayNoC and the HighwayNoC architectures, presented in Chapter 4 and 5, respectively, implement different levels of

14 CHAPTER 2. RELATED WORK

| Network        | Data rate | Pipeline<br>bypass | No. of pl. stages | Switching rate | Min. hop latency |

|----------------|-----------|--------------------|-------------------|----------------|------------------|

| Intel [9]      | (DDR)     |                    | 5+LT              | 1/15 FO4       | 90 FO4           |

| SCORPIO [13]   | SDR       | (SA)               | 3+LT              | 1/28 FO4       | 56 FO4           |

| ShortPath [30] | SDR       | VA, SA             | 3+LT              | 1/25 FO4       | 50 FO4           |

| DDRNoC         | DDR       |                    | 2+LT              | 1/21 FO4       | 84 FO4           |

| FreewayNoC     | DDR       | (SA)               | 2+LT              | 1/21 FO4       | 42 FO4           |

| HighwayNoC     | DDR       | SA                 | 2+LT              | 1/21 FO4       | 42 FO4           |

| FastTrackNoC   | DDR       | SA, ST             | 2+LT              | 1/21 FO4       | 21 FO4           |

Table 2.1: State-of-the-art NoC router architectures.

allocation bypassing to reduce packet latency. Finally, the FastTrackNoC architecture, presented in Chapter 6, offers both SA and ST bypassing to incoming flits in order to reduce packet latency.

## 2.3 Summary

Table 2.1 summarizes the main characteristics of competing designs including performance estimations measured in FO4 delays either taken from the respective papers [9] or based on post place and route results on 28nm technology, as explained in Chapter 7. The aforementioned Intel design offers a very fast router with oversimplified control and datapath which achieves the fastest rate of routing flits (1/15 FO4), however without pipeline bypassing it suffers long hop latency of 90 FO4 delays [9]. SCORPIO is a 3-stage SDR router that offers speculative allocation, control forwarding, and some pipeline bypassing support, and exhibits a cycle time of 28 FO4 delays [13]. It offers low hop latency of 56 FO4 delays achieved by bypassing router pipeline stages. ShortPath is a faster 3-stage SDR router with better pipeline bypassing and shorter critical path (25 FO4 delays) than SCORPIO [30]. It offers a minimum hop latency of 50 FO4 delays. DDRNoC, presented in this thesis, is the first fully DDR router that increases the rate of routing flits to one flit per 21 FO4 delays (every half a cycle) offering higher throughput. It offers pre-computed routing, speculative SA, and control forwarding, however it has no pipeline bypassing support so it suffers high packet latency. FreewayNoC improves on the DDRNoC offering limited in-network pipeline bypassing to non-turning flits, improving packet latency and HighwayNoC adds bypassing support for flits that enter or exit the network. Finally, FastTrackNoC is applied to a DDR router so it maintains the fast switching rates and reduces the minimum router latency to half (21 FO4 delays) employing ST bypassing.

# Chapter 3

# The DDRNoC Architecture

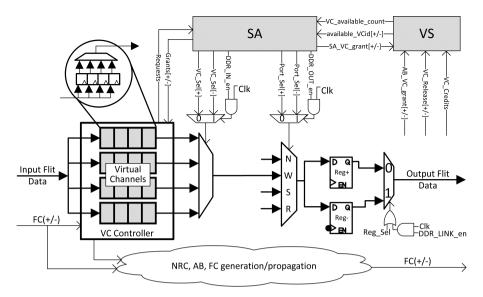

This Chapter describes the first DDR NoC architecture, called the DDRNoC. The DDRNoC is based on the observation that NoC clock frequency is defined by its control logic, while its datapath contains slack which reduces maximum achievable network throughput. The DDRNoC is an on-chip interconnect composed of routers that have a double-pumped datapath. As opposed to a conventional SDR NoC router, the critical path of a DDRNoC router is on its switch and link traversal rather than on the control. This allows packets to be routed at a faster rate increasing network throughput. Without loss of generality, our DDRNoC design considers a 2D-mesh network, with look-ahead XY-routing, composed of routers with virtual channels and credit-based flow control.

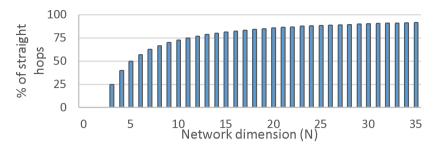

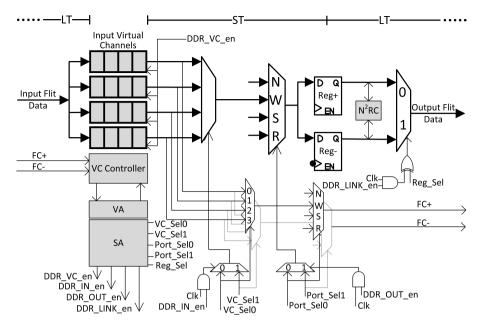

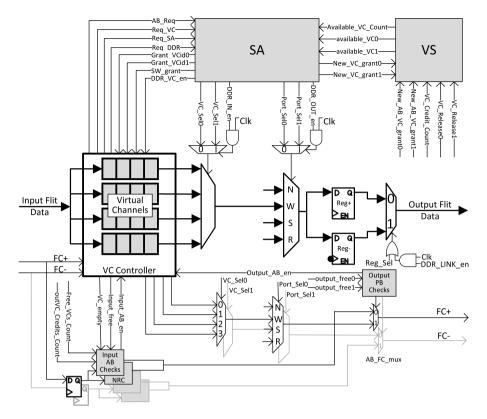

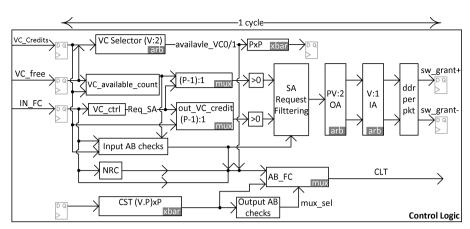

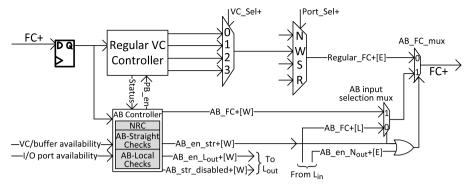

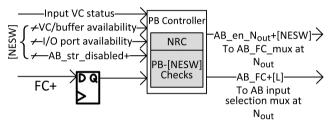

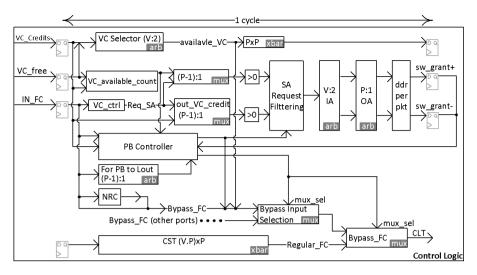

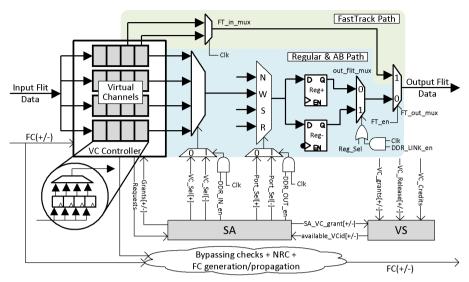

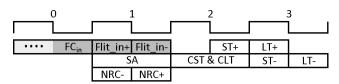

The top-level view of the DDRNoC router is shown in Figure 3.1. The datapath is composed of two stages: Switch Traversal (ST) and Link Traversal (LT). Each stage is able to handle two flits per cycle, one at the high phase and one at the low phase of the clock. There are three main control blocks in the router: Virtual Channel Allocation (VA), Speculative Switch Allocation (SA) and Next-Next-Route-Computation (N<sup>2</sup>RC) which are explained in detail below.

The rest of this Chapter is organized as follows. In the next Section, we describe the DDR datapath of the DDRNoC. In Section 3.2, we describe the timing details of flits and forwarded control information propagating through DDRNoC routers, illustrated using a timing example. In Section 3.3 we analyze the zero-load latency of DDRNoC. In Section 3.4, we describe the control modules of a DDRNoC router. In Section 3.5, we discuss some of our design decisions. Finally, in Section 3.6, we summarize the main aspects of the DDRNoC architecture.

## 3.1 Router Datapath

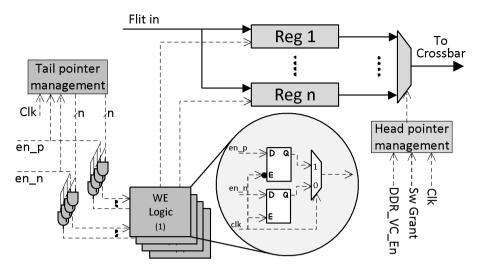

The input port of a DDRNoC router is able to receive two flits per cycle, one at each phase of the clock. As shown in Figure 3.2, the VC buffers are composed of registers that are selectively triggered either at the rising or at the falling edge of the clock to store a flit arriving at the low or the high phase, respectively. This enables two flits per cycle to be enqueued in a single VC buffer because they are stored in different registers of the buffer. Dequeuing two flits per cycle from a single VC buffer is enabled by the  $DDR_{-}VC_{-}en$  signal, which allows two different VC registers to be selected during two consecutive clock phases. Similarly, dequeuing two flits from different VCs within a

Figure 3.1: The DDRNoC router architecture.

cycle is enabled by the  $DDR\_IN\_en$  signal, which is used by the input port multiplexer to implement two input arbitration decisions ( $VC\_Sel0$  and  $VC\_Sel1$ ). Besides the flit data, the input port receives once every cycle early forwarded control information for the (up to two) received flits (FC+, FC-). As explained later, this information refers to flits that arrive a cycle later, thus it is called  $forwarded\ control$ .

Besides the input port multiplexer, the ST stage includes the output port multiplexer, which applies up-to two output arbitration decisions per cycle (*Port\_Sel*0, *Port\_Sel*1) using the *DDR\_OUT\_en* signal. This allows two different input ports to send a flit to the same output port during the high or the low phase of a clock cycle.

A positive edge triggered output register (Reg+) and a negative edge triggered one (Reg-) are used to store the flits switched in the low and the high phase of a cycle, respectively. Subsequently, a multiplexer selects one of the two registers to send a flit through the link. Using the  $DDR\_LINK\_en$  signal, this multiplexer allows LT of two flits in a cycle. For packet header flits, the  $N^2RC$  module computes routing information for two-hops ahead in half a cycle and the result (2-bits) is embedded in the header flit data before LT.

In general, DDR mode is selected in two cases. Firstly, when flits of multiple packets in different VCs compete for the same datapath part (input port multiplexer, output port multiplexer, or link). Secondly, when multiple flits of a single packet are available in a VC buffer and their requested datapath is not allocated to any other packet during the same cycle. Figure 3.3, illustrates more precisely all alternative uses of the DDRNoC datapath. In Figure 3.3a, two flits in different VCs of the same input port are sent to the same output port in DDR (DDR\_IN\_en and DDR\_LINK\_en enabled). Figure 3.3b shows two flits from different input ports sent to the same output port in DDR (DDR\_OUT\_en and DDR\_LINK\_en enabled). Two flits from different VCs of the same input in DDR going to different outputs are illustrated in Figure 3.3c (DDR\_IN\_en is enabled). Figure 3.3d shows two flits of the same packet (same input

3.2. TIMING 17

Figure 3.2: DDRNoC VC buffers. Signals en\_n and en\_p signals indicate whether there is a valid flit in the high and low clock phase. Tail and header pointers as well as a write enable signal (per register) are updated based on these two signals.

Figure 3.3: Alternative ways to propagate a flit through the DDRNoC router datapath.

VC) in DDR (*DDR\_VC\_en* and *DDR\_LINK\_en* enabled). Finally, a flit sent in SDR is depicted in Figure 3.3e.

In parallel to the ST of (up to) two flits, their control information (FC+ and FC-) is forwarded separately. As explained next, both FC+ and FC- are switched during the first half of a cycle and traverse the link during the second half. This is possible as the minimum ST and LT delay in a DDRNoC router is half a cycle.

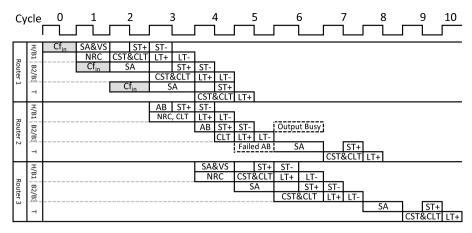

## 3.2 Timing

Despite operating at SDR or DDR, a flit always spends half a clock cycle in each datapath stage (ST or LT), separated by another half a clock cycle which is used for route computation. In DDR mode, a flit utilizes either the high or the low phase of the clock. We call a flit using the high clock phase  $flit^+$  and one using the low phase  $flit^-$ . A  $flit^+$  is switched during the first half of a cycle and registered by the negative edge triggered output register Reg-, it uses again the high phase of the next cycle for LT and is stored at the input VC of the downstream router in the next negative clock edge. Similarly, a  $flit^-$  uses for both ST and LT two consecutive low clock phases, it is registered in the positive edge triggered output register Reg+ and is stored in a VC

Figure 3.4: Timing of two packets traversing two hops through the same input and output ports (different VCs) of two routers.

buffer of the downstream router in the next positive clock edge. Finally, a flit switched at SDR ( $flit^{\pm}$ ) propagates in a manner similar to  $flit^{+}$ .

Besides data, a flit usually carries additional control bits that indicate flit type, allocated VC, or the computed next route. In a baseline SDR router, these control bits pass through ST and LT together with the data of a flit. On the contrary, in a DDRNoC router, the control bits of flit(s) travel ahead of the data so as to enable the SA in the downstream router a cycle earlier and reduce packet latency. During ST of flits,  $flit^+$  and  $flit^-$ , their control bits FC+ and FC- perform both ST and LT (half a cycle each). In effect, during the cycle flit<sup>+</sup> and flit<sup>-</sup> perform LT, their control bits are already in the downstream router and are considered in the SA and VA, saving one cycle. We call the above technique control forwarding. Control forwarding is possible in our router architecture for two reasons: firstly, due to the fact that switch and link traversal have a latency of half a cycle, and secondly, because a flit performs ST and LT in two consecutive cycles (instead of a single cycle). A flit does not enter a new datapath stage in the middle of a cycle to avoid misalignment with the SA in the downstream router, which anyway starts at the positive clock edge and takes an entire cycle to complete. Although the data of a flit are routed slower than they potentially could, sending the control of the flits ahead, enables the downstream router to start SA a cycle earlier recovering the wasted time.

In order to perform the NRC in parallel with the VA and SA in a router with control forwarding, the entire destination address of a packet should be forwarded together with the rest of the control bits (earlier than the actual header flit). That would be quite costly as it would require for a  $16 \times 16$  2D-mesh, 16 more link wires for the two flits in flight. To avoid this, we perform the NRC in the output of the upstream router, effectively, performing a routing computation for two hops ahead (Next-Next Route Computation:  $N^2RC$ ). A flit takes half a cycle to traverse a link, during either the high or low clock phase, but it is sitting idle in an output register (Reg+, Reg-) for the other half of the cycle.  $N^2RC$  is performed during this idle half cycle. The  $N^2RC$  module is placed after the output registers and before the link multiplexer. When a

head flit is registered in the output after ST, N<sup>2</sup>RC is performed for half a cycle, the result of the N<sup>2</sup>RC overwrites the (two) respective header bits and is sent to the link multiplexer before LT. Note that the two output registers are triggered in different clock edges, so the same N<sup>2</sup>RC module can be used by one of them in each half of the cycle.

For the header flit, SA speculates on the VA allocation result. Thereby, the VA can be performed in parallel with the SA. The header flit zero-load latency is then reduced by one cycle when the speculation is successful.

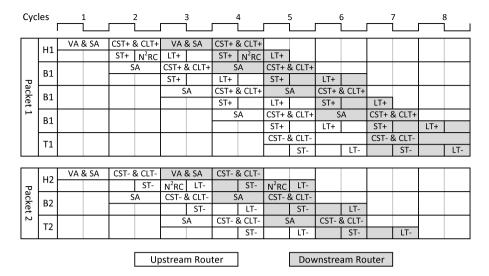

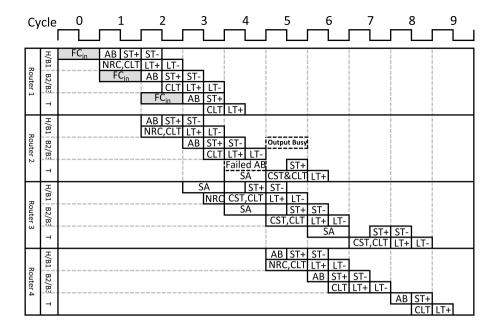

Figure 3.4 illustrates the timing of two DDRNoC routers, putting all the above together. In the example, a packet of five flits and a packet of three flits traverse the same two routers. In the first router, VA and SA is performed during the first cycle for the head flits of the two packets. Subsequently, ST is performed for the header flits (ST<sup>+</sup> and ST<sup>-</sup>), each using half of a cycle. In parallel, during cycle 2, control information for the head flits is traversing the switch (CST<sup>+</sup> and CST<sup>-</sup> for flit<sup>+</sup> and flit<sup>-</sup>, respectively) and the link (CLT<sup>+</sup> and CLT<sup>-</sup>). H1 traverses the switch in the high phase of clock 2 and is stored in the output register Reg – at the falling edge of cycle 2 enabling  $N^2RC$  to be performed in the second half of cycle 2. Similarly, H2 traverses the switch in the low phase of clock 2, it is stored in the output register Reg+ at the rising edge of cycle 3 enabling N<sup>2</sup>RC to be performed in the first half of cycle 3. LT is then performed by H1 and H2 after their N<sup>2</sup>RC during the first and second half of cycle 3, respectively. In parallel during the same cycle (cycle 3), SA and VA are performed in the downstream router for the two header flits, as their control information has arrived a cycle earlier. The subsequent flits of the two packets follow, sharing the datapath of the two routers, having one cycle latency per ST and LT stage and throughput of two flits per cycle. Note, that packet 2 is two flits shorter than packet 1 and therefore the last two flits of packet 1 are routed in DDR mode through the two routers, similar to the example of Figure 3.3d.

## 3.3 Zero-Load Latency Analysis

The zero-load latency (ZLL) in a DDRNoC<sup>1</sup> is equal to one cycle for the first SA plus two cycles per hop for the head flit and an additional half a cycle for each of the remaining flits<sup>2</sup>:

$$ZLL_{DDRNoC} = 1 + 2 \times hops + (N-2)/2 \ cycles \tag{3.1}$$

where, *hops* is the number of hops traversed by the packet, and *N* the number of flits per packet.

Moreover, the ShortPath router which uses dynamic pipeline bypassing to reduce pipeline stages to 2 (VA, SA and ST in one cycle and LT in the other) has a zero load latency of:

$$ZLL_{ShortPath} = 2 \times hops + N - 1 \ cycles$$

(3.2)

As mentioned in the introduction and confirmed in our evaluation, the ST/LT stages in a router can be clocked about 18% faster than ShortPath. The ST or LT delay

<sup>&</sup>lt;sup>1</sup>We consider that the VC buffer size is sufficient to support the credit round-trip time, as explained in 3.4.3.

<sup>&</sup>lt;sup>2</sup>In zero load, a single packet can send its flits in DDR having serialization latency of half a cycle per flit (Figure 3.3d). In case of contention, the serialization latency would increase at least to one cycle per flit.

is then 83% the delay of the ShortPath NoCs. Considering that the DDRNoC can have a clock period of  $2\times$  the ST (or LT) delay, then one DDRNoC cycle is equal to about 1.67 ShortPath cycles. So, for a packet with 3 flits, propagating between 2 and 32 hops, zero-load latency for the DDRNoC is about 53-66% longer than ShortPath.

### 3.4 DDRNoC Control

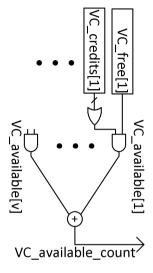

#### 3.4.1 Virtual Channel Allocation

Despite the increasing load of the VA in a DDRNoC router, we choose to use the SDR baseline VA unmodified. That is a VA with round-robin priority-based output-first separable allocator as described by Becker and Dally [39]. For a router with P output ports and V VCs per port, the VA uses PV:1 and V:1 arbiters for the output and input arbitration, respectively, and takes one cycle to complete allocation. In DDR mode, up to two head flits per cycle may arrive at an input port of a router, which (in the worst case) would result in ten new VA requests per cycle, compared to five in the baseline. Although this may lower the VA matching quality, we did not observe any significant performance drawbacks in our experiments for packet sizes based on application driven workloads.

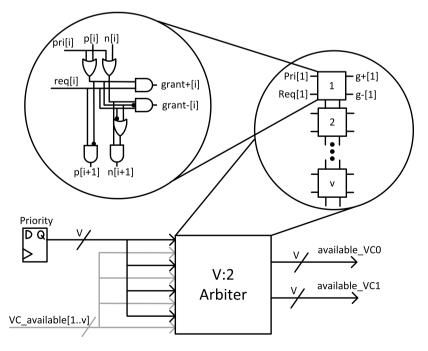

#### 3.4.2 Switch Allocation

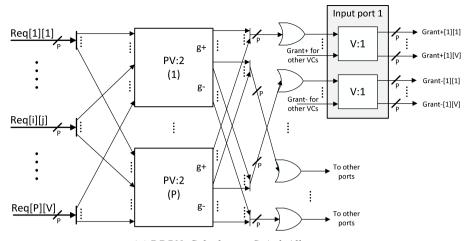

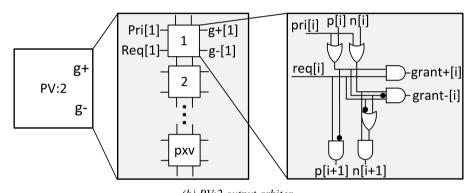

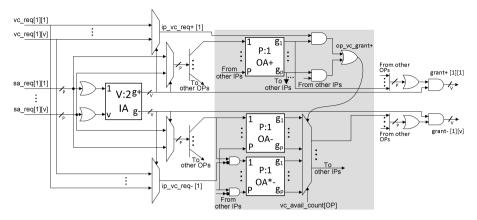

The DDRNoC routers, as well as the baseline SDR ones, use a single-cycle speculative SA to resolve contention among flits requesting the same input and output ports of the crossbar. The speculative SA gives higher priority to requests which have already been allocated a downstream VC. The DDRNoC SA, shown in Figure 3.5a is a modified version of the output-first separable allocator described in [39]. It makes two input and output arbitration decisions every cycle, one for the high  $(g^+[i])$  and one for the low  $(g^{-}[i])$  phase of the clock. The output arbiter for a single output port, shown in Figure 3.5b, accepts  $P \times V$  arbitration requests and a one-hot priority vector (which updates in round-robin) to generate two grant signals for each input request. At most one of these two grant signals would be asserted per input request. Moreover, at most one  $g^+$  and one  $g^-$  signal would be asserted as a result of each output port arbitration. The second stage of the SA performs (input) arbitration among the VCs of an input port, which after the output arbitration might have two or more of its VCs granted access to the switch on the same half of the cycle. Two V:1 input arbiters per port are required, one to arbitrate among grants received for the high half of the cycle and the other among the grants received for the low half. After input arbitration a maximum of two grants (one per clock edge, grant+ and grant-) are asserted for each input port. The DDRNoC SA described so far is not yet able to allow two flits of the same packet to be switched in DDR mode. This is performed using additional logic appended to the above SA. In particular, based on the above grant decisions, a single packet, with an allocated downstream VC, will be allowed to send two flits through the switch in a cycle when all following conditions are met: (i) that packet has received a SA grant, (ii) more than one flits of the packet are available in the input VC, (iii) there are enough credits for them, (iv) no other packet has been granted the same input or output of the switch. After SA, the grant+ and grant- signals are registered and the DDR enable signals are generated. These are the signals that control the DDR mode

3.4. DDRNOC CONTROL 21

(a) DDRNoC dual grant Switch Allocator.

(b) PV:2 output arbiter.

Figure 3.5: Block diagram of the DDRNoC Switch Allocator.