Whether you realize it or not, we have witnessed the evolution of wireless communication technologies taking place in the last few decades. Services such as real-time video calls, which were originally accessible to TV reporters only, are now available for everyone. The tons of equipment previously required for establishing a video connection is now converged to a smartphone easily fitting our pocket. Moreover, the continuously developing high speed and low latency wireless networks enable new services such as self-driving cars and

the internet of things, which would be integrated into our daily lives in the nearest future.

The evolution of wireless communications is driven by advances in radio hardware technologies, which need to offer us high-performance, energy-efficient, compact, and cost-effective solutions. The above targets are feasible at an individual metric level but are very challenging in combination. This thesis presents a non-conventional design approach for efficient and high-performance millimeter-wave power amplifiers (PAs), which are critical components of modern wireless systems. The focus of this work is on silicon-based technologies allowing a high level of integration at a reasonable cost but traditionally providing insufficient output power and energy efficiency limited by conventional power-combining approaches. The latter problems have been partly overcome by the proposed PA architecture based on a new efficient power-combining solution. The work evaluates the performance and scalability bounds of the architecture as well as presents its optimization flow for achieving optimal system-level performance by accounting for various multiphysics effects. Moreover, the proposed architecture has been demonstrated through an example of the combined PA implemented in an advanced high-speed SiGe process from NXP Semiconductors, which is one of the main industrial partners of this work. The developed PA has a wideband performance with both high efficiency and high output power, which outperforms the state-of-the-art silicon-based PAs.

I believe that the techniques and ideas proposed in this thesis will play an important role in sustainable wireless systems where high-performance, low energy consumption, and cost efficiency are important requirements.

Wideband Watt-Level Spatial Power-Combined Power Amplifier in SiGe BiCMOS Technology for Efficient mm-Wave Array Transmitters

PHD THESIS

Wideband Watt-Level Spatial Power-Combined Power Amplifier in SiGe BiCMOS Technology for Efficient mm-Wave Array Transmitters

ARTEM ROEV

#### DEPARTMENT OF FLECRICAL ENGINEERING

## Wideband Watt-Level Spatial Power-Combined Power Amplifier in SiGe BiCMOS Technology for Efficient mm-Wave Array Transmitters

#### ARTEM ROEV

Department of Electrical Engineering

Antenna Group

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden 2021

#### Wideband Watt-Level Spatial Power-Combined Power Amplifier in SiGe BiCMOS Technology for Efficient mm-Wave Array Transmitters

ARTEM ROEV ISSN 1403-266X

© ARTEM ROEV, 2021.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie n<br/>r ${\rm R}03{\rm X}$  ISSN 0346-718X

Department of Electrical Engineering Antenna Group CHALMERS UNIVERSITY OF TECHNOLOGY SE-412 96 Göteborg Sweden

Telephone: +46 (0)31 - 772 1000

Email: roev@chalmers.se

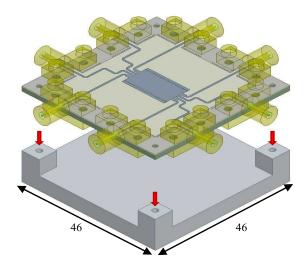

Front Cover: The figure on the front cover illustrates the developed Watt-Level spatial power-combined power amplifier in SiGe BiCMOS technology.

Typeset by the author using  $\LaTeX$ .

Chalmers Reproservice Göteborg, Sweden 2021

## Wideband Watt-Level Spatial Power-Combined Power Amplifier in SiGe BiCMOS Technology for Efficient mm-Wave Array Transmitters

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op donderdag 31 augustus 2021 om 16:00 uur

door

#### ARTEM ROEV

geboren te Izjevsk, Russische Federatie

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

1<sup>e</sup> promotor: prof.dr. M.V. Ivashina (Chalmers University of Technology)

2<sup>e</sup> promotor: prof.dr. M. Matters-Kammerer

copromotor(en): prof.dr.ir. R. Maaskant (Chalmers University of Technology) leden: prof.dr. Z. Popovic (University of Colorado at Boulder)

prof.dr. H. Sjöland (Lund University)

prof.dr.ir. M.J. Bentum

prof.dr. S. E. Gunnarsson (SAAB AB)

adviseur(s): dr. A. Höök (SAAB AB)

ir. M. Geurts (NXP Semiconductors) dr.ir. J. Qureshi (NXP Semiconductors)

Het onderzoek of ontwerp dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

## Abstract

The continued demand for high-speed wireless communications is driving the development of integrated high-power transmitters at millimeter wave (mm-Wave) frequencies. Si-based technologies allow achieving a high level of integration, but usually provide insufficient generated RF power to compensate for the increased propagation and material losses at mm-Wave bands due to the relatively low breakdown voltage of their devices. This problem can be reduced significantly if one could combine the power of multiple active devices on each antenna element. However, conventional on-chip power combining networks have inherently high insertion losses reducing transmitter efficiency and limiting its maximum achievable output power.

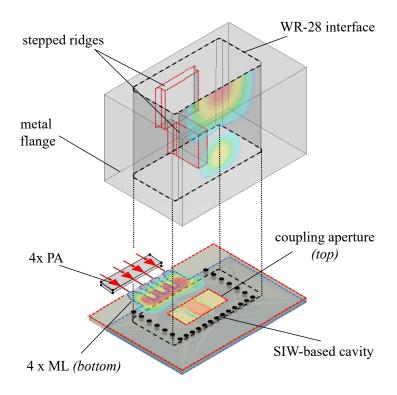

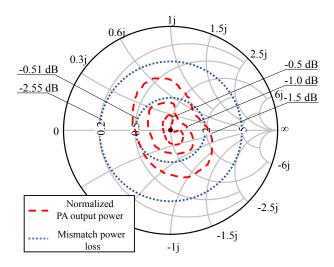

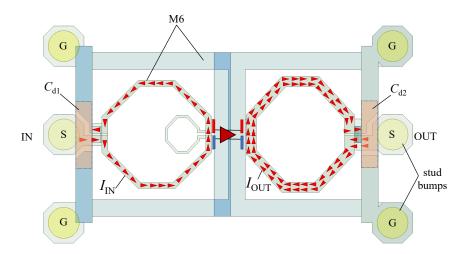

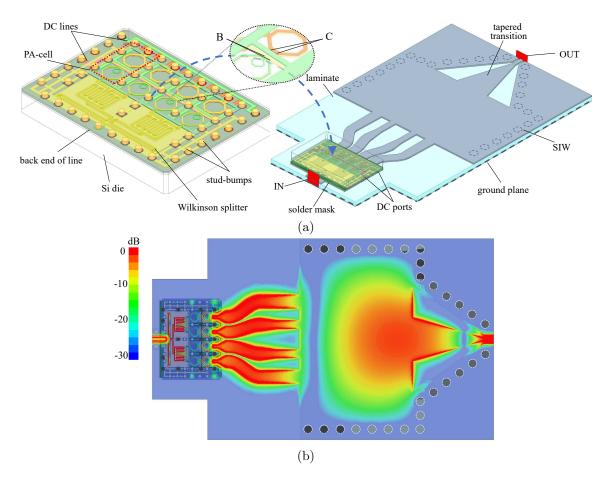

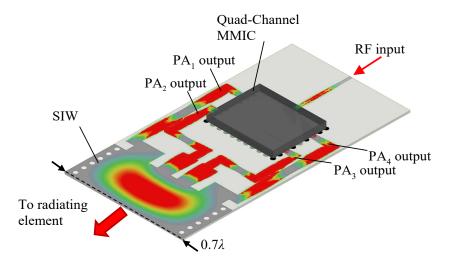

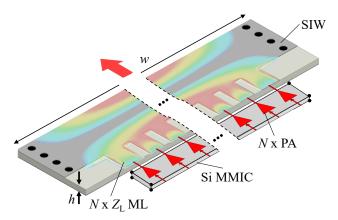

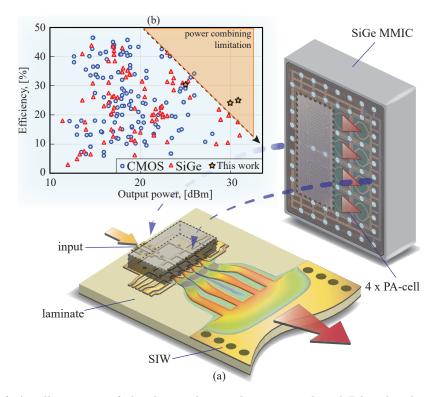

This work presents a non-conventional design approach for mm-Wave Si-based Watt-level power amplifiers that is based on novel power-combining architecture, where an array of parallel custom PA-cells suited on the same chip is interfaced to a single substrate integrated waveguide (to be a part of an antenna element). This allows one to directly excite  $TE_{m0}$  waveguide modes with high power through spatial power combining functionality, obviating the need for intermediate and potentially lossy on-chip power combiners. The proposed solution offers wide impedance bandwidth (50%) and low insertion losses (0.4 dB), which are virtually independent from the number of interfaced PA-cells. The work evaluates the scalability bounds of the architecture as well as discusses the critical effects of coupled non-identical PA-cells, which are efficiently reduced by employing on-chip isolation load resistors.

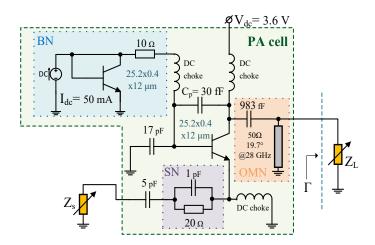

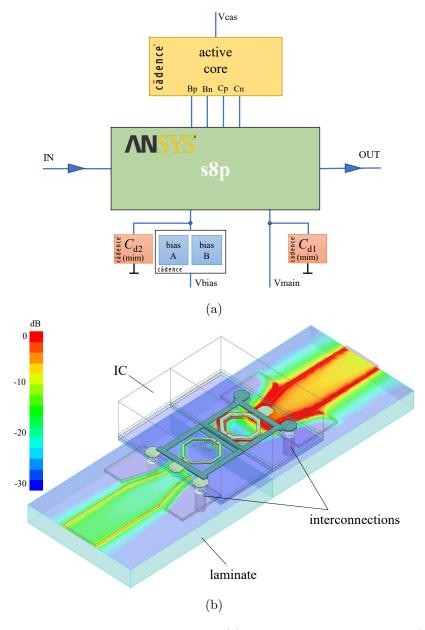

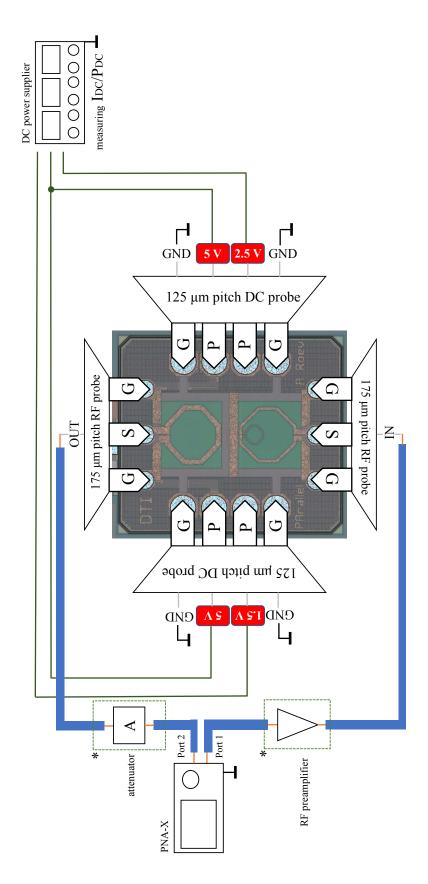

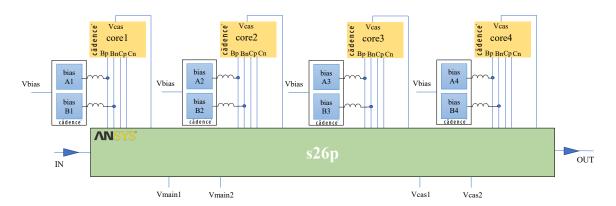

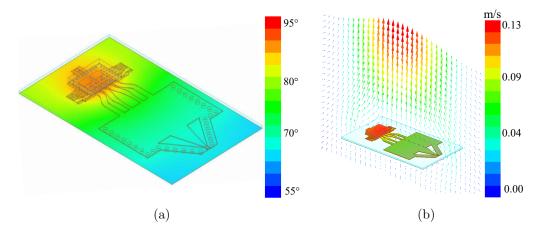

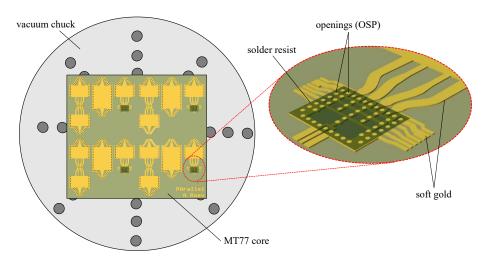

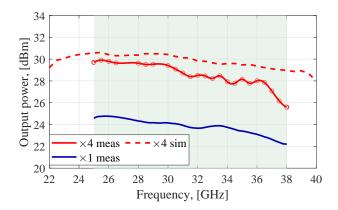

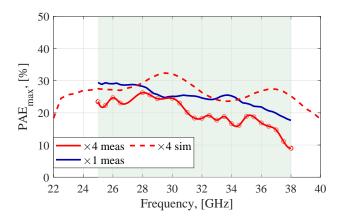

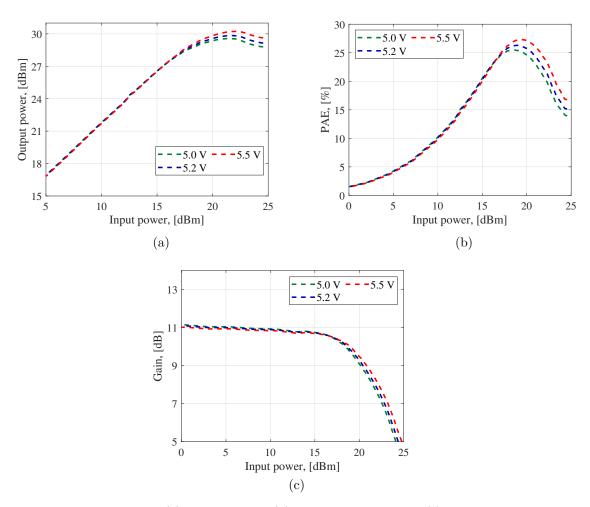

The proposed architecture has been demonstrated through an example of the combined PA with four differential cascode PA-cells suited on the same chip, which is flip-chip interconnected to the combiner placed on a laminate. This design is implemented in a 0.25  $\mu$ m SiGe BiCMOS technology. The PA-cell has a wideband performance (38.6%) with both high peak efficiency (30%) and high saturated output power (24.9 dBm), which is the highest reported output power level obtained without the use of circuit-level power combining in Si-based technologies at Ka-band. In order to achieve the optimal system-level performance of the combined PA, an EM-circuit-thermal optimization flow has been proposed, which accounts for various multiphysics effects occurring in the joint structure. The final PA achieves the peak PAE of 26.7% in combination with 30.8 dBm maximum saturated output power, which is the highest achievable output power in practical applications, where the 50- $\Omega$  load is placed on a laminate. The high efficiency ( $\geq$  20%) and output power ( $\geq$ 29.8 dBm) over a wide frequency range (30%) exceed the state-of-the-art in Si-based PAs.

$\bf Keywords:$  spatial power combining, array amplifiers, integration, RFIC, substrate integrated waveguide.

## **Preface**

This thesis is in partial fulfillment for the degree of Doctor of Philosophy at Chalmers University of Technology and Eindhoven University of Technology (TU/e).

The work resulting in this thesis was carried out between December 2016 and August 2021 at the Antenna Group, Department of Electrical Engineering, Chalmers and Integrated Circuits Group, Department of Electrical Engineering, TU/e. The doctoral program involved the industrial internships at SAAB AB (Gothenburg, Sweden) and NXP Semiconductors (Nijmegen, The Netherlands) - in a total duration of 21 months. Professor Marianna Ivashina of Chalmers is the main supervisor and examiner. Associate Professor Rob Maaskant of Chalmers is the co-supervisor. Professor Marian Matters-Kammerer of TU/e is the dual-degree promoter.

The work is a part of the Silicon-based Ka-band massive MIMO antenna systems for new telecommunication services (SILIKA) project, funded by the European Union's Horizon 2020 research and innovation program under the Marie Skłodowska Curie grant agreement №721732.

## Acknowledgment

First and foremost, I would like to express my deepest gratitude to my main supervisor, Prof. Marianna Valerevna Ivashina, for the great opportunity she gave me to start this doctoral journey and for her enthusiasm, optimism, and continuous support in many aspects of my research and life in general. I also wish to personally thank my co-supervisor, Assoc. Prof. Rob Maaskant, for his infinite support in a deep understanding of complex electromagnetic phenomena with special attention to detail. It was a pleasure to work under their leadership.

I want to thank Prof. Marion Matters-Kammerer for accepting to become my supervisor at TU/e under the dual-degree program. We have had many fruitful discussions, and I look forward to our future collaboration in the coming years. Furthermore, I would like to acknowledge all members of the Silika consortium, especially Profs. Bart Smolders and Ulf Johansson from TU/e, for initiating and leading this joint project. I would also thank Dr. Anders Höök (SAAB AB) for the interest, attention, and time he has put at the beginning of my project.

My sincere gratitude goes to all the current and former members of the BL Smart Antenna Solutions group (NXP Semiconductors) I had the honor to work with during my more than 1.5-year industrial internship. In particular, I would thank Ir. Marcel Geurts for his support in problem-solving, responsiveness, and priceless lessons extending beyond the internship realms. I also wish to especially thank Dr. Jawad Qureshi for his expert advice, constructive feedback, and valuable time he spent teaching me. Successful development of the custom power amplifier in such a short period of time has not been possible without his technical insights and extensive experience. Furthermore, I would like to acknowledge Ir. Louis Praamsma, Dr. Xin Yang, Dr. Mustafa Acar, Ir. Jan Willem Bergman, Carlota Salamat and Alexander Simin, whose expertise and encouragement allowed me quickly learn Qubic process and prepare three successful designs for a single tape-out. In addition, I wish to thank Marcel Webers for supporting with the measurements and Ir. Arjen van der Helm from TCE-N Sample Services for assisting with the prototype assembly. Moreover, I will always be thankful to Parastoo Taghikhani, Marzieh SalarRahimi, Mohammad Hossein Moghaddam, and Dr. Eduardo Vilela Pinto dos Anjos for their kind friendship and invaluable help in many practical aspects during my stay in the Netherlands.

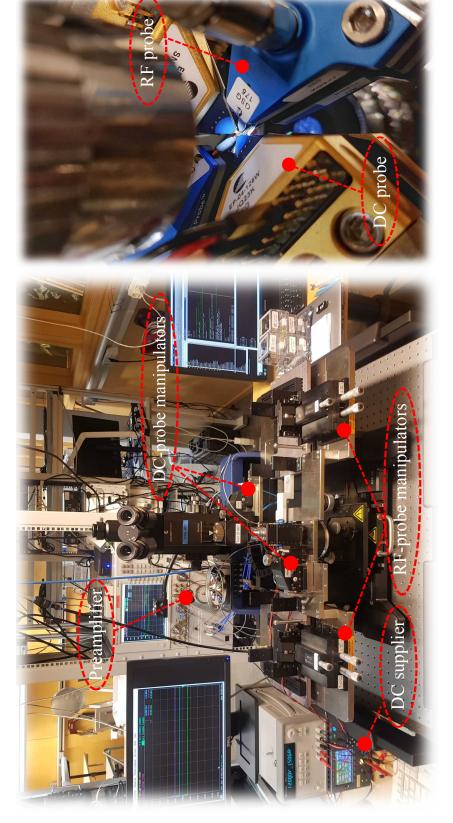

My special acknowledgment goes to Prof. Christian Fager, Dr. Yu Yan, and Dr. Ahmed Adel Hassona from the Microwave Electronics Laboratory (Chalmers) for their help with building measurement setups and performing on-wafer tests. My special thanks are extended to all former and current colleagues in the Antenna Systems Group at Chalmers and Integrated Circuits Group at TU/e for creating a nice and enjoyable working environment. In particular, I am highly indebted to my friend, Dr. Oleg Iupikov, for his kind friendship and invaluable and consistent support and help from the first day I entered the group in 2016.

Finally, I would like to thank the faculty opponent, Prof. Zoya Popovic, and the committee members, Adj. Prof. Sten E. Gunnarsson, Prof. Henrik Sjöland, and Prof. Mark Bentum for their time invested in reviewing my thesis.

Last but not least, I would like to express my deepest gratitude to my family for always being there for me, supporting me at every step I take.

## List of Publications

This thesis is based on the work contained in the following appended papers:

#### Paper A

A. Roev, R. Maaskant, M. Ivashina, and A. Höök, "Wide-band spatially distributed TE<sub>10</sub> substrate integrated waveguide transition for high-power generation at mm-Wave frequencies," in *Proceedings of the 2017 International Symposium on Antennas and Propagation (ISAP)*, Phuket, 2017, pp. 1-2.

#### Paper B

A. Roev, R. Maaskant, A. Höök, and M. Ivashina, "Efficient millimeter-wave high power generation with spatial power-combined feeding element," in *Proceedings of the 12th European Conference on Antennas and Propagation (EuCAP 2018)*, London, 2018, pp. 1-4.

#### Paper C

A. Roev, R. Maaskant, A. Höök, and M. Ivashina, "Wideband mm-Wave transition between a coupled microstrip line array and SIW for high-power generation MMICs," in *IEEE Microwave and Wireless Components Letters*, vol. 28, no. 10, pp. 867-869, Oct. 2018.

#### Paper D

A. Roev, M. V. Ivashina, R. Maaskant, and M. K. Matters-Kammerer, "N-way spatial power combining in SIW for high power generation MMICs – scalability bounds," in Proceedings of the 2019 IEEE International Symposium on Antennas and Propagation and USNC-URSI Radio Science Meeting, Atlanta, GA, USA, 2019, pp. 1789-1790.

#### Paper E

A. Roev, R. Maaskant, M. K. Matters-Kammerer, and M. V. Ivashina "High power mm-Wave spatial power combiner employing on-chip isolation resistors," in *Proceedings of the 14th European Conference on Antennas and Propagation (EuCAP 2020)*, Copenhagen, 2020, pp. 1-5.

#### Paper F

A. Roev, P. Taghikhani, R. Maaskant, C. Fager, and M. Ivashina, "A wideband and low-loss spatial power combining module for mm-Wave high-power amplifiers," in *IEEE Access*, vol. 8, pp. 194858-194867, 2020.

#### Paper G

A. Roev, J. Qureshi, M. Geurts, R. Maaskant, M. Matters-Kammerer, and M. Ivashina, "A wideband mm-Wave Watt-level spatial power-combined power amplifier with 26% PAE in SiGe BiCMOS technology," in preparation for submission to *IEEE Transactions on Microwave Theory and Techniques*, vol. X, pp. XX-XX, 2021.

#### Paper H

A. Roev, R. Maaskant, M. Ivashina, "Transition arrangement between an SIW structure and a transmission line arrangement," Swedish Patent application M1 P2SE00 AB/ab. Filled on: October 27, 2017.

Other related publications of the Author not included in this thesis:

• O. A. Iupikov, A. A. Roev and M. V. Ivashina, "Prediction of far-field pattern characteristics of phased array fed reflector antennas by modeling only a small part of the array – case study of spaceborne radiometer antennas," in *Proceedings of the 2017 11th European Conference on Antennas and Propagation (EuCAP)*, Paris, 2017, pp. 2636-2639.

#### Thesis

Some of the work presented in this thesis, such as text, figures, and tables may partly or fully be reused from  $[\star]$ , which is a part of the author's doctoral studies.

[\*] A. Roev, "Compact and wideband spatial power combining module for mm-Wave high-power amplifiers," Thesis for the Degree of Licentiate of Engineering, Department of Electrical Engineering, Antenna Group, Chalmers University of Technology, Gothenburg, 2020.

## Acronyms

3GThird Generation 4GFourth Generation 5GFifth Generation AG Array Gain B2BBack-to-Back **BEOL** Back End of Line BiCMOS Bipolar Complementary Metal Oxide Semiconductor BWBandwidth CBCommon Base CECommon Emitter CPWCoplanar Waveguide CWContinuous Wave DCDirect Current DTI Deep Trench Isolation DUT Device under Test **EIRP** Equivalent Isotropically Radiated Power EMElectromagnetic ESD Electrostatic Discharge **ETSI** European Telecommunications Standards Institute FLAFocal Line Array FSPLFree Space Path Loss GaAs Gallium Arsenide GaN Gallium Nitride **GPPG** Ground-Power-Power-Ground GSG Ground-Signal-Ground **HBT** Heterojunction Bipolar Transistor HVHigh Voltage InP Indium Phosphide ISA Irregular Sparse Array **JFOM** Johnson's Figure of Merit

LNA Low Noise Amplifier

LTCC Low Temperature Co-fired Ceramic

LV Low Voltage

MIM Metal-Insulator-Metal

MIMO Multiple Input Multiple Output

ML Microstrip Line mm-Wave Millimeter Wave

OSP Organic Solderability Preservative

P1dB 1-dB Compression Point

PA Power Amplifier

PAE Power Added Efficiency

PCB Printed Circuit Board

QAM Quadrature Amplitude Modulation

RF Radio Frequency

RFIC Radio Frequency Integrated Circuit

RMS Root Mean Square

Rx Receive

SiGe Silicon-Germanium

SIW Substrate Integrated Waveguide

SNR Signal to Noise Ratio

SOA Safe Operating Area

SoC System-on-Chip

SOLT Short-Open-Load-Through

TE Transverse Electric

TEM Transverse Electromagnetic

TL Transmission Line TRL Thru-Reflect-Line

Tx Transmit

VNA Vector Network Analyzer

WG Waveguide

## Contents

| A  | bstra       | ct      |                                                            | i    |

|----|-------------|---------|------------------------------------------------------------|------|

| Pı | refac       | e       |                                                            | iii  |

| A  | ckno        | wledgn  | nents                                                      | v    |

| Li | ${f st}$ of | Public  | cations                                                    | vii  |

| A  | crony       | yms     |                                                            | xi   |

| C  | onter       | nts     |                                                            | xiii |

| Ι  | Int         | trodu   | ctory Chapters                                             |      |

| 1  | Int         | roduct  | zion                                                       | 1    |

|    | 1.1         | Active  | Antenna Array Challenges at mm-Wave Frequencies            | 2    |

|    |             | 1.1.1   | Conventional Power Combining                               | 6    |

|    |             | 1.1.2   | Integration with Antenna Elements                          | 9    |

|    | 1.2         | Goal a  | and Objectives                                             | 10   |

| 2  | Spa         | tial Po | ower Combining in Substrate Integrated Waveguide           | 13   |

|    | 2.1         | Spatia  | l Power Combining Techniques                               | 13   |

|    | 2.2         | Substr  | ate Integrated Waveguide                                   | 15   |

|    |             | 2.2.1   | Fundamental Characteristics                                | 16   |

|    |             | 2.2.2   | Integration with Active Components                         | 18   |

|    |             | 2.2.3   | Practical Implementation                                   | 19   |

|    | 2.3         | Transi  | tion between a Coupled Microstrip Line Array and Substrate |      |

|    |             | Integr  | ated Waveguide                                             | 21   |

|    |             | 2.3.1   | Scalability Bounds                                         | 22   |

#### Contents

|    |          | 2.3.2            | Numerical Validation                                          | 23       |

|----|----------|------------------|---------------------------------------------------------------|----------|

|    |          | 2.3.3            | Isolation Enhancement Technique                               | 26       |

|    |          | 2.3.4            | Experimental Demonstration                                    | 29       |

|    | 2.4      | Conclu           | asion                                                         | 32       |

| 3  | Spa      | tial Po          | ower-Combining Module                                         | 33       |

|    | 3.1      | Design           | Description                                                   | 33       |

|    | 3.2      |                  | al Effects of Coupled Power Amplifiers                        | 35       |

|    | 3.3      | Experi           | imental Validation                                            | 38       |

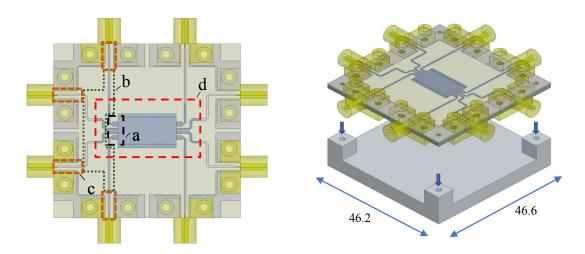

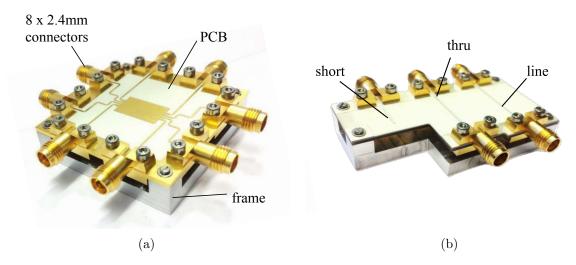

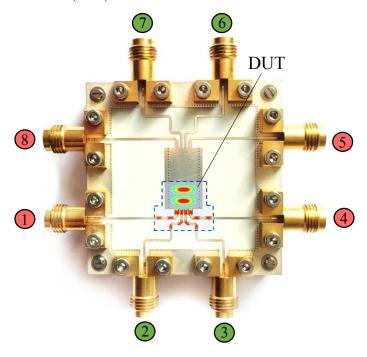

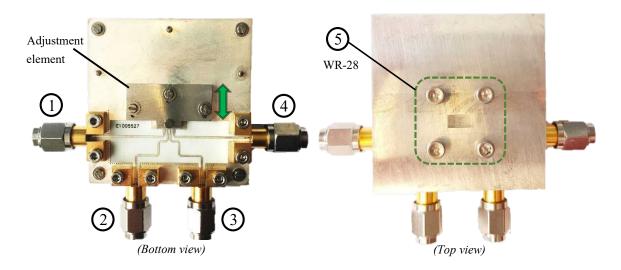

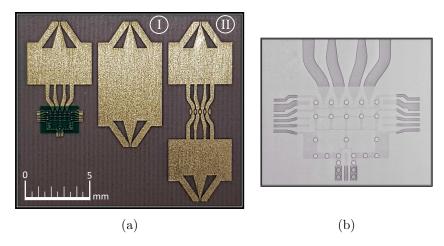

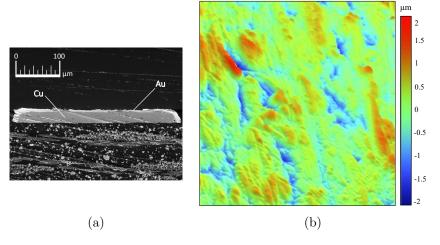

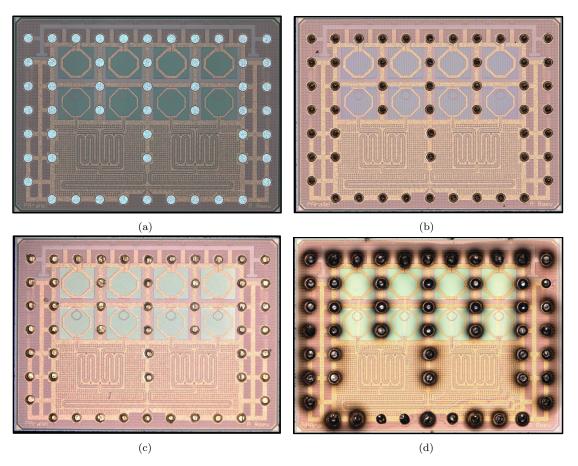

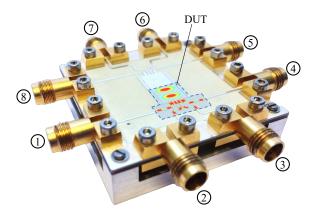

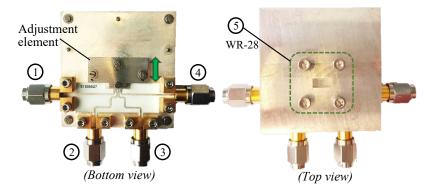

|    |          | 3.3.1            | Fabricated Prototype                                          | 38       |

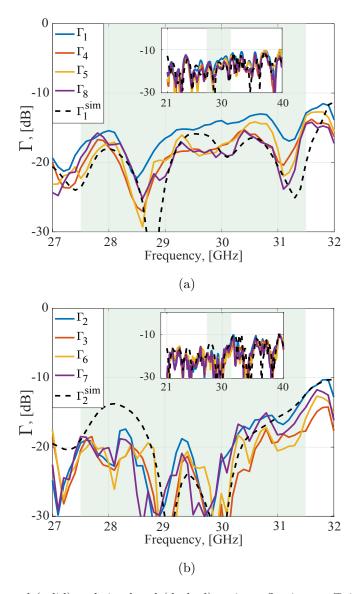

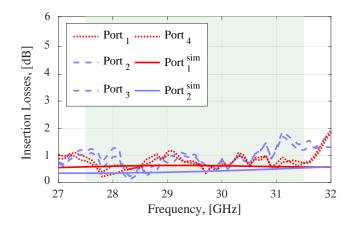

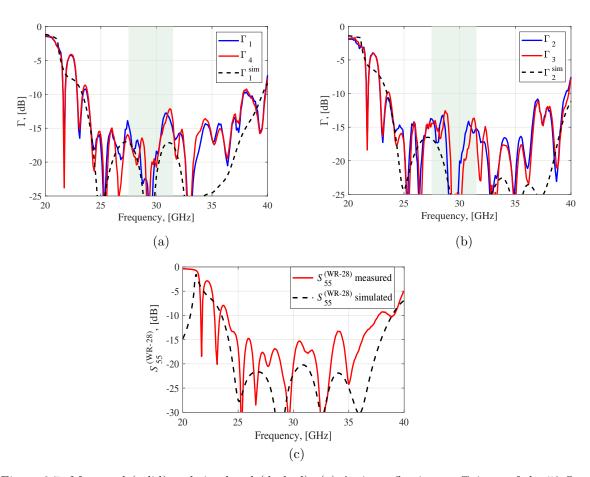

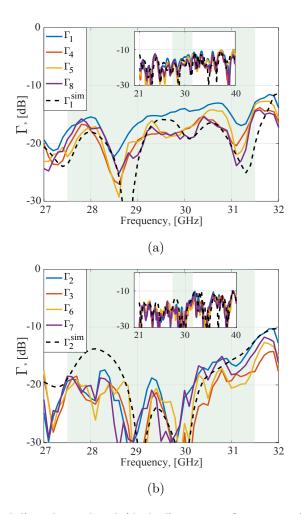

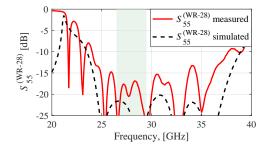

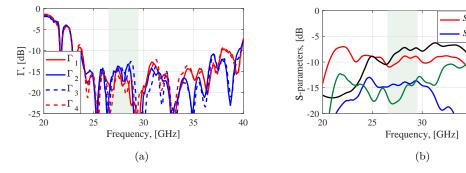

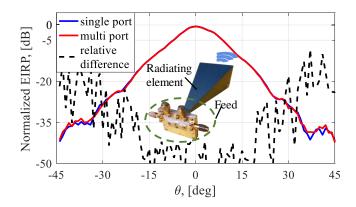

|    |          | 3.3.2            | Measurement Results                                           | 39       |

|    | 3.4      | Summ             | ary                                                           | 43       |

| 4  | Wa       | tt-Leve          | el mm-Wave SiGe Power Amplifier                               | 45       |

|    | 4.1      | Power            | Amplifier Architecture                                        | 46       |

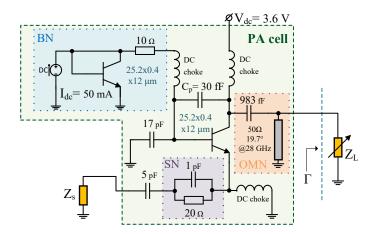

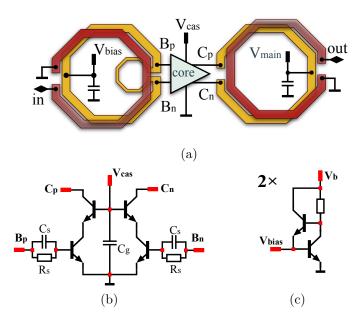

|    | 4.2      | Power            | Amplifier Cell                                                | 47       |

|    |          | 4.2.1            | Overall Design Description                                    | 47       |

|    |          | 4.2.2            | Active Circuitry                                              | 50       |

|    |          | 4.2.3            | Passive Circuitry                                             | 52       |

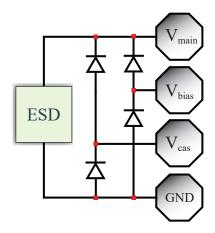

|    |          | 4.2.4            | ESD Protection Circuit                                        | 55       |

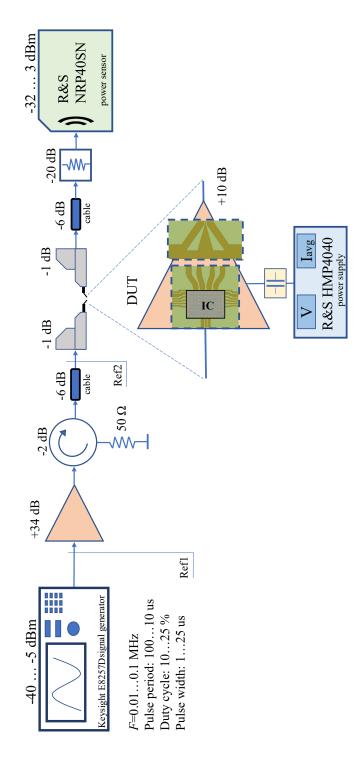

|    |          | 4.2.5            | Experimental Setup                                            | 56       |

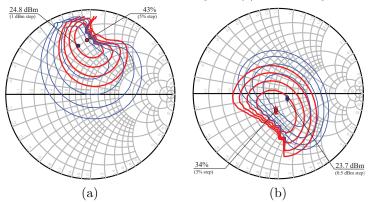

|    |          | 4.2.6            | Measurement Results                                           | 59       |

|    |          | 4.2.7            | Summary                                                       | 63       |

|    | 4.3      | Combi            | ned Power Amplifier                                           | 65       |

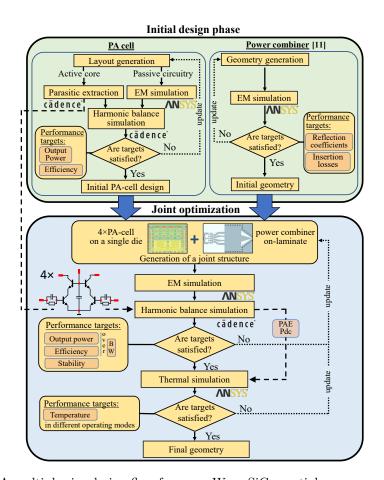

|    |          | 4.3.1            | Multiphysics Design Flow                                      | 65       |

|    |          | 4.3.2            | Fabrication and Assembly Considerations                       | 70       |

|    |          | 4.3.3            | Experimental Setup                                            | 74       |

|    |          | 4.3.4            | Performance Evaluation                                        | 77       |

|    | 4.4      | Summ             | ary                                                           | 83       |

| 5  | Cor      | clusio           | ns                                                            | 89       |

|    | 5.1      | Summ             | ary and Achievements                                          | 89       |

|    | 5.2      | Future           | e Perspectives                                                | 91       |

|    | -        |                  | l D                                                           |          |

| II | 11       | ıclude           | ed Papers                                                     |          |

| Pa | -        |                  | ide-Band Spatially Distributed $TE_{10}$ Substrate Integrated |          |

|    |          | veguido<br>ncies | e Transition for High-Power Generation at mm-Wave Fre-        | 13       |

|    | que<br>1 |                  |                                                               | 13<br>13 |

|    | 2        |                  |                                                               | 114      |

| 3             | Numerical Results                                             | 114        |

|---------------|---------------------------------------------------------------|------------|

| 4             | Conclusions                                                   | 116        |

| 5             | Acknowledgment                                                | 117        |

| Re            | eferences                                                     | 117        |

| Pape          | er B Efficient Millimeter-Wave High Power Generation with Spa | <b>ì</b> - |

| tia           | al Power-Combined Feeding Element                             | 121        |

| 1             | Introduction                                                  | 121        |

| 2             | Numerical Results                                             |            |

| 3             | Design of the Prototype                                       | 127        |

| 4             | Conclusion                                                    | 128        |

| 5             | Acknowledgment                                                | 128        |

| Re            | eferences                                                     | 128        |

| -             | r C Wideband mm-Wave Transition between a Coupled Microst     | -          |

|               | ne Array and SIW for High Power Generation MMICs              | 133        |

| 1             | Introduction                                                  | 133        |

| 2             | Numerical Results                                             | 135        |

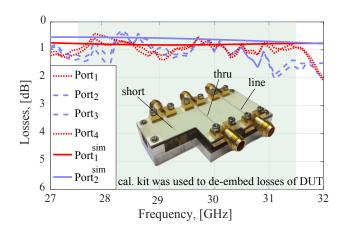

| 3             | Prototype and Measurement Results                             | 136        |

| $\frac{4}{-}$ | Conclusions                                                   | 138        |

| Re            | eferences                                                     | 139        |

| Pape          | v 1                                                           |            |

|               | eneration MMICs – Scalability Bounds                          | 143        |

| 1             | Introduction                                                  | 143        |

| 2             | Scalability Study                                             |            |

| 3             | Numerical Results                                             | 145        |

| Re            | eferences                                                     | 147        |

| -             | er E High Power mm-Wave Spatial Power Combiner Employin       | _          |

|               | n-Chip Isolation Resistors                                    |            |

| 1             | Introduction                                                  | 151        |

| 2             | Concept and Operation Principle                               | 152        |

| 3             | Numerical Validation Results                                  | 153        |

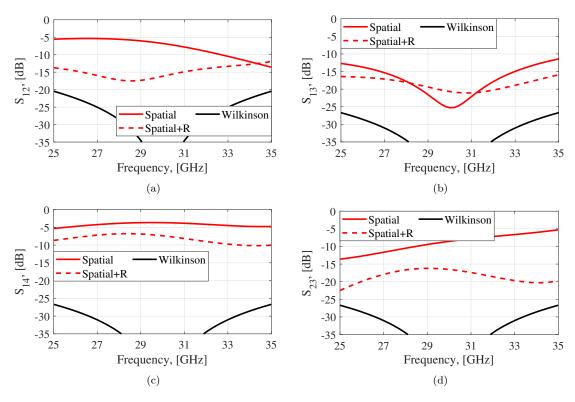

|               | 3.1 Scattering Parameters                                     | 154        |

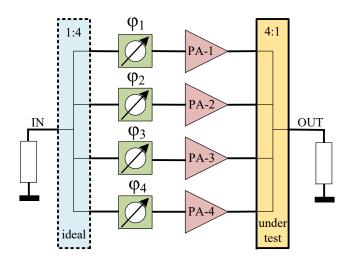

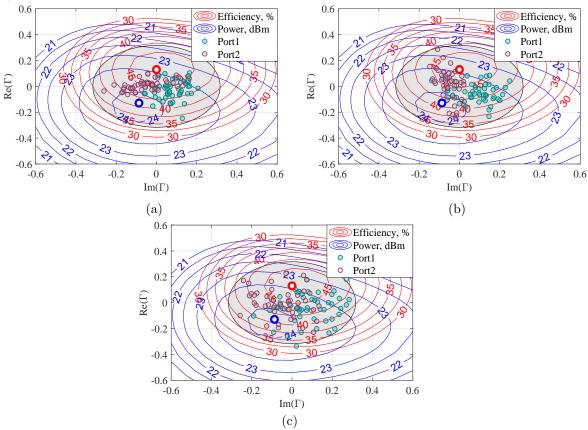

|               | 3.2 Total Performance in Presence of PAs                      | 155        |

| 4             | Conclusion                                                    | 158        |

| Re            | eferences                                                     | 158        |

| Pape          | 1                                                             |            |

|               | r mm-Wave High-Power Amplifiers                               | 163        |

| 1             | Introduction                                                  | 163        |

#### Contents

| 2      | Design of the Power Combining Module Including the Effects of PAs . | 165 |

|--------|---------------------------------------------------------------------|-----|

| 3      | Measurement Results                                                 | 173 |

|        | 3.1 Input Impedance Matching                                        | 173 |

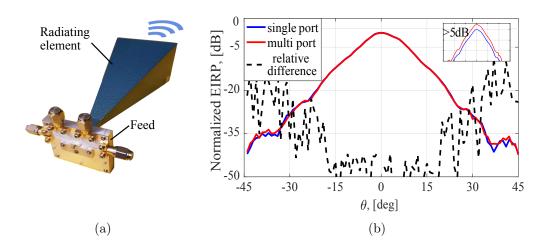

|        | 3.2 Radiation Pattern                                               | 175 |

|        | 3.3 Power Combining                                                 | 175 |

| 4      | Conclusion                                                          | 178 |

| Ref    | erences                                                             | 178 |

| Paper  | G A wideband mm-Wave Watt-level spatial power-combined              | d   |

| pov    | wer amplifier with 26% PAE in SiGe BiCMOS technology                | 185 |

| 1      | Introduction                                                        | 185 |

| 2      | Design Flow                                                         | 187 |

| 3      | Power Amplifier Unit Cell                                           | 188 |

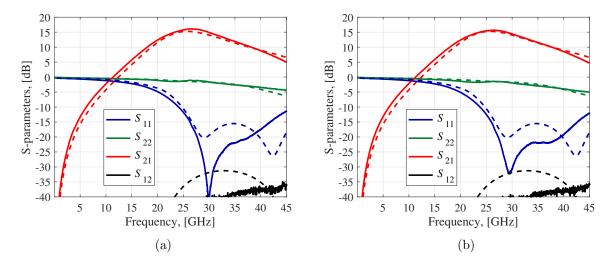

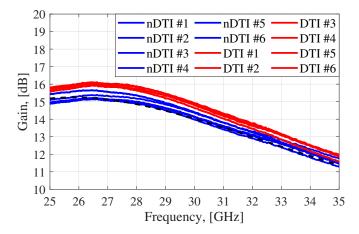

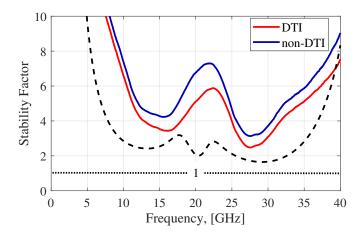

|        | 3.1 Circuit Design                                                  | 189 |

|        | 3.2 Measurement Results                                             | 191 |

| 4      | Combined Power Amplifier                                            | 192 |

|        | 4.1 Description of the Architecture                                 | 192 |

|        | 4.2 Joint EM-Circuit-Thermal Optimization                           | 193 |

|        | 4.3 Spatial Power Combiner                                          | 196 |

|        | 4.4 Measurement Results of the Combined Power Amplifier             | 199 |

| 5      | Discussion                                                          | 203 |

| 6      | Conclusion                                                          | 204 |

| Ref    | erences                                                             | 205 |

| Paper  | g                                                                   |     |

|        | ansmission Line Arrangement                                         | 211 |

| 1      | Technical Field                                                     | 211 |

| 2      | Background                                                          | 211 |

| 3      | Summary                                                             | 212 |

| 4      | Brief Description of the Drawings                                   | 213 |

| 5      | Detailed Description                                                | 213 |

| 6      | Claims                                                              | 217 |

| Ref    | erences                                                             | 218 |

| Currio | culum Vitae                                                         | 219 |

# Part I Introductory Chapters

Chapter 1

## Introduction

Historically, the millimeter wave (mm-Wave) spectrum has been mostly allocated for radar applications, however, the increasing demand in high speed and low latency wireless data channels has led to the exploitation of the possibilities of launching communication services at Ka-band (26–40 GHz) and beyond [1]. The achievable data rate over a wireless channel is mostly determined by four factors: bandwidth, signal-to-noise ratio (SNR), modulation scheme, and whether spatially separated data paths are exploited. These fundamental relations are expressed in the Shannon-Hartley theorem [2]:

$$C_{\text{max}} = N_{\text{p}} B \log_2(1 + \text{SNR}).$$

(1.1)

This theorem establishes the maximum data rate  $(C_{\text{max}})$  at which error-free information can be transmitted over the channel with a certain bandwidth (B) and SNR. Factor  $N_{\rm p}$  represents the number of independent data paths. In order to compensate for the limited channel bandwidth of the third generation (3G) and its successor – the fourth generation (4G) communication systems – the wireless industry has started to explore more advanced methods and new technologies. In particular, the multipleinput multiple-output (MIMO) technique allows us to increase the data rate of a wireless link using multiple transmitting and receiving antennas to exploit multipath effects of the channel efficiently [3]. The performance of such MIMO systems is critically dependent on the availability of uncorrelated paths. In practice, for a limited array antenna area, continuous increase in the number of antennas and, hence, spatial channels, does not necessarily lead to significantly higher data rates. This is the consequence of the spatial correlation between multiple paths as well as increased antenna mutual coupling effects [4]. Furthermore, improvement of SNR in 3G/4G communication systems by increased transmitter output power is restricted according to applicable electromagnetic (EM) fields exposure limits [5]. Therefore, to further increase the data rate, a wider frequency bandwidth is required [6]. However, such a wide bandwidth is not available at existing sub-6 GHz communication bands.

As a result, mm-Waves is a key enabler for high data rate fifth-generation (5G)

communication networks by providing a wide frequency spectrum [7]. Despite the obvious advantage of a large available spectrum, using mm-Wave bands are accompanied by many technological challenges. Mainly, this is due to the increased propagation and material loss, as well as limitations of existing semiconductor processes [8].

## 1.1 Active Antenna Array Challenges at mm-Wave Frequencies

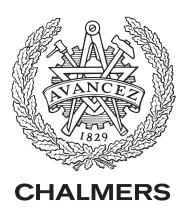

In order to indicate the main technological challenges in wireless networks at mm-Wave frequencies and to explore possible solutions, a basic link budget analysis is essential. For this purpose a downlink scenario assuming a base station with 1000 m reach in a suburban deployment at 28 GHz is examined. The block diagram of a wireless link system example is shown in Figure 1.1 [9]. The chosen 100 MHz

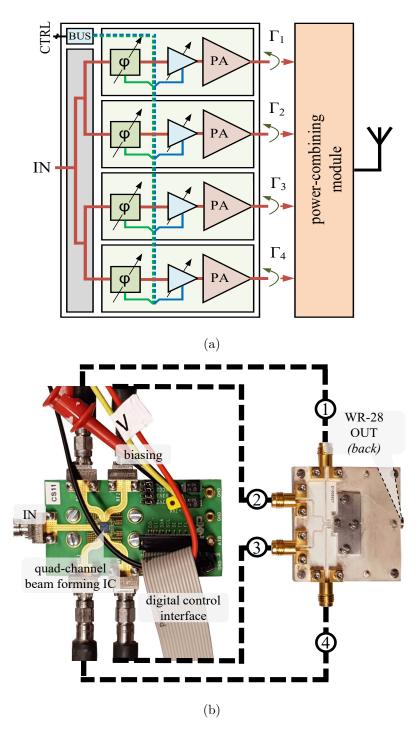

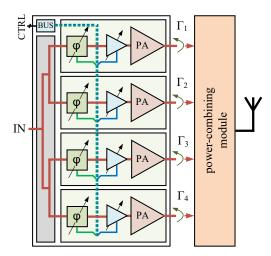

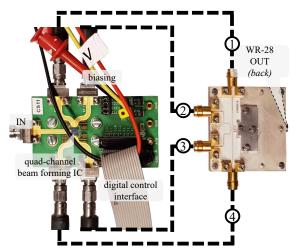

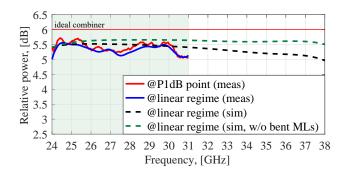

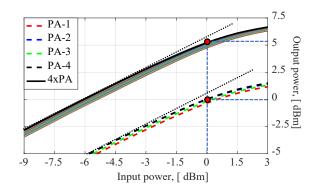

Figure 1.1: Block diagram of a mm-Wave wireless link system employing N-channel beamforming RFIC in downlink scenario.

bandwidth results in -84 dBm receiver sensitivity [10, 11]. The required SNR for quadrature amplitude modulation with 16 points in the grid (16-QAM) is 8 dB [10,12]. The receiver antenna gain is 17 dB. The required total equivalent isotropic radiated power (EIRP) can be determined as:

$$EIRP_{dBm} = Receiver Sensitivity + SNR - Rx Antenna Gain + Path Loss.$$

(1.2)

The path loss in the idealistic case (lossless medium) might be represented by free-space path loss (FSPL), caused by the spherical expansion of the wavefront in free space [13]:

$$FSPL_{dB} = 20 \log_{10} \left( \frac{\lambda}{4\pi R} \right), \tag{1.3}$$

where  $\lambda$  is the wavelength in free space, and R is the distance between the transmitting and the receiving antennas. The shift from conventional 3G/4G operation bands

towards mm-Wave implies more than  $10 \times$  wavelength reduction, which leads to more than 20 dB higher FSPL. Moreover, absorption losses in different mediums are increased at mm-Wave frequencies. Rain, fog, and water vapor exacerbate this loss [14]. In the present scenario, the estimated path loss is in the order of 133-156 dB [10,15]. Given the calculations above, the required total EIRP for the transmit side is between 40 and 63 dBm (see Table 1.1) [16].

| Parameter                  | Assumptions        | Value      |

|----------------------------|--------------------|------------|

| Receiver Sensitivity Limit | $100~\mathrm{MHz}$ | -84 dBm    |

| Required SNR               | 16-QAM             | 8 dB       |

| Total Array Gain           | 16 Elements        | 17 dB      |

| Estimated Path Loss        | 1000 m             | 133–156 dB |

| Required Transmitted EIRP  | -                  | 40–63 dBm  |

Table 1.1: Downlink link budget at 28 GHz

The next question is how to realize the required EIRP by the transmitter? From the transmitter perspective, EIRP is defined as:

$$EIRP_{dBm} = P_t + G_A - L, \tag{1.4}$$

where  $P_{\rm t}$  is the RF power supplied to transmitting antenna in dBm,  $G_{\rm A}$  is the antenna gain in a given direction relative to an isotropic antenna in dBi, the term L represents losses at the interconnections and feeding lines in dB. In order to realize the required EIRP in specific directions corresponding to the positions of users, mm-Wave transmitters exploit a phased-array architecture [17]. Figure 1.1 shows an RF integrated circuit (RFIC) containing N independent RF braches each of which is interfaced with the corresponding antenna element. In the transmit mode, each RF branch is formed by a tunable phase shifter and power amplifier (PA). The beam steering functionality is realized by setting corresponding phase coefficients in each RF branch.

The gain of an antenna array  $G_A$  is produced by its individual element gain  $G_{\rm el}$  and the array gain AG, representing the array configuration effects. There are different promising unconventional antenna array architectures, such as irregular sparse arrays (ISAs) [18,19] and focal line arrays (FLAs) [20,21]. The unconventional array architectures allow for more degrees of freedom in the design, but are not established technologies yet. In the present analysis a conventional uniform array architecture is employed. The array gain of the antenna array with uniformly-spaced identical elements is defined by element spacing d [22]. The individual element gain in an idealistic case is dependent on the effective aperture area  $A_{\rm eff}$  only [22]. The above relations are summarized in (1.5).

$$G_{\rm el} = 10 \log_{10} \left( \frac{4\pi A_{\rm eff}}{\lambda^2} \right)$$

$$G_{\rm A} = G_{\rm el} + {\rm AG} , \text{ where}$$

$${\rm AG} = 10 \log_{10} \left( \frac{2Nd}{\lambda} \right) \Big|_{d < \lambda \ll Nd}$$

$$(1.5)$$

However, to prevent unwanted grating lobes in wide-scan antenna arrays ( $\pm 45^{\circ}$  or larger), element spacing d must not exceed  $\lambda/2$ . Taking that into account, array gain becomes  $AG|_{d=\lambda/2} = 10\log_{10}(N)$ . The half-wavelength spacing also limits the aperture size of antenna elements and, hence, individual gain  $G_{\rm el} \leq 5$  dBi. Increasing the number of antenna elements N requires more PAs. Assuming each individual PA operates at an output power of  $P_{\rm out}$ , the total power accepted by the transmitting antenna can be expressed as:

$$P_{\rm t} = P_{\rm out} + 10\log_{10}(N). \tag{1.6}$$

Therefore, for the assumed scenario the transmitter EIRP can be written as:

$$EIRP_{dBm} = P_{out} - L + G_{el} + 20 \log_{10}(N)$$

, where  $G_{el} \le 5$  dBi. (1.7)

As one can see from Equation 1.7, there are three intuitive ways to improve EIRP:

- 1. Increase the number of antenna elements (N);

- 2. Employ high-power PAs;

- 3. Reduce interconnection losses (L).

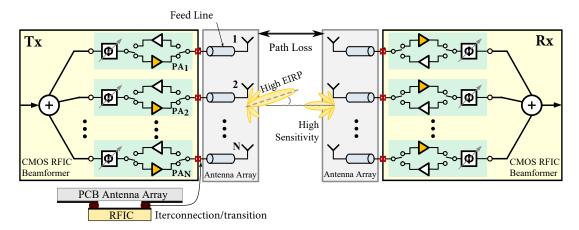

Figure 1.2: EIRP as a function of the number of antenna elements (N) in the uniform array. The set of curves corresponds to different  $P_{\text{out}}$ . The colored regions indicate the typical  $P_{\text{out}}$  at Ka-band for diffrent semiconductor technologies.

Figure 1.2 shows the EIRP as a function of the number of antenna elements for different PA output power levels. At the desired EIRP levels, increasing the individual PA output power by 5 dBm is equivalent to adding 100 extra antenna elements in a large-scale antenna array ( $N \geq 150$ ). The latter is not practical since it occupies more area and requires a lot of additional beamforming branches. Hence, the system becomes more expensive and less reliable.

Therefore, using a high-power PA ( $P_{\rm out} \geq 25\text{--}30~{\rm dBm}$ ) per single antenna element and minimizing interconnection losses between them allows one to efficiently generate the desired EIRP, and hence, to compensate for the increased path loss at higher frequencies. However, existing loss minimization techniques demonstrate a trade-off between their power enhancement and relative bandwidth [23]. In particular, a direct matching approach in [24] obviates the need for a potentially lossy impedance matching network and demonstrates 20% higher output power but offers 5% bandwidth only.

Although the continued growth of new applications drives the semiconductor industry towards more cost-effective solutions for mm-Wave, an efficient generation of high-power is still challenging at these frequencies [25–29]. In order to characterize and compare the performance of semiconductor materials for high-power applications at mm-Wave frequencies, Johnson's figure of merit (JFoM) can be used [30]. It includes the most critical parameters of materials: the charge carrier saturation

| Material | Saturation velocity, $[\times 10^4 \text{ m/s}]$ | Breakdown<br>field, [MV/cm] | JFoM<br>normalized to Si |

|----------|--------------------------------------------------|-----------------------------|--------------------------|

| Si       | 1.0                                              | 0.3                         | 1.0                      |

| GaAs     | 1.5                                              | 0.4                         | 2.7                      |

| InP      | 0.7                                              | 0.5                         | 20                       |

| GaN      | 2.5                                              | 3.3                         | 27                       |

Table 1.2: Properties of the typical semiconductor materials

velocity in the material and the electric breakdown field. The latter directly defines the amount of power, which a semiconductor device could bring to the load. As is clear from Table 1.2, III-V compound semiconductors (GaN, GaAs, InP) can potentially generate more power at mm-Wave frequencies in comparison with silicon (Si) [31–34]. However, their relatively low thermal conductivity (compared to Si) restricts the maximum power density, which results in devices with larger areas. The relatively lower level of integration for III-V compound devices has limited their mainstream use. From a cost perspective, GaAs and GaN technologies are more expensive for high volumes, mainly due to their smaller wafer size.

In cellular communications, where compactness and cost-effectiveness are important, silicon technologies are becoming attractive alternatives [35, 36]. The high integration capability of Si technologies allows designing multi-functional chips con-

taining independent Tx/Rx beamforming branches as well as a digital control interface [37–41]. However, due to the fundamental material properties (See Table 1.2), the generation of 25-30 dBm output powers is very challenging for silicon technologies and requires non-conventional design solutions.

#### 1.1.1 Conventional Power Combining

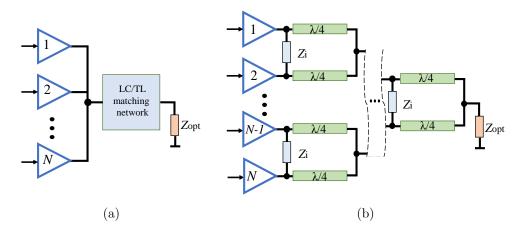

The maximum output power limitation of a single Si transistor might be overcome by combining the power of multiple active devices on each antenna array element [42–46]. Traditionally, on-chip power combining is categorized by the scale of integration. It might be device-level or circuit-level [47].

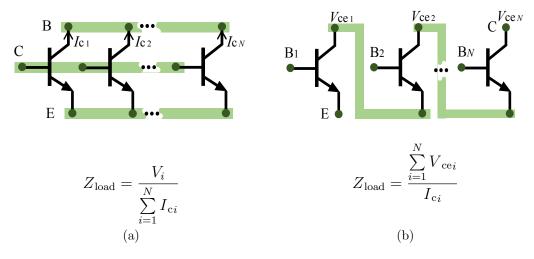

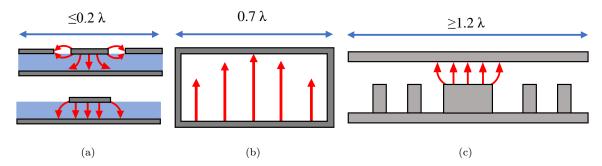

The device-level power combining is based on parallelization or stacking (and sometimes both) identical transistors in a region whose extent is small compared to one wavelength, and is generally limited to the number of devices that can be combined efficiently. Placing multiple transistors in parallel (See Figure 1.3) allows one to increase the output current, but it is also accompanied by a proportional reduction of the output load impedance [48–50]. It means that an additional matching circuit with a high transformation ratio is needed. Stacking multiple transistors leads

Figure 1.3: Device-level power combining: (a) Parallelization; (b) Stacking.

to the output voltage and optimal load impedance increasing. The latter is usually desired since individual high-power devices have intrinsically low optimal impedance. However, in practice, the number of stacked transistors is limited due to the increasing complexity of interconnection topology and difficulty to minimize parasitic effects [51–53]. The device-level power combining is efficient at sub-6 GHz frequencies. At mm-Wave frequencies, spatially distributed effects in the interconnecting and routing lines become significant. This causes the transistors to operate differently from each other, which leads to the reduction of output power, efficiency, and gain. Moreover, when

#### 1.1. ACTIVE ANTENNA ARRAY CHALLENGES AT MM-WAVE FREQUENCIES

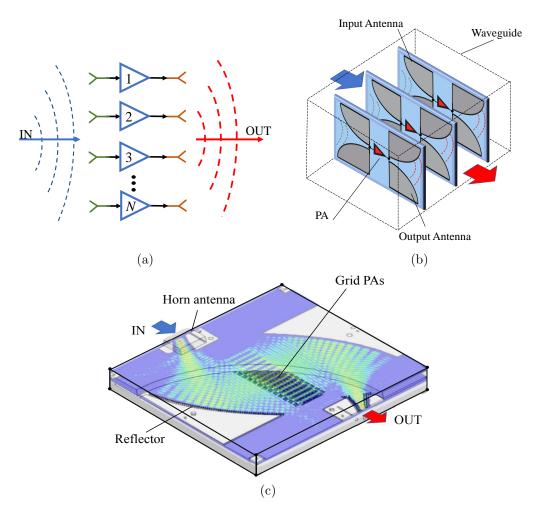

Figure 1.4: Conventional circuit-level power combiners: (a) Non-Isolated current combiner; (b) Wilkinson combiner based on transmission lines.

the devices are closely spaced, mutual thermal coupling between them increases, which might cause a thermal breakdown [54]. Thereby, the number of the combined devices (N) usually does not exceed 5, which corresponds to  $\leq 6.9$  dB relative power increase [49, 51, 52].

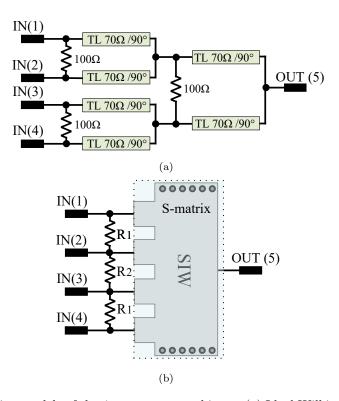

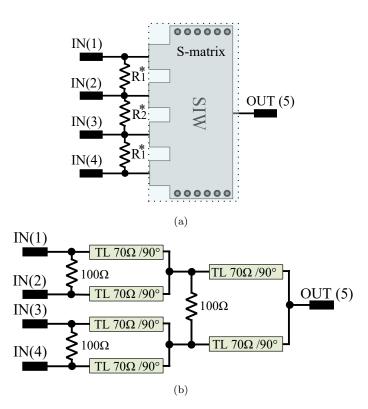

To overcome the above interconnect and thermal issues, circuit-level power combining is based on combining multiple smaller independent PA-cells. Figure 1.4 (a) shows a non-isolated current combiner, where the outputs of the N individual PAcells are simply connected to a single point. This approach is similar to the devicelevel parallelization (Fig. 1.3 (a)) and also requires an additional matching circuit. Increasing the number of interfaced PAs results in the higher impedance transformation ratio, and hence the output matching circuit becomes more complex, especially if a wide bandwidth is required [55]. Wideband operation is usually achieved by using multi-stage matching networks, which intrinsically occupy more areas and have higher losses. Another challenge is the mutual coupling between the combiner input ports, which might negatively affect the individual PA-cell behavior. The latter is addressed in Wilkinson power combiners with isolation load resistors [56–58]. Figure 1.4 (b) shows an example of a planar Wilkinson combiner using traditionally  $\lambda/4$ transmission lines (TLs). The cascade connection of two-way Wilkinson power combiners can provide an N-way combining; however, increasing the number of inputs is accompanied by higher losses in the series-connected  $\lambda/4$  TLs. This fact constrains the relative increase of power after combining, which is expressed as:

Relative Power Increase

$$_{dB} = 10 \log_{10}(N) - L_{\lambda/4} \log_2(N),$$

(1.8)

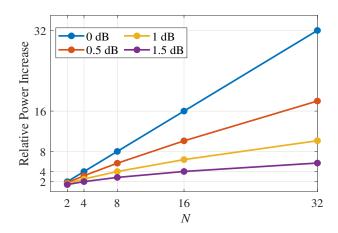

where  $L_{\lambda/4}$  represents incertion losses in a single TL with electrical length  $\lambda/4$ . Figure 1.5 shows the relative increase of output power as a function of the number of interfaced PAs. The set of curves correspond to different insertion losses of the  $\lambda/4$  TLs. In the lossless case (blue line), the output power is proportional to the number

#### CHAPTER 1. INTRODUCTION

Figure 1.5: Relative power increase as a function of number of interconnecting PA-cells (N). The set of curves correspond to different losses of the  $\lambda/4$  TLs.

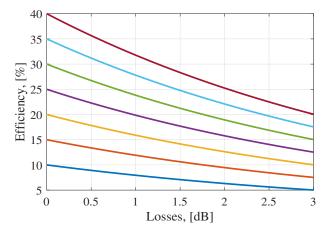

Figure 1.6: Efficiency as a function of insertion losses in the output power combiner. The set of curves corresponds to the efficiency of an individual PA-cell (lossless combining).

of PA-cells. However, in the presence of losses, increasing of the number of PAs does not help to significant increase the output power [59,60].

Besides the maximum output power limitation, the combiner losses cause a significant reduction of the combined PA efficiency, which is a ratio between the output RF power and the total DC power taken from a supply source. This effect is exemplified in Figure 1.6, showing the combined PA efficiency as a function of insertion losses in the output power combiner. In the case of an ideal (lossless) power combiner, the efficiency of the combined PA is equal to the efficiency of its individual PA-cell, which corresponds to the points on the y-axis. Increasing the combiner insertion losses leads to the output power reduction while the DC power consumption remains the same. As a result, a significant efficiency degradation is observed, especially for the PA-cell with initially high efficiency (dark red curve). For example, the insertion losses of

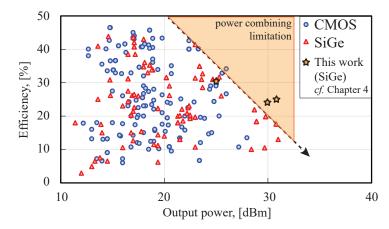

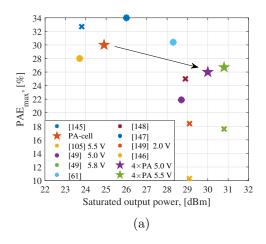

Figure 1.7: Performance of the reported state-of-the-art Si-based PAs at Ka/V-band: efficiency versus saturated output power [61].

2 dB lead to the efficiency drop from 40% to 25% for the PA-cell with initially high efficiency, whereas the PA-cell with initially low efficiency (light red curve) demonstrates the efficiency reduction from 15% to 10% only. Since conventional circuit-level on-chip power combiners are intrinsically lossy due to the Si substrate [60,62,63], the exiting combined PAs demonstrate a trade-off between the output power and efficiency. Figure 1.7 shows the performance of the reported state-of-the-art Si-based PAs at Ka/V-band in the efficiency-power coordinate plane. Although the reported PAs with output power less than 24 dBm demonstrate relatively high efficiency, the Watt-level PAs have very limited efficiency ( $\leq 18\%$ ) caused by the lossy power combiners. Therefore, new power-combing solutions and PA architectures are required for facilitating efficient high-power generation at mm-Wave frequencies.

#### 1.1.2 Integration with Antenna Elements

Besides the employment of high-power PAs, reaching the desired EIRP level requires minimization of interconnection losses between active devices and antenna elements. In the perspective of integration with active components, planar TL structures such as microstrip line (ML), coplanar waveguide (CPW), and stripline offer a compact and cost-efficient solution (See Figure 1.8 (a)). However, these TLs suffer from high dielectric and ohmic losses as well as radiation leakage, especially at mm-Wave frequencies [64].

Moreover, parasitic field radiation by bent planar TLs might cause undesired coupling between adjacent RF branches, and hence, affect the performance of active components [65]. In contrast, conventional hollow metal waveguides (WGs) have intrinsically low insertion losses and perfect isolation, however it is difficult to combine with active components (See Figure 1.8 (b)). It also requires a good electrical contact between metal blocks. The latter might be partly overcome by using the gap waveg-

Figure 1.8: Transmission lines and fundamental E-field mode distribution: (a) CPW and ML planar TLs; (b) Hollow metal rectangular WG; (c) Ridge gap WG.

uide technology [66], but it has limited application in dense beam-steering antenna arrays since it requires more space in order to realize artificial magnetic conductors as shown in Figure 1.8 (c).

Despite the huge amount of challenges, mm-Wave offers a wide variety of integration options in comparison with conventional sub-6 GHz bands. At mm-Wave frequencies the size of antennas becomes compatible with RFICs size. This fact allows to make an antenna as a part of a package or even integrate it into an RFIC back-end [67–69].

#### 1.2 Goal and Objectives

In view of the aforementioned motivation, this work aims to develop and experimentally demonstrate new power combining and integration solutions for efficient Watt-level mm-Wave transmitters in Si-based technologies. Several objectives are established to achieve this aim:

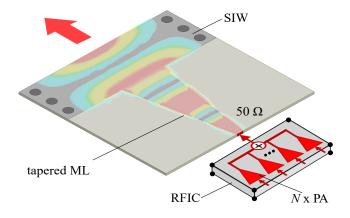

Objective 1. Develop a new power combining architecture eliminating the need for the intermediate and potentially lossy on-chip combiners by directly interfacing an array of PAs to a single radiation element;

- Investigate architecture constraints and scalability bounds;

- Analyze the critical effects of interconnected PAs in different operating regimes (linear and non-linear regimes);

- Explore possibilities of integration with existing antenna elements, in particular elements in SIW technology.

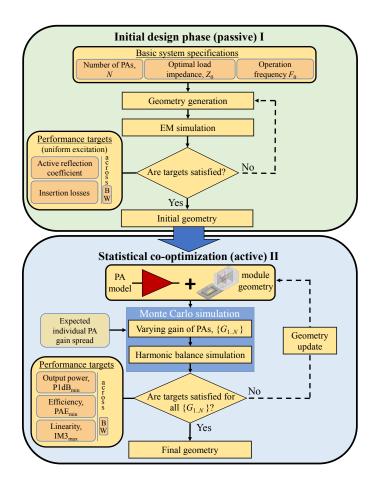

**Objective 2.** Design a combined Watt-level PA using a new architecture, demonstrating both high output power and high efficiency over a wide frequency bandwidth. The focus of the design is on an advanced high-speed SiGe process from NXP Semiconductors, which is one of the main industrial partners of the Silika project [70].

- Design a custom PA-cell suitable for the new PA architecture;

- Develop a new EM-circuit-thermal design flow capable of taking account of various multiphysics effects occurring in the joint structure containing multiple PA-cells;

- Develop a combined PA prototype to evaluate its performance as well as to explore the architecture sensitivity to assembly and fabrication imperfections.

Throughout this work, the main performance targets are high output power and energy efficiency in combination with a wide operation bandwidth and a compact size for potential applications in dense antenna arrays with electrically small inter-element distance.

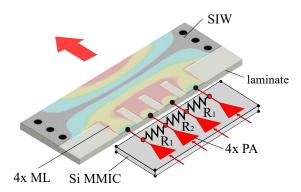

# Spatial Power Combining in Substrate Integrated Waveguide

This chapter outlines the principle of operation and the design methodology of the proposed compact spatial power combining transition between an array of amplifiers and a single substrate integrated waveguide (SIW). This concept is validated through measurements of the fabricated passive back-to-back transition.

# 2.1 Spatial Power Combining Techniques

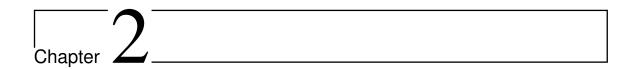

As an alternative to the conventional device-level and circuit-level power combining, quasi-optical or spatial power combining techniques are becoming more and more attractive as the interest in mm-Wave frequency applications is growing. [47, 59, 71–74]. Spatial power combining is an essential part of quasi-optical amplifiers, as for example shown in Figure 2.1 (a), where the spatially distributed electromagnetic wave is coupled to the space-fed array of PAs, amplified, and transmitted directly to the radiating element.

Spatial power combiners have a number of advantages over conventional circuitlevel solutions [47]:

- *Intrinsicly low insertion losses*, which do not increase significantly when increasing the number of combined PAs.

- High maximum achievable output power (as a result of the constant insertion losses). The maximum number of interfaced PAs is constrained by the physical limitations of the architecture only.

- Direct integration with an antenna element. A spatially distributed output wave can be directly fed to the radiation element without using any intermediate transitions that are potentially bulky and lossy.

#### CHAPTER 2. SPATIAL POWER COMBINING IN SUBSTRATE INTEGRATED...

Figure 2.1: Spatial power combining: (a) Quasi-optical beam amplifier concept; (b) Fundamental WG mode amplification using insert longitudinal active trays [75,76]; (c) Spatial power combining in gap WG technology [71].

In practice, spatial power combiners are usually realized inside hollow metal WGs [74–76], as shown in Figure 2.1 (b). The coming waves are sampled by an array of receiving probe antennas, amplified by multiple PAs, and radiated into a WG by an array of output antennas. The PAs and antenna probes can be placed on multiple planar longitudenal trays inside the WG. This arrangement allows us to accommodate broadband traveling-wave antennas and improve performance by using multi-stage active components placed along the direction of propagation. Nevertheless, this structure also has technological and implementation problems including complex packaging for performing high isolation between the inputs and outputs of active components and high sensitivity to assembling tolerances. The latter is partly addressed by a spatial power combiner packaged in the gap WG technology, where a parallel-plate WG mode can be potentially amplified by a grid of PAs (See Figure 2.1 (c)). However, in order to create the distributed WG mode, a bulky

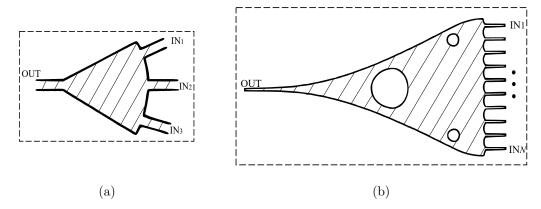

Figure 2.2: Planar spatial power dividers/combiners: (a) Sectorial 1:3 power divider [77]; (b) Tapered microstrip power divider [78].

parallel-plate reflector illuminated by a (horn) antenna is required. The latter limits applications of such combiners in dense antenna arrays with electrically small interelement distance. In addition, despite a potentially high scalability of the structure, the edge PAs cannot be efficiently utilized due to the tapered field distribution [71].

Planar spatial power combiners are more suitable for the integration with active components since a combiner and amplifier modules can be placed on the same substrate. However, the existing solutions of planar dividers/combiners are based on the generation of a distributed quasi-TEM mode in over-sized MLs [79]. Over-sized MLs have intrinsically low impedance, which is challenging for their direct integration with conventional planar antennas. As a consequence, an impedance transformer formed by a long tapered ML section is an essential part of such combiners. Figure 2.2 (a) shows a sectorial power divider as an example [77]. Besides the lossy tapered ML section, an additional drawback of this solution is that the input ports are located on an arc to ensure that the input signals combined constructively. The latter has been addressed in [78], where etched holes in the middle of the conductor pattern are used to equalize the signal path lengths from the input port to the output port, as shown in Figure 2.2 (b). However, this structure is long and has a narrow-band performance.

# 2.2 Substrate Integrated Waveguide

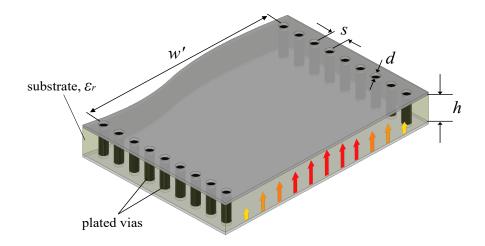

Substrate integrated waveguide (SIW) technology plays an important role in the realization of active antenna arrays at mm-Wave frequencies. It combines functionalities and performance of conventional WGs as well as supports an efficient integration with active components due to its compact and planar structure. SIW is a particular case of a conventional rectangular metal WG shrunk in height that is embedded into a printed circuit board (PCB), as shown in Figure 2.3. The top and bottom metal

#### Chapter 2. Spatial Power Combining in Substrate Integrated...

Figure 2.3: Substrate integrated waveguide (SIW) and its fundamental  $TE_{10}$  mode E-field distribution.

walls are directly represented by two PCB metal layers, whereas side walls are formed by rows of plated vias between the corresponding metal layers [80].

### 2.2.1 Fundamental Characteristics

Due to the same topology, SIWs are similar to the conventional rectangular WGs in terms of their propagation and dispersion characteristics [81]. For a rectangular WG, the longitudinal wave vector component  $(k_z)$  of arbitrary  $TE_{mn}$  mode is given by:

$$k_z = \sqrt{k^2 - \left(\frac{m\pi}{w}\right)^2 - \left(\frac{n\pi}{h}\right)^2},\tag{2.1}$$

where w is the WG width; h is the WG height;  $k = 2\pi/\lambda$ ;  $n, m \in \mathbb{N}_0$ . Each WG mode is mainly characterized by its cut-off frequency; it is the lowest frequency for which a mode will propagate. The WG cut-off frequency corresponds to  $k_z = 0$ . Therefore, the cut-off frequency for an arbitrary  $TE_{mn}$  mode can be defined as:

$$f_{c\ mn} = \frac{c}{2\pi\sqrt{\varepsilon_r}}\sqrt{\left(\frac{m\pi}{w}\right)^2 + \left(\frac{n\pi}{h}\right)^2},\tag{2.2}$$

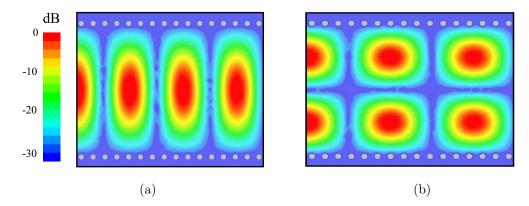

where  $\varepsilon_r$  is the relative permittivity of the medium inside the WG. Since the height of the SIW (h) is very small, the  $\text{TE}_{mn}$  modes with  $n \geq 1$  propagate at extremely high frequencies only and usually are not taken into consideration. As one can see, for any  $\text{TE}_{m0}$  mode the cut-off frequency is defined by the WG width (w) only. Therefore, SIW and conventional waveguide with the same electrical width have identical propagating  $\text{TE}_{m0}$  modes. Figure 2.4 shows the magnitude of the E-field distributions for the  $\text{TE}_{10}$  and  $\text{TE}_{20}$  modes propagating in the SIW with w' = 7.11 mm,

Figure 2.4: Magnitude of the real part of the E-field distribution at 30 GHz: (a)  $TE_{10}$  mode; (b)  $TE_{20}$  mode.

h = 0.254 mm,  $\varepsilon_r = 3.6$ . The fundamental mode of a WG is the mode that has the lowest cut-off frequency, in the presented case, it is the TE<sub>10</sub> mode. The cut-off frequency of TE<sub>10</sub> is defined as:

$$f_{10c} = \frac{c}{2w\sqrt{\varepsilon_r}}. (2.3)$$

However, it is worth noting that in order to take into account a finite size of the vias forming the side walls, the width of the SIW can be expressed as:

$$w = w' - \frac{d^2}{0.95s},\tag{2.4}$$

where w' corresponds to the center-to-center distance between the vias in the transverse direction, d is the diameter of the vias, s is the spacing among them in the longitudinal direction [81].

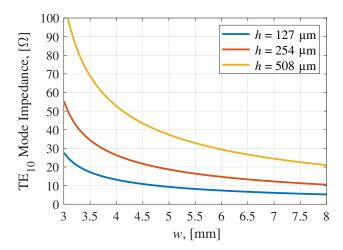

Another important characteristic of the SIW as a TL is its characteristic impedance. The impedance concept plays a fundamental role in transmission theory. There are several definitions of the TL characteristic impedance: voltage-current, power-voltage, and power-current [82]. For the TEM mode all definitions converge to the same characteristic impedance, i.e., one that is solely a function of the geometry and is frequency independent [82,83]. Conversely, the characteristic impedance of the fundamental  $TE_{10}$  mode propagating in the SIW is not uniquely defined and depends on frequency:

$$Z_{\text{TE10}} = k \frac{h}{w} \sqrt{\frac{\mu}{\epsilon}} \left( 1 - \frac{\lambda^2}{4w^2} \right)^{-1/2} \text{ where } \begin{cases} k = \frac{\pi}{2}, \text{ if V-I def.} \\ k = 2, \text{ if P-V def.} \\ k = \frac{\pi^2}{8}, \text{ if P-I def.} \end{cases}$$

(2.5)

According to the voltage-current approach, the characteristic impedance of the SIW is defined as the ratio of the maximum transverse voltage across the top and bottom

Figure 2.5: Characteristic impedance of the SIW as a function of the width. The set of curves corresponds to different substrate thicknesses.

to the total longitudinal current. Whereas the power-voltage and power-current definitions are based on the power propagating through the WG cross-section. However, the definitions differ by a scaling factor (k) only. Figure 2.5 shows the characteristic impedance of the fundamental SIW  $TE_{10}$  mode (V-I def.) as a function of the SIW width (w) for different substrate height values (h). By analogy with a ML, employing a thinner substrate and increasing the SIW width allows reducing the characteristic impedance. The latter conclusion is important for future integration with active components, as it is discussed in the next section.

## 2.2.2 Integration with Active Components

As shown in Figure 2.5, the characteristic impedance of the SIW is in practice significantly lower than the typical  $50-\Omega$  interface impedance of the (PA) chip. Therefore,

Figure 2.6: Classical transition interfacing an array of PAs with a single SIW.

in order to realize optimal impedance matching a transition between the SIW and the ML/CPW should have an impedance-transforming functionality. A straightforward way of doing this is to employ a tapered TL section.

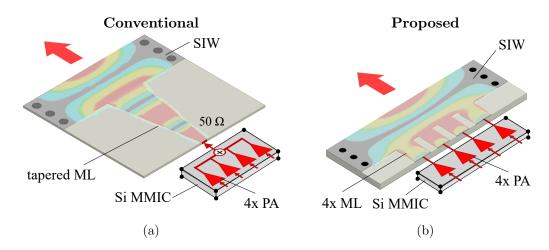

Figure 2.6 exemplifies a conventional ML to SIW transition concept [80, 84]. As illustrated, the chip with multiple PAs delivers high power to the input port of the transition which is then transferred to the SIW. Achieving an optimal impedance match renders the transition long and therefore lossy, especially if a wide frequency bandwidth (BW) is required (See [80, 84], and Table 2.1).

| Reference                     | Frequency,<br>[GHz] | Bandwidth, [%] | Losses (b2b), [dB] | SIW width, $[\lambda]$ |

|-------------------------------|---------------------|----------------|--------------------|------------------------|

| 1×, TE10 [80]                 | 25-31               | 12             | 0.15               | 0.50-0.62              |

| 1×, TE10 [84]                 | 17.5-30             | 50             | 1                  | 0.44-0.76              |

| 2×, TE20 [85]                 | 20-40               | 50             | 2                  | 0.57-1.14              |

| $4\times$ , TE10 [this work]  | 22-36               | 48             | 0.3                | 0.51-0.84              |

| 8×, TE10 [this work]          | 25-36               | 42             | 0.4                | 0.62-1.06              |

| $10\times$ , TE10 [this work] | 25-35               | 30             | 0.4                | 0.65-1.10              |

Table 2.1: Comparison between state-of-the-art solutions and the proposed designs

This fundamental trade-off between BW and power losses limits the applicability of conventional transitions in high-power mm-Wave transmitters. Moreover, as discussed in Section 1.1.1, on-chip power combiners are inherently lossy, and thus, constrain the maximum output power generated by the PAs.

## 2.2.3 Practical Implementation

The SIW technology permits the implementation of conventional rectangular WG components and antennas in a planar form, as well as enables their integration with active devices [86]. SIW-based structures preserve most of the advantages of conventional metallic WGs, such as high quality-factor, self-consistent electrical shielding, and high power-handling capabilities. This fact results in the great acceptance of SIW-based components, including iris and cavity filters [87], directional couplers [88], circulators [89], slot array [90], and leaky-wave antennas.

In terms of practical implementation, SIW-based structures could be fabricated using standard PCB processes or low-temperature co-fired ceramic (LTCC) technology, which makes them lighter and less expensive in comparison with metal WGs. However, the presence of a dielectric inside the structures increases its losses. Dielectric losses can be minimized by using substrates with low loss tangent.

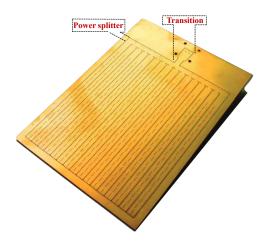

Figure 2.7 shows an example of an SIW-based slot array antenna [90]. It consists of 16 SIW columns each of which has 22 longitudinal slots. The columns are fed through the incorporated 1-to-16 alternating phase power divider. In order to synthesize an

#### Chapter 2. Spatial Power Combining in Substrate Integrated...

Figure 2.7: A K-band  $16\times22$  SIW-based slot array antenna. The radiation pattern shape complies with ETSI class 3, the antenna gain is  $\geq 26$  dBi over 20–24 GHz [90].

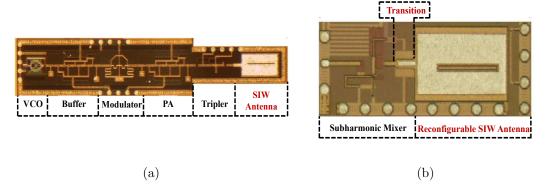

Figure 2.8: A SiGe BiCMOS transmitter/receiver chipset with on-chip SIW antennas at THz frequencies [91]: (a) Integrated transmitter chip; (b) Receiver chip.

antenna array with the desired radiation pattern envelope and gain, a well-established approach for conventional metal WG array antennas has been implemented. The measured antenna gain is  $\geq 26.0$  dBi within the operation band 20–24 GHz, the radiation pattern shape complies with the European Telecommunications Standards Institute (ETSI) class 3 requirements. The radiation efficiency is 74.3 % at the center frequency. The antenna has a simple planar structure allowing its fabrication using a conventional low-cost PCB technology.

At THz frequencies, SIW-based structures become more compact and could be directly implemented on-chip. Figure 2.8 shows a SiGe BiCMOS transmitter/receiver chipset with on-chip SIW-based antennas [91]. Despite the intrinsically high silicon substrate losses, system-on-chip (SoC) architectures become more efficient at these frequencies compared to conventional approaches where discrete antennas are used that suffer from extremely high interconnection losses. THz transmitters are usually based on frequency multiplication using non-linear active components. In the present case, the frequency tripler is directly connected to the antenna, as shown in

Figure 2.8 (a). Therefore, an antenna should have a high-pass filtering functionality to suppress unwanted fundamental and second harmonic signals. An SIW-based antenna is a good candidate to realize the desired functionality due to its intrinsic high-pass filtering property (See Equation (2.1)). Figure 2.8 (b) shows the microphotograph of the THz receiver with the on-chip SIW-based slot antenna. The interconnecting transition between the 50- $\Omega$  subharmonic mixer and the SIW is formed by a conventional tapered ML section. However, this solution has several limitations as discussed in the above subsection.

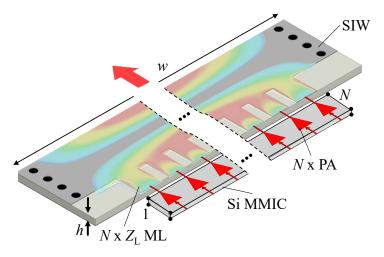

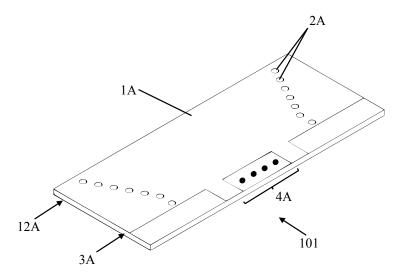

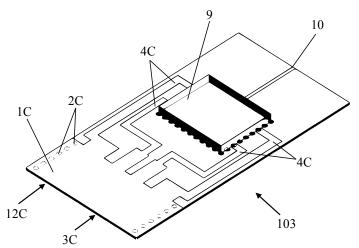

# 2.3 Transition between a Coupled Microstrip Line Array and Substrate Integrated Waveguide

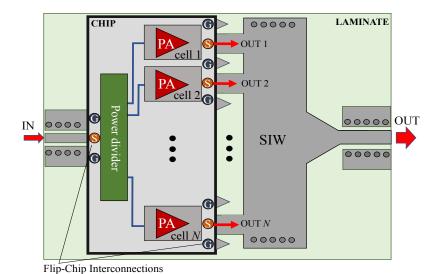

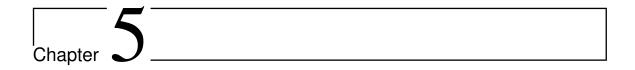

In order to overcome the limitations of the conventional power combining approaches, minimize interconnection losses, and enable direct integration between active components and antenna elements in mm-Wave dense antenna arrays, a new transmitter architecture has been proposed. It is based on a multi-channel transition [Paper A], which directly interfaces an array of PAs to an SIW via multiple spatially distributed MLs, as shown in Figure 2.9. This allows one to directly excite spatially distributed SIW modes with high power. Figure 2.9 visualizes the transfer from the ML mode(s) to the fundamental TE<sub>10</sub> SIW mode. The input ports are coupled through the spatially distributed SIW modes, which causes mutual coupling effects to play a critical role in the proposed transition performance and its design process. In order to take into account mutual coupling effects, the design aproach is based on 'active'

Figure 2.9: Compact transition interfacing N power amplifiers (possibly embedded in a single MMIC) to a single SIW.

impedance matching, a technique known from antenna array network theory. It allows the reflection coefficient of each ML mode to be analyzed in the presence of the ML array excitation and ML array mutual coupling effects, with the ultimate goal to maximize the overall power transfer to the SIW. The active reflection coefficients at the transition input ports are defined as

$$\Gamma_n = \frac{1}{A_n} \sum_{m=1}^N A_m S_{nm} \quad n \in \{1, \dots, N\},$$

(2.6)

where  $S_{nm}$  is the 50- $\Omega$  S-parameter from ML port m to n,  $A_m$  is the complex excitation coefficient of port m. In the case of uniform excitation  $\{A_n\}_{n=1}^N = 1$ .

The proposed transmitter architecture has a number of advantages over the conventional approach as shown in Figure 2.6:

- Output power is no longer limited by lossy on-chip power combiners.

- Spatial power-combining functionality resulting in low insertion losses, which are virtually constant relative to the number of interfaced PAs.

- Wide bandwidth in combination with compact size, since the tapered ML section is not required.

- Generation of the desired higher-order modes (TE<sub>m0</sub>) by applying corresponding excitation coefficients  $\{A_n\}_{n=1}^N$ .

## 2.3.1 Scalability Bounds

In the proposed architecture, the power accepted by the antenna element is proportional to the number of interfaced PAs. Therefore, it is important to investigate the scalability of the multi-channel transition. According to the voltage-current approach, the characteristic impedance of the SIW is defined as a ratio of the maximum transverse voltage across the top and bottom to the total longitudinal current (See Equation (2.5)). Assuming that the total (integrated) SIW longitudinal current is a sum of N ML currents, an impedance matching model could be represented as a parallel connection of N MLs (each with an equal input impedance  $Z_{\rm L}$  in active mode) to a common port. The common port impedance should be approximately equal to the characteristic impedance of the SIW  ${\rm TE}_{10}$  mode ( $Z_{\rm TE10}$ ) to realize a good impedance match:

$$Z_{\text{TE10}} \approx Z_{\text{L}}/N.$$

(2.7)

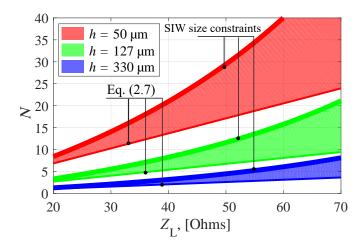

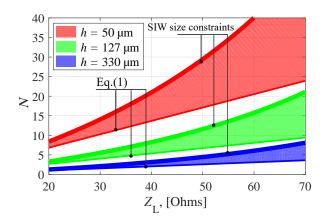

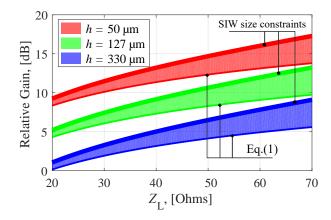

Thus, increasing the number of channels demands decreasing the SIW characteristic impedance  $(Z_{\text{TE}10})$ . This could be done by increasing the width (w) or decreasing the height (h) (See Equation (2.5)). Figure 2.10 shows the estimated number of connected PAs (N) as a function of the ML impedance for different substrate thickness

Figure 2.10: Estimated number of the connected PAs as a function of their optimal impedance for different substrate height values h. Results correspond to a single mode SIW at Ka-band.

values (h). The upper bound of the filled areas corresponds to the maximum number of channels, geometrically limited by the SIW width (the spacing between the lines is assumed to be equal to the line width). The lower bounds are set by the optimal impedance matching criteria. As one can see, employment of a thin substrate and high ML impedance channels allow for interfacing more amplifiers to a single SIW, and hence significantly increase the output power as compared to a single channel transition (See Figure 2.6).

For example, employing a substrate with  $h=50~\mu m$  allows to interface up to  $N=30~\mathrm{PAs}$  with  $50\text{-}\Omega$  optimal load impedance into a single mode SIW at Ka-band. In an ideal case, it results in 14.7 dB relative power increase. A small substrate thickness of the proposed solution enables its future in-package and on-chip realization.

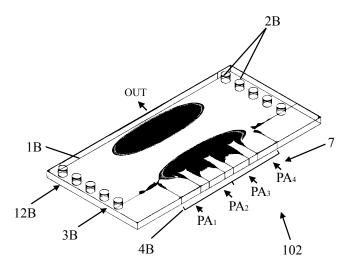

### 2.3.2 Numerical Validation

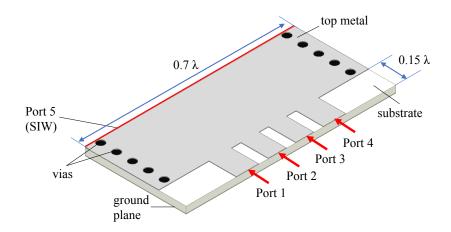

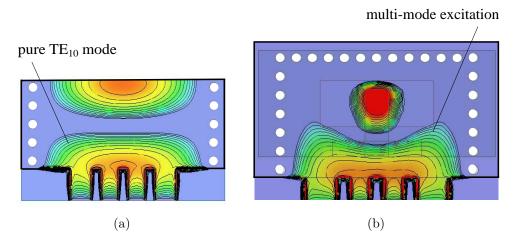

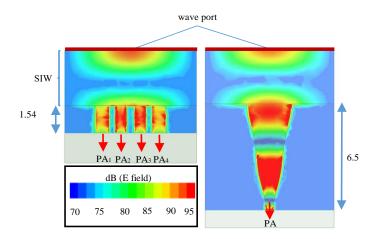

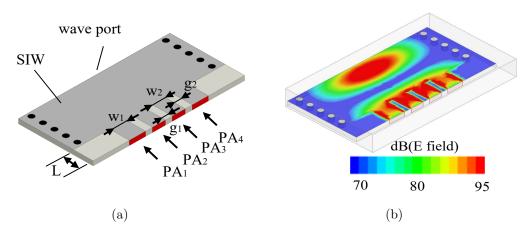

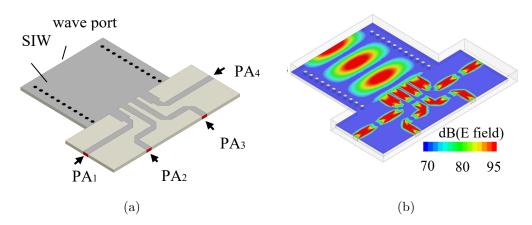

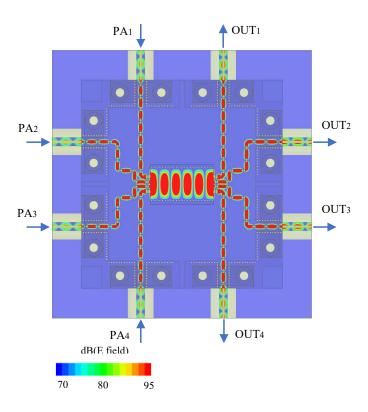

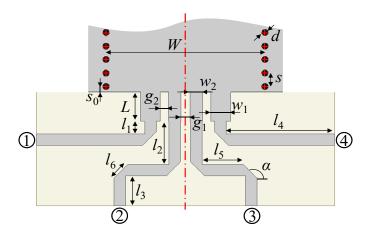

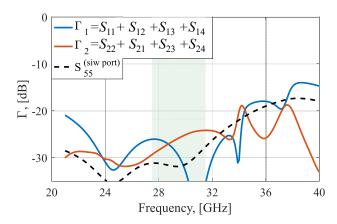

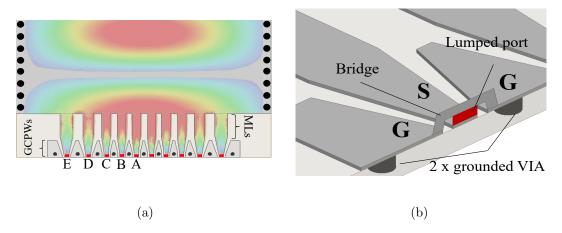

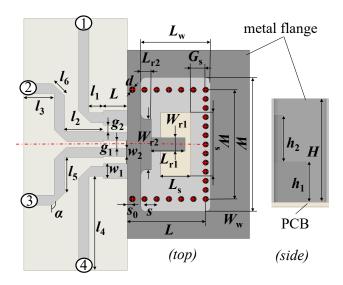

The proposed spatial power-combining transition has been tested in a 4:1 configuration, as shown in Figure 2.11. It includes four input ML ports with  $50-\Omega$  reference impedance and a single matched SIW port as an output. The SIW width has been choosen in such a way that both the  $TE_{10}$  and  $TE_{20}$  modes can propagate.

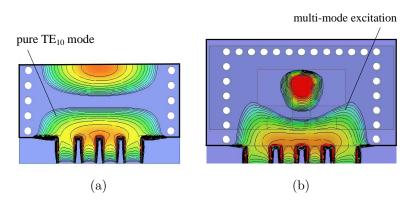

The critical design parameters are the positions of MLs, the distances between MLs, their lengths and widths. The transition has been optimized to realize an optimal active impedance matching under the condition of uniform excitation ( $\{A_n\}_{n=1}^4 = 1$ ). The optimal design parameters are presented in [Paper B]. Figure 2.12 (a) illustrates the field coupling from multiple quasi-TEM modes to the TE<sub>10</sub> mode and its subsequent propagation inside the SIW when the input ports are uniformly excited. In spite of the fact that the transition has been optimized to maximize power transfer into the fundamental TE<sub>10</sub> mode, higher-order modes could also be generated by ap-

#### Chapter 2. Spatial Power Combining in Substrate Integrated...

Figure 2.11: EM model of the proposed power-combining transition in a 4:1 configuration.

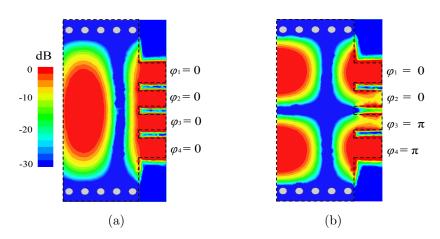

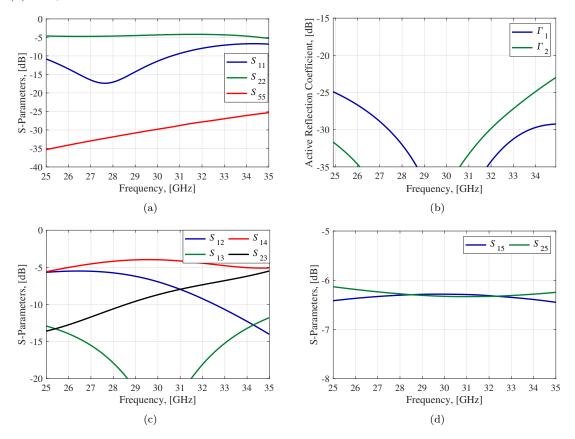

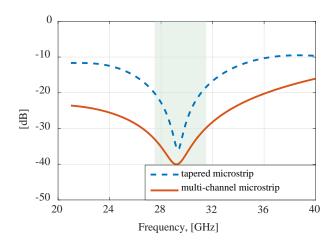

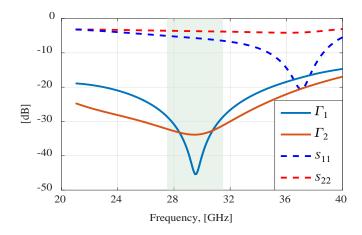

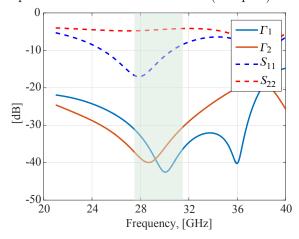

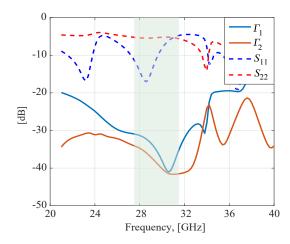

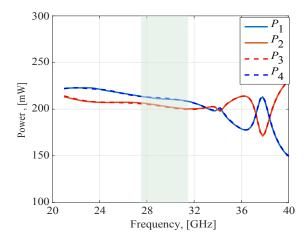

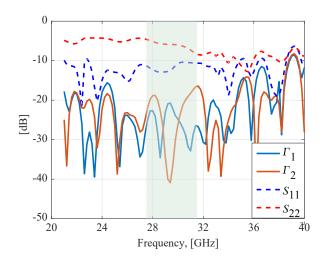

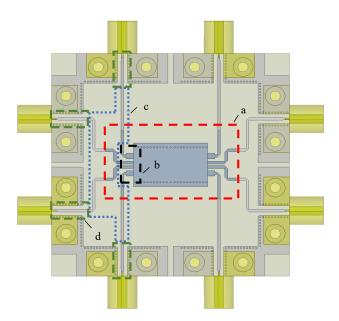

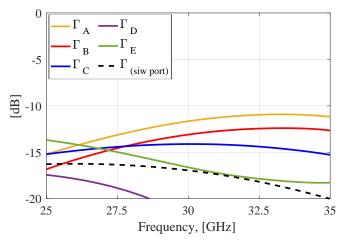

plying different excitation scenarios. Figure 2.12 (b) exemplifies a generation of the TE<sub>20</sub> mode by the same arrangement; corresponding excitation coefficients are defined as:  $A_n = e^{-j\phi_n}$ , where  $\phi_n = \{0, 0, \pi, \pi\}$ . The higher modes (TE<sub>30</sub>, TE<sub>40</sub>) might be obtained by increasing the SIW width and interfacing more input ports, which gives extra degrees of freedom for implementing more complex excitation scenarios. Due to the flexibility of the proposed transition, it is expected to play an essential role in multi-mode antennas, where multiple modes are usually employed to increase the operation bandwidth [92]. The simulated passive and active reflection coefficients  $(|S_{11}|, |S_{22}| \text{ and } |\Gamma_1|, |\Gamma_2|)$  of the 50- $\Omega$  ports of the 4:1 transition over the 25–35 GHz frequency range are shown in Figures 2.13 (a) and (b) respectively. Although the passive reflection coefficients of the individual ports reach -5 dB level, their active reflection coefficients (when all input ports are excited simultaneously) remain below -25 dB over 30% bandwidth and  $\leq -15 \text{ dB}$  over 50% bandwidth. The latter is a result of efficiently utilizing mutual couplings between the ports. Figure 2.13 (c) shows the couplings between the  $50-\Omega$  input ports. As one can see, the coupling between the edge ports ( $|S_{14}|$ ) reaches -4 dB level, whereas the coupling between port 1 and port 3 ( $|S_{13}|$ ) is below -12 dB over the 25–35 GHz frequency range. The relatively high  $|S_{14}|$  mainly attributes to the coupling between the ports within SIW modes. This effect might be critical for some applications, where active components require a good isolation between channels. A method of isolation enhancement is discussed in the next subsection.

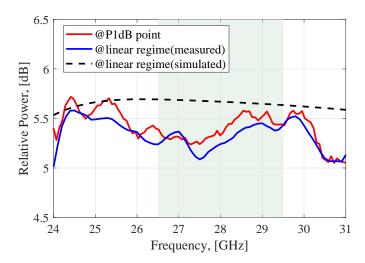

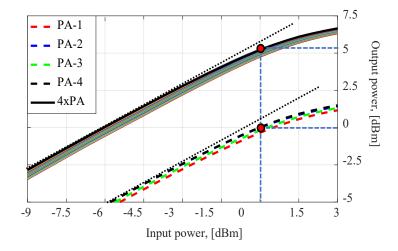

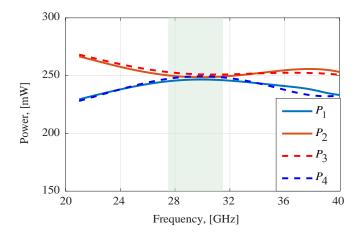

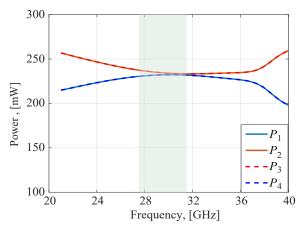

Figure 2.13 (d) shows transmission coefficients between the symmetric 50- $\Omega$  input ports and the output SIW port ( $|S_{15}|$ ,  $|S_{25}|$ ). In case of an ideal 4:1 power combiner/divider:  $|S_{15}| = |S_{25}| = -6$  dB. However, the average level of the simulated transmission coefficients is  $\geq -6.25$  dB, which results in approximatly 0.25 dB incertion losses. The relative difference between  $|S_{15}|$  and  $|S_{25}|$  does not exceed 0.2 dB, implying that the power amplifiers in the array are utilized effectively.

### 2.3. Transition between a Coupled Microstrip Line Array and...

Figure 2.12: Magnitude of the real part of the E-field distribution at 30 GHz: (a)  $TE_{10}$  mode; (b)  $TE_{20}$  mode.

Figure 2.13: Simulated (a) Passive reflection coefficients; (b) Active reflection coefficients of the input ports, as shown in Figure 2.11; (c) Coupling between the input ports; (d) Combiner insertion losses. The results for symmetric ports are omitted.

The special case of a 10-way power combiner with  $50-\Omega$  CPW input ports has been presented in [Paper D]. The simulated active reflection coefficients of the CPW-ports and passive reflection coefficient at the wave port of the structure are better than -10 dB over more than 30% relative bandwidth (25–35 GHz). Numerical results validate the model and show that this configuration allows for efficient power combining from multiple amplifiers, and hence can generate  $10\times$  more power while maintaining a constant loss of almost 0.3 dB.

Summarizing the above, the proposed transition overcomes fundamental limitations of single-channel SIW transitions and simultaneously achieves a wide bandwidth and low power loss, and also outperforms the state-of-the-art multi-channel multi-mode transitions in terms of its compactness and power transfer/combining efficiency (See Table 2.1).

## 2.3.3 Isolation Enhancement Technique

An essential factor worth taking into account in the transition design procedure is the mutual coupling between PAs. The transition is designed under the condition of a uniform excitation assuming identical PAs ( $\{A_n\}_{n=1}^4 = 1$ ). However, realistic PAs might be slightly different in their amplitude-phase characteristics due to dif-

Figure 2.14: Simulation models of the 4-way power combiners: (a) Ideal Wilkinson power combiner; (b) Spatial power combiner with and without isolation load resistors.

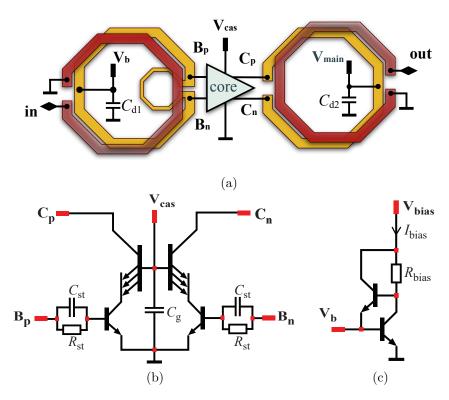

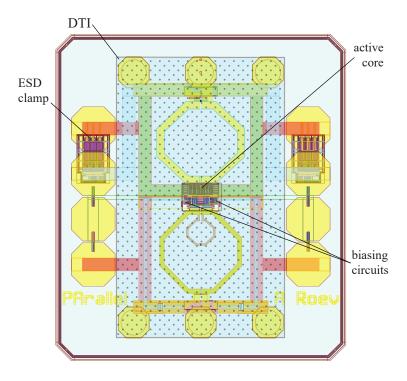

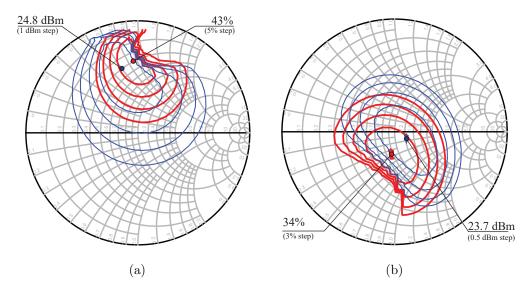

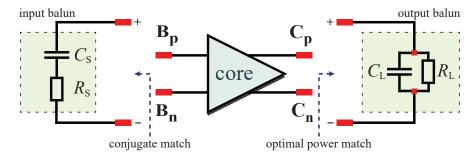

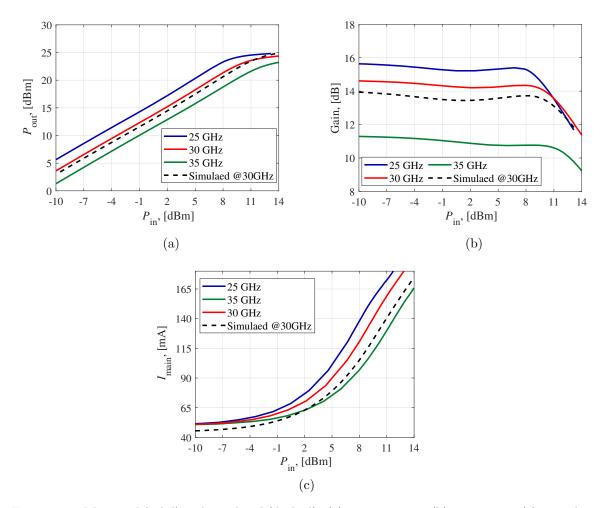

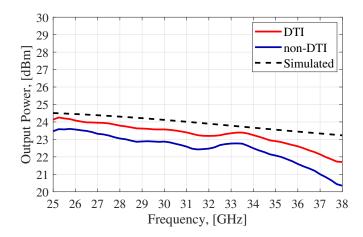

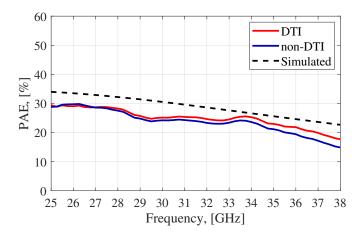

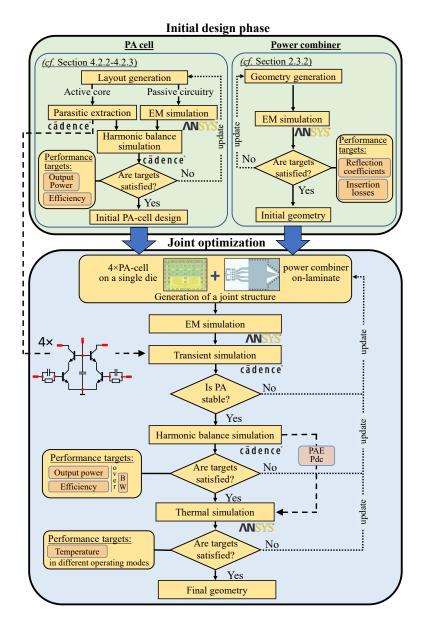

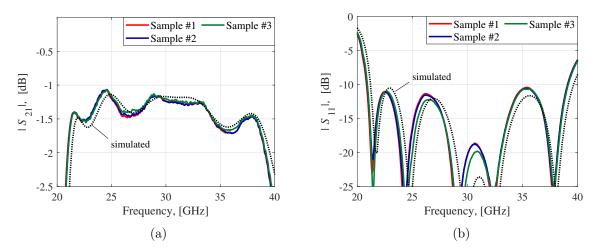

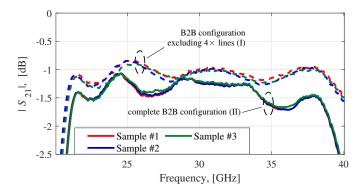

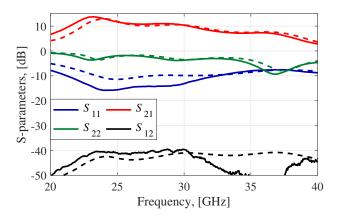

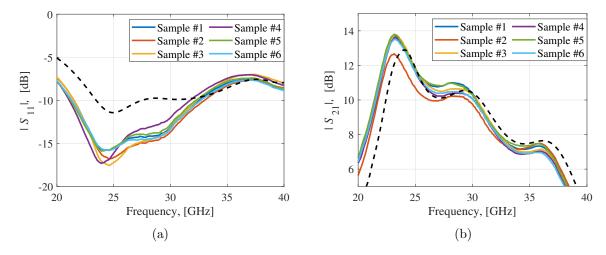

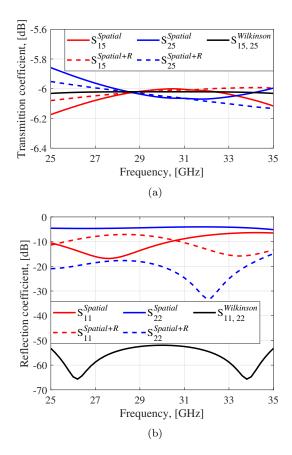

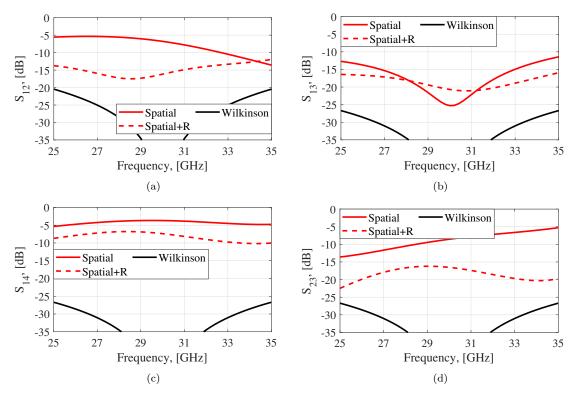

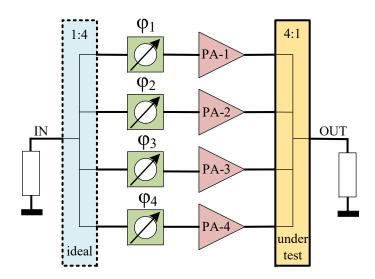

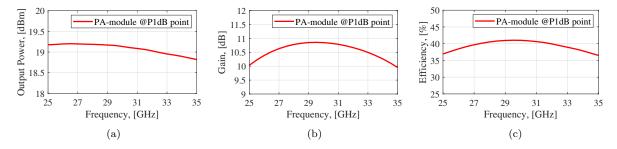

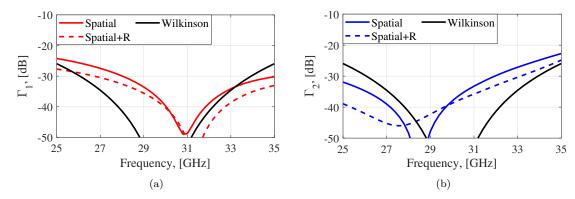

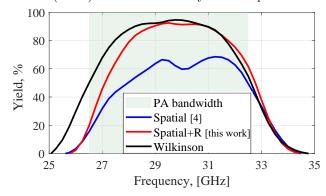

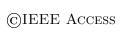

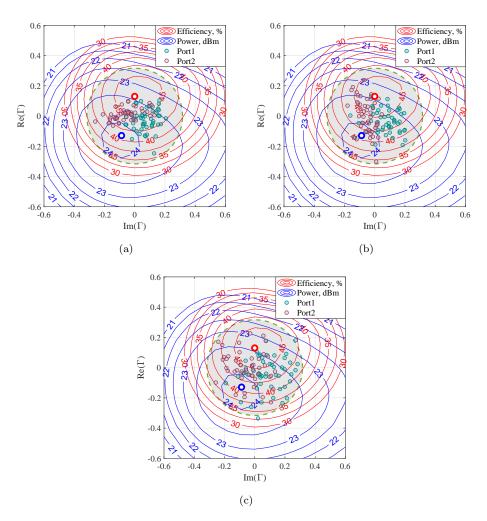

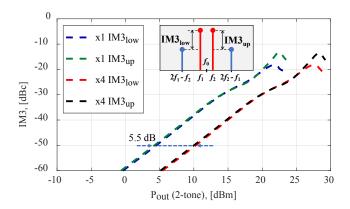

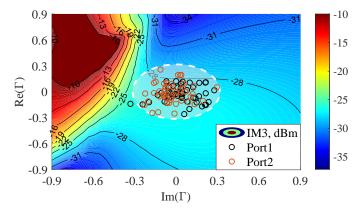

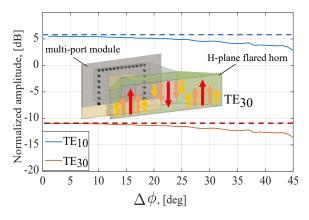

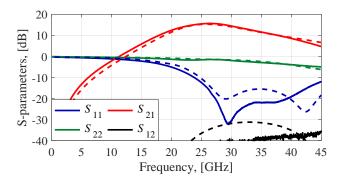

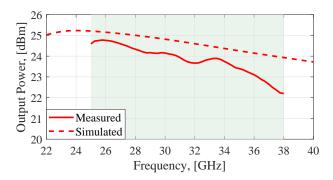

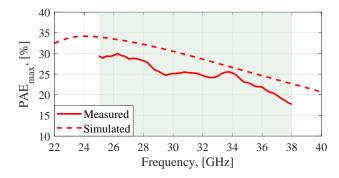

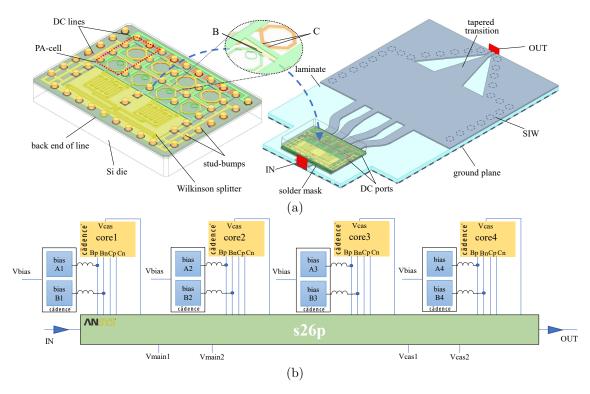

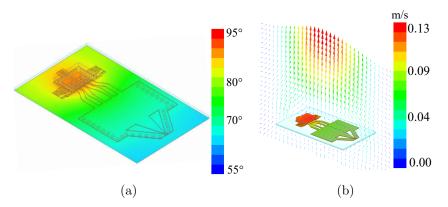

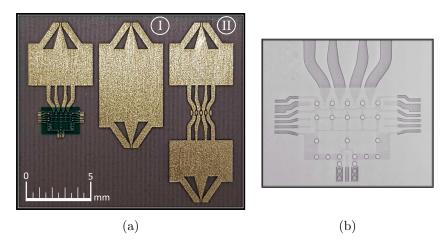

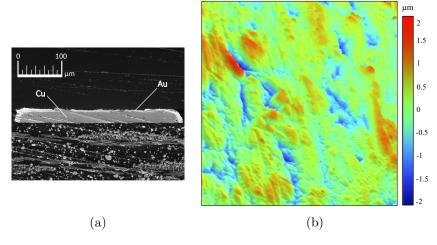

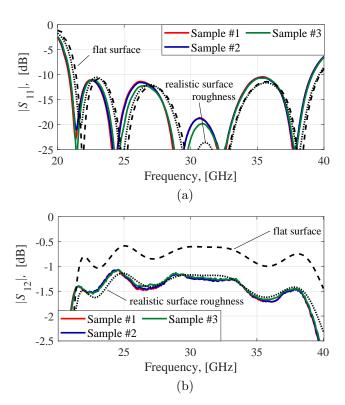

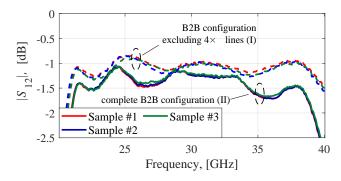

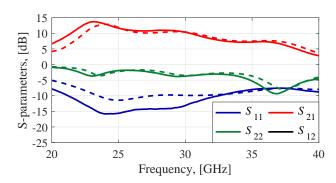

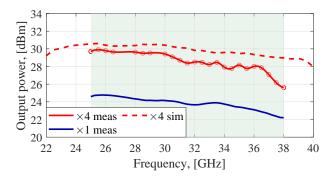

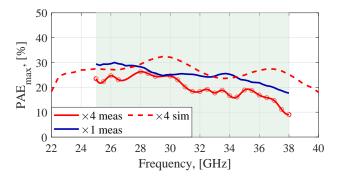

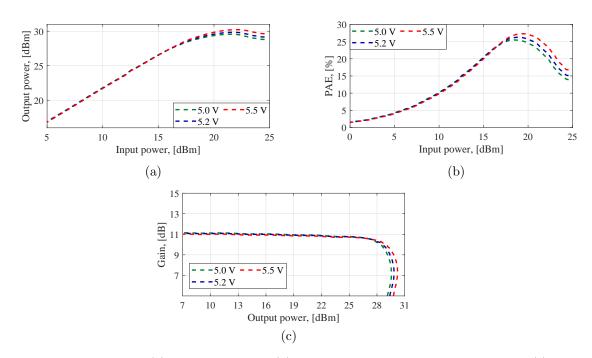

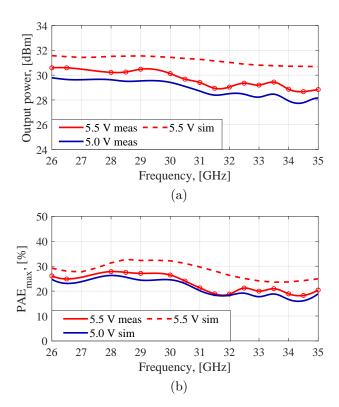

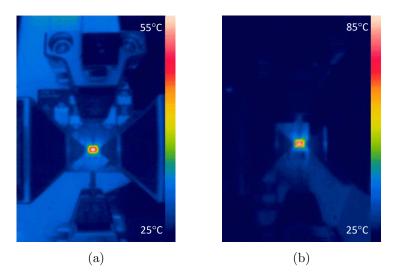

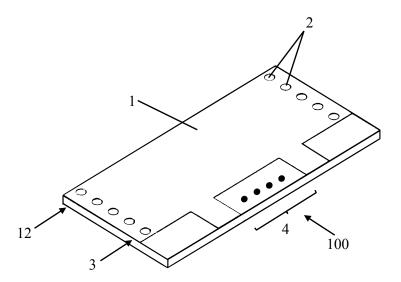

ferent thermal regimes, semiconductor process variations and fabrication tolerances. This effect could be introduced into the design procedure by varing complex excitation coefficients  $\{A_m\}_{m=1}^4$  in Equation 2.6. Generally, in order to reduce the effect of  $\{A_m\}_{m=1}^4$  on the active reflections  $\{\Gamma_n\}_{n=1}^4$ , the magnitudes of  $S_{nm}$  have to be minimized.