### Geometrical magnetoresistance effect and mobility in graphene field-effect transistors

Downloaded from: https://research.chalmers.se, 2025-12-10 01:20 UTC

Citation for the original published paper (version of record):

Harrysson Rodrigues, I., Generalov, A., Soikkeli, M. et al (2022). Geometrical magnetoresistance effect and mobility in graphene field-effect transistors. Applied Physics Letters, 121(1). http://dx.doi.org/10.1063/5.0088564

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

# Geometrical magnetoresistance effect and mobility in graphene field-effect transistors

Cite as: Appl. Phys. Lett. **121**, 013502 (2022); https://doi.org/10.1063/5.0088564 Submitted: 18 February 2022 • Accepted: 22 June 2022 • Published Online: 07 July 2022

🧓 Isabel Harrysson Rodrigues, 🗓 Andrey Generalov, 🗓 Miika Soikkeli, et al.

#### ARTICLES YOU MAY BE INTERESTED IN

Graphene/SOI-based self-powered Schottky barrier photodiode array

Applied Physics Letters 121, 011105 (2022); https://doi.org/10.1063/5.0092833

Topological sensor on a silicon chip

Applied Physics Letters 121, 011101 (2022); https://doi.org/10.1063/5.0097129

Continuously tunable radio frequency electrometry with Rydberg atoms Applied Physics Letters 121, 014002 (2022); https://doi.org/10.1063/5.0086357

☐ QBLOX

Shorten Setup Time

Auto-Calibration

More Qubits

Fully-integrated

Quantum Control Stacks

Ultrastable DC to 18.5 GHz

Synchronized <<1 ns

Ultralow noise

100s qubits

visit our website >

## Geometrical magnetoresistance effect and mobility in graphene field-effect transistors

Cite as: Appl. Phys. Lett. **121**, 013502 (2022); doi: 10.1063/5.0088564 Submitted: 18 February 2022 · Accepted: 22 June 2022 · Published Online: 7 July 2022

Isabel Harrysson Rodrigues,<sup>1,a)</sup> (i) Andrey Generalov,<sup>2</sup> (i) Miika Soikkeli,<sup>2</sup> (i) Anton Murros,<sup>2</sup> (ii) Sanna Arpiainen,<sup>2</sup> (ii) and Andrei Vorobiev<sup>1</sup> (ii)

#### **AFFILIATIONS**

<sup>1</sup>Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296 Gothenburg, Sweden <sup>2</sup>VTT Technical Research Center of Finland Ltd., P.O. Box 1000, FI-02044 VTT, Finland

#### **ABSTRACT**

Further development of graphene field-effect transistors (GFETs) for high-frequency electronics requires accurate evaluation and study of the mobility of charge carriers in a specific device. Here, we demonstrate that the mobility in the GFETs can be directly characterized and studied using the geometrical magnetoresistance (gMR) effect. The method is free from limitations of other approaches since it does not require an assumption of the constant mobility and the knowledge of the gate capacitance. Studies of a few sets of GFETs in the wide range of transverse magnetic fields indicate that the gMR effect dominates up to approximately 0.55 T. In higher fields, the physical magnetoresistance effect starts to contribute. The advantages of the gMR approach allowed us to interpret the measured dependencies of mobility on the gate voltage, i.e., carrier concentration, and identify the corresponding scattering mechanisms. In particular, the range of the fairly constant mobility is associated with the dominating Coulomb scattering. The decrease in mobility at higher carrier concentrations is associated with the contribution of the phonon scattering. Analysis shows that the gMR mobility is typically 2–3 times higher than that found via the commonly used drain resistance model. The latter underestimates the mobility since it does not take the interfacial capacitance into account.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0088564

Future progress in modern electronics relies on the development of novel two-dimensional (2D) materials with cutting-edge performance, among which graphene is a promising candidate. The very high carrier mobility and velocity in graphene could enable much faster electronics than traditional semiconductors. The roomtemperature intrinsic mobility in single layer graphene is above 100 000 cm<sup>2</sup>/V s, which is larger than that in the highest mobility III-V compounds. 1-3 With such high mobility, the graphene-based high-frequency electronics might reach the still uncovered terahertz range offering many exciting novel applications. 4 However, currently, in real graphene devices, mobility is significantly reduced. In particular, the room temperature mobility in the graphene field-effect transistors (GFETs), with the highest reported high-frequency performance, is below  $5000\,\mathrm{cm}^2/\mathrm{V}\,\mathrm{s}^{.5,6}$  The mobility degradation is associated with material imperfections caused by the specific device processing and vicinity of dielectrics in the device structure. Additionally, there is typically a strong surface distribution of the mobility measured in the GFETs located at different positions on the wafer caused by the spatially inhomogeneous Coulomb potential associated with charged impurities.<sup>8,9</sup> Therefore, for further development of the graphene-based

high-frequency electronics, methods of accurate evaluation of the mobility directly based on the measured characteristics of the specific device, i.e., without involving different test structures, should be developed and applied.

To date, the mobility in a specific GFET is generally characterized using a drain resistance model applied to the measured transfer characteristics. 10-12 This approach does not require additional test structures. However, it has a number of limitations including the assumption of constant mobility and uncertainty of the gate capacitance, which can be strongly modified by the interfacial states.<sup>13</sup> This may result in large errors in the mobility evaluation. For example, we have shown that the mobility values calculated using the drain resistance model can be 2-3 times lower than those found from the delay time analysis in the same GFETs.7 Already in the early years of the development of the field-effect transistors, it has been proposed that the carrier mobility and velocity can be assessed through the geometrical magnetoresistance (gMR) effect. 14,15 This effect arises when the magnetic field causes the path of the charge carriers to deviate from a straight line, raising the sample resistance. 16 It was indicated that advantages of the gMR method for the evaluation of the mobility, in

a) Author to whom correspondence should be addressed: isabelr@chalmers.se

comparison with other methods, are that it does not require knowledge of the carrier concentration or the transistor's capacitance, gate length, access resistance, and threshold voltage. <sup>17</sup> In our previous work, we have studied the low-field mobility and high-field carrier velocity in InGaAs/InP high-electron-mobility transistors found via the gMR effect. <sup>18</sup> In this work, we demonstrate that mobility in GFETs can be directly characterized using the gMR method. This method is free from the limitations of the drain resistance approach since it does not require an assumption of a constant mobility or knowledge of the gate capacitance.

The paper is structured in two parts. The first part focuses on demonstrating the gMR effect in the GFETs and evaluating the gMR mobility and the associated charge carrier transport mechanisms. The second part reports on a comparative analysis of the mobility applying the commonly used drain resistance model approach, which shows that it may underestimate the mobility 2–3 times because of uncertainty in the gate capacitance.

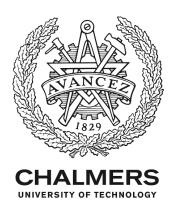

The GFETs studied in this work have layouts similar to those previously published, <sup>5</sup> i.e., with dual gate-fingers centered between the source and drain contacts, with 100 nm long ungated regions, as illustrated in Fig. 1. Two sets of GFETs with the gate length (*L*) and width

**FIG. 1.** (a) A typical optical microscopy image and (b) a 3D illustration of the GFET with transverse B-field applied, together with (c) a schematic cross-sectional view of the active area indicating the materials of different layers. Also shown is the total resistance equivalent circuit at the condition of applied B-field (c). Note that the first and second gate dielectric layers, labeled as  $Al_2O_3$  layer 1 and  $Al_2O_3$  layer 2, respectively, are assumed to be transparent and, hence not visible in (b).

(*W*) varying in the ranges of 0.2–2.0 and 5–15  $\mu$ m, respectively, were fabricated on two different Si wafers, at VTT and Chalmers, which will be referred to below as wafer-1 and wafer-2, respectively. The processing steps are similar to those described previously.

The four main distinguishable stages (i)-(iv) of the GFET fabrication are as follows. In stage (i), the chemical vapor deposition (CVD) graphene film, prepared by Graphenea, is transferred onto high resistivity silicon/silicon oxide (Si/SiO<sub>2</sub>) substrate, with a SiO<sub>2</sub> thickness of 1 μm, using the Easy Transfer approach. <sup>19</sup> The transferred graphene film is covered by an approximately 8 nm thick Al<sub>2</sub>O<sub>3</sub> layer constituting the first layer of the gate dielectric. This layer is obtained by six times repeating the steps of the deposition of 1 nm thick Al film and its subsequent oxidation on a hotplate at 160 °C for 5 min. In this technology, the first gate dielectric layer encapsulates graphene, preventing contamination during further processing. In stage (ii), the graphene/ dielectric mesa is patterned with e-beam lithography, followed by an etch of the Al<sub>2</sub>O<sub>3</sub> layer using the buffered oxide etch diluted by ten parts of water (BOE/H2O) and a subsequent etch of the graphene using oxygen plasma. The openings in the Al<sub>2</sub>O<sub>3</sub> layer for the drain/ source contacts are patterned with e-beam lithography followed by an etch using BOE/H2O. The drain/source contacts are formed by deposition of 1 nm Ti/15 nm Pd/250 nm Au layered structure and the use of standard liftoff process. In stage (iii), the second gate dielectric layer of Al<sub>2</sub>O<sub>3</sub> is formed by repeating the aforementioned process ten times. The second gate dielectric layer is approximately 14 nm thick making the total gate dielectric thickness of 22 nm. The second dielectric layer covers the graphene edges exposed at the mesa sidewalls and, hence, prevents short-circuiting by the overlapping gate fingers. In stage (iv), the gate electrodes and the contact pads are fabricated by e-beam lithography and deposition of 10 nm Ti/290 nm Au layered structure by e-beam evaporation followed by a standard liftoff process. Figure 1(a) shows a typical optical microscope image of a fabricated GFET.

As shown and discussed below, despite the similarity of the processing steps, the series resistance in the GFETs on wafer-1 is typically more than ten times larger than that on wafer-2. However, the gMR mobility can be extracted after de-embedding the series resistance. This allows us to demonstrate that the gMR method is applicable on GFETs with significantly different series resistance and mobility values.

The transfer characteristics of the GFETs were measured in the one-finger, common source configuration at the drain voltage  $V_{DS}=0.3\,\mathrm{V}$  and  $-0.1\,\mathrm{V}$  on wafer-1 and wafer-2, respectively, using a Keithley 2612B dual-channel source meter, as well as a HP 4156B semiconductor parameter analyzer without and with a transverse magnetic field. The measurements were performed in a standard Hall set-up equipped with a movable permanent magnet with magnetic flux density (*B*-field)  $B=0.33\,\mathrm{T}$ , see figure in the supplementary material. Several GFETs have been measured with the aim of confirming the gMR effect and making a comprehensive error analysis, see the supplementary material. To further verify the gMR effect, the dependencies of the drain resistances on the transverse *B*-field in the range of 0–0.8 T, in both directions, were measured under vacuum at room temperature using a current source (Keithley 6221), a nanovoltmeter (Keithley 2182A) and an electromagnet.

The measurements of the transfer characteristics without a magnetic field were done comparatively in the dark and illuminated environment to investigate variations of the drain resistance, which were

shown to remain within the errors of measurements. This allowed for excluding the possible effects of the persistent photo-conductivity traps, <sup>15</sup> caused by screening the light by the magnet, and confirms that the charge carrier transport under magnetic field is governed mainly by the gMR effect.

Figures 1(b) and 1(c) show a 3D illustration of the GFET with transverse *B*-field applied, together with a schematic cross-sectional view of the active area indicating materials of different layers indicated. Figure 1(c) also shows the equivalent circuit of the total drain-source resistance under an applied magnetic field *B*. The  $R_{\rm gated}^B$  and  $\frac{1}{2}R_{\rm ungated}^B$  are the resistances of the gated and ungated regions of the channel, respectively. The  $\frac{1}{2}R_{\rm contact}^B$  is the contact resistance associated with the graphene-metal junction. At the condition without *B*-field, the corresponding resistances are notated as  $R_{\rm gated}^0$ ,  $\frac{1}{2}R_{\rm ungated}^0$ , and  $\frac{1}{2}R_{\rm contact}^0$ . The resistances of the ungated regions and contact resistances constitute the total series resistances as  $R_{\rm series}^B = R_{\rm ungated}^B + R_{\rm contact}^B$  and  $R_{\rm series}^0 = R_{\rm ungated}^0 + R_{\rm contact}^0$  with and without *B*-field, respectively. The total GFET resistance can be expressed as  $R_{\rm total}^B = R_{\rm series}^B + R_{\rm gated}^B$  and  $R_{\rm total}^0 = R_{\rm series}^0 + R_{\rm gated}^0$  with and without *B*-field, respectively.

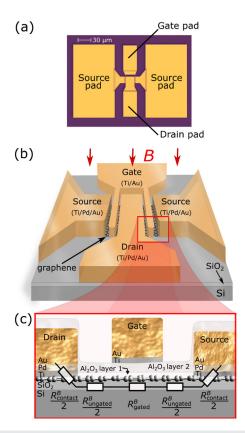

Figure 2(a) shows a typical dependence of the  $R_{\rm total}^B$ , measured between the drain and source terminals of a GEET from wafer-1 with

Figure 2(a) shows a typical dependence of the  $R_{\text{total}}^B$ , measured between the drain and source terminals, of a GFET from wafer-1, with  $L=1~\mu\text{m}$  and  $W=5~\mu\text{m}$  on the transverse *B*-field varied in both directions at zero gate voltage. It can be seen that the dependence is symmetric and with the drain resistance increasing with the *B*-field as a power law function. Under the conditions of a negligible physical magnetoresistance effect (pMR) and L/W < 0.4, the gMR mobility is given by Ref. 16

$$\mu_{\rm gMR} \approx \frac{1}{B} \sqrt{\frac{R_{\rm gated}^B}{R_{\rm gated}^0} - 1}.$$

(1)

In general, the series resistance depends on the magnetic field due to the gMR effect in the ungated regions of the channel. Since the top and bottom graphene–dielectric interfaces of gated and ungated regions of the channel are similar, one can assume that at zero gate voltage ( $V_{\rm GS}=0$ ), the gated and ungated regions are indistinguishable. One can also assume that the variation of contact resistance due to gMR effect in the transfer area of the graphene–metal contact is negligible because of the dominating transverse electric field component and, hence, negligible Lorentz force. Therefore, the contact resistance does not depend on the magnetic field and  $R_{\rm contact}^B=R_{\rm contact}^0$ . With these assumptions, one can readily get from Eq. (1) that

**FIG. 2.** (a) The  $R_{\text{total}}^{\mathcal{B}}$  of a GFET from wafer-1 vs transverse *B*-field varying in both directions at zero gate voltage. (b) The same data plotted vs the square of the *B*-field. The straight line indicates a pure quadratic dependence of  $R_{\text{total}}^{\mathcal{B}}$  vs *B*.

$$R_{\text{total}}^{B} = \left(R_{\text{total}}^{0} - R_{\text{contact}}^{0}\right) \left(\mu_{\text{gMR}}B\right)^{2} + R_{\text{total}}^{0}.$$

(2)

It can be seen from Eq. (2) that the dependence of the  $R_{\text{total}}^B$  on  $B^2$  should reveal a straight line. Figure 2(b) shows the same experimental data presented in Fig. 2(a) plotted vs  $B^2$ . The dependence is fairly linear up to  $B \approx 0.55$  T, indicating that the approximation by Eq. (1) is valid below this B-field. The sub-linear behavior at higher B-field is in agreement with that calculated using exact solution. <sup>14</sup> This behavior is in a qualitative agreement with a similar dependence observed on AlGaAs MODFETs. <sup>14</sup>

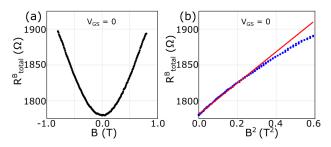

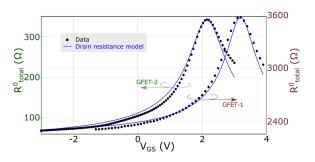

Figure 3(a) shows typical dependencies of the drain resistances on the gate voltage of a GFET on wafer-1 (referred below as GFET-1) and a GFET on wafer-2 (referred below as GFET-2), with and without transverse magnetic field. GFET-1 and GFET-2 have the same gate length of 1  $\mu$ m, but different gate width of 5 and 15  $\mu$ m, respectively. It can be seen that the magnetic field increases the drain resistance in the whole range of the gate voltage, apparently, due to the gMR effect, see also inset in Fig. 3(a).

**FIG. 3.** (a) The drain resistance of GFET-1 and GFET-2 vs gate voltage with and without the transverse *B*-field. Inset shows the narrow range of the gate voltage from  $-0.1\,\text{V}$  to  $0.1\,\text{V}$ , for a clearer demonstration of the gMR effect, in GFET-2. (b) The drain resistances of GFET-1 and GFET-2, with and without the transverse *B*-field, plotted vs  $\frac{1}{V_{GSO}}$  in the hole conductivity branch above  $-1\,\text{V}^{-1}$ . The straight lines are linear fits in the ranges of constant mobility.

-0.50 1/V<sub>GSO</sub> (V<sup>-1</sup>)

-0.25

50<u>1.0</u>

-0.75

0.0

The gMR mobility can be calculated using Eq. (1) after subtracting the corresponding series resistances from the measured drain resistances. To find the series resistances, we applied an approach similar to that published previously. In the GFETs, at relatively high gate voltage overdrive  $V_{\rm GSO} = V_{\rm GS} - V_{\rm Dir}$ , where  $V_{\rm Dir}$  is the Dirac voltage, i.e., under the condition of the gate induced concentration much larger than the residual concentration of the charge carriers  $(n_0)$ , the drain resistances with (and without) magnetic field can be expressed as

$$R_{\text{total}}^{0} = R_{\text{series}}^{0} + \frac{L}{Wen\mu}, \tag{3}$$

where e is the elementary charge,  $\mu$  is the field-effect mobility, and n is the charge carrier concentration proportional to  $V_{GSO}$ . <sup>22</sup> Based on our previous studies, we assume that in the limited range of n, the carrier transport is governed by the Coulomb scattering with the mobility independent of the concentration. For comparison, analysis of the carrier density in the graphene test structures showed that mobility is relatively constant in the range of concentration  $2-3 \times 10^{12}$  cm<sup>-2</sup> which is explained by the dominating Coulomb scattering. It was shown that the Coulomb scattering is the only mechanism resulting in mobility being independent of the carrier concentration.<sup>8,22,23</sup> Under these conditions, the drain resistances given by Eq. (3) are linear functions of the  $\frac{1}{V_{\rm CSO}}$ , and the series resistances can be found by linear fitting of the corresponding dependencies. In the analysis below, we consider only hole branches of the transfer characteristics, i.e., at  $V_{\rm GSO} < 0$ , because the number of data in the electron branches is not sufficient for reliable fitting and the series resistance in the electron branch is typically higher due to the formation of the pn-junction in the ungated regions.<sup>24</sup> Figure 3(b) shows the series resistances of GFET-1 and GFET-2 plotted vs  $\frac{1}{V_{\text{CSO}}}$  in the hole conductivity branch above  $-1\,\text{V}^{-1}$  together with the linear fits made in the ranges of the constant mobility. It can be seen that the dependencies are fairly linear up to approximately  $-0.5 \,\mathrm{V}^{-1}$ , manifesting that the mobility is constant. Deviations from the linear dependencies above  $-0.5 \,\mathrm{V}^{-1}$ , i.e., higher carrier concentration, can be explained by a decrease in mobility due to the increasing contribution of phonon scattering.<sup>22</sup> The linear fits give the series resistances of 2198 and 52  $\Omega$ , with corresponding specific-width resistivity of 5495 and 780  $\Omega \times \mu m$  for GFET-1 and GFET-2, respectively. The GFETs on wafer-1 typically reveal relatively larger specific-width resistivity than the GFETs on wafer-2, which can be explained by incomplete removal of the Al<sub>2</sub>O<sub>3</sub> layer in the drain/source contact openings.

Figure 4 shows a flow chart of the algorithm used in this work to extract the gMR mobility. The algorithm consists of two similar sequences of de-embedding the series resistances of a GFET without *B*-field (left part of the flow chart) and with *B*-field (right part of the flow chart) followed by calculation of the gMR mobility using Eq. (1).

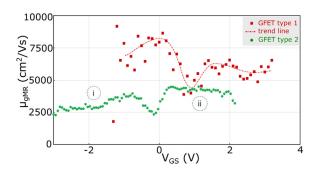

Figure 5 shows the gMR mobility calculated using Eq. (1) with the series resistances found by the linear fits of the dependencies in Fig. 3(b). It can be seen that, in general, the mobility depends on the gate voltage, i.e., carrier concentration. In the dependence of GFET-2, one can distinguish two different regions. In the region (i) for  $V_{\rm GS}$  up to approximately  $-0.5\,\rm V$ , the mobility decreases with increasing the gate voltage modulus, which can be associated with increasing contribution of phonon scattering at higher carrier concentrations. The decrease in mobility with carrier concentration has been previously observed and similarly explained by changing the dominant scattering

FIG. 4. Flowchart showing algorithm of extraction of the gMR mobility used in this work

mechanism from Coulomb to phonon scattering.<sup>22</sup> In the region (ii) of  $V_{\rm GS}$  between approximately 0.5 and 2 V, the mobility is relatively constant indicating that Coulomb scattering dominates. It can be seen from Fig. 5 that between the regions (i) and (ii), there is a drop in the mobility at  $V_{\rm GS} \approx -0.1$  V. One can notice that this gate-source voltage coincides with the drain-source voltage bias used in the measurements of GFET-2. Therefore, the gate-drain voltage is approximately zero, and the channel potential at the gated region's drain side equals that of the ungated region. Under this condition, there is no ppjunction formed between the gated and ungated region, as described, e.g., in Ref. 25, and, hence, the series resistance is lower compared to that at other gate-source voltages below and above this value. Since, in the applied algorithm, the series resistance is found in the region (ii), this local minimum of the series resistance results in an underestimation of the actual  $\mu_{\rm gMR}$ , which manifests itself as a drop in mobility at  $V_{\rm GS} \approx V_{\rm DS}$ . As shown in Fig. 5, the data from GFET-1 are relatively

**FIG. 5.** The gMR mobility of GFET-1 (squares) and GFET-2 (circles) vs gate voltage. Two different regions with different dominating charge carrier mechanisms are indicated as (i) and (ii) for GFET-2. The trend line is shown as a guide for the eye.

more scattered than that of GFET-2, which most likely is a result of drain current instabilities caused by tunneling of the charge carriers through the  ${\rm Al_2O_3}$  residuals in the graphene-metal junctions. This complicates the physical interpretation of the dependence found for GFET-1. However, the clearly seen drop in mobility at 0.5–1.0 V approximately coincides with the drain voltage bias used in the measurements of GFET-1, which confirms our above explanation. Note that this differs from  $V_{\rm DS} = -0.1$  V used in the experiments and the drop in mobility seen in Fig. 5 for GFET-2.

For comparison, we evaluated the field-effect mobility by applying the commonly used drain resistance model

$$R_{\text{total}}^{0} = R_{\text{series}}^{0} + \frac{L}{W} \frac{1}{\mu e} \frac{1}{\sqrt{n_0^2 + \left(V_{\text{GSO}} \frac{C_g}{e}\right)^2}},$$

(4)

where  $C_{\rm g}$  is the gate capacitance per unit area. <sup>10,11</sup> It can be shown that under the conditions used in our experiments, the graphene quantum capacitance can be ignored. Figure 6 shows the  $R_{\text{total}}^0$  vs gate voltage of GFET-1 and GFET-2, measured without B-field, together with fitting by the drain resistance model. The solid lines represent the best fitting using the commonly applied approach, i.e., using the  $R_{

m series}^0,\ n_0$  and  $\mu$  as fitting parameters and the  $C_{

m g}$  calculated as  $\frac{(\epsilon imes \epsilon_0)}{d_c}$ , where the  $\epsilon_0$  is the vacuum permittivity and  $\epsilon$  is the dielectric constant of the gate dielectric. We assume that in our GFETs,  $\epsilon \approx 7.5$ . The values of the fitting parameters and  $C_g$  are given in Table I, where  $C_g$  is equivalent to the oxide capacitance ( $C_{ox}$ ), since no other capacitance is considered. In both GFET-1 and GFET-2, the mobility found using the drain resistance model is 2-3 times lower than the corresponding gMR mobility. We explain it by the limitations of the drain resistance model, which includes the assumption of constant mobility and uncertainty of the gate capacitance. In particular, in our previous studies, using the delay time analysis and capacitance-voltage characteristics, we showed explicitly that the drain resistance model, in its commonly used approach, i.e., using only  $C_{ox}$  as the gate capacitance, can underestimate the mobility. Furthermore, we have shown that the gate capacitance in GFETs can be strongly modified by the interfacial states, which further introduces uncertainties in the capacitance value. 7,13 In summary, the gMR method of extraction of mobility can be considered as potentially more accurate, in comparison with the commonly used approach of fitting by the drain resistance model,

**FIG. 6.** The drain resistances of GFET-1 and GFET-2 vs gate voltage without magnetic field. The solid lines represent the drain resistance model fitting with the commonly applied approach, i.e., using the  $R_{\text{series}}^0$ ,  $n_0$ , and  $\mu$  as fitting parameters. Note that the plot aspect ratio differs from that in Fig. 3(a) showing in part the same experimental data.

TABLE I. Parameters used in the drain resistance model

|        | $\mu$ (cm <sup>2</sup> /V s) | $R_0(\Omega)$ | $n_0 \times 10^{15}  (\mathrm{m}^{-2})$ | $C_{ox} \times 10^{-3} \; (\text{F/m}^2)$ |

|--------|------------------------------|---------------|-----------------------------------------|-------------------------------------------|

| GFET-1 | 868                          | 2150          | 10                                      | 3                                         |

| GFET-2 | 1380                         | 40            | 10                                      | 3                                         |

|        | Fitting parameters           |               |                                         |                                           |

since it does not require the assumption of the constant mobility and knowledge of the gate capacitance, i.e., it is free from these limitations and associated uncertainties.

In conclusion, we show that the geometrical magnetoresistance effect can be used to extract and study mobility directly in the graphene field-effect transistors, i.e., without involving additional specific test structures. This allows for avoiding the significant uncertainties associated with the strong surface distribution of the mobility over the wafer surface caused by the spatially inhomogeneous Coulomb potential of charged impurities. In contrast to the commonly used approach of fitting by the drain resistance model, the gMR method does not require the assumption of the constant mobility and knowledge of gate capacitance and is, therefore, free from the limitations and potentially more accurate. Furthermore, the gMR method allows for studying and interpreting of the measured dependencies of mobility on the gate voltage, i.e., carrier concentration, and identifying the corresponding scattering mechanisms. In particular, the decrease in mobility at higher carrier concentrations observed in this work is associated with the contribution of the phonon scattering. Finally, we show that the gMR method is applicable even to the GFETs with relatively high series resistance with a specific width-resistivity up to 5.5 k  $\Omega \times \mu m$ .

See the supplementary material for details of a thorough error analysis of the data and a description of the measurements set-up.

This work was supported, in part, by the EU Graphene Flagship Core 3 Project under Grant No. 881603. This work was performed, in part, at Myfab Chalmers and, in part, at the Micronova Nanofabrication Centre. The authors thanks Anamul Md Hoque for assisting them in the laboratory measurements. A.G. and S.A. acknowledge funding from the Academy of Finland (Grant Nos. 343842 and 314809), and A.M. and M.S. acknowledge funding from the Graphene Flagship 2D Experimental Pilot Line. The authors also thank Professors Jan Stake and Kjell Jeppson for fruitful discussions and Professor Niklas Rorsman for help with measurements, constructive feedback during discussions, and the writing process. The authors also thank Dr. Muhammad Asad for his assistance in the GFET design and fabrication techniques.

### AUTHOR DECLARATIONS Conflict of Interest

The authors have no conflicts to disclose.

#### **Author Contributions**

**Isabel Hanna Harrysson Rodrigues:** Conceptualization (lead); Data curation (lead); Formal analysis (lead); Investigation (lead); Methodology (lead); Software (lead); Validation (lead); Visualization

(lead); Writing – original draft (lead); Writing – review and editing (lead). Andrey Generalov: Data curation (equal); Formal analysis (equal); Methodology (equal); Resources (equal); Writing – review and editing (equal). Miika Soikkeli: Resources (equal); Supervision (equal). Anton Murros: Resources (equal); Writing – review and editing (equal). Sanna Arpiainen: Funding acquisition (equal); Resources (equal); Supervision (equal). Andrei Vorobiev: Conceptualization (equal); Formal analysis (equal); Funding acquisition (equal); Methodology (equal); Project administration (equal); Resources (equal); Supervision (equal); Writing – original draft (equal); Writing – review and editing (equal).

#### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

- <sup>1</sup>J.-H. Chen, C. Jang, S. Xiao, M. Ishigami, and M. S. Fuhrer, "Intrinsic and extrinsic performance limits of graphene devices on SiO<sub>2</sub>," Nat. Nanotechnol. 3, 206–209 (2008).

- <sup>2</sup>S. D. Sarma, S. Adam, E. H. Hwang, and E. Rossi, "Electronic transport in two-dimensional graphene," Rev. Mod. Phys. 83, 407–470 (2011).

- <sup>3</sup>A. S. Mayorov, R. V. Gorbachev, S. V. Morozov, L. Britnell, R. Jalil, L. A. Ponomarenko, P. Blake, K. S. Novoselov, K. Watanabe, T. Taniguchi, and A. K. Geim, "Micrometer-scale ballistic transport in encapsulated graphene at room temperature," Nano Lett. 11, 2396–2399 (2011).

- <sup>4</sup>F. Schwierz, "Graphene transistors: Status, prospects, and problems," Proc. IEEE 101, 1567–1584 (2013).

- <sup>5</sup>M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier, and J. Stake, "Graphene field-effect transistors with high extrinsic  $f_T$  and  $f_{\text{max}}$ ," IEEE Electron Device Lett. **40**, 131–134 (2019).

- <sup>6</sup>M. Asad, S. Majdi, A. Vorobiev, K. Jeppson, J. Isberg, and J. Stake, "Graphene FET on diamond for high-frequency electronics," IEEE Electron Device Lett. 43, 300–301 (2022).

- M. Bonmann, A. Vorobiev, M. A. Andersson, and J. Stake, "Charge carrier velocity in graphene field-effect transistors," Appl. Phys. Lett. 111, 233505 (2017).

- 8S. Adam, E. H. Hwang, V. M. Galitski, and S. D. Sarma, "A self-consistent theory for graphene transport," Proc. Natl. Acad. Sci. 104, 18392–18397 (2007).

- <sup>9</sup>M. Asad, M. Bonmann, X. Yang, A. Vorobiev, K. Jeppson, L. Banszerus, M. Otto, C. Stampfer, D. Neumaier, and J. Stake, "The dependence of the high-frequency performance of graphene field-effect transistors on channel transport properties," IEEE J. Electron Devices Soc. 8, 457–464 (2020).

- <sup>10</sup>I. Meric, M. Han, A. Young *et al.*, "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," Nat. Nanotechnol. 3, 654–659 (2008).

- <sup>11</sup>S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, "Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," Appl. Phys. Lett. **94**, 062107 (2009).

- <sup>12</sup>H. Zhong, Z. Zhang, H. Xu, C. Qiu, and L.-M. Peng, "Comparison of mobility extraction methods based on field-effect measurements for graphene," AIP Adv. 5, 057136 (2015).

- <sup>13</sup>M. Bonmann, A. Vorobiev, J. Stake, and O. Engström, "Effect of oxide traps on channel transport characteristics in graphene field effect transistors," J. Vac. Sci. Technol., B 35, 01A115 (2017).

- <sup>14</sup>W. Masselink, W. Kopp, T. Henderson, and H. Morkoc, "Measurement of the electron velocity-field characteristic in modulation-doped structures using the geometrical magnetoresistance method," IEEE Electron Device Lett. 6, 539–541 (1985).

- <sup>15</sup>W. T. Masselink, T. S. Henderson, J. Klem, W. F. Kopp, and H. Morkoc, "Dependence of 77 K electron velocity-field characteristics on low-field mobility in AlGaAs-GaAs modulation-doped structures," IEEE Trans. Electron Devices 33, 639 (1986).

- <sup>16</sup>D. K. Schroder, Semiconductor Material and Device, 3rd ed. (Wiley-IEEE Press, 2006), p. 481.

- <sup>17</sup>M. Sakowicz, R. Tauk, J. Lusakowski, A. Tiberj, W. Knap, Z. Bougrioua, M. Azize, P. Lorenzini, K. Karpierz, and M. Grynberg, "Low temperature electron mobility and concentration under the gate of AlGaN/GaN field effect transistors," J. Appl. Phys. 100, 113726 (2006).

- <sup>18</sup>I. H. Rodrigues and A. Vorobiev, "Low-field mobility and high-field velocity of charge carriers in InGaAs/InP high-electron-mobility transistors," IEEE Trans. Electron Devices 69, 1786–1791 (2022).

- <sup>19</sup>See https://www.graphenea.com "Graphenea" (2010).

- <sup>20</sup>K. Nagashio and A. Toriumi, "Density-of-states limited contact resistance in graphene field-effect transistors," Jpn. J. Appl. Phys., Part 1 50, 070108 (2011)

- <sup>21</sup>J. Lusakowski, W. Knap, Y. Meziani, J.-P. Cesso, A. E. Fatimy, R. Tauk, N. Dyakonova, G. Ghibaudo, F. Boeuf, and T. Skotnicki, "Electron mobility in quasi-ballistic Si MOSFETs," Solid-State Electron. 50, 632–636 (2006).

- <sup>22</sup>V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," Appl. Phys. Lett. **97**, 082112 (2010).

- 23F. Giannazzo, S. Sonde, R. L. Nigro, E. Rimini, and V. Raineri, "Mapping the density of scattering centers limiting the electron mean free path in graphene," Nano Lett. 11, 4612–4618 (2011).

- <sup>24</sup>S. Bidmeshkipour, A. Vorobiev, M. A. Andersson, A. Kompany, and J. Stake, "Effect of ferroelectric substrate on carrier mobility in graphene field-effect transistors," Appl. Phys. Lett. 107, 173106 (2015).

- <sup>25</sup>W. Kim, J. Riikonen, C. Li, Y. Chen, and H. Lipsanen, "Highly tunable local gate controlled complementary graphene device performing as inverter and voltage controlled resistor," Nanotechnology 24, 395202 (2013).

- <sup>26</sup>M. Groner, J. Elam, F. Fabreguette, and S. George, "Electrical characterization of thin Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition on silicon and various metal substrates," Thin Solid Films 413, 186–197 (2002).