## An optimized parameter design method of SiC/Si hybrid switch considering turn-off current spike

Citation for the original published paper (version of record):

Qin, H., Xie, S., Xun, Q. et al (2022). An optimized parameter design method of SiC/Si hybrid switch considering turn-off current spike. Energy Reports, 8: 789-797. http://dx.doi.org/10.1016/j.egyr.2022.08.029

N.B. When citing this work, cite the original published paper.

#### Available online at www.sciencedirect.com

## **ScienceDirect**

Energy Reports 8 (2022) 789-797

www.elsevier.com/locate/egyr

The 5th International Conference on Electrical Engineering and Green Energy CEEGE 2022, 8–11 June, Berlin, Germany

# An optimized parameter design method of SiC/Si hybrid switch considering turn-off current spike

Haihong Qin<sup>a,\*</sup>, Sixuan Xie<sup>a</sup>, Qian Xun<sup>b</sup>, Fanghua Zhang<sup>a</sup>, Zhenxiang Xu<sup>c</sup>, Lingyan Wang<sup>c</sup>

<sup>a</sup> College of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 211106, China <sup>b</sup> Division of Electric Power Engineering, Department of Electrical Engineering, Chalmers University of Technology, Hörsalsvägen 11, Gothenburg, SE-41279, Sweden

<sup>c</sup> Beijing Institute of Precision Mechatronics and Controls, Beijing 100071, China

Received 18 July 2022; accepted 5 August 2022 Available online xxxx

#### Abstract

In order to reduce the switching loss of SiC MOSFET/Si IGBT (SiC/Si) hybrid switch, the switching mode that turn off the Si IGBT prior to the SiC MOSFET is generally adopted to achieved the zero-voltage switching operation of IGBT. The minority carrier in N-base region of the IGBT are recombined in the form of exponential attenuation due to the conductivity modulation effect. When the SiC MOSFET is turned off, if the carrier recombination process of the IGBT is not finished, it needs to bear a large collector–emitter voltage change rate, resulting in apparent current spike. This current spike will increase the current stress of the device and produce additional turn-off loss. The equivalent model of double pulse test circuit of SiC/Si hybrid switch considering parasitic parameters is established, and the turn-off transient process is given analytically. The influence of turn-off delay time, circuit parameters and working conditions on current spike are analysed quantitatively. Combined with the consideration of device stress and comprehensive turn-off loss, an optimized circuit design method of SiC/Si hybrid switch considering turn-off current peak is proposed, which provides theoretical and design guidance for high reliability and high efficiency SiC/Si-based converters.

© 2022 The Authors. Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

Peer-review under responsibility of the scientific committee of the 5th International Conference on Electrical Engineering and Green Energy, CEEGE, 2022.

Keywords: SiC MOSFET; Si IGBT; Hybrid switch; Switching loss; Parameter optimization

#### 1. Introduction

Silicon (Si) Insulated-Gate-Bipolar Transistor (IGBT) is commonly used as power device in high power converter, but its high turning-off loss limits the development of the converter to high frequency and miniaturization. Silicon carbide (SiC) Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) has the advantages of lower on-resistance, faster switching speed and higher temperature resistance, and has broad application prospects in the fields of electric vehicles, new energy power generation [1–4].

https://doi.org/10.1016/j.egyr.2022.08.029

2352-4847/© 2022 The Authors. Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

Peer-review under responsibility of the scientific committee of the 5th International Conference on Electrical Engineering and Green Energy, CEEGE, 2022.

<sup>\*</sup> Corresponding author.

E-mail address: qinhaihong@nuaa.edu.cn (H. Qin).

However, due to the constraints of wafer fabrication and manufacturing process, the current level of existing SiC devices are still lower than that of Si IGBT [5,6]. Therefore, in order to take advantage of the conduction characteristics of Si IGBT under high current and the switching characteristics of SiC MOSFET, researchers have proposed a hybrid parallel structure based on SiC/Si devices [7]. At present, for SiC/Si hybrid switch, researchers have carried out research on their electrical characteristics, switching mode optimization, current level ratio and so on. Ref. [8] analysed the static and dynamic characteristics of SiC/Si switch, and proved that compared with the full SiC scheme, hybrid switch can increase short-circuit withstand capacity, reduce power loss and total cost. Ref. [9] combined variable switching mode and variable PWM frequency strategy, by reducing the switching frequency near the peak current region, it can not only ensure that SiC device does not bear overcurrent stress, but also reduce the switching loss introduced by IGBT, but did not consider the influence of different turn on/off delay time on the switching loss of SiC/Si hybrid switch. Junction temperature of SiC/Si hybrid switch realized balance by optimizing the switching control strategy [10] and multi-objective optimization control strategy based on the loss model [11]. However, the loss introduced by the turn-off current spike of Si IGBT is calculated by experimental fitting in [10,11], which is not accurate enough. In [12], the influence of parasitic inductance imbalance on the internal static current sharing time of the device was described, but no detailed loss modelling was performed for the switching process. In [13], researchers proposed the current ratio optimization design method of SiC/Si hybrid switch and pointed out that with the increase of turn-off delay time, the loss introduced by IGBT current peak will decrease, but the turn-off current peak value under different turn-off delay time was not given.

According to the turn-off current spike and circuit parameter design of Si IGBT, the presence of turn-off current spikes was pointed out in [14] by analysing the switching modes of SiC/Si hybrid switch, and [15] evaluated the turn-off current spikes at different turn-off delay time, but no studies were performed for other circuit parameters. In [16], the use of simple devices such as resistors and capacitors to achieve delay time regulation was proposed, but the effect of other parameters on the switching characteristics of SiC/Si hybrid switch was not considered. The active driving circuit was designed to optimize the switching characteristics by adjusting circuit parameters such as the switching delay time and the driving voltage of the hybrid switch, but the effect of the parameters on the IGBT turn-off current spikes was not addressed in [17]. Since the turn-off current spike of Si IGBT increases both the device current stress and the power loss of the hybrid switch, and also affect the setting of the dead time in the phase-leg configuration, it is important to evaluate the turn-off current spike to improve efficiency and ensure reliable converter operation.

Based on the above problems, this paper firstly considers the influence of parasitic parameters and analyses the turn-off transient process of SiC/Si hybrid switch. Secondly, the influencing factors of IGBT turn-off current spike are studied and analysed. Then, a parameter optimization design method is proposed by combining reliability and comprehensive loss optimization as the guideline. Finally, experiments are conducted by a double-pulse test platform to verify the correctness of the theoretical analysis and the proposed design method.

#### 2. Turn-off transient modelling of SiC/Si hybrid switch

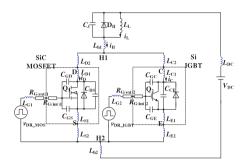

The schematic diagram of SiC/Si hybrid switch is shown in Fig. 1, in which:  $V_{DR.MOS}$ ,  $V_{DR.IGBT}$  are the gate drive voltage of SiC MOSFET and Si IGBT;  $T_{on.delay}$ ,  $T_{off.delay}$  are the turn-on delay time and turn-off delay time between SiC MOSFET and Si IGBT, respectively. In order to fully utilize the switching characteristic advantages of SiC MOSFET, the switching mode as shown in Fig. 1 is generally used. In this switching mode, since the turn-on speed of Si IGBT is slower than that of SiC MOSFET, Si IGBT can turn on at zero voltage when the turn-on delay time is zero. Also, since the Si IGBT turns off before the SiC MOSFET, the Si IGBT can achieve zero-voltage turn-off.

In order to analyse the turn-off process of SiC/Si hybrid switch thoroughly, we take the double-pulse test circuit shown in Fig. 2 as an example and models the turn-off transient for SiC/Si hybrid switch in segments considering the main parasitic parameters in the circuit. In the figure:  $V_{\rm DC}$  is the bus voltage,  $I_{\rm L}$  is the load current.  $D_{\rm H}$  is the ideal SiC SBD,  $C_{\rm J}$  is the junction capacitance;  $C_{\rm GS}$ ,  $C_{\rm GD}$  and  $C_{\rm DS}$  are the capacitance of SiC MOSFET.  $C_{\rm GE}$ ,  $C_{\rm GC}$  and  $C_{\rm CE}$  are the capacitance of Si IGBT.  $L_{\rm D1}$ ,  $L_{\rm S1}$ ,  $L_{\rm C1}$ ,  $L_{\rm E1}$  are the parasitic inductors introduced by the device package,  $L_{\rm G1}$ ,  $L_{\rm G2}$  are the gate loop parasitic inductors,  $R_{\rm G(int)1}$ ,  $R_{\rm G(int)2}$  are the gate internal resistance,  $R_{\rm G(ext)1}$ ,  $R_{\rm G(ext)2}$  are the external driving resistance;  $L_{\rm h1}$ ,  $L_{\rm h2}$ ,  $L_{\rm D2}$ ,  $L_{\rm C2}$ ,  $L_{\rm S2}$ ,  $L_{\rm E2}$  are the stray inductors introduced by the PCB layout.

Fig. 1. Schematic diagram of SiC/Si hybrid switch.

Fig. 2. Double pulse test circuit for SiC/Si hybrid switch considering parasitic parameters.

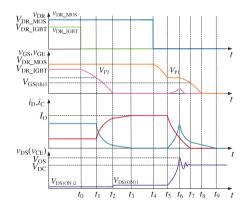

The turn-off waveform of the SiC/Si hybrid switch considering the parasitic parameters is shown in Fig. 3, from top to bottom: driving signal  $v_{DR\_MOS}$  and  $v_{DR\_IGBT}$ , gate voltage  $v_{GS\_MOS}$  and  $v_{GS\_IGBT}$ , drain current  $i_D$  and collector current  $i_C$ , and drain-source voltage  $v_{DS}$ . The turn-off process can be divided into nine stages according to the current-voltage variation.

Fig. 3. Turn-off waveform of SiC/Si switch considering parasitic parameters.

Stage1[ $t_0 \sim t_1$ ]: At  $t_0$ , the Si IGBT driving signal steps to zero, and its equivalent input capacitance  $C_{ISS2}$  (=  $C_{GE} + C_{GC}$ ) starts to discharge through the driving resistance  $R_{G2}$  (=  $R_{G(int)2} + R_{G(ext)2}$ ), and the gate voltage  $v_{GE}$  starts to decrease. However, before  $v_{GE}$  decreases to  $V_{P2}$ , the IGBT works in the linear region, and the collector current  $i_C$  and the collector voltage  $v_{CE}$  remain unchanged. The time of this phase can be expressed as:

$$t_1 - t_0 = R_{G2} C_{ISS2} \ln(\frac{V_{TH2} + I_O/g_{fs}}{V_{DR.IGBT}})$$

(1)

Stage2[ $t_1 \sim t_2$ ]: At  $t_1$ , the gate voltage  $v_{\text{GE}}$  of the Si IGBT decreases to  $V_{\text{P2}}$ , the channel starts to shut down. The collector voltage  $v_{\text{CE}}$  is clamped by the on-state voltage drop  $V_{\text{DS(ON)2}}$ , so  $v_{\text{CE}}$  does not rise. The collector current  $i_{\text{C}}$  starts to fall, at which time the current is gradually transferred to the SiC MOSFET, and the drain current  $i_{\text{D}}$  starts to rise until the moment  $t_2$ , when the Si IGBT enters the turn-off trailing current phase.

Stage3[ $t_2 \sim t_3$ ]: At  $t_2$ , the Si IGBT enters the turn-off trailing current phase and the equivalent MOSFET channel within the IGBT is completely shut down. Since there is only one carrier conducting in the IGBT, the low mobility of the minority carriers (holes) in the drift region can only disappear by compounding, so the collector current  $i_C$ decreases slowly, resulting in a trailing current phenomenon with a relatively long time. Obviously, the length of this period depends mainly on the life of the minority carriers in the drift region. At this time the hybrid device on-state voltage drop also rises to the on-state voltage drop of SiC MOSFET.

Stage4[ $t_3 \sim t_4$ ]: At moment of  $t_3$ , the trailing current in the Si IGBT basically disappears and the SiC MOSFET undertakes the load current.

Stage5[ $t_4 \sim t_5$ ]: At  $t_4$ , the SiC MOSFET driving signal steps to zero, its equivalent input capacitance  $C_{ISS1}$  (=  $C_{\rm GS} + C_{\rm GD}$ ) starts to discharge through the driving resistance  $R_{\rm GI}$  (=  $R_{\rm G(int)1} + R_{\rm G(ext)1}$ ), and the MOSFET gate voltage  $v_{GS}$  starts to decrease. But before  $v_{GS}$  decreases to  $V_{P1}$ , SiC MOSFET works in the linear region, and the drain current  $i_D$  and the drain-source voltage  $v_{DS}$  remain constant. The time can be expressed as:

$$t_5 - t_4 = R_{\rm G1} C_{\rm ISS1} \ln(\frac{V_{\rm TH1} + I_{\rm O}/g_{\rm fs}}{V_{\rm DR.MOS}})$$

(2)

Stage6[ $t_5 \sim t_6$ ]: At  $t_5$ , the voltage  $v_{GS}$  drops to the voltage  $V_{P1}$  and remains constant during this phase, the voltage  $v_{\rm DS}$  rises slowly and the current  $i_{\rm D}$  starts to drop, with the load current discharging the junction capacitance  $C_{\rm J}$  and output capacitance  $C_{OSS2}$  (=  $C_{CE} + C_{GC}$ ). At the same time, the remnant carriers in the IGBT need to withstand the high turn-off dv/dt of SiC MOSFET, so there will be a very high rate of carrier extraction, thus causing the current spike of the IGBT. The magnitude of its carrier compound extraction current is related to the lifetime of the remnant carriers. In addition, the displacement current of the  $C_{GC}$  charge causes a forward spike in the voltage  $v_{\rm GE}$ . The time of this phase can be expressed as:

$$t_6 - t_5 = \frac{Q_{\text{GD}} \cdot R_{\text{G1}}}{V_{\text{Pl}}} \tag{3}$$

Stage7[ $t_6 \sim t_7$ ]: After the voltage  $v_{DS}$  stabilizes, the SiC MOSFET works in the saturation region. The current  $i_{\rm C}$  and  $i_{\rm D}$  continue to fall, the voltage  $v_{\rm GS}$  continues to fall to  $V_{\rm GS(th)1}$ , and the current  $i_{\rm D}$  drops to zero at  $t_{\rm 7}$ . The duration of this phase is:

$$t_7 - t_6 = R_{G1} C_{ISS1} \ln \frac{V_{P1}}{V_{GS(th)1}}$$

(4)

Stage8[ $t_7 \sim t_8$ ]: At  $t_7$ , the voltage  $v_{GS}$  continues to drop from the threshold voltage  $V_{TH1}$  and the SiC MOSFET is shut down. The carrier complex current of the Si IGBT continues to drop.

Stage9[ $t_8 \sim t_9$ ]: At  $t_9$ , all the load current is transferred into the diode. The duration of this phase depends on the carrier compound rate of the IGBT.

The turn-off loss  $E_{\text{off}}$  of SiC/Si hybrid switch consists of three main components, which are SiC MOSFET hard turn-off loss  $E_{\text{off,MOS}}$ , SiC MOSFET additional conduction loss  $\Delta E_{\text{con,MOS,off}}$  during the turn-off delay time, and the loss caused by Si IGBT turn-off current spike  $E_{\text{off,IGBT}}$ . The expression of each component loss are as follows.

$$E_{\text{off}} = E_{\text{off MOS}} + \Delta E_{\text{con MOS off}} + E_{\text{off IGBT}}$$

(5)

$$E_{\text{off}} = E_{\text{off\_MOS}} + \Delta E_{\text{con\_MOS\_off}} + E_{\text{off\_IGBT}}$$

$$E_{\text{off\_MOS}} = \int_{T_{\text{off\_delay}}}^{T_{\text{off\_delay}} + t_{\text{off\_MOS}}} v_{\text{DS}} \cdot i_{\text{D}} dt$$

$$\Delta E_{\text{con\_MOS\_off}} = \int_{0}^{T_{\text{off\_delay}}} v_{\text{DS}} \cdot i_{\text{D}} dt$$

$$(5)$$

$$(6)$$

$$\Delta E_{\text{con\_MOS\_off}} = \int_{0}^{T_{\text{off\_delay}}} v_{\text{DS}} \cdot i_{\text{D}} dt \tag{7}$$

$$E_{\text{off.IGBT}} = (E_{\text{hard.off.IGBT}} - E_{\text{res.off}}) \cdot e^{-\tau \cdot t_{\text{off.delay}}} + E_{\text{res.off}}$$

(8)

where: toff.MOS and toff.IGBT are the turn-off time of SiC MOSFET and Si IGBT. Eoff.hard.IGBT is the hard turn-off loss of Si IGBT,  $E_{res.off}$  is the loss of parasitic capacitor charging when Si IGBT is subjected to bus voltage,  $\tau$  is the time constant of Si IGBT turn-off loss, and the magnitude is related to the carrier lifetime in the Si IGBT, which can be obtained by fitting the double pulse experiment.

The analysis shows that the rise of the voltage  $v_{DS}$  causes the current spike due to the parasitic capacitance charging and carrier compounding. Since the degree of remnant carrier compounding in IGBTs is related to the operating conditions and compounding time, the turn-off delay time  $T_{\rm off.delay}$  also affects the turn-off current spikes. The turn-off current spike is also affected by dv/dt, so the SiC MOSFET driving circuit parameters also affect the current spike.

## 3. Analysis of influencing factors on the turn-off current spike

According to the analysis in the previous section, the influencing factors of the IGBT turn-off current spike include the remnant carrier compound degree and the drain-source voltage variation rate dv/dt. In this section, the LTspice simulation software is used to investigate the influence law of the influencing factors of the turn-off current spikes. The power devices used in the simulation are Rohm 650 V/27 A SiC MOSFET (SCT3060AL) and Infineon 600 V/40 A Si IGBT (IKW40N60H3), and the simulation parameters are set as shown in Table 1.

| <b>Table 1.</b> Parameter values of SiC/Si hybrid switch simula |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| Parameter                                         | Value | Parameter                                         | Value |

|---------------------------------------------------|-------|---------------------------------------------------|-------|

| Bus voltage $V_{\rm DC}/{\rm V}$                  | 350   | Driving voltage of MOSFET V <sub>DR_MOS</sub> /V  | 18/-2 |

| Load current I <sub>O</sub> /A                    | 25    | Driving resistance of MOSFET $R_{G1}/\Omega$      | 12    |

| Turn-on delay time $T_{\text{on\_delay}}/\mu s$   | 0     | Gate parasitic inductance $L_{G1}$ , $L_{G2}$ /nH | 40    |

| Turn-off delay time $T_{\text{off\_delay}}/\mu s$ | 0.5   | Equivalent junction capacitance $C_J/pF$          | 80    |

## 3.1. Turn-off delay time

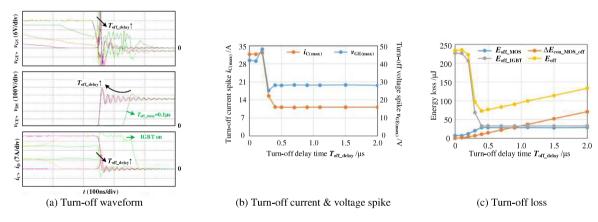

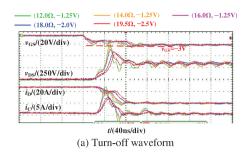

The turn-off waveforms of SiC/Si hybrid switch with different turn-off delay time  $T_{\rm off\_delay}$  are shown in Fig. 4(a). When  $T_{\rm off\_delay} = 0.1~\mu s$ , due to the slower turn-off speed of Si IGBT, when the SiC MOSEFT is completely turn off, the load current is all transferred to the IGBT, which makes the Si IGBT produce hard switching loss, while the drain-source voltage  $v_{\rm DS}$  change phase is delayed. As  $T_{\rm off\_delay}$  increases, the turn-off current spike decreases from 31.63 A to 11.16 A, at the same time, the voltage spike of  $v_{\rm DS}$  increases and stabilizes at about 480 V.

Fig. 4. Effect of turn-off delay time on turn-off characteristics of SiC/Si hybrid switch.

As can be seen from Fig. 4, under the condition that dv/dt is basically constant, when  $T_{\rm off.delay} \le 0.2~\mu s$ , the Si IGBT turns off after SiC MOSFET, the voltage drop generated by the common source parasitic inductance in the Si IGBT package with large di/dt interaction causes the peak of  $v_{\rm GE}$ . When  $T_{\rm off.delay} > 0.2~\mu s$ , the SiC MOSFET turn off later and the peak of  $v_{\rm GE}$  tends to be constant. When  $T_{\rm off.delay} < 0.9~\mu s$ , the current spike and its resulting loss  $E_{\rm off.IGBT}$  decreases as  $T_{\rm off.delay}$  increases. When  $T_{\rm off.delay} > 0.9~\mu s$ , the degree of Si IGBT carrier compound will be independent of time, the current spike and  $E_{\rm off.IGBT}$  no longer decreases, but will increase the additional conduction loss of SiC MOSFET. According to the curve of turn-off loss  $E_{\rm off}$  can be seen that there is a loss optimal point, comprehensive consideration of turn-off current spike and  $E_{\rm off}$ ,  $T_{\rm off.delay}$  is recommended to be 0.4  $\mu s$ .

## 3.2. Turn-off driving voltage of SiC MOSFET

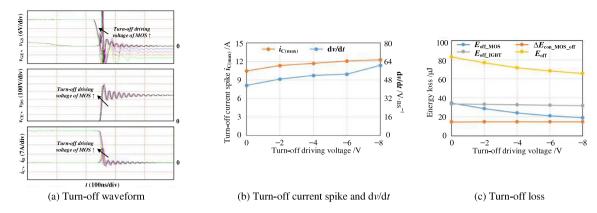

The SiC/Si hybrid switch turn-off waveforms when the turn-off driving voltage of SiC MOSFET is taken as 0 V, -2 V, -4 V, -6 V and -8 V are shown in Fig. 5(a). As the absolute value of the turn-off driving voltage increases,

Fig. 5. Effect of SiC MOSFET's driving voltage on turn-off characteristics of SiC/Si hybrid switch.

it has little effect on the turn-off current variation rate di/dt, and the turn-off drain-source voltage spike is basically unchanged. At the same time, the dv/dt of the voltage  $v_{DS}$  increases slightly and the remnant carrier extraction rate of the IGBT increases making the IGBT turn-off current spike increase from 10.45 A to 12.28 A.

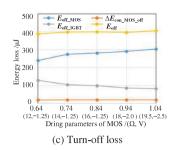

As can be seen from Fig. 5, as the turn-off driving voltage of SiC MOSFET increases, the hard turn-off loss  $E_{\text{off\_MOS}}$  decreases and the additional conduction loss  $\Delta E_{\text{con\_MOS\_off}}$  remains essentially unchanged. Since the current spike of IGBT changes insignificantly,  $E_{\text{off\_IGBT}}$  remains basically the same, and then the total turn-off loss  $E_{\text{off}}$  increases.

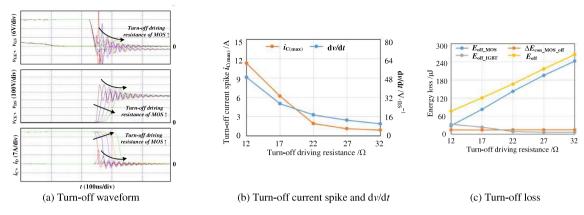

## 3.3. Turn-off driving resistance of SiC MOSFET

Considering that the SiC MOSFET device selected in this paper has 12  $\Omega$  gate internal resistance, the SiC/Si hybrid switch turn-off waveform is shown in Fig. 6(a) when its turn-off driving resistance is taken as 12  $\Omega$ , 17  $\Omega$ , 22  $\Omega$ , 27  $\Omega$  and 32  $\Omega$ , respectively. As the turn-off driving resistance increases, the voltage drop across the power loop inductor decreases and the turn-off drain-source voltage spike decreases from 500 V to 440 V due to the decrease of di/dt. At the same time, the variation rate dv/dt of turn-off drain-source voltage is significantly reduced, and the reduced rate of remnant carrier extraction for IGBT makes the IGBT turn-off current spike reduced from 11.32 A to 0.92 A.

As can be seen from Fig. 6, the hard turn-off loss  $E_{\rm off\_MOS}$  increases significantly as the turn-off driving resistance increases, and the additional conduction loss  $\Delta E_{\rm con\_MOS\_off}$  remains essentially unchanged. Since the variation of the turn-off current spike decreases,  $E_{\rm off\_IGBT}$  will also decrease as the turn-off driving resistance increases. The total turn-off loss  $E_{\rm off}$  increases because the driving resistance has a greater effect on the hard turn-off loss  $E_{\rm off\_MOS}$ .

#### 4. Parameter optimization design method and experimental verification

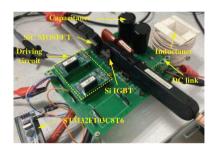

In order to verify the effects of the parameter optimization design method on the Si IGBT turn-off current spikes and integrated losses, a double-pulse experimental platform as shown in Fig. 7 is built to test the turn-off characteristics of SiC/Si hybrid switch. The power devices used in the experiment are Rohm 650 V/27 A SiC MOSFET (SCT3060AL), Infineon 600 V/40 A Si IGBT (IKW40N60H3) and Rohm 600 V/40 A SiC SBD (SCS240AE).

#### 4.1. Optimization design method of turn-off delay time

For SiC/Si hybrid switch, the increase of the turn-off delay time  $T_{\rm off\_delay}$  leads to a linear increase of the additional conduction loss  $\Delta E_{\rm con\_MOS\_off}$  of SiC MOSFET and a nonlinear decrease of the turn-off current spike loss  $E_{\rm off\_IGBT}$  of IGBT, so there is an optimal turn-off loss  $E_{\rm off}$ , and the optimal turn-off delay time  $T_{\rm off\_delay}$  is selected based on the "comprehensive turn-off loss optimization principle".

Fig. 6. Effect of SiC MOSFET's driving resistance on turn-off characteristics of SiC/Si hybrid switch.

Fig. 7. Double-pulse experimental platform for SiC/Si hybrid switch.

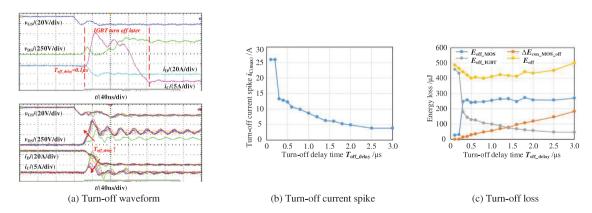

Fig. 8 shows the turn-off characteristics when the turn-off delay time  $T_{\rm off\_delay}$  is 0.1  $\mu s \sim 3.0 \,\mu s$ . Fig. 9(a) shows the turn-off waveforms when the turn-off delay is 0.1  $\mu s$ , 0.5  $\mu s$ , 1.0  $\mu s$ , 1.5  $\mu s$ , 2.0  $\mu s$ , 2.5  $\mu s$ , 3.0  $\mu s$ , respectively. It can be seen that when the turn-off delay  $T_{\rm off\_delay} = 0.1 \,\mu s$ , the IGBT turn-off time  $t_{\rm off\_IGBT}$  is less than 0.1  $\mu s$ , so the IGBT turn off later and generates 450  $\mu J$  hard turn-off loss. With the increase of the turn-off delay time, the turn-off current spike decreases from 13.3A to 3.9 A, which reduces the loss caused by the IGBT turn-off current spike by 73.23%. Therefore, for the working condition of 350 V/25 A, a turn-off delay time of 0.5  $\mu s$  is recommended for considering the comprehensive turn-off loss  $E_{\rm off}$ , which is very close to the simulation results.

Fig. 8. Experimental results with different turn-off delay time.

Fig. 9. Experimental results with different driving parameters of SiC MOSFET.

### 4.2. Optimization design method of driving parameters

Due to the presence of parasitic inductance in the driving circuit of power devices, it will cause second-order oscillation. So reasonable driving resistance and driving voltage are required to ensure gate reliability. Therefore, the driving circuit parameters of SiC/Si hybrid switch need to be optimized considering gate reliability, IGBT turn-off current spike and turn-off loss. Since zero voltage switching is realized when SiC/Si hybrid switch is in the switching mode that the IGBT turn off firstly, the driving circuit parameters of IGBT has little effect on the turn-off characteristics of SiC/Si hybrid switch, we mainly optimize the driving circuit parameters of SiC MOSFET.

For the optimization design of the driving parameters, first, the maximum negative gate voltage  $V_{\rm GS(-max)}$  should be limited, then the driving circuit parameters are adjusted and the optimized parameters are selected according to the "comprehensive turn-off loss optimization principle". Obviously, as the driving resistance increases, the driving voltage can be increased accordingly.

For SiC MOSFET driving circuit parameters, increasing the turn-off driving resistance  $R_{\rm GI}$  can be more effective to reduce  ${\rm d}v/{\rm d}t$  than increasing the turn-off driving voltage  $V_{\rm DR\_MOS-}$ , thus it should be more effective to suppress IGBT turn-off current spike and reduce  $E_{\rm off\_IGBT}$ , but will cause very large  $E_{\rm off\_MOS}$ . However, considering the comprehensive turn-off loss  $E_{\rm off}$ ,  $R_{\rm GI}$  can still not be too large.

Similarly, while increasing the turn-off driving voltage  $V_{DR\_MOS-}$  can reduce the loss caused by current spike  $E_{off\_IGBT}$ , the low negative gate withstand voltage of the SiC MOSFET and the severe turn-off oscillations caused by the fast turn-off speed make it difficult to change the driving voltage significantly.

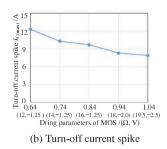

In order to find the optimal combination of driving parameters, the turn-off characteristics are shown in Fig. 9 when  $V_{\rm GS(-max)} = -3{\rm V}$  and the driving loop damping ratios of SiC MOSFET are set to be 0.64, 0.74, 0.84, 0.94 and 1.04, respectively, under the condition that  $L_{\rm GI}$  is 42 nH. As the driving resistance increases, the turn-off speed of SiC MOSFET decreases, so the turn-off voltage peak decreases from 760 V to 530 V, which almost decreases by 30.3%, and the turn-off current peak decreases from 12.3 A to 7.9 A, which almost decreases by 35.8%.

Since the SiC MOSFET gate negative withstand voltage is -4 V, the absolute value of turn-off gate voltage spikes larger than 4 V when the driving resistance is less than 16  $\Omega$ , so a 16  $\Omega$  driving resistance is required to suppress the turn-off oscillation in order not to exceed  $V_{\rm GS(-max)}$ . Although adjusting the driving parameters could ensure the gate reliability, increasing  $R_{\rm GI}$  will make the SiC MOSFET turn-off loss  $E_{\rm off\_MOS}$  significantly larger, but at the same time it can reduce the spike loss  $E_{\rm off\_IGBT}$ . From the experimental results, it can be seen that the optimized combination of SiC MOSFET driving parameters that both to ensure reliability and the lowest turn-off loss is (18  $\Omega$ , -2V), and the driving circuit damping ratio is 0.94.

#### 5. Conclusions

In this paper, the influencing factors of IGBT turn-off current spike in SiC/Si hybrid switch are evaluated, and an optimized circuit parameter design method of SiC/Si hybrid switch considering turn-off current spike is given:

- (1) The turn-off current spike of Si IGBT is formed when the remnant carriers in the carrier storage region bear the high dv/dt during the turn off process of SiC MOSFET.

- (2) The influencing factors of Si IGBT turn-off current spike include turn-off delay time and SiC MOSFET driving parameters. Among them, increasing the turn-off delay time, turn-off driving resistance of MOSFET and reducing turn-off driving voltage of MOSFET can effectively suppress the Si IGBT turn-off current spike.

- (3) According to the "comprehensive turn-off loss optimization principle", there is generally an optimal turn-off delay time, and  $0.5~\mu s$  was selected as the optimal turn-off delay time of hybrid switch consisting of SiC MOSFET (SCT3060AL) and Si IGBT (IKW40N60H3).

- (4) For the parameters of SiC MOSFET driving circuit, a damping ratio greater than 0.84 should be first confirmed to ensure the gate reliability, and then respective parameters of driving circuit should be optimized according to the "comprehensive turn-off loss optimization principle".

## **Declaration of competing interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

### Data availability

Data will be made available on request.

## Acknowledgements

This paper is supported financially in part by Zhejiang Science and Technology Project, China under grant Number LGG21E070001, State Key Laboratory of Wide-Bandgap Semiconductor Power Electronic Devices, China, under Grant Number 2019KF001 and in part by National Natural Science Foundation of China under grant Number 51677089.

#### References

- [1] Zhang L, Yuan X, Wu X, Shi C, Zhang J, Zhang Y. Performance evaluation of high-power SiC MOSFET modules in comparison to Si IGBT modules. IEEE Trans Power Electron 2019;34(2):1181–96.

- [2] Wei C, Shao J, Agrawal B, Zhu D, Xie H. New surface mount SiC MOSFETs enable high efficiency high power density Bi-directional on-board charger with flexible DC-link voltage. In: 2019 IEEE applied power electronics conference and exposition (APEC), Anaheim, CA, USA.

- [3] Wang R, Tan L, Li C, Huang T, Li H, Huang X. Analysis, design, and implementation of junction temperature fluctuation tracking suppression strategy for SiC MOSFETs in wireless high-power transfer. IEEE Trans Power Electron 2021;36(1):1193–204.

- [4] Zhaoming Qian, Junming Zhang, Kuang Sheng. Statusand development of power semiconductor devices and its applications. Proc CSEE 2014;34(29):5149–61.

- [5] Sheng H, Chen Z, Wang F, Millner A. Investigation of 1.2 kV SiC MOSFET for high frequency high power applications. In: 2010 twenty-fifth annual IEEE applied power electronics conference and exposition (APEC), Palm Springs, CA, USA. 2010, p. 1572–7.

- [6] Cui Y, Chinthavali MS, Xu F, Tolbert LM. Characterization and modeling of silicon carbide power devices and paralleling operation. In: 2012 IEEE international symposium on industrial electronics, Hangzhou, China.

- [7] Jiang Y, Hua GC, Yang E, Lee FC. Soft-switching of IGBTs with the help of MOSFETs in bridge-type converters. In: Proceedings of IEEE power electronics specialist conference PESC '93, Seattle, WA, USA.

- [8] Rahimo M, Canales F, Minamisawa RA, et al. Characterization of a silicon IGBT and silicon carbide MOSFET cross-switch hybrid. IEEE Trans Power Electron 2015;30(9):4638–42.

- [9] Peng Z, Wang J, Liu Z, et al. A variable-frequency current-dependent switching strategy to improve tradeoff between efficiency and SiC MOSFET overcurrent stress in Si/SiC-hybrid-switch-based inverters. IEEE Trans Power Electron 2021;36(4):4877–86.

- [10] Li Z, Wang J, Deng L, et al. Active gate delay time control of Si/SiC hybrid switch for junction temperature balance over a wide power range. IEEE Trans Power Electron 2020;35(5):5354–65.

- [11] He Z, Li Z, Yu J, Jiang X, Wang J. Multi-objective optimization control strategy for SiC/si hybrid switches. In: 2019 IEEE energy conversion congress and exposition (ECCE), Baltimore, MD, USA.

- [12] Deshpande A, Luo F. Practical design considerations for a si IGBT + SiC MOSFET hybrid switch: Parasitic interconnect influences, cost, and current ratio optimization. IEEE Trans Power Electron 2019;34(1):724–37.

- [13] Li Z, Wang J, Ji B, Shen ZJ. Power loss model and device sizing optimization of Si/SiC hybrid switches. IEEE Trans Power Electron 2020;35(8):8512–23.

- [14] Qin H, Wang D, Zhang Y, Fu D, Zhao C. Characteristics and switching patterns of Si/SiC hybrid switch. In: PCIM Asia 2017; International exhibition and conference for power electronics, intelligent motion, renewable energy and energy management, Shanghai, China

- [15] Qin H, Wang R, Xun Q, Chen W, Xie S. Switching time delay optimization for SiC+Si hybrid device in a phase-leg configuration. IEEE Access 2021;9:37542–56Y.

- [16] Li Z, Dai X, Jiang X, et al. A novel gate driver for Si/SiC hybrid switch for multi-objective optimization. IET Power Electron 2020;14(2):422–31.

- [17] Wei Y, Woldegiorgis D, Sweeting R, Mantooth A. Four control freedoms AGD for hybrid SiC MOSFET and Si IGBT application. In: 2021 IEEE applied power electronics conference and exposition (APEC), Phoenix, AZ, USA.