# Investigation of Isolation Approaches and the Stoichiometry of SiN<inf>x</inf> Passivation Layers in "Buffer-Free" AlGaN/GaN

Downloaded from: https://research.chalmers.se, 2024-04-20 11:43 UTC

Citation for the original published paper (version of record):

Hult, B., Thorsell, M., Chen, J. et al (2023). Investigation of Isolation Approaches and the Stoichiometry of SiN<inf>x</inf> Passivation Layers in "Buffer-Free" AlGaN/GaN Metal–Insulator–Semiconductor High-Electron-Mobility Transistors. Physica Status Solidi (A) Applications and Materials Science, 220(8). http://dx.doi.org/10.1002/pssa.202200533

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

# Investigation of Isolation Approaches and the Stoichiometry of SiN<sub>x</sub> Passivation Layers in "Buffer-Free" AlGaN/GaN Metal–Insulator–Semiconductor High-Electron-Mobility Transistors

Björn Hult,\* Mattias Thorsell, Jr-Tai Chen, and Niklas Rorsman

Critical process modules for the fabrication of metal-insulator-semiconductor high-electron-mobility transistors (MISHEMTs) based on a novel 'buffer-free' AlGaN/GaN heterostructure grown with metal-organic chemical vapor deposition (MOCVD) are presented. The methods of isolation and passivation for this type of heterostructure are investigated. Utilizing nitrogen implantation, it is possible to achieve off-state destructive breakdown voltages (BVs) of 2496 V for gate-drain distances up to 25 µm, whereas mesa isolation techniques limit the BV below 1284 V. The stoichiometry of the SiN, passivation layer displays a small impact on the static and dynamic on-resistance. However, MISHEMTs with Si-rich passivation show off-state gate currents in the range of  $1-100 \,\mu\text{A mm}^{-1}$  at voltages above 1000 V, which is reduced below 10 nA mm<sup>-1</sup> using a stoichiometric SiN<sub>x</sub> passivation layer. Destructive BVs of 1532 and 1742 V can be achieved using gateintegrated and source-connected field plates for MIHEMTs with stoichiometric and Si-rich passivation layers, respectively. By decreasing the field plate lengths, it is possible to achieve BVs of 2200 V. This demonstrates the implementation of MISHEMTs with high-voltage operation and low leakage currents on a novel "buffer-free" heterostructure by optimizing the SiN<sub>x</sub> stoichiometry.

# 1. Introduction

The GaN-based high-electron-mobility transistor (HEMT) is considered a potential candidate for future power electronic

B. Hult, M. Thorsell, N. Rorsman

Department of Microtechnology and Nanoscience

Chalmers University of Technology

Kemivägen 9, 412 96 Gothenburg, Sweden

E-mail: bjornhu@chalmers.se

J.-T. Chen

SweGaN AB

583 30 Linköping, Sweden

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/pssa.202200533.

© 2022 The Authors. physica status solidi (a) applications and materials science published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

#### DOI: 10.1002/pssa.202200533

switching devices due to its high breakdown field and good electron transport properties.<sup>[1]</sup> GaN-based heterostructures are typically grown on Si due to the low manufacturing cost of Si wafers. This necessitates the growth of strain relaxation layers and a thick (Al)GaN buffer layer to reduce the number of extended defects as a result of the large lattice mismatch between GaN and Si.<sup>[2,3]</sup> Unintentionally doped (UID) GaN is typically rendered lightly n-doped due to the incorporation of oxygen atoms or nitrogen vacancies during metal-organic chemical vapor deposition (MOCVD) growth.<sup>[4,5]</sup> This can lead to high vertical off-state currents in GaNon-Si HEMTs, which limit the breakdown voltage (BV). Carbon is typically introduced into the thick buffer layer to reduce these off-state leakage currents. The carbon atoms in the nitrogen site  $(C_N)$  act as a deep acceptor level in GaN,<sup>[6]</sup> which can compensate the unintentional donors and therefore increase the resistivity. However, introduc-

ing high carbon concentrations in the buffer layer has also been associated with dynamic on-resistance ( $R_{on,dyn}$ ) dispersion.<sup>[7,8]</sup>

Previously, we have presented a heterostructure that can avoid carbon-related trapping effects in the GaN layers and, therefore, potentially reduce R<sub>on,dyn</sub>.<sup>[9]</sup> In this heterostructure, no highly doped buffer layer is used. Instead, a 265 nm UID GaN layer is grown between a thin AlGaN barrier layer and an AlN nucleation layer. Furthermore, the AlGaN/GaN/AlN heterostructure is grown on a semi-insulating SiC substrate, providing good vertical isolation. Although the cost of semi-insulating SiC substrates is high relative to Si substrates, the advantages of using the buffer-free heterostructure on SiC include improved lattice mismatch between GaN and the substrate, reduced epitaxial growth time, higher thermal conductivity and a lower thermal resistance between the active region and the substrate (due to a thinner GaN layer). Moreover, technological improvements in SiC substrate growth have rapidly increased due to increasing demands for SiC-based power electronic diodes and transistors, which have led to a reduced cost for SiC substrates. Therefore, GaN-on-SiC HEMTs could become an alternative to GaN-on-Si HEMTs in future power electronic switching devices. Power electronic GaN-on-SiC HEMTs can also be cointegrated with

microwave electronics. In such applications, semi-insulating SiC substrates may be more advantageous due to their superior thermal and insulating properties. However, to realize high-voltage operation with low  $R_{\rm on,dyn}$  on this new material, both the passivation layer and the isolation of the active areas have to be optimized. In this article, we investigate different isolation approaches and the effect of different stoichiometries in the SiN<sub>x</sub> passivation layer.

ADVANCED SCIENCE NEWS \_\_\_\_\_

Besides buffer-related trapping effects, surface states have been shown to cause current collapse and Ron,dyn dispersion in GaN HEMTs,<sup>[10]</sup> resulting in increased on-state losses. Surface-related trapping effects can be mitigated through proper surface treatments and the deposition of a passivation layer.<sup>[10]</sup> SiNx, deposited with either plasma-enhanced chemical vapor deposition (PECVD) or low-pressure chemical vapor deposition (LPCVD), is commonly used as a passivation layer. The  $SiN_x$  passivation layer provides a positive charge to the (Al)GaN surface that neutralizes the negative polarization surface charge.<sup>[11]</sup> In addition, LPCVD SiN<sub>x</sub> provides a high interface quality and reduced oxygen content at the SiN<sub>x</sub>/(Al)GaN interface, making it the preferred choice for GaN-based HEMTs.<sup>[12]</sup> Stoichiometric  $SiN_x$  (Si<sub>3</sub>N<sub>4</sub>), as opposed to Si-rich  $SiN_x$ , improves the isolation and suppresses off-state gate leakage currents.<sup>[13]</sup> However, it has been suggested that GaN HEMTs with carbon-doped buffer layers are susceptible to greater  $R_{on,dyn}$  dispersion when depositing stoichio-metric SiN<sub>x</sub> passivation layers.<sup>[13,14]</sup> This is caused by a change in the conductivity in the GaN epi due to the diffusion of hydrogen ions through the GaN epi during the deposition of the SiN<sub>x</sub> passivation laver.<sup>[15]</sup> Therefore, highly insulating passivation layers could potentially be used without compromising Ron,dyn in the "buffer-free" heterostructure without carbon doping. Here, AlGaN/GaN metal-insulator-semiconductor HEMTs (MISHEMTs) with Si-rich and stoichiometric SiNx passivation layers were fabricated on the "buffer-free" heterostructure, and their on-state and off-state characteristics were compared. The devices were characterized in terms of DC, pulsed I-V, and off-state BV.

In addition, a proper isolation technique must be implemented to further increase the off-state BV and prevent high lateral off-state leakage. High resistivity has been achieved for GaN with implantation of N,<sup>[16,17]</sup> He,<sup>[16]</sup> Ar,<sup>[18]</sup> or Kr<sup>[18]</sup> or by dry etching with Cl-based plasma to form a mesa. Although mesa isolation techniques are more straightforward, implantation isolation has proven to be the best choice to increase off-state BVs in GaN HEMTs with buffer layers. However, a study comparing implantation and mesa isolation in this new heterostructure has not yet been conducted. The potential benefit of having a thin GaN layer grown directly on the nucleation layer is the ability to easily dry etch (when using mesa isolation) or implant down to the semi-insulating SiC substrate.

To test the high-voltage properties of this heterostructure, we investigate the impact of N implantation isolation and mesa isolation on the off-state BV and leakage currents in MISHEMTs fabricated on the "buffer-free" heterostructure.

## 2. Epitaxial Design and Device Fabrication

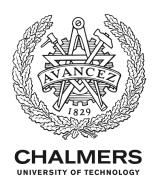

The epitaxial heterostructure grown on a high-purity semiinsulating SiC substrate in this study consists of four layers (from the bottom to the top): a 43 nm AlN nucleation layer, a 265 nm UID GaN layer, an 18.5 nm Al<sub>0.22</sub>Ga<sub>0.78</sub>N, and a 2.5 nm GaN cap (**Figure 1a**). The heterostructure, termed QuanFINE, was grown by SweGaN AB using MOCVD. The dislocation density in the UID GaN layer is in the low  $10^8 \text{ cm}^{-2}$ , and the carbon concentration is  $\sim 3 \times 10^{16} \text{ cm}^{-3}$ . Further details on the epitaxial growth and crystal quality have been presented by Lu et al. and Chen et al.<sup>[19,20]</sup>

The device fabrication started with the deposition of a  $SiN_r$ passivation layer using LPCVD with dichlorosilane (H2SiCl2) and ammonia (NH<sub>3</sub>) as Si and N precursors, respectively. Two different passivation layers were deposited: a 101 nm layer using a H<sub>2</sub>SiCl<sub>2</sub>/NH<sub>3</sub> flow ratio of 98/360 (Sample A) and a 176 nm layer using a H<sub>2</sub>SiCl<sub>2</sub>/NH<sub>3</sub> flow ratio of 224/23 (Sample B). The chamber pressure was set to 250 mTorr for both Sample A and B, while the deposition temperature for Sample A and B was 770 and 820 °C, respectively. A J.A. Woollam RC2 ellipsometer was used to estimate the thicknesses and refractive indices of the two layers. Refractive indices of 2.02 (2.00) and 2.40 (2.34) were extracted at a wavelength of 633 nm (830 nm) for Sample A and B, respectively. The Si content in the  $SiN_x$  layers was estimated using the relationship given by Dehan et al.,<sup>[21]</sup> where the N/Si ratio can be calculated using the refractive indices of the layers at 830 nm. The high refractive index in the  $SiN_x$  of Sample B indicates N/Si ratio of  $\sim$ 1.02, while a refractive index of 2.00 (Sample A) results in N/Si ratio of 1.36. In this work, the  $SiN_x$  on Sample A is referred to as "stoichiometric  $SiN_x$ ", or "Si<sub>3</sub>N<sub>4</sub>," as the N/Si ratio is close to 4/3, while the SiN<sub>x</sub> on Sample B is referred to as "Si-rich SiN<sub>x</sub>."

A 40–43 nm LPCVD stoichiometric  $SiN_x$  gate dielectric was deposited using the same deposition parameters as Sample A, after forming a gate recess etch into the passivation layer. The gate recess forms the gate length  $(L_g)$ , which was 2 and 4  $\mu$ m for Sample A and Sample B, respectively. The ohmic contacts consisted of a 15/280/20 nm Ta/Al/Ta stack,<sup>[22,23]</sup> which resulted in average contact resistances of  $0.44 \,\Omega$  mm for Sample A and  $0.75 \Omega$  mm for Sample B. A 600 nm PECVD SiO<sub>x</sub> second dielectric was deposited following the ohmic contact formation. The gate-source distance  $(L_{gs})$ , gate-drain distance  $(L_{gd})$ , and device width ( $W_g$ ) were 2, 5–40, and 100–200 µm, respectively. The gate-integrated field plate lengths ( $L_{gfp}$ ) were 0.75 µm toward the source and 4  $\mu$ m toward the drain. The source-integrated field plate length ( $L_{sfp}$ ) was 0 or 5 µm (as measured from the edge of the gate field plate). A top-view microscope image of a typical fabricated MISHEMT is shown in Figure 1b. In addition to the to MISHEMTs, a dielectric leakage test structure<sup>[24]</sup> was fabricated on Samples A and B. A schematic and microscope image of the test structure can be seen in Figure 1c,d, respectively.

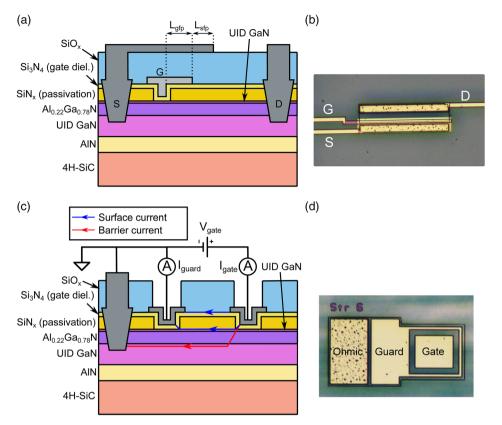

Two techniques were used to isolate the material surrounding the active areas: nitrogen implantation and mesa isolation etched to the SiC substrate. For the sample with nitrogen implantation isolation, three implantation energies were used: 30, 100, and 180 keV with implantation doses of  $5 \times 10^{12}$ ,  $10^{13}$ , and  $1.8 \times 10^{13}$  cm<sup>-2</sup>, respectively.

The stopping and range of ions in matter (SRIM) program was used to simulate the three nitrogen implantation profiles (Figure 2a) and the resulting vacancy concentration profiles (Figure 2b). The mesa isolation was formed with a dry etch using  $Cl_2/Ar$  gas chemistry with a 100 W reactive-ion etch power and a 50 W inductively coupled plasma power in an Oxford Plasmalab

Figure 1. a) Schematic and b) microscope image of a MISHEMT fabricated on a "buffer-free" heterostructure. c) Schematic and d) microscope image of a dielectric leakage test structure.

Figure 2. Simulated a) nitrogen and b) total vacancy concentration in a "buffer-free" heterostructure after nitrogen implantation.

100 system. The resulting mesa step height was measured to 400 nm using a step profilometer. In both of these samples, a Si-rich  $SiN_x$  passivation layer was used.

# 3. Results

#### 3.1. Impact of Isolation Techniques

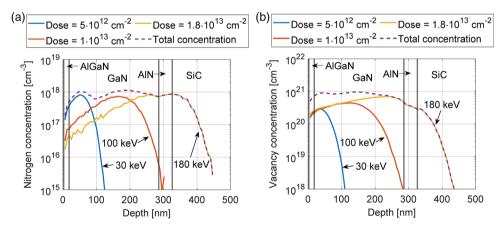

Off-state BVs were measured on MISHEMTs with nitrogen implantation and mesa isolation around the active device areas

using a Keysight B1505A Parameter Analyzer. The effect of nitrogen implantation on the off-state breakdown voltage is evident in **Figure 3**a, where destructive breakdown voltages of 1480–2496 V could be achieved for MISHEMTs on Sample B with  $L_{\rm gd} = 12-25 \,\mu\text{m}, \ L_{\rm gfp} = 0.75 \,\mu\text{m}, \ {\rm and} \ L_{\rm sfp} = 0 \,\mu\text{m}.$  This can be contrasted with mesa isolation, where the breakdown voltage was limited to 1284 V up to  $L_{\rm gd} = 25 \,\mu\text{m}.$

The breakdown electric fields, as calculated by  $BV/L_{gd}$ , are 98–123 and 51–85  $V\,\mu m^{-1}$  for implantation and mesa isolation, respectively. The MISHEMTs with nitrogen implantation

**Figure 3.** a) Destructive breakdown voltages of short field plate MISHEMTs with a Si-rich SiN<sub>x</sub> passivation layer with gate-drain distances of 12–25  $\mu$ m. b) Off-state breakdown characteristics of a short field plate MISHEMT with Si-rich SiN<sub>x</sub> passivation layer and  $L_{gd} = 20 \,\mu$ m.

Table 1. Breakdown voltage comparison with GaN-based HEMTs found in the literature with the 1 mA  $\rm mm^{-1}$  breakdown current criterion.

| References | Substrate | BV [V] | L <sub>gd</sub> [µm] | $BV/L_{gd} [V \mu m^{-1}]$ |

|------------|-----------|--------|----------------------|----------------------------|

| This work  | SiC       | 1480   | 12                   | 123                        |

| This work  | SiC       | 1762   | 15                   | 117                        |

| [17]       | Si        | 1800   | 10                   | 180                        |

| [25]       | Si        | 1590   | 15                   | 106                        |

| [26]       | Si        | 1900   | 15                   | 127                        |

| [27]       | SiC       | 3000   | 30                   | 100                        |

| [28]       | Si        | 1230   | 15                   | 82                         |

isolation display breakdown fields which are comparable with GaN-based HEMTs with Si and SiC substrates in the literature, where values in the range of 82–180 V  $\mu$ m<sup>-1</sup> have been demonstrated (**Table 1**).<sup>[17,25–28]</sup> Although GaN-on-Si HEMTs with carbon-doped buffers layers show vertical breakdown fields above 200 V  $\mu$ m<sup>-1</sup>,<sup>[3]</sup> the buffer layer can limit the off-state breakdown voltage. Therefore, increasingly thicker buffer layers are required to target higher breakdown voltages. However, in the "buffer-free" heterostructure, the vertical breakdown in the

SiC substrate is not primarily limiting the breakdown voltage.<sup>[9]</sup> The reduced breakdown for the mesa–isolated MISHEMTs is likely caused by surface states induced by the dry etch used to form the mesa or by a high electric field peak in the SiC trench.

Regardless of the isolation technique, there is a predominant drain–gate leakage current in the range of 1–100  $\mu$ A mm<sup>-1</sup> above 1000 V (Figure 3b), despite having a highly insulating stoichiometric SiN<sub>x</sub> gate dielectric.

The HEMTs with implantation isolation display leakage currents lower by a factor of 4 at 1000 V compared with HEMTs with SiC mesa isolation. The high leakage current and reduced breakdown voltage caused by Cl<sub>2</sub>/Ar plasma etching can be reduced using postetch treatments using tetramethylammonium hydroxide (TMAH).<sup>[29]</sup> However, the extent to which this can reduce the large breakdown voltage difference between "buffer-free" HEMTs with nitrogen implantation and mesa isolation techniques (Figure 3a) was not studied in this work.

Even though a small difference in off-state leakage can be observed between the two isolation techniques, both show high currents in the  $\mu$ A mm<sup>-1</sup> range. This indicates that the high leakage is primarily caused by the Si-rich passivation, gate dielectric, or both (see Section 3.1). Therefore, the stoichiometry of the SiN<sub>x</sub> dielectric(s) has to be tuned to improve the electrical isolation to suppress current levels below 1  $\mu$ A mm<sup>-1</sup> in the off state.

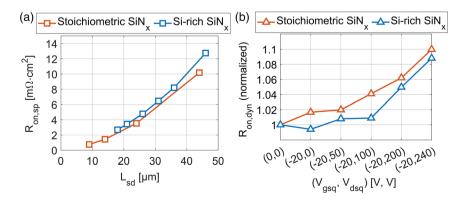

**Figure 4.** a) Specific on-state resistances for MISHEMTs with Si-rich and stoichiometric SiN<sub>x</sub> passivation with varying source–drain distances. b)  $R_{on,dyn}$  measured at  $V_{gs} = 0$  V, and  $V_{ds} = 1$  V after biasing  $V_{dsq}$  up to 240 V with an on/off-state time of 1/99 µs.

ADVANCED SCIENCE NEWS \_\_\_\_\_ www.advancedsciencenews.com

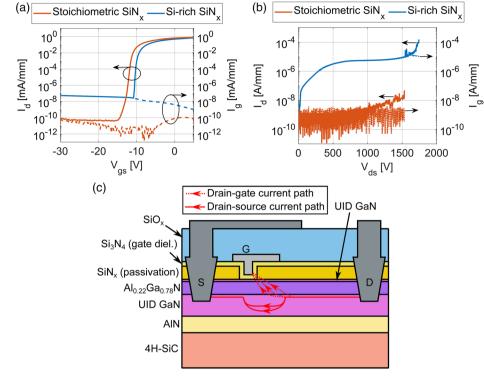

**Figure 5.** a) Transfer characteristics for MISHEMTs with long field plates and with  $V_{ds} = 40$  V. b) Off-state breakdown characteristics of MISHEMTs with long field plates with  $V_{gs} = -30$  V. c) A schematic showing potential off-state leakage current paths in the MISHEMTs with Si-rich and stoichiometric SiN<sub>x</sub> passivation layers.

#### 3.2. Impact of SiN<sub>x</sub> Stoichiometry

The specific on-resistances ( $R_{on,sp}$ ) were obtained from the output characteristics at  $V_{gs} = 0$  V,  $V_{ds} = 1$  V of MISHEMTs with source–drain distances ( $L_{sd} = L_{gs} + L_g + L_{gd}$ ) varying between 9 and 46 µm (**Figure 4**a), using a Keysight B1500 parameter analyzer. Low  $R_{on,sp}$  of 0.75 and 10.2 m $\Omega$  cm<sup>2</sup> for  $L_{gd} = 5-40$  µm was obtained, which shows that the electron transport properties are not adversely affected by having a thin UID GaN layer grown directly on the AlN nucleation layer. The SiN<sub>x</sub> stoichiometry did not seem to have any significant impact on the static on-state resistance. The difference in contact resistance between the two samples can explain the small discrepancy in the resistance.

The  $R_{\text{on,dyn}}$  was measured on MISHEMTs with an  $L_{\text{gd}} = 20 \,\mu\text{m}$  (Figure 4b) using an AMCAD 3200 system. The devices were pulsed from an off-state bias point with a gate voltage ( $V_{\text{gsq}}$ ) of -20 V and with a drain voltage ( $V_{\text{dsq}}$ ) that varied from 0 to 240 V (measurement system limit) to an on-state at  $V_{\text{gs}} = 0$  V and  $V_{\text{ds}} = 1$  V. The on-state time was set to 1  $\mu$ s, while the off-state time was set to 99  $\mu$ s. All  $R_{\text{on,dyn}}(V_{\text{gsq}}, V_{\text{dsq}})$  values extracted from the pulsed *I*–V measurements were normalized against  $R_{\text{on,dyn}}(0$  V,0 V).  $R_{\text{on,dyn}}$  was increased from 12.79 (12.88  $\Omega$  mm) to 14.07  $\Omega$  mm (14.01  $\Omega$  mm) on MISHEMTs with stoichiometric (Si-rich) SiN<sub>x</sub> passivation layers, representing an increase of 10% (9%). In GaN HEMTs with carbon-doped buffer layers, stoichiometric SiN<sub>x</sub> passivation layer can lead to

normalized  $R_{\text{on,dyn}}$  of 4–6, while the Si-rich passivation layers show a much smaller dispersion.<sup>[13,14]</sup> In contrast, the stoichiometry of the SiN<sub>x</sub> passivation layers did not seem to have the same impact on  $R_{\text{on,dyn}}$  up to a  $V_{\text{dsq}}$  of 240 V in the "buffer-free" MISHEMTs. This indicates that the trapping effects are not significantly affected by the stoichiometry in the passivation layer. However, despite not being affected by the type of passivation, it is still possible that the increase in  $R_{\text{on,dyn}}$  is caused by traps in the UID GaN layer, AlN nucleation layer, or at one of the III-nitride interfaces.

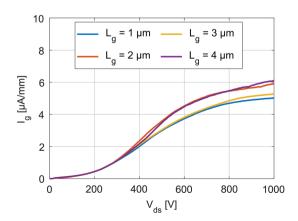

Figure 6. Off-state gate current for MISHEMTs with Si-rich  $SiN_x$  passivation layer with varying gate lengths.

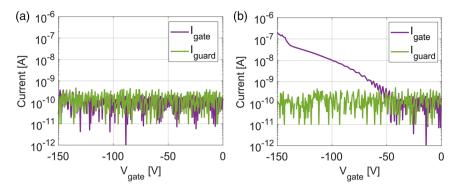

Figure 7. Dielectric leakage test with a) stoichiometric and b) Si-rich  $SiN_{x}$ .

MISHEMTs on Sample A and B showed a marked difference in terms of off-state leakage currents (**Figure 5**a,b). These MISHEMTs were fabricated with  $L_{gfp} = 4 \,\mu\text{m}$  and  $L_{sfp} = 5 \,\mu\text{m}$ . Using a stoichiometric SiN<sub>x</sub> passivation layer and gate dielectric, the gate current was reduced from  $4 \times 10^{-8}$  to  $4.7 \times 10^{-11} \,\text{A mm}^{-1}$  at  $V_{gs} = -20 \,\text{V}$  (Figure 5a). At voltages above 1000 V, the gate current remains below 10 nA mm<sup>-1</sup>, while the drain current increases to a maximum of 47 nA mm<sup>-1</sup> (Figure 5b). This indicates a small drain–source leakage current (punch-through) in the UID GaN layer underneath the depleted gate region (Figure 5c), which shows that the GaN, AlN, and the semi-insulating SiC provide sufficient electron confinement. In the HEMTs with Si-rich SiN<sub>x</sub> passivation layer, the high drain currents are likely caused by currents through the passivation layer and gate dielectric (Figure 5c).

Gate leakage currents up to 1000 V were also measured for HEMTs with Si-rich  $SiN_x$  passivation and gate lengths between 1 and 4 µm to make the comparison between MISHEMTs of Sample A and B fairer (Figure 6). No significant difference in gate leakage between the three gate lengths can be seen. Therefore, the high gate current seen in Figure 5 is not caused by a large gate area. A gate length of 2 µm or less could be used to minimize the on-state resistance without compromising off-state leakage currents.

The dielectric leakage test structure shows that the gate current (Igate) and guard current (Iguard) in Sample A are below 1 nA for gate voltages ( $V_{gate}$ ) between 0 and -150 V(Figure 7a), which indicate that both the barrier current and surface-related currents are small. However, in Sample B, the barrier current through the SiN<sub>x</sub> films and AlGaN layer increased by almost three orders of magnitude for Sample B when the gate voltage ( $V_{gate}$ ) decreased from -40 to -150 V (Figure 7b). This suggests that the large off-state drain-gate currents were caused by leakage through the gate dielectric, passivation layer, and AlGaN barrier down to the 2D electron gas rather than by surface-related leakage currents at (or surrounding) the  $SiN_x/$ GaN interface. The destructive breakdown voltages of the two measured MISHEMTs with  $L_{gfp} = 4 \,\mu m$  and  $L_{sfp} = 5 \,\mu m$  was 1532 and 1742 V for the Si-rich and stoichiometric-passivated MISHEMT, respectively (Figure 4b). However, MISHEMTs with shorter field plates display higher breakdown voltages (Figure 3a), showing that the field plate design is not optimized for the highest breakdown voltage in Figure 5. By decreasing the length of the field plates, it was possible to increase the breakdown voltage from 1742 to 2200 V (Figure 3b and 4b). However, the drain–gate current remains high (>1  $\mu$ A mm<sup>-1</sup>) regardless of the field plate length. By combining short gate and source field plates with a stoichiometric SiN<sub>x</sub> passivation and gate dielectric, the breakdown voltage could be increased further while maintaining a low gate leakage current.

## 4. Conclusion

MISHEMTs with two isolation techniques and two SiN<sub>x</sub> passivation layers were fabricated on a "buffer-free" AlGaN/GaN-on-SiC heterostructure to study their impact on the DC, pulsed I-V, and high-voltage off-state characteristics. Drain-gate leakage currents were suppressed by more than two orders of magnitude at high voltages using stoichiometric instead of a Si-rich SiN<sub>x</sub> passivation layer without compromising the dynamic on-state resistance in the measured interval. The high drain-gate currents observed in the MISHEMTs with a Si-rich passivation layer were likely not caused by surface-related currents but instead by leakage from the gate metal down to the 2DEG through the SiN<sub>x</sub> layers. When using a stoichiometric  $SiN_x$  passivation layer, the primary leakage mechanism at high voltages was a drain-source leakage current in the III-nitride heterostructure rather than a drain-gate leakage. MISHEMTs with nitrogen implantation isolation allowed for the highest off-state breakdown voltages compared with mesa isolation down to the SiC substrate. By combining the stoichiometric SiNx passivation layer with short field plates, an enhanced breakdown voltage with drain leakage currents in the  $1-100 \text{ nA mm}^{-1}$  can be achieved, which shows the potential of this material for high-voltage power electronic HEMTs.

# Acknowledgements

This work was performed within the framework of the competence center for III-Nitride technology, C3NiT Janzén supported by the Swedish Governmental Agency for Innovation Systems (VINNOVA) under the Competence Center Program grant no. 2016-05190, Linköping University, Chalmers University of Technology, Ericsson, Epiluvac, Swedish Defence Materiel Administration (FMV), Gotmic, Hexagem, Hitachi Energy, onsemi, Saab, SweGaN, and United Monolithic Semiconductors (UMS). The authors further acknowledge support from the Swedish Foundation for Strategic Research under grant no. EM16-0024.

2200533 (6 of 7)

# **Conflict of Interest**

The authors declare no conflict of interest.

# **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

# **Keywords**

AlGaN/GaN, buffer free, high voltages, mesa isolations, metal–insulator–semiconductor high-electron-mobility transistors, nitrogen implantation, SiN<sub>x</sub> passivations

Received: July 30, 2022

- Revised: October 10, 2022

- Published online: December 11, 2022

- [1] C.-T. Ma, Z.-H. Gu, Electronics 2019, 8, 1401.

- M. Borga, M. Meneghini, D. Benazzi, E. Canato, R. Püsche, J. Derluyn,

I. Abid, F. Medjdoub, G. Meneghesso, E. Zanoni, *Microelectron. Reliab.* 2019, 100, 113461.

- [3] I. B. Rowena, S. L. Selvaraj, T. Egawa, IEEE Electron Device Lett. 2011, 32, 1534.

- [4] D. C. Look, G. C. Farlow, P. Drevinsky, D. Bliss, J. Sizelove, Appl. Phys. Lett. 2003, 83, 3525.

- [5] A. F. Wright, J. Appl. Phys. 2005, 98, 103531.

- [6] J. Lyons, A. Janotti, C. Van de Walle, Appl. Phys. Lett. 2010, 97, 152108.

- [7] J. Würfl, O. Hilt, E. Bahat-Treidel, R. Zhytnytska, P. Kotara, F. Brunner, O. Krueger, M. Weyers, in *IEEE Int. Electron Devices Meet.*, IEEE, Piscataway, NJ 2013, p. 6.1.1.

- [8] M. J. Uren, S. Karboyan, I. Chatterjee, A. Pooth, P. Moens, A. Banerjee, M. Kuball, IEEE Trans. Electron Devices 2017, 64, 2826.

- [9] B. Hult, M. Thorsell, J.-T. Chen, N. Rorsman, IEEE Electron Device Lett. 2022, 43, 781.

- [10] G. Koley, V. Tilak, L. F. Eastman, M. G. Spencer, IEEE Trans. Electron Devices 2003, 50, 886.

- [11] T. Prunty, J. Smart, E. Chumbes, B. Ridley, L. Eastman, J. Shealy, in *IEEE/Cornell Conf. High Perform. Devices*, IEEE, Piscataway, NJ 2000, p. 208.

- [12] X. Wang, S. Huang, Y. Zheng, K. Wei, X. Chen, G. Liu, T. Yuan, W. Luo, L. Pang, H. Jiang, *IEEE Electron Device Lett.* **2015**, *36*, 666.

- [13] W. M. Waller, M. Gajda, S. Pandey, J. J. Donkers, D. Calton, J. Croon, S. Karboyan, J. Šonský, M. J. Uren, M. Kuball, *IEEE Trans. Electron Devices* **2017**, *64*, 1197.

- [14] F. Yang, S. Dalcanale, M. Gajda, S. Karboyan, M. J. Uren, M. Kuball, IEEE Trans. Electron Devices 2020, 67, 869.

- [15] W. M. Waller, M. Gajda, S. Pandey, J. J. Donkers, D. Calton, J. Croon, J. Šonský, M. J. Uren, M. Kuball, *IEEE Trans. Electron Devices* 2017, 64, 4044.

- [16] S. Binari, H. Dietrich, G. Kelner, L. Rowland, K. Doverspike, D. Wickenden, J. Appl. Phys. 1995, 78, 3008.

- [17] M. Sun, H.-S. Lee, B. Lu, D. Piedra, T. Palacios, Appl. Phys. Express 2012, 5, 074202.

- [18] S. Arulkumaran, K. Ranjan, G. I. Ng, J. Kennedy, P. P. Murmu, T. N. Bhat, S. Tripathy, J. Vac. Sci. Technol., B: Nanotechnol. Microelectron.: Mater., Process., Meas., Phenom. 2016, 34, 042203.

- [19] J. Lu, J.-T. Chen, M. Dahlqvist, R. Kabouche, F. Medjdoub, J. Rosen, O. Kordina, L. Hultman, *Appl. Phys. Lett.* **2019**, *115*, 221601.

- [20] J.-T. Chen, J. Bergsten, J. Lu, E. Janzén, M. Thorsell, L. Hultman, N. Rorsman, O. Kordina, Appl. Phys. Lett. 2018, 113, 041605.

- [21] E. Dehan, P. Temple-Boyer, R. Henda, J. Pedroviejo, E. Scheid, Thin Solid Films 1995, 266, 14.

- [22] A. Malmros, H. Blanck, N. Rorsman, Semicond. Sci. Technol. 2011, 26, 075006.

- [23] Y.-K. Lin, J. Bergsten, H. Leong, A. Malmros, J.-T. Chen, D.-Y. Chen, O. Kordina, H. Zirath, E. Y. Chang, N. Rorsman, Semicond. Sci. Technol. 2018, 33, 095019.

- [24] W. Tan, M. Uren, P. Houston, R. Green, R. Balmer, T. Martin, IEEE Electron Device Lett. 2005, 27, 1.

- [25] J.-G. Lee, B.-R. Park, H.-J. Lee, M. Lee, K.-S. Seo, H.-Y. Cha, Appl. Phys. Express 2012, 5, 066502.

- [26] N. Herbecq, I. Roch-Jeune, N. Rolland, D. Visalli, J. Derluyn, S. Degroote, M. Germain, F. Medjdoub, *Appl. Phys. Express* 2014, 7, 034103.

- [27] H.-S. Lee, D. Piedra, M. Sun, X. Gao, S. Guo, T. Palacios, *IEEE Electron Device Lett.* 2012, 33, 982.

- [28] J. Ma, C. Erine, M. Zhu, N. Luca, P. Xiang, K. Cheng, E. Matioli, in IEEE Int. Electron Devices Meet., IEEE, Piscataway, NJ 2019, p. 4.1.1.

- [29] Y. J. Yoon, J. H. Seo, M. S. Cho, H.-S. Kang, C.-H. Won, I. M. Kang, J.-H. Lee, Solid-State Electron. 2016, 124, 54.