# Mobility and quasi-ballistic charge carrier transport in graphene field-effect transistors

Downloaded from: https://research.chalmers.se, 2025-12-05 00:13 UTC

Citation for the original published paper (version of record):

Harrysson Rodrigues, I., Rorsman, N., Vorobiev, A. (2022). Mobility and quasi-ballistic charge carrier transport in graphene field-effect transistors. Journal of Applied Physics, 132: 244303-1-244303-9. http://dx.doi.org/10.1063/5.0121439

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

# Mobility and quasi-ballistic charge carrier transport in graphene field-effect transistors

Isabel Harrysson Rodrigues,<sup>1, a)</sup> Niklas Rorsman,<sup>1</sup> and Andrei Vorobiev<sup>1</sup>

Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296 Gothenburg,

Sweden

(Dated: 8 November 2022)

The optimization of graphene field effect transistors (GFETs) for high frequency applications requires further understanding of the physical mechanisms concerning charge carrier transport at short channel lengths. Here, we study the charge carrier transport in GFETs with gate lengths ranging from 2  $\mu$ m down to 0.2  $\mu$ m by applying a quasi-ballistic transport model. It is found, that the carrier mobility, evaluated via the drain-source resistance model including geometrical magnetoresistance effect, is more than halved with decreasing the gate length in the studied range. This decrease in mobility is explained by the impact of ballistic charge carrier transport. The analysis allows for evaluation of the characteristic length, a parameter of the order of the mean free path, which is found to be in the range of 359-374 nm. The mobility term associated with scattering mechanisms is found to be up to 4456 cm²/Vs. Transmission formalism treating the electrons as purely classical particles allows for the estimation of the probability of charge carrier transport without scattering events. It is shown, that at the gate length of 2  $\mu$ m approximately 20 % of the charge carriers are moving without scattering, while at the gate length of 0.2  $\mu$ m this number increases to above 60 %.

## INTRODUCTION

The future progress in modern electronics partly relies on the development of novel materials with improved charge carrier transport properties, such as graphene. 1,2 The extremely high carrier mobility and saturation velocity in graphene could possibly enable much faster electronics compared to traditional semiconductors. Graphene has already demonstrated high potential as channel material in advanced graphene fieldeffect transistors (GFETs), specifically for high frequency applications.<sup>3,4</sup> However, full realization of the capabilities of the high-frequency GFETs requires better understanding of the charge carrier transport mechanisms, which will allow for optimization of device design and layout, as well as operational conditions. In the majority of the previous works, the high-frequency performance of GFETs was analyzed using the drift-diffusion theory of charge carrier transport assuming that the intrinsic transit (cutoff) frequency is limited by the saturation velocity  $(v_{\text{sat}})$  as  $f_{\text{T}} = \frac{v_{\text{sat}}}{2\pi L}$ , where L is the gate length.<sup>5–7</sup> It was shown theoretically that, in the typical GFET structures, the saturation velocity is limited by the remote optical phonons of the adjacent dielectrics, e.g., SiO<sub>2</sub> layer on surface of Si substrate, which phonon energy is significantly less than that of the longitudinal zone boundary phonons of intrinsic graphene (160 meV).<sup>8,9</sup> Therefore, for further increasing  $f_{\rm T}$ , selecting the dielectric materials with higher phonon energies was suggested.<sup>6,8</sup> This approach was verified experimentally using encapsulation by hBN, Al<sub>2</sub>O<sub>3</sub> buffer layer, or diamond substrate resulting in increased saturation velocity and transit frequency. 5,10,11 The approach apparently reaches its limit in the GFETs based on graphene encapsulated by diamond-like carbon (DLC) layers, since the surface phonon energy of DLC (165 meV) is slightly higher than that of graphene. 12 Thus, the remaining obvious way

of further increasing  $f_T$  is continuing scaling down the gate length. However, the above analysis and conventional relationship between the  $f_T$  and L, i.e. derived using the driftdiffusion theory, might not be valid for GFETs with relatively short gate lengths due to contribution of the ballistic mode in the charge carrier transport.<sup>13</sup> In particular, in the purely ballistic mode, the saturation velocity in the above relationship should be replaced by a Fermi velocity or virtual source injection velocity. 13,14 For comparison, it was predicted, that in short channel (submicron) high-electron-mobility transistors, the effective, i.e., measured, mobility must be much smaller than that in long channel devices, which was related to the ballistic transport. 15 There is relatively limited number of publications analyzing the ballistic charge carrier transport in GFETs. The reduction of the effective mobility in the GFETs with gate lengths shorter than 1-2  $\mu$ m was reported in Refs. 14,16–18 In Refs. 14,17 the observed reduction of the mobility was associated with the quasi-ballistic transport and by using the concept of ballistic mobility, 15 the mean free path was found to be in the range of 175-400 nm. However, the reported data and analysis do not allow for conclusion to which extent the ballistic motion contributes to the total charge carrier transport in the GFETs. For comparison, in Ref. 19, electron mobility in quasi-ballistic Si metal-oxide-semiconductor field-effect transistors was analyzed using the concept of ballistic mobility and the transmission formalism, which allowed for evaluation of the transmission probability and estimation of fraction of the total number of ballistic electrons.<sup>20</sup>

In this work, we apply the concept of ballistic mobility and the transmission formalism to study the charge carrier transport in GFETs with different gate lengths in the range 0.2-2.0  $\mu$ m. Comparative analysis of collision and ballistic mobility parameters allows us to clearly illustrate the transition of the charge carrier transport from the scattering regime through the quasi-ballistic to the purely ballistic regime.

a) isabel.harrysson.rodrigues@gmail.com

#### **DEVICE FABRICATION AND MEASUREMENTS**

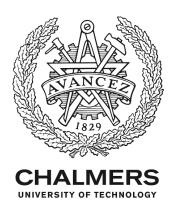

The GFETs studied in this work have layout similar to those previously published, 21 i.e., with dual-gate fingers centered between source and drain contacts separated by 100 nm long ungated regions. The layout and design are optimized for high-frequency performance of the GFETs taking into account the following considerations and conditions. As shown in introduction, the  $f_{\rm T}$ , which is the device high-frequency figure of merit, is inversely proportional to the gate length, i.e., charge carriers transit time. This relationship is a driving force of the scaling down, i.e., implies that the L should be as short as possible. Analysis of extrinsic  $f_T$  indicates that, relatively large gate width and two gate fingers should be used to minimize the effects of the pad capacitances. Current optimal design and technology utilize the two gate fingers with total gate width of 30  $\mu$ m. In the dc analysis of this work, only one gate finger is used. Analysis indicates also that the ungated regions should be as short as possible to minimize the effect of the total series resistance. With current technology the ungated regions of 100 nm are used, which is the lower limit defined by the e-beam lithography in this fabrication process flow. To minimize the resistance of the graphene-metal junctions, the overlapping of the drain and source electrodes with edges of the graphene in the channel direction is designed to be 10  $\mu$ m, i.e. sufficiently larger than the transfer length, which is typically below 0.25  $\mu$ m.<sup>22</sup> The top gate configuration of the GFETs is used with the aim to minimize the parasitic gate-source and gate-drain capacitances. In the current planar gate technology, a relatively thick gate electrode composed by 10 nm/300 nm Ti/Au layers is used to minimize the limiting effect of the gate resistance on the extrinsic maximum frequency of oscillations. In the optimized GFET design used in this work, the thickness of the SiO<sub>2</sub> layer on top of the Si substrate is increased up to 1  $\mu$ m with the aim to reduce the parasitic pad capacitances. The above improvements in the design allowed for development and demonstrating GFETs with state-of-the-art high-frequency performance.<sup>23</sup> Fig. 1 (a) shows an optical microscope image of a fabricated device, where source, drain, and gate pads are indicated. Fig. 1 (b) shows a 3D schematic illustration of a cross-section of the gate region describing the material of the different layers. Several sets of GFETs with gate length ranging from 2  $\mu$ m down to  $0.2 \mu m$  and one finger gate width (W) of 15  $\mu m$  were fabricated on a Si wafer.

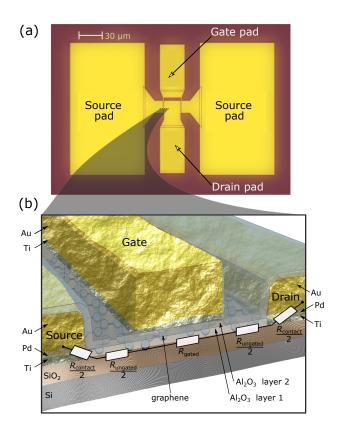

The GFETs were fabricated using processing steps based on the previously developed technology optimized for improving high-frequency performance via preserving graphene intrinsic properties by encapsulation at initial stage of fabrication and reducing the contact resistance. <sup>23,24</sup> The very detailed recipe of the processing used in this work is given in Ref. <sup>25</sup> Fig. 2 shows main steps of the GFET fabrication summarized below. In the first step, graphene prepared by Graphenea using chemical vapor deposition (CVD) was transferred onto high resistivity silicon/silicon oxide (Si/SiO<sub>2</sub>) substrate, with a SiO<sub>2</sub> thickness of 1  $\mu$ m, using the Easy Transfer approach. <sup>26</sup> After the transfer, with the aim to remove water molecules absorbed on the surface and trapped at the interface,

FIG. 1. (a) An optical microscope image of a fabricated device with the source, drain, and gate pads indicated. (b) A 3D schematic illustration of a cross-section area of a gate finger showing materials of different layers and total resistance equivalent circuit.

FIG. 2. Main steps of the GFET fabrication. (i) Formation of the 1<sup>st</sup> dielectric layer, (ii) patterning of the dielectric/graphene mesa and formation of the source and drain contacts, (iii) deposition of the 2<sup>nd</sup> dielectric layer, and (iv) formation of the gate electrodes and source, along with the drain contact pads. Labels S, D and G indicate source, drain and gate electrodes, respectively.

the graphene was dried on hotplate, first at low temperature of approx. 47°C until its color changed, then at higher temperature of 150-160°C to get rid of water bubbles. After that, the graphene was placed in vacuum chamber for 2-3 days with the aim to remove completely the residual water molecules. The transferred graphene film was covered by an approximately

8 nm thick Al<sub>2</sub>O<sub>3</sub> layer obtained by six times repetitive deposition of 1 nm thick Al film and its subsequent oxidation on a hotplate at 160°C for 5 minutes. This layer constitutes the 1st layer of the gate dielectric, which encapsulates the graphene protecting it from contamination throughout the subsequent fabrication steps. In the following step the graphene/dielectric mesa and, subsequently, the openings in the Al<sub>2</sub>O<sub>3</sub> layer for the drain/source contacts were patterned via e-beam lithography. The drain/source contacts were formed by deposition of 1 nm Ti/15 nm Pd/250 nm Au and the use of a standard lift-off process. After this, the approximately 14 nm thick 2<sup>nd</sup> gate dielectric layer of Al<sub>2</sub>O<sub>3</sub> was formed by repeating ten times the process described above, which results in the total gate dielectric thickness ( $d_g$ ) of approximately 22 nm. The 2<sup>nd</sup> dielectric layer covers the graphene edges exposed at the mesa sidewalls, which prevents short-circuiting by the overlapping gate fingers. As it can be seen from Fig. 2 (iv), the 2<sup>nd</sup> gate dielectric layer serves also as a passivation layer for the ungated regions, which prevents degradation of the corresponding part of the series resistance due to interaction with ambient, e.g., absorbing water. Again, this improvement of the design and technology is experimentally verified by demonstrating GFETs with state-of-the-art high-frequency performance.<sup>23</sup> Finally, the gate electrodes and the contact pads were fabricated by e-beam lithography and deposition of 10 nm Ti/290 nm Au by e-beam evaporation followed by a standard lift-off process. Notice that before metal deposition in the openings of the source and drain contact areas, the 1<sup>st</sup> dielectric layer, which separates the graphene from the lithographic resist, is etched off by the buffered oxide etch (BOE) for metal/graphene ohmic contact formation. Apparently, this process allows for the effective removal of e-beam resist residues, providing a rather clean interface between the graphene and the metal and resulting in an extremely low specific-width contact resistivity of the graphene/metal junctions below 100  $\Omega \times \mu m$ .<sup>23,24</sup> The specific-width contact resistivity have been evaluated via analysis of the GFET transfer characteristics and its low value confirmed by measurements using the multi-terminal transfer length method.<sup>24,27</sup> As it can be seen from Fig. 2, the graphene/metal contacts are made in the conventional top, or planar type, configuration. The measured specific-width contact resistivity is close to the theoretical limit of 88  $\Omega \times \mu m$  for the planar contacts and comparable or even lower than that reported for the side, or edge type, contacts.<sup>28,29</sup> The effectiveness of removal of the e-beam resist residues in the source/drain contact openings have been confirmed by comparative study of the Raman spectra of the as-transferred graphene, graphene in the Al<sub>2</sub>O<sub>3</sub> openings made by BOE and graphene in the e-beam resist openings made by a standard developer.<sup>27</sup> A feature of the GFET processing used in this work is formation of the Al<sub>2</sub>O<sub>3</sub> gate dielectric by sequential deposition of 1 nm thick Al films followed by its oxidation on a hot plate at 160°C for 5 min. in ambient conditions, *i.e.*, ex-situ, without involving the atomic layer deposition (ALD). The high quality of the gate dielectric was confirmed by measurements of the permittivity using Corbino disc test structures similar to that reported in Ref.<sup>30</sup> The permittivity is found to be approximately 7.5,

which is higher than approximately 6.5 typical for the 20 nm thick Al<sub>2</sub>O<sub>3</sub> made by ALD.<sup>31</sup>

Fig. 1 (b) also shows the equivalent circuit of the total drainsource resistance ( $R_{\text{total}}$ ). The  $R_{\text{gated}}$  and  $\frac{1}{2} \times R_{\text{ungated}}$  are resistances of the gated and ungated regions of the channel, respectively. The  $\frac{1}{2} \times R_{\text{contact}}$  is the contact resistance associated with a graphene-metal junction. The contact resistance also includes the probe and cable resistances (not shown in Fig. 1). The resistances of the ungated regions and contact resistances constitute the total series resistance as  $R_{\text{series}} =$  $R_{\rm ungated} + R_{\rm contact}$ , and the total drain-source resistance can be expressed as  $R_{\text{total}} = R_{\text{series}} + R_{\text{gated}}$ . The transfer characteristics, i.e., drain current (IDS) versus gate voltage (VGS), of the GFETs were measured in common source configuration at the drain voltage  $V_{DS} = -0.1 \text{ V}$  using a Keysight B1500A parameter analyzer on a Cascade summit 12000 semi-automatic probe station. The drain-source resistance was calculated as  $R_{\text{total}} = \frac{V_{\text{DS}}}{I_{\text{DS}}}$ .

### **RESULTS AND DISCUSSION**

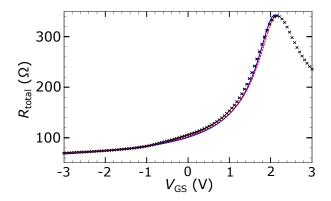

Fig. 3 shows a typical dependence of the total drain-source resistance on the gate voltage of a GFET with the gate length of 1  $\mu$ m. The mobility ( $\mu_{\rm eff}$ ) in GFETs is usually extracted from the drain-source resistance model as

$$R_{\text{total}} = R_{\text{series}} + \frac{L}{W} \frac{1}{\mu_{\text{eff}} e} \frac{1}{\sqrt{n_0^2 + \left( (V_{\text{GS}} - V_{\text{Dir}}) \frac{C_g}{e} \right)^2}}, \quad (1)$$

where e is the elementary charge,  $n_0$  is the residual concentration of the charge carriers,  $V_{\text{Dir}}$  is the Dirac voltage and  $C_{\text{g}}$ is the gate capacitance per unit area.<sup>8,32</sup> It can be shown that under the conditions used in our experiments, the graphene quantum capacitance can be ignored.<sup>32</sup> In the common approach the  $\mu_{\rm eff}$ ,  $n_0$  and  $R_{\rm series}$  are used as fitting parameters with the  $\mu_{\rm eff}$  being of a target parameter, i.e., main parameter to be found in this case. The  $C_g$  is usually associated with the capacitance of the gate oxide dielectric  $C_{\text{ox}} = \frac{\varepsilon \mathcal{E}_0}{d_g}$ , where the  $\varepsilon_0$  is the vacuum permittivity and  $\varepsilon$  is the dielectric constant of the gate dielectric. We assume that,  $\varepsilon \approx 7.5$ , which gives  $C_{\rm g} = \tilde{C}_{\rm ox} \approx 3.0 \times 10^{-3} \text{ F/m}^2$ . Fig. 3 shows the fitting curve obtained using Eq. (1) with corresponding parameters presented in Table I in the row where mobility indicated as target parameter. It can be seen, that the very good fitting is obtained. The mobility is found to be 1777 cm<sup>2</sup>/Vs. However, in our recent studies using the geometrical magnetoresistance (gMR) effect, we demonstrated that the mobility found assuming  $C_{\rm g} = C_{\rm ox}$  can be significantly underestimated.<sup>21</sup> In particular, the average value of the gMR mobility of the same GFET, was found to be 3492 cm<sup>2</sup>/Vs. We explained this by contribution of the interfacial capacitance, which significantly reduces the gate capacitance in comparison with that given by the oxide dielectric only. This agrees well with results of our previous studies using the delay time analysis and analysis of the capacitance-voltage dependencies in the GFETs.<sup>33</sup> Therefore, in this work the drain-source resistance model given by Eq. (1) is instead used to extract the gate capacitance with

the average mobility value found via the gMR effect, *i.e.*,  $3492 \text{ cm}^2/\text{Vs}$ . In this case, the gate capacitance per unit area is found to be  $1.6 \times 10^{-3} \text{ F/m}^2$ , which is almost 2 times lower than the  $C_{\text{ox}}$ . Fig. 3 shows result of the fitting with the parameters given in Table I in the row where the  $C_{\text{g}}$  is indicated as target parameter. It can be seen, that almost identical fitting is obtained. Below, in the analysis of the charge carrier transport in GFETs applying a quasi-ballistic transport model, we use the mobility values found via fitting of the drain-source resistance model (Eq. (1)) with mobility as target parameter, for both values of the  $C_{\text{g}} = 3.0 \times 10^{-3} \text{ F/m}^2$  and  $1.6 \times 10^{-3} \text{ F/m}^2$ , for comparison.

FIG. 3. Drain-source resistance (crosses) vs gate voltage of a GFET with the gate length of 1  $\mu$ m obtained from measured transfer characteristic. The dashed line represents fitting by the drain-source resistance model, Eq. (1), in the common approach, *i.e.*, using the  $\mu_{\rm eff}$ ,  $n_0$  and  $R_{\rm series}$  as fitting parameters with the  $\mu_{\rm eff}$  being of a target parameter and using  $C_{\rm g} = C_{\rm ox} = 3.0 \times 10^{-3} \ {\rm F/m^2}$ . The solid line represents fitting by the drain-source resistance model, Eq. (1), in the modified approach, *i.e.*, using the  $C_{\rm g}$ ,  $n_0$  and  $R_{\rm series}$  as fitting parameters with the  $C_{\rm g}$  being of a target parameter and assuming  $\mu_{\rm eff} = 3492 \ {\rm cm^2/Vs}$  found from the gMR effect. <sup>21</sup> The fitting parameters are presented in Table I.

TABLE I. Parameters used in the drain-source resistance model fitting in Fig. 3.

| •              | -                                     |                           |                                |                                   |

|----------------|---------------------------------------|---------------------------|--------------------------------|-----------------------------------|

| Target         | $\mu_{\rm eff}$ (cm <sup>2</sup> /Vs) | $R_{\rm series} (\Omega)$ | $n_0 (10^{15} \text{ m}^{-2})$ | $C_{\rm g}~(10^{-3}~{\rm F/m^2})$ |

| $\mu_{ m eff}$ | 1777                                  | 45                        | 10                             | 3.0                               |

| $C_{g}$        | 3492                                  | 45                        | 4.3                            | 1.6                               |

It was shown that in the quasi-ballistic regime, the measured, *i.e.*, effective, mobility can be expressed using Mathiessen's rule as <sup>13,15,19,34</sup>

$$\frac{1}{\mu_{\text{eff}}} = \frac{1}{\mu_0} + \frac{1}{\mu_{\text{ballistic}}},\tag{2}$$

where  $\mu_0$  is the mobility resulting from all scattering mechanisms, which would be measured in a long device under collision-dominated conditions, and termed as collision mobility in the analysis below.  $\mu_{\text{ballistic}}$  is a length-dependent "ballistic" mobility. For a degenerate two-dimensional elec-

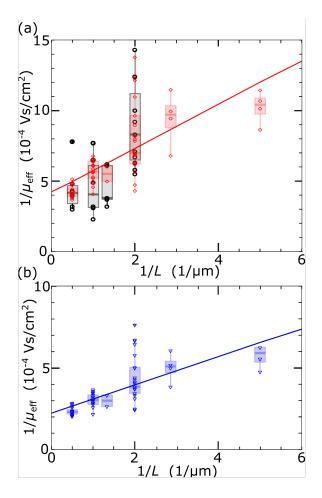

FIG. 4. Reciprocal of effective mobility vs reciprocal of gate length found using drain-source resistance model, Eq. (1), assuming  $C_{\rm g} = 3.0 \times 10^{-3} \ {\rm F/m^2}$  (a) and  $1.6 \times 10^{-3} \ {\rm F/m^2}$  (b) for sets of GFETs measured at each gate length. Shown in (a) are also data from Ref.<sup>24</sup> (circles), for comparison. The data are shown also in the box plot formats illustrating distributions. The straight lines are linear fits. The edges of the boxes indicate the  $25^{\rm th}$  and  $75^{\rm th}$  percentile values, while the short lines within the boxes indicate the median values.

tron gas the ballistic mobility is given by <sup>13</sup>

$$\mu_{\text{ballistic}} = \frac{2qL}{\pi m v_{\text{F}}},$$

(3)

$$\frac{1}{\mu_{\text{eff}}} = \frac{1}{\mu_0} + \frac{\lambda_{\text{B}}}{\mu_0} \frac{1}{L},\tag{4}$$

where  $\lambda_{\rm B}=\frac{\mu_0\pi m v_{\rm F}}{2g}$  is the characteristic length of the order of

Fig. 4 (a) and Fig. 4 (b) show plots of  $\frac{1}{\mu_{\rm eff}}$  versus  $\frac{1}{L}$  for the GFETs in this work with mobilities found using the drainsource resistance model, Eq. (1), and assuming the  $C_{\rm g}=$  $3.0 \times 10^{-3}$  F/m<sup>2</sup> and  $1.6 \times 10^{-3}$  F/m<sup>2</sup>, respectively. The data are shown also in the box plot formats illustrating the data distribution and allowing for statistical analysis. The edges of the boxes indicate the 25th and 75th percentile values, while the short lines within the boxes indicate the median values. According to our analysis, the error in evaluation of the  $\lambda_{\rm B}$ is caused mainly by error in the straight-line fitting of the data in the  $\frac{1}{\mu_{\text{eff}}}$  versus  $\frac{1}{L}$  format made by a MATLAB code. Comparison with the best manual fit shows that the error in evaluation of the  $\lambda_B$  is less than 5 % in all cases. It can be seen from Fig. 4 that the 5 % error is significantly less than the dispersion of data due to surface distribution of the graphene properties, which, as shown below, is caused by Coulomb inhomogeneities and, hence, can be ignored. The values at  $L = 0.5 \mu m$  looks more scattered because the corresponding sample data set is intentionally larger. The reason is that the GFETs with this specific gate length were simultaneously used in more comprehensive studies for development of the integrated 10 GHz GFET amplifiers.<sup>37</sup> Fig. 4 (a) also shows the data from our previous work,<sup>24</sup> for comparison. The GFETs reported in Ref.<sup>24</sup> were fabricated by similar technology, using a different CVD graphene. The effective mobility values found in this work reveal comparable or even smaller distribution of the GFETs with similar gate lengths, compared to Ref.<sup>24</sup> The distribution of the mobility is usually explained by the spatially inhomogeneous screened Coulomb potential caused by charged defects and impurities.<sup>38</sup> The charged defects/impurities can be created during the GFET processing either in the graphene or adjacent dielectrics and usually associated with the water molecules trapped at the graphene/substrate interface or with the oxygen vacancies in the gate dielectric.<sup>39-42</sup> It was shown with terahertz time-domain spectroscopy that the mobility can be distributed in the range of approximately 600-1400 cm<sup>2</sup>/Vs even in the bare CVD graphene. 43 For comparison, even in the GFETs based on the exfoliated graphene, i.e., with potentially much cleaner graphene interfaces than that on the CVD graphene, the dispersion in the dependence of the measured mobility on the gate length with even relatively limited number of the experimental points can be up to 50 %.<sup>17</sup> One can expect that with a larger sample data set the dispersion will be correspondingly larger, *e.g.*, as it can be seen in Fig. 4 at  $L=0.5~\mu m$ . According to the self-consistent theory, the mobility limited by Coulomb scattering depends only on the charged impurity concentration and the dielectric constant of the substrate.<sup>38</sup> The charged impurity concentration ( $n_{\rm imp}$ ) plainly defines the residual concentration of the charge carriers as  $n_0=0.2\times n_{\rm imp}$  for graphene on SiO<sub>2</sub>.<sup>44–46</sup> According to the theory, the product of the mobility and the residual carrier concentration is constant, and for graphene on the SiO<sub>2</sub> is  $n_0\times \mu_{\rm eff}\approx 1.5\times 10^{15}~{\rm V}^{-1}{\rm s}^{-1}.^{44-46}$  Fig. 5

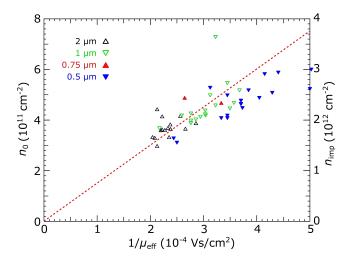

FIG. 5. Residual concentration of charge carriers  $(n_0)$  and concentration of charged impurities  $(n_{\rm imp})$  versus reciprocal of effective mobility, found using drain-source resistance model, Eq. (1), assuming  $C_{\rm g}=1.6\times 10^{-3}$  F/m², in the GFETs with gate lengths of 2  $\mu$ m ( $\triangle$ ), 1  $\mu$ m ( $\nabla$ ), 0.75  $\mu$ m ( $\blacktriangle$ ), and 0.5  $\mu$ m ( $\blacktriangledown$ ), located at different positions on the Si wafer. The line corresponds to the product  $n_0 \times \mu_{\rm eff}=1.5\times 10^{15}$  V<sup>-1</sup>s<sup>-1</sup>.

shows the  $n_0$ , found as fitting parameter in the drain-source resistance model, Eq. (1), assuming  $Cg = 1.6 \times 10^{-3}$  F/m<sup>2</sup>, and the  $n_{\rm imp}$ , calculated using the above relationship, versus the  $\frac{1}{\mu_{\rm eff}}$  for the GFETs with different gate lengths located at different positions on the Si wafer. It can be seen, that the data can be fitted by the straight line corresponding to the product  $n_0 \times \mu_{\rm eff} \approx 1.5 \times 10^{15} \ {\rm V}^{-1} {\rm s}^{-1}$ , indicating that the Coulomb scattering dominates. The deviation from the straight line at the  $\frac{1}{\mu_{\rm eff}}$  above approximately  $4 \times 10^{-4} \ {\rm Vs/cm^2}$ , *i.e.*, corresponding lower mobility values, can be explained by increasing contributions of the additional scattering mechanisms, *e.g.*, short range scattering associated with neutral defects and graphene ripples. <sup>44</sup> Alternatively, it can be explained by decreasing the  $\mu_{\rm eff}$  at shorter gate length due to increasing contribution of the quasi-ballistic transport, as shown below.

Fig. 4 clearly reveals a reduction of mobility with shorter gate length, which manifests the contribution of the ballistic motion to the charge carrier transport. The fact that the data from Ref.<sup>24</sup> show similar dependence on the gate length again supports results of this work. The straight lines in Fig. 4 are linear fits giving, in accordance with Eq. (4),  $\mu_0 = 2389 \text{ cm}^2/\text{Vs}$  and  $4456 \text{ cm}^2/\text{Vs}$ , while  $\lambda_B = 374 \text{ nm}$  and

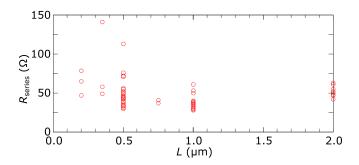

FIG. 6. Series resistance, found as fitting parameter of the drain-source resistance model assuming  $C_{\rm g}=1.6\times 10^{-3}~{\rm F/m^2}$ , versus gate length.

359 nm for  $C_{\rm g}=3.0\times10^{-3}~{\rm F/m^2}$  and  $1.6\times10^{-3}~{\rm F/m^2}$ , respectively. For comparison, the  $\mu_0$  and  $\lambda_{\rm B}$  found using the ambipolar virtual source model and a similar analysis of the  $\frac{1}{\mu_{\text{eff}}}$  versus  $\frac{1}{L}$  characteristics using Eq. (4) are reported to be 2702 cm<sup>2</sup>/Vs and 175 nm.<sup>14</sup> The larger values of the characteristic length found in our work can be explained by a higher quality of graphene, which should be associated with higher mobility. This indicates that the calculation of the mobility using the gate capacitance accounting for the interfacial states is more accurate, since it results in higher effective mobility. The values of the characteristic length found in this work agree well with that of  $300 \pm 100$  nm reported in Ref. <sup>17</sup> In Ref. <sup>17</sup> the collision mobility evaluated via measurement of transconductance was found to be up to 3500 cm<sup>2</sup>/Vs, which is also closer to that found in this work. The similarity of the values of the mobility and mean free path reported in Ref. 17 and those found in this work allows for conclusion that the methodology is reproducible and, hence, accurate enough.

Fig. 6 shows the  $R_{\rm series}$ , found as the fitting parameter of the drain-source resistance model (Eq. (1)) with the  $C_{\rm g}=1.6\times 10^{-3}$  F/m², versus gate length. As it can be seen, the  $R_{\rm series}$ , does not reveal any remarkable dependence on L in the studied range. This confirms, that the observed changes in  $R_{\rm total}$  with the scaling down are governed mainly by the reduction of the  $\mu_{\rm eff}$  due to contribution of the quasi-ballistic charge carrier transport. In our previous works, we demonstrated correlations of both  $R_{\rm ungated}$  and  $R_{\rm contact}$  with the low-field mobility, associated with concentration of the charged impurities at the graphene interfaces and in the adjacent dielectrics. Thus, the visible distributions of the  $R_{\rm series}$  at certain gate lengths, again, can be explained by the spatially inhomogeneous screened Coulomb potential caused by charged defects and impurities.

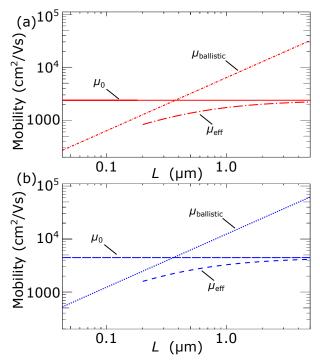

Knowing the  $\mu_0$  allows for the calculation of all mobility terms in Eq. (2). Fig. 7 shows the mobilities plotted versus gate length. The  $\mu_{\rm eff}$  is calculated as a reciprocal of the linear fits in Fig. 4. This plot clearly illustrates the transition of the charge carrier transport from the scattering regime through the quasi-ballistic to the purely ballistic regime with a reduction of the gate length. It can be seen that the scattering regime fully dominates above  $L\approx 4~\mu{\rm m}$  when the  $\mu_{\rm ballistic}$  is approximately 10 times larger than the  $\mu_0$ . In the quasi-ballistic

regime, which occurs when L is similar to  $\lambda_{\rm B}$  ( $\approx 0.4~\mu{\rm m}$ ),  $\mu_{\rm ballistic}$  is of the same order as  $\mu_0$ . The almost purely ballistic transport occurs below  $L \approx 0.04~\mu{\rm m}$  when the  $\mu_{\rm ballistic}$  is approximately 10 times smaller than the  $\mu_0$ . Transmission

FIG. 7. Effective, collision and ballistic mobility vs gate length calculated using Eq. (2) and Eq. (4) assuming  $C_{\rm g}=3.0\times10^{-3}~{\rm F/m^2}$  (a) and  $1.6\times10^{-3}~{\rm F/m^2}$  (b).

formalism treating the electrons as purely classical particles, *i.e.*, neglecting any quantum effects, gives the transmission probability through a conductor of length L by  $^{20}$

$$T = \frac{\lambda_{\rm B}}{L + \lambda_{\rm R}}. (5)$$

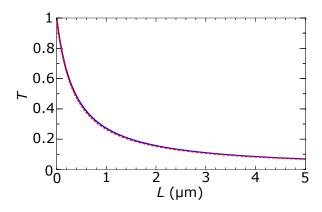

A similar expression is derived in the Lundstrom-model for the backscattering coefficient. To ur case the T is equal to the probability that a charge carrier moves without scattering. In the purely ballistic regime T=1, while in the quasi-ballistic regime T is smaller than 1, and much less than 1 for diffusive transport. Thus, the T can be considered as a measure of the ballisticity of a device. See Fig. 8 shows the transmission probability versus gate length calculated for our GFETs using Eq. (5), for both  $C_g=3.0\times10^{-3}$  F/m² and  $1.6\times10^{-3}$  F/m². The similarity of the T for both values of the  $C_g$  indicates relatively low sensitivity of the transmission probability calculated using Eq. (5) to the rather large uncertainty of the gate capacitance in the range studied in this work. One can explain it as follows. Combining Eqs. (4) and (1), at high enough  $V_{GS}$ , the transmission probability can be expresses as

$$T = 1 - \frac{\mu_{\text{eff}}}{\mu_0} = 1 - \frac{\frac{\partial I_{\text{ds}}^{\text{eff}}}{\partial V_{\text{ds}}}}{\frac{\partial I_{\text{ds}}^0}{\partial V_{\text{g}}}} \frac{C_g^0}{C_g^{\text{eff}}} = 1 - \frac{g_{\text{ds}}^{\text{eff}}}{g_{\text{ds}}^0} \frac{C_g^0}{C_g^{\text{eff}}}, \tag{6}$$

where  $I_{

m ds}^0$ ,  $g_{

m ds}^0$ ,  $C_{

m g}^0$  and  $I_{

m ds}^{

m eff}$ ,  $g_{

m ds}^{

m eff}$ ,  $C_{

m g}^{

m eff}$  are the drain current, drain conductance and gate capacitance per unit area in a long device and in the quasi-ballistic regime, respectively;  $V_{

m ds}$  is the drain voltage dropped on the gated region. One can assume that the gate capacitance per unit area does not depend on the gate length, i.e.,  $C_{

m g}^0 = C_{

m g}^{

m eff}$  and, therefore,

$$T = 1 - \frac{g_{\rm ds}^{\rm eff}}{g_{\rm ds}^0} \tag{7}$$

Thus, both T and, following Eq. (5),  $\lambda_B$  do not depend on the gate capacitance, *i.e.*, concentraton of the charge carriers, and are governed only by the response of the drain current to the variations of the drain field, *i.e.*, by contribution of the ballistic charge carriers. It can be seen from Fig. 8, that at  $L=2~\mu m$ , approximately 20 % of the charge carriers are moving ballistically. At  $L=0.2~\mu m$  this number increases to above 60 %. However, one should take into account that at such short gate lengths other mechanisms, like direct quantum tunnelling between source and drain, may contribute and govern the charge carrier transport. <sup>19</sup>

FIG. 8. Transmission probability vs gate length calculated using Eq. (5) assuming  $C_{\rm g}=3.0\times10^{-3}$  F/m  $^2$  (dashed line) and  $1.6\times10^{-3}$  F/m² (solid line).

### **CONCLUSION**

In conclusion, we found that effective mobility in the GFETs is more than halved with decreasing the gate length from 2.0  $\mu$ m down to 0.2  $\mu$ m. The effective mobility was evaluated via the drain-source resistance model with gate capacitance corrected using the geometrical magnetoresistance effect. The observed reduction of the effective mobility is associated with contribution of the ballistic motion to the charge carrier transport. We applied the concept of the ballistic mobility and found the carrier mean free path to be in the range of 359-374 nm. Analysis indicated that the scattering regime fully dominates at gate lengths larger than 4  $\mu$ m. At gate lengths similar to the mean free path, the quasi-ballistic regime occurs. The almost purely ballistic transport dominates at gate lengths below 0.04  $\mu$ m. By applying transmission formalism, we evaluated the transmission probability,

*i.e.*, probability of transport without collisions, and found that at the gate length of 2  $\mu$ m approximately 20 % of the charge carriers are moving ballistically. At the gate length of 0.2  $\mu$ m this number increases to above 60 %. The transmission probability was found to be relatively low sensitive to the variation of the gate capacitance studied in this work. Clarifying contribution of the ballistic motion to the charge carrier transport will allow for further development of GFETs, in particular, for advanced high-frequency applications.

#### Acknowledgment

The project is supported by grants from the LM Ericsson research foundation (grant number FOSTIFT - 21:007), A & LE Landahls minnesfond (grant number 90211117), Göran Wallbergs minnesfond (grant number SC 2021-0081, 90401199), Barbro Osher Pro Suecia Foundation (grant number SC 2021-0017, 90401181) and the EU Horizon 2020, Graphene Core 3 (Grant No 881603). The authors also thank M. Asad for his assistance in the GFET design and fabrication techniques.

- <sup>1</sup>A. K. Geim and K. S. Novoselov, "The rise of graphene," Nat. Mater. 6, 183–191 (2007).

- <sup>2</sup>A. Castro Neto, "The electronic properties of graphene," Reviews of Modern Physics **81**, 109–162 (2009).

- <sup>3</sup>Y. Lin, "100-GHz transistors from wafer-scale epitaxial graphene," Science **327**, 662 (2010).

- Schwierz, "Graphene transistors," Nat. Nanotechnol. 5, 487–496 (2010).

M. A. Yamoah, W. Yang, E. Pop, and D. Goldhaber-Gordon, "High velocity saturation in graphene encapsulated by hexagonal boron nitride," ACS Nano 11, 9914–9919 (2017).

- <sup>6</sup>M. Bonmann, A. Vorobiev, M. A. Andersson, and J. Stake, "Charge carrier velocity in graphene field-effect transistors," Applied Physics Letters 111, 233505 (2017), https://doi.org/10.1063/1.5003684.

- <sup>7</sup>A. Vorobiev, M. Bonmann, M. Asad, X. Yang, J. Stake, L. Banszerus, C. Stampfer, M. Otto, and D. Neumaier, "Graphene field-effect transistors for millimeter wave amplifiers," in *2019 44th International Conference on Infrared, Millimeter, and Terahertz Waves (IRMMW-THz)* (2019) pp. 1–2.

- 8I. Meric, M. Han, A. Young, and et al., "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," Nature Nanotech 3, 654–659 (2008).

- <sup>9</sup>V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," Applied Physics Letters **97**, 082112 (2010), https://doi.org/10.1063/1.3483130.

- <sup>10</sup>M. Asad, K. O. Jeppson, A. Vorobiev, M. Bonmann, and J. Stake, "Enhanced High-Frequency Performance of Top-Gated Graphene FETs Due to Substrate- Induced Improvements in Charge Carrier Saturation Velocity," IEEE Transactions on Electron Devices 68, 899–902 (2021).

- <sup>11</sup>M. Asad, S. Majdi, A. Vorobiev, K. Jeppson, J. Isberg, and J. Stake, "Graphene FET on Diamond for High-Frequency Electronics," IEEE Electron Device Letters 43, 300–303 (2022).

- <sup>12</sup>Y. Wu, K. A. Jenkins, A. Valdes-Garcia, D. B. Farmer, Y. Zhu, A. A. Bol, C. Dimitrakopoulos, W. Zhu, F. Xia, P. Avouris, and Y.-M. Lin, "State-of-the-art graphene high-frequency electronics," Nano Letters 12, 3062–3067 (2012), pMID: 22563820, https://doi.org/10.1021/nl300904k.

- <sup>13</sup>M. Shur, "Ballistic transport and terahertz electronics," in 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC) (2010) pp. 1–7.

- <sup>14</sup>S. Rakheja, Y. Wu, H. Wang, T. Palacios, P. Avouris, and D. A. Antoniadis, "An ambipolar virtual-source-based charge-current compact model for nanoscale graphene transistors," IEEE Transactions on Nanotechnology 13, 1005–1013 (2014).

- <sup>15</sup>M. Shur, "Low Ballistic Mobility in Submicron HEMTs," IEEE Electron Dev Lett 23 (2002).

- <sup>16</sup>I. Meric, "Channel Length Scaling in Graphene Field-Effect Transistors Studied with Pulsed Current-Voltage Measurements," Nano Letters 11, 1093–1097 (2011).

- <sup>17</sup>Z. Chen and J. Appenzeller, "Mobility extraction and quantum capacitance impact in high performance graphene field-effect transistor devices," in 2008 IEEE International Electron Devices Meeting (2008) pp. 1–4.

- <sup>18</sup> A. K. Upadhyay, A. K. Kushwaha, P. Rastogi, Y. S. Chauhan, and S. K. Vishvakarma, "Explicit model of channel charge, backscattering, and mobility for graphene fet in quasi-ballistic regime," IEEE Transactions on Electron Devices 65, 5468–5474 (2018).

- <sup>19</sup>J. Lusakowski, W. Knap, Y. Meziani, J.-P. Cesso, A. El Fatimy, R. Tauk, N. Dyakonova, G. Ghibaudo, F. Boeuf, and T. Skotnicki, "Electron mobility in quasi-ballistic Si MOSFETs," Solid-State Electronics 50, 632–636 (2006), special Issue: Papers Selected from the 35th European Solid-State Device Research Conference ESSDERC'05.

- <sup>20</sup>S. Datta, *Electronic Transport in Mesoscopic Systems*, Cambridge Studies in Semiconductor Physics and Microelectronic Engineering (Cambridge University Press, 1995).

- <sup>21</sup>I. Harrysson Rodrigues, A. Generalov, M. Soikkeli, A. Murros, S. Arpiainen, and A. Vorobiev, "Geometrical magnetoresistance effect and mobility in graphene field-effect transistors," Applied Physics Letters 121, 013502 (2022), https://doi.org/10.1063/5.0088564.

- <sup>22</sup>S. ang Peng, Z. Jin, P. Ma, D. yong Zhang, J. yuan Shi, J. bin Niu, X. yun Wang, S. qing Wang, M. Li, X. yu Liu, T. chun Ye, Y. hui Zhang, Z. ying Chen, and G. hui Yu, "The sheet resistance of graphene under contact and its effect on the derived specific contact resistivity," Carbon 82, 500–505 (2015).

- $^{23}$ M. Bonmann, M. Asad, X. Yang, A. Generalov, A. Vorobiev, L. Banszerus, C. Stampfer, M. Otto, D. Neumaier, and J. Stake, "Graphene field-effect transistors with high extrinsic  $f_T$  and  $f_{\rm max}$ ," IEEE Electron Device Letters **40**, 131–134 (2019).

- <sup>24</sup>M. Asad, M. Bonmann, X. Yang, A. Vorobiev, K. Jeppson, L. Banszerus, M. Otto, C. Stampfer, D. Neumaier, and J. Stake, "The dependence of the high-frequency performance of graphene field-effect transistors on channel transport properties," IEEE Journal of the Electron Devices Society 8, 457–464 (2020).

- <sup>25</sup>I. Harrysson Rodrigues, Charge carrier transport in field-effect transistors with two-dimensional electron gas channels studied using geometrical magnetoresistance effect., Ph.D. thesis, series: 5194 (Chalmers University of Technology, 2022).

- <sup>26</sup>"Graphenea," https://www.graphenea.com (2010).

- <sup>27</sup>M. Asad, *Impact of adjacent dielectrics on the high-frequency performance of graphene field-effect transistors.*, Ph.D. thesis, series: 8754 (Chalmers University of Technology, 2021).

- <sup>28</sup>F. Xia, V. Perebeinos, Y. Lin, Y. Wu, and P. Avouris, "The origins and limits of metal-graphene junction resistance," Nat Nanotechnol. 6, 179–84 (2011).

- <sup>29</sup>L. Wang, I. Meric, P. Huang, Q. Gao, Y. Gao, H. Tran, T. Taniguchi, K. Watanabe, L. Campos, D. Muller, J. Guo, P. Kim, J. Hone, K. Shepard, and C. Dean, "One-dimensional electrical contact to a two-dimensional material," Science, 614–7 ((2013)).

- <sup>30</sup>X. Yang, M. Bonmann, A. Vorobiev, and J. Stake, "Characterization of Al<sub>2</sub>O<sub>3</sub> gate dielectric for graphene electronics on flexible substrates," in

- 2016 Global Symposium on Millimeter Waves (GSMM) and ESA Workshop on Millimetre-Wave Technology and Applications (2016) pp. 1–4.

- <sup>31</sup>M. Groner, J. Elam, F. Fabreguette, and S. George, "Electrical characterization of thin Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition on silicon and various metal substrates," Thin Solid Films 413, 186–197 (2002).

- <sup>32</sup>S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. K. Banerjee, "Realization of a high mobility dual-gated graphene fieldeffect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric," Applied Physics Letters **94**, 062107 (2009), https://doi.org/10.1063/1.3077021.

- <sup>33</sup>M. Bonmann, A. Vorobiev, J. Stake, and O. Engström, "Effect of oxide traps on channel transport characteristics in graphene field effect transistors," Journal of Vacuum Science Technology B 35, 01A115 (2017), https://doi.org/10.1116/1.4973904.

- <sup>34</sup>J. Wang and M. Lundstrom, "Ballistic transport in high electron mobility transistors," IEEE Transactions on Electron Devices 50, 1604–1609 (2003).

- <sup>35</sup>C. K. Ullal, J. Shi, and R. Sundararaman, "Electron mobility in graphene without invoking the Dirac equation," American Journal of Physics 87, 291–295 (2019), https://doi.org/10.1119/1.5092453.

- <sup>36</sup>M. Lundstrom, "On the mobility versus drain current relation for a nanoscale mosfet," IEEE Electron Device Letters 22, 293–295 (2001).

- <sup>37</sup>A. Hamed, M. Asad, M.-D. Wei, A. Vorobiev, J. Stake, and R. Negra, "Integrated 10-ghz graphene fet amplifier," IEEE Journal of Microwaves 1, 821–826 (2021).

- <sup>38</sup>S. Adam, E. H. Hwang, V. M. Galitski, and S. Das Sarma, "A self-consistent theory for graphene transport," Proceedings of the National Academy of Sciences 104, 18392–18397 (2007), https://www.pnas.org/content/104/47/18392.full.pdf.

- <sup>39</sup>S. Bidmeshkipour, A. Vorobiev, M. A. Andersson, A. Kompany, and J. Stake, "Effect of ferroelectric substrate on carrier mobility in graphene field-effect transistors," Applied Physics Letters **107**, 173106 (2015), https://doi.org/10.1063/1.4934696.

- <sup>40</sup>Y. Zhang, V. Brar, C. Girit, and et al., "Origin of spatial charge inhomogeneity in graphene," Nature Phys, 722–726 (2009).

- <sup>41</sup> Adsorbates on graphene: Impurity states and electron scattering," Chemical Physics Letters **476**, 125–134 (2009).

- <sup>42</sup>M. J. Hollander, M. LaBella, Z. R. Hughes, M. Zhu, K. A. Trumbull, R. Cavalero, D. W. Snyder, X. Wang, E. Hwang, S. Datta, and J. A. Robinson, "Enhanced transport and transistor performance with oxide seeded high-k gate dielectrics on wafer-scale epitaxial graphene," Nano Letters 11, 3601–3607 (2011), pMID: 21805989, https://doi.org/10.1021/nl201358y.

- <sup>43</sup>J. Buron, F. Pizzocchero, P. Jepsen, and et al., "Graphene mobility mapping." Sci Rep 5, 12305 ((2015)).

- <sup>44</sup>S. Adam, E. Hwang, and S. Das Sarma, "Scattering mechanisms and Boltzmann transport in graphene," Physica E: Low-dimensional Systems and Nanostructures 40, 1022–1025 (2008).

- <sup>45</sup>J. Chen, C. Jang, S. Adam, M. S. Fuhrer, E. D. Williams, and M. Ishigami, "Charged-impurity scattering in graphene," Nature Phys. 4, 377–381 (2008).

- <sup>46</sup>J. Chan, A. Venugopal, A. Pirkle, S. McDonnell, D. Hinojos, C. W. Magnuson, R. S. Ruoff, L. Colombo, R. M. Wallace, and E. M. Vogel, "Reducing extrinsic performance-limiting factors in graphene grown by chemical vapor deposition," ACS Nano 6, 3224–3229 (2012), pMID: 22390298, https://doi.org/10.1021/nn300107f.