### The Schottky barrier transistor in emerging electronic devices

Citation for the original published paper (version of record):

Schwarz, M., Vethaak, T., Derycke, V. et al (2023). The Schottky barrier transistor in emerging electronic devices. Nanotechnology, 34(35). http://dx.doi.org/10.1088/1361-6528/acd05f

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

#### **TOPICAL REVIEW • OPEN ACCESS**

## The Schottky barrier transistor in emerging electronic devices

To cite this article: Mike Schwarz et al 2023 Nanotechnology 34 352002

View the <u>article online</u> for updates and enhancements.

#### You may also like

- (Invited) Ionic Liquid-Gated PCBM Transistors: Pushing the Limit of the Doping in Organic Transistors Jonathan Sayago, Mitesh Patel, Fabio Cicoira et al.

- Transient Phenomena in Ion Sensitive Field Effect Transistors Rosemary L. Smith, Jii Janata and Robert J. Huber

- <u>Double Epitaxial Isolation Method for the Fabrication of Integrated Circuit Transistors</u>

Kiyoshi Demizu

#### **Topical Review**

# The Schottky barrier transistor in emerging electronic devices

Mike Schwarz<sup>1,10</sup>, Tom D Vethaak<sup>2,10</sup>, Vincent Derycke<sup>3</sup>, Anaïs Francheteau<sup>4</sup>, Benjamin Iniguez<sup>5</sup>, Satender Kataria<sup>6</sup>, Alexander Kloes<sup>1</sup>, Francois Lefloch<sup>4</sup>, Max Lemme<sup>6</sup>, John P Snyder<sup>7</sup>, Walter M Weber<sup>8</sup> and Laurie E Calvet<sup>9,\*</sup>

E-mail: mike.schwarz@ei.thm.de, vethaak@chalmers.se and laurie.calvet@cnrs.fr

Received 30 September 2022, revised 20 March 2023 Accepted for publication 25 April 2023 Published 15 June 2023

#### Abstract

This paper explores how the Schottky barrier (SB) transistor is used in a variety of applications and material systems. A discussion of SB formation, current transport processes, and an overview of modeling are first considered. Three discussions follow, which detail the role of SB transistors in high performance, ubiquitous and cryogenic electronics. For high performance computing, the SB typically needs to be minimized to achieve optimal performance and we explore the methods adopted in carbon nanotube technology and two-dimensional electronics. On the contrary for ubiquitous electronics, the SB can be used advantageously in source-gated transistors and reconfigurable field-effect transistors (FETs) for sensors, neuromorphic hardware and security applications. Similarly, judicious use of an SB can be an asset for applications involving Josephson junction FETs.

Keywords: Schottky barriers, field effect transistors, thin film transistors, source-gated transistors, 2D materials, 1D materials, Josephson junctions

(Some figures may appear in colour only in the online journal)

Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

#### 1. Introduction

The direction taken by the semiconductor industry has been greatly influenced by new innovations. Planar technology led to enhanced integrated circuits and advances in computing from the 1960s onward. In addition to significantly improving device performance on bulk substrates, it also enabled the first thin film transistors (TFTs), where the channel is formed from a material deposited onto a substrated instead of from the bulk

<sup>&</sup>lt;sup>1</sup>THM University of Applied Sciences, Germany

<sup>&</sup>lt;sup>2</sup> Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-412 96 Gothenburg, Sweden

<sup>&</sup>lt;sup>3</sup> Université Paris-Saclay, CEA, CNRS, NIMBE, LICSEN, Gif-sur-Yvette, F-91191, France

<sup>&</sup>lt;sup>4</sup> University Grenoble Alps, GINP, CEA-IRIG-PHELIQS, Grenoble, France

<sup>&</sup>lt;sup>5</sup> Universitaet Rovira i Virgili (URV), Spain

<sup>&</sup>lt;sup>6</sup>RWTH Aachen, Germany

<sup>&</sup>lt;sup>7</sup> JCap, LLC, United States of America

<sup>&</sup>lt;sup>8</sup> Technische Universität Wien, Institute of Solid State Electronics, Vienna, Austria

<sup>&</sup>lt;sup>9</sup> LPICM, CNRS-Ecole Polytechnique, Palaiseau, France

<sup>10</sup> These authors contributed equally to this work.

<sup>\*</sup> Author to whom any correspondence should be addressed.

wafer. The turn of the century marked the beginning of wide interest in non-planar geometries with the introduction of the FIN field-effect transistor, FINFET, featuring source/drain 'fin' regions and a gate wrapping around the channel [1]. Most recently, emerging nano-materials, including those realized in one- and two-dimensions have led to a large variety of new technologies for integrated circuits [2]. Devices based on this plethora of novel materials often involve non-ohmic source-drain contacts, also known as Schottky barriers (SBs), which can arise not only between the interface of different materials, but also due to different geometrical constraints such as contacting a 1D nanowire or nanotube to a 3D metal.

The rectifying nature of metal-semiconductor junctions (MSJs) was first observed in 1874 by Ferdinand Braun [3] using a point-contact geometry. MTJs have been important for industrial applications since their use in the 1900s as radio detectors [4], which were notably vital during WWII. With the advent of planar techniques, the main advantage of SB junctions became their speed, due to majority carrier transport, and their ability to support high power operation compared to p—n junctions. Modern applications include their use as gates in metal-semiconductor field effect transistors (MESFETs), power devices, photodetectors, and solar cells, while of course they remain important for RF and microwave devices [5].

The use of SBs as a replacement to the doped source and drain regions of a transistor was first proposed in 1966 [6]. It was often considered as a device that would always perform worse than a conventional MOSFET because of the increased source/drain resistance. While simulations have shown that for very small devices, the SB can be an asset, they have not been commercially viable to date [7–9]. Some of the advantages that they still afford, such as economy of fabrication, may prove them yet to be an exploitable technology as the increased environmental and monetary costs of computing become more problematic. Emerging technologies such as carbon nanotube transistors are also essentially SB devices and are being considered as a promising candidate for computing in the 2028–2037 time frame [2].

As devices for computing become ever more exigent and the performance of 1D and 2D materials is enhanced to meet this challenge, the line between research in TFTs and those for high performance computing intersects. A variety of different materials fabricated in TFT geometries are now promising for use in many different electronic devices, which we term ubiquitous electronics [10], where very high performance may not be needed. TFTs are often limited by their comparatively poor material properties (low mobility, large variability due to lower precision fabrication methods), which give rise to scaling limitations. However, advantageous use of a gated SB, commonly called a source gated transistor or SGT [11], can significantly improve device performance and promises to reduce device sizes into the nanometer regime. Another emerging technology that uses SBs advantageously is the reconfigurable field-effect transistor (RFET), where gating of the SB enables operation as an n- or p-type transistor at will [12]. This allows for decreased complexity and reconfiguring of circuits at the level of the devices.

Operation of conventional MOSFETs is well-known to improve as temperature is decreased, due to an increase in mobility from decreased phonon scattering. Nevertheless operation at low temperatures has not been exploited due to the difficulty and expense of cooling. With the recent interest in quantum computing technologies, however, cryogenic electronics is of increasing importance. At very low temperatures, carriers in semiconductors freeze out and contacts therefore need to be degenerately doped or made from Schottky barriers. SBMOSFET transistors thus hold some potential for low temperature applications. In addition, if the metallic source and drain become superconducting, a novel type of quantum computing implementation can be realized.

Schottky barrier devices are thus of increasing importance in three different fields of emerging electronic technologies: high performance computing, ubiquitous electronics and cryogenic electronics. By reviewing how SB devices can be used advantageously in these fields in a single paper, we hope to enable synergies between distant fields that can enhance research going forward. The rest of this section focuses on some of the basic physics necessary to understand these devices and brings the reader up to date with the most recent research in theoretical modeling. It concludes with a discussion of Si and Ge SBMOSFETs, which have been widely studied and serve as a basis for understanding the other technologies explored here. The remaining sections are organized according to these three main fields of application: (1) high performance computing, (2) ubiquitous electronics and (3) cryogenic electronics. Throughout we include references to more specialized reviews and focus on the role of Schottky devices.

#### 1.1. Formation of the Schottky barrier

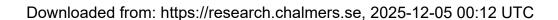

When a metal with work function  $\phi_m$  is placed into intimate contact with a semiconductor with an electron affinity  $\chi$  and Fermi level position  $\phi_n$  below the conduction band, a net charge transfer occurs at the interface. An ideal theory for understanding these junctions, due to Mott and Schottky, is depicted in the energy band diagram in figure 1 for  $\phi_m > \chi + \phi_n$ . An abrupt barrier, called the SB, arises at the MSJ due to the delta function of charge at the metallic interface. A charge depleted region that extends into the semiconductor also forms. In comparison with a p-n junction, where there is a depletion region on both sides of the interface, the SB allows for a much smaller space-charge region. SBMOSFETs are therefore advantageous for avoiding the merging of the depletion widths, which results in short-channel effects in reduced-dimension MOSFETs.

The standard ideal description of MSJs assumes that (a) a maximum electric field occurs in the semiconductor, very close to the interface (due to image charge lowering) [13], (b) the only charges involved in the semiconductor are the donor impurities with concentration  $N_{\rm D}$ , and (c) the space charge region is confined to a depletion zone, delimited by width  $W_{\rm D}$ .

**Figure 1.** Energy-band diagrams of MSJs. (a) Relative electronic energies of a high work-function metal and an n-type semiconductor in separate systems. The work function of the metal  $q\phi_{\rm m}$  is the difference between the Fermi level  $E_{\rm f}$  and vacuum level  $E_{\rm 0}$  [5]. (b) Relative electronic energies of the two systems in intimate contact. As the distance between the two systems is decreased, a barrier  $q\phi_{\rm Bn0}$  between the interface results, as shown in (b). The band bending in the semiconductor represents the built-in potential, where  $\phi_{\rm bi} = \phi_{\rm m} - \chi - \phi_{\rm n}$ . From [5] John Wiley & Sons. Copyright © 2007 John Wiley & Sons, Inc. All rights reserved.

Solving the Poisson equation we find

$$W_D = \sqrt{\frac{2\epsilon_0 \epsilon_{\rm s}}{q N_{\rm D}}} \left( \phi_{\rm bi} - V - \frac{k_{\rm B}T}{q} \right),\tag{1}$$

where  $\epsilon_{\rm s}$  is the dielectric constant of semiconductor,  $k_{\rm B}$  is the Boltzmann constant, T is the temperature in Kelvin, V is the applied voltage, and  $\phi_{\rm bi}$  is the band bending in the semiconductor, known as the built-in potential. The length of the depletion region decreases with increasing doping concentration, which in general is limited by the solid solubility limit of the particular dopant. Note, however, that advanced techniques such as gas immersion laser doping [14] can overcome this limitation and are an important area of ongoing research.

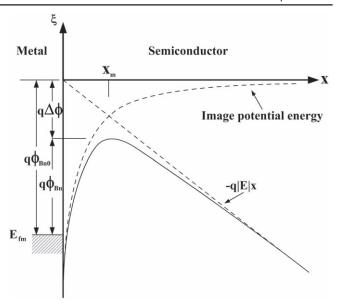

Image charge lowering plays a role in the electrostatics during electron transport and becomes increasingly important in reduced-dimensional devices. As depicted in figure 2, this lowering is the result of the reduced field at the interface from the electrostatic attraction of a negative charge moving towards it. The resultant image charge lowers the barrier by

$$\Delta \phi = \sqrt{\frac{qE}{4\pi\epsilon_s}},\tag{2}$$

where E is the externally applied electric field across the metal/semiconductor interface.

Although this ideal theory is taught in semiconductor physics classes, we know from extensive research that the observed barrier height is rarely the one obtained from this analysis. While larger work-function metals do tend to have larger barrier heights, the dependence is much weaker than expected. The lack of correlation between the barrier height and the work-function is often attributed generically to 'Fermi-level pinning', covering a wide variety of different effects, including inhomogeneities at the junction, surface

**Figure 2.** Energy band diagram of Schottky barrier lowering between a metal surface and an n-type semiconductor. Note that the barrier is not at the MSJ, but is located at a distance  $X_{\rm m}$  from the interface. [5] John Wiley & Sons. Copyright © 2007 John Wiley & Sons, Inc. All rights reserved.

states at the interface due to either defects or to metal induced states, or chemical bonding at the interface [15]. Many of these models have similar dependencies with temperature and voltage and it is therefore difficult to disentangle the origin of the deviations of the barrier height without additional structural characterization techniques or different experimental conditions for the formation of the SB. Nevertheless, enormous progress in understanding has been achieved, as described in two excellent review articles [15, 16]. This progress originates from three significant advances: (1) the realization of epitaxial MSJs using molecular-beam epitaxy resulting in inhomogeneity-free interfaces, (2) the advent of scanning probe technologies allowing electrical measurements of nano-scale junctions, and (3) the development of powerful computers enabling first-principles ab initio calculations. This knowledge now makes it possible to understand and engineer the SB to a high degree of precision. For simulations and after an eventual optimization of the experimental devices, the Schottky barrier height (SBH) can be considered a parameter obtained from measurements. The mostly widely explored MSJs involve silicon/metallic silicon alloys, known as silicides, because of their wide industrial use in CMOS technology. These investigations have allowed thorough investigations of Si SBMOSFET devices.

Understanding the SB formation in more novel materials is an important subject of current research. An excellent review on the nature of contacts with one- and two-dimensional materials can be found in [17], while more recent reviews focused on two-dimensional materials can be found in [18–20]. Understanding the image charge lowering in bounded geometries [21] and the variation of the SB height in nanowire geometries have been explored by Calahorra *et al* [22], and measurements of barrier heights on Si nanowires

using photoemission have been carried out by Yoon et al [23].

#### 1.2. Current Transport

Electron transport in rectifying MSJs can be broadly grouped into 3 limiting transport mechanisms [5, 24]: (1) transport over the barrier, (2) tunneling through the barrier including direct, thermal- and trap-assisted tunneling, and (3) mechanisms occurring just adjacent to the barrier, such as diffusion and recombination. The overall current is modeled by a combination of these processes. Room temperature transport processes at the SB junctions that are used for transistors are most typically fully described by transport over the barrier via thermionic emission (TE), and direct/thermal assisted tunneling through the barrier [9], which are therefore the focus of this section.

The large majority of treatments of the current transport in SB diodes use semi-classical approximations. For TE and diffusion transport the basic equations can be rigorously derived from the Boltzmann transport equation [25], which provides a complete description of the distribution function. This formalism assumes that the band structure can be included into an effective mass and that the potential due to the applied field is small and does not vary rapidly in space.

The thermionic theory, proposed by Bethe [26] in 1942, describes how carriers with energies larger than  $q\phi_{Bn}$  or  $q\phi_{Bp}$  overcome the SB and contribute to electron transport. The total current is the sum of the two current densities that flow from the metal to the semiconductor and from the semiconductor to the metal. The current density is found by integrating over the concentration of electrons with velocities  $v_x$  in the transport direction and sufficient energy to overcome the barrier. In this classical calculation, the velocity is isotropic and given by a Maxwellian distribution with band structure taken into account via an effective mass  $m^*$ . The sum of both current contributions for electrons is given by [13, 27–29]

$$J_n = J_{\text{TE}} \left[ \exp\left(\frac{qV}{k_{\text{B}}T}\right) - 1 \right],\tag{3}$$

where

$$J_{\text{TE}} = A^* T^2 \exp\left(-\frac{q\phi_{\text{Bn0}}}{k_{\text{B}}T}\right). \tag{4}$$

Here  $\phi_{\mathrm{Bn0}}$  denotes the intrinsic barrier height and

$$A^* \equiv \frac{4\pi q m^* k_{\rm B}^2}{h^3} \tag{5}$$

is the effective Richardson constant with h the Planck constant and  $m^*$  the effective mass. In this approximation quantum-mechanical reflections and optical-phonon scattering have been neglected, but detailed research has shown how to include these effects [28, 30] and subsequently how to include them in a modified effective Richardson constant. In silicon,  $A^* = 120 \,\mathrm{A\,cm}^{-2}\,\mathrm{K}^{-2}$  for electrons and  $40 \,\mathrm{A\,cm}^{-2}\,\mathrm{K}^{-2}$  for holes. Other descriptions of transport over the barrier can include diffusion theory [5], which becomes important for

materials with a small density of states. Image-force lowering must also be included, where the resulting barrier height  $\phi_{\rm Bn0}$  for electrons from equation (4) is reduced by  $\Delta\phi$  from equation (2) [5]. The effective mass in the prefactor of this equation results in lower thermionic field emission for materials like Ge and GaAs.

Typical treatments of quantum mechanical tunneling in SB devices follow the method first considered by Bardeen [31], originally developed to explain tunneling in superconducting electrodes separated by a thin oxide. It was later extended by Harrison [32] to include regions of varying band structure. This approach solves the Schrödinger equation directly by separating the system into distinct sub-systems with known Hamiltonians and then uses the Fermi golden rule to obtain the transition probability, assumed to be constant in energy. Stratton first applied it to tunneling between two conductors through an insulator, assuming parabolic energymomentum relations [33], and later to SBs [24]. The main shortcoming of the latter paper was that the pre-exponential terms in the forward and reverse bias resulted in different constants, such that it was unable to obtain zero current at zero bias. This was resolved by the work of Crowell [13], who noticed that due to image charge lowering the barrier occurs not at the metal/semiconductor interface but inside the semiconductor. Therefore, the effective mass Richardson constant should always be that of semiconductor.

Following Crowell, the tunneling current from the semiconductor to the metal (after integration over momentum transverse to the metal/semiconductor interface) is given by [34]

$$J = \frac{A^*T}{k_{\rm B}} \int_0^\infty d\xi [f_{\rm s}(\xi) - f_{\rm m}(\xi)] \mathcal{T}(\xi), \tag{6}$$

where  $f_s(\xi)$  and  $f_m(\xi)$  are respectively the Fermi–Dirac distribution functions of occupied states on the semiconductor side of the junction and unoccupied states on the metal side of the junction, and  $\mathcal{T}(\xi)$  is the one-dimensional transmission probability for the barrier with an energy  $\xi$ , associated with the component of momentum normal to the metal-semi-conductor interface. Note that this equation can also describe TE when  $\mathcal{T}(\xi) = 1$  and the limits of integration extend to the top of the barrier. In this framework, calculating the tunneling current is reduced to calculating the transmission coefficient.

Before discussing how the transmission coefficient can be calculated, we first briefly discuss the Richardson constant  $A^*$ , which appears in both the tunneling and the TE equations. In the ideal theory  $A^*$  is defined by equation (5), but the effective mass used in this equation can be different for direct tunneling versus thermally assisted tunneling and TE [13, 25]. Nevertheless, this work assumes that the effective mass should be that of the semiconductor and independent of the metal and that there is no interfacial oxide layer between the metal and the semiconductor. Research by Toyama has shown, however, that the Richardson constant varies with film thickness [35, 36]. Work exploring tunneling of metal-insulator-semiconductor junctions showed that the effective mass of each region needed to be included in order to

correctly match boundary conditions [37, 38]. Variations of the Richardson constant from the ideal value are thus often attributed to the presence of a tunnel barrier at the MSJ and the resulting impact due to the additional prefactor from this mismatch of effective mass. More recently, the effective mass of the metal was used to obtain a value intermediate between that of the metal and that of the semiconductor, and was used to explain TE transport in SB SiC diodes [39].

The transmission coefficient  $T(\xi)$  has been the target of many different approximations. The most extensively used technique is the Wentzel-Kramers-Brillouin (WKB) approximation, which assumes that the amplitude of the wavefunction varies slowly compared to the phase so that, as in the classical case, the total energy is greater than the potential energy [40–42]. The Gundlach method [43] assumes that the potential barrier is linear, and transforms the Schrödinger equation into Airy functions. The transfer matrix method approximates the barrier in the transport direction as piecewise linear functions and determines the transmission coefficient for each one. Finally, the wavelet methodology approximates the wavefunction by a wavelet [44, 45].

We briefly recall the WKB approximation for determining the transmission coefficient [40–42]:

$$T(\xi) = \exp\left(-\frac{2}{\hbar} \int_{x_1}^{x_2} \sqrt{2m(V(x) - \xi)} \ dx\right), \tag{7}$$

where  $x_1$  and  $x_2$  are the classical turning points,  $\xi \leqslant V(x)$  and equation (7) is real. This approximation has been extensively explored by Padovani and Stratton [24] for barriers of arbitrary shape. Most often, however, it is approximated as triangular, with  $V(x) = q \ \phi_{\rm Bn0} - qEx$ . This results in the analytical solution

$$T(\xi) = \exp\left(-4\frac{\sqrt{2m^*}}{3\hbar qE}(q\phi_{\rm Bn0} - \xi)^{3/2}\right),$$

(8)

which leads to Fowler-Nordheim type equations.

As devices are scaled down, three-dimensional calculations become inaccurate. Other formalisms that can be employed include Wigner functions, the non-equilibrium Green's functions (NEGF)—Landauer method and/or combining these with *ab initio* calculations. The Wigner distribution function method [46] has typically been used to explore transport in systems far from equilibrium, most notably resonant tunneling diodes [47], where the non-stationary description is important. It models the system using a density operator (the Wigner function) whose time evolution is given by the Liouville-von Neumann equation. Solutions can be obtained using either finite difference or Monte Carlo methods. This technique has also successfully been applied to explore quantum transport in ultra-scaled MOSFETs [48].

A large majority of the models that are used to model transport through the SBs in SBMOSFETs are based on the semi-classical TE and tunneling methods because the quantum methods consume large computing resources for just the calculation of transport at the SB. Quantum techniques that describe transport in SBMOSFETs typically use the SB

height as a boundary condition, grouping the different types of transport into a unified treatment [49, 50].

#### 1.3. Silicon and germanium SBMOSFETs

During the past 25 years, research has shown that Si SBMOSFETs are intrinsically lower cost, more energy efficient and inherently more scalable than conventional doped source/drain MOSFETs [7–9]. As a result of the many obstacles in realizing this technology, however, there has been little industrial exploitation. We briefly review their fabrication and advantages as they serve as a basis for all the SB transistors considered in this review.

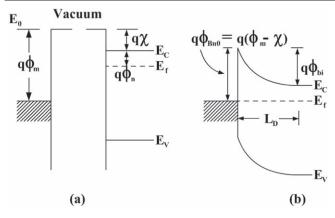

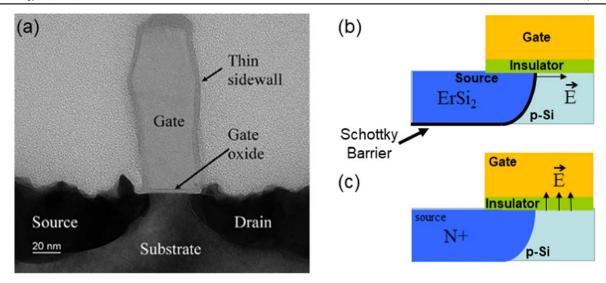

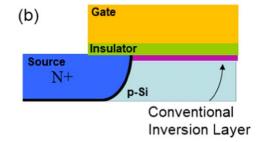

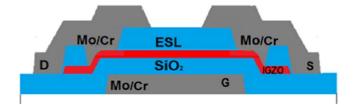

SBMOSFETs as depicted in figure 3(a), are realized by depositing a metallic layer onto the semiconductor source and drain contact regions, typically with a self-aligned process. To ensure reproducible, void-free and geometrically well-defined metal/silicon interface regions, a post-deposition anneal (PDA) step is carried out. In silicon the metallic region formed by the PDA typically results in a metallic alloy, known as a silicide [51]. These materials have been widely used in conventional doped source/drain FETs (DSDFETs) to realize ohmic contacts at the doped source and drain regions, as well as for doped poly-Si gate electrodes. The formation of many metal silicides is a result of the diffusion of the metallic atoms into the silicon. For SB transistors this leads to an overlap of the source/drain regions with the gate and additional control over the band bending near the interface. MSJs involving low-doped silicon result in Fermi-level pinning closer to the valence band edge, resulting in a low SB height for holes. Rare-earth silicides such as those involving yttrium, erbium, holmium, dysprosium and gadolinium [52] form low n-type Schottky barriers to silicon. By comparison, for Ge, where the metallic compounds are known as metal germanides [53], there is generally a lower phase stability compared to silicides.

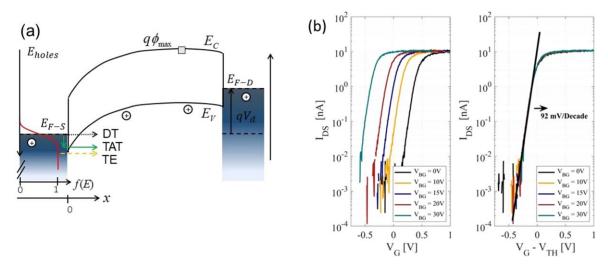

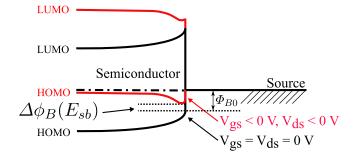

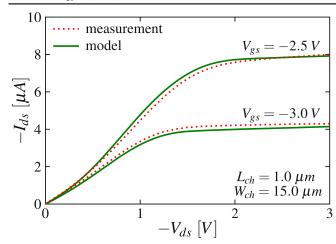

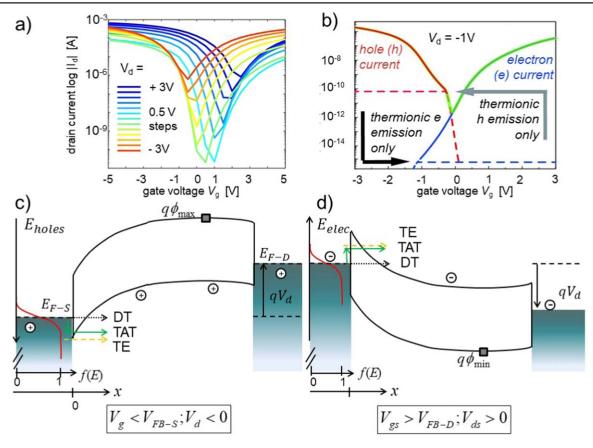

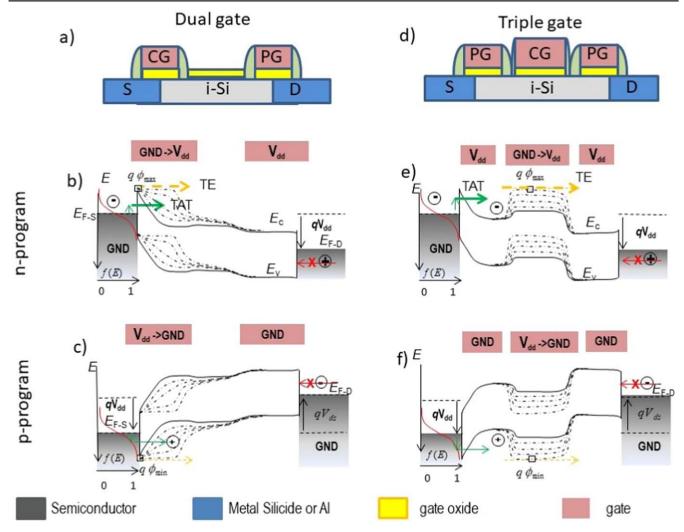

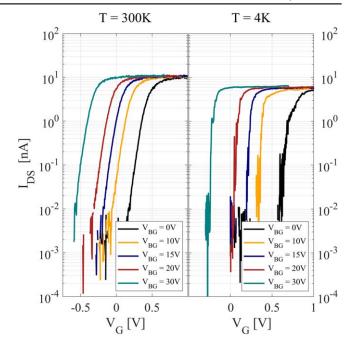

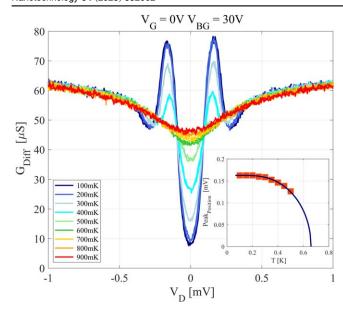

Depending on the SB height of the junctions, two distinct operating regimes are differentiated: (a) unipolar SBMOSFET with small barrier height or near-ohmic contacts for electrons or holes and (b) ambipolar SBMOSFET with a substantial barrier height for both electrons and holes. An ideal SBMOSFET for high performance computing corresponds to type (a), with the SB at the source playing a significant role in preventing the 'off' state leakage current between the source and the channel [7]. In the on state the SBs would become nearly or even completely transparent and the device would operate as a conventional doped source/drain FET (DSDFET). In the ideal case then, the difference in transport would be predominantly found in the sub-threshold region. For low power analog electronics, case (b), ambipolar SBMOSFETs can be employed, as will be discussed in the section on ubiquitous computing. Figure 4 shows a schematic band diagram and transfer characteristics of a Si SBMOSFET device. Figure 4(a) is biased as a p-type transistor in the on state, where the band bending is inverted so that not only TE over the barrier occurs but also direct and thermal assisted tunneling processes. These are the same processes described for MSJs in section 1.2. An example of the characteristics of a

**Figure 3.** (a) High-resolution TEM of a 22 nm p-type SBMOSFET. (b) A Schottky barrier exists along the perimeter of the source (and drain) electrodes, where there is contact to the silicon substrate. This barrier presents an impedance to the flow of current in the device that is not present in a conventional doped source/drain MOSFET. The electric field  $\vec{E}$  at the SB, indicated by the arrow is normal to the metallic surface and therefore has a strong lateral component, especially near the source. In contrast, the electric field near the source in a conventional device (c) is nearly vertical. [2006] IEEE. Reprinted, with permission, from [7].

Figure 4. (a) Schematic band diagram of a p-type SBMOSFET in the 'on' state with three possible types of transport indicated (direct tunneling, DT, thermal assisted tunneling, TAT, and TE). (b) Room-temperature characteristics of an experimental PtSi-based SBMOSFET on FDSOI at  $V_d = 100~\mu$ A. The transistor was fabricated using standard CMOS technologies [55, 56] with a buried oxide layer (BOX) of 145 nm and a slightly n-doped channel (800 nm wide/60 nm long). The silicon substrate can be used as a back-gate, in addition to the top gate. (Left) Source/drain current  $I_{\rm ds}$  vs top-gate voltage for various values of the applied back gate voltage  $V_{\rm bg}$ . (Right) Scaling of  $I_{\rm ds}$  vs  $V_{\rm g}$ – $V_{\rm Th}$  for various values of  $V_{\rm bg}$ . The solid line shows the SS.

pSBMOSFET is shown in the device in figure 4(b) with a Subthreshold Swing SS of 92 mV Decade<sup>-1</sup>. Understanding the current transport mechanisms in the sub-threshold and other regimes of operation is an important part of the literature. Note that the effective barrier to transport in the sub-threshold regime includes not only the SB height, but also the height of the bands that rises above it. In this region, transport occurs by TE and the current is very small. Nevertheless, the changing effective barrier height to carriers, due to changes in gate potential, causes large changes in the sub-threshold current in the channel. The threshold voltage in bulk SB

devices can thus be defined as the  $V_{\rm g}$  value corresponding to the flat-band voltage [54].

Ideally, on-state device performance is equivalent to that of DSDFETs. In practice, however, this will occur only when the SB is completely transparent, which is challenging to achieve. Nevertheless, linear or ohmic contacts can be realised by strong or even degenerate doping of the semiconductor, where the SBH to the valence or conduction band edges can be reduced to 0.1 eV. Moreover, for doped Si and Ge semiconductors a special situation can occur during the PDA when the phenomenon of dopant segregation takes place. This has been observed experimentally through ion

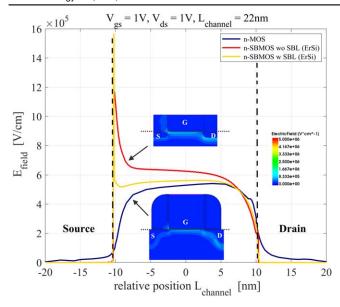

**Figure 5.** Comparison of the electric field underneath the silicon oxide of n-type SBMOSFET versus classical n-type MOSFET (coordinates origin set to the center of the device). The simulations were performed for the follwing device charactersitics:  $V_d=1~\rm V$ ,  $V_g=1~\rm V$ ,  $T=300~\rm K$ ,  $L_{\rm channel}=22~\rm nm$ . The electric field for the SBMOSFET is one order of magnitude greaterthan for the MOSFET. The effect of Schottky barrier lowering strengthens this effect. Note that ErSi was introduced with a Schottky barrier height of 0.27 eV and a nonlocal tunneling model was used for the n-type barrier.

SIMS profiles and further described theoretically with DFT calculations by Kinoshita et al [57]. Typical dopant impurities for Si and Ge, like P, As, Sb and B, show a low or even zero solubility in many metal silicides and germanides [58]. Consequently, during the metal-silicide/-germanide growth, the impurity atoms initially residing in the transformed semiconductor region are dissolved and displaced by diffusion and finally accumulate in the semiconductor adjacent to the MSJ. Measurements show that the dopant atoms are not built into the semiconductor lattice because of the low silicide formation temperatures. Instead, they tend to reside as interstitials, influencing the band alignment at the Schottky junction. Experiments demonstrated that B and As dopants in CoSi<sub>2</sub>/Si junctions [57] and B, P and As dopants in  $Ni_xSi_{1-x}/Si$  films [59] are the most efficient for dopant seggregation.

The SB at the source/drain will thus influence the flow of current and the distribution of charges and depend on the device materials, the voltages, temperature of operation and other factors such as interface states, barrier inhomogeneities [60], etc. The device physics of the SBMOSFET can be quite complex. We now address the more subtle differences between SBMOSFSETs and DSDFETs with a focus on the advantages of SBMOSFETs.

1.3.1. Charge transport near the Schottky barrier. The metallic source/drain electrodes constrain the electric field to be normal to their surfaces and will be determined almost exclusively by the shape of the metallic electrodes, as shown

in the simulations in figure 5. This contrasts conventional DSDFETs, where, except in specific circumstances, such as near the drain under high drain voltage, the field near the source is largely vertical. It is independent of the details of the source/drain regions, as shown schematically in figure 3(c) and in the lateral direction by the simulations in figure 5. Carrier emission from the source is simply from one type of silicon to another and there is no abrupt change in velocity as charge carriers transit from source to channel.

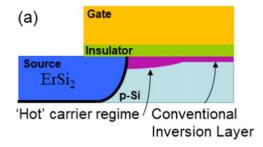

Multiple authors have explored experimentally and via two-dimensional (2D) technology computed aided design (TCAD) simulations the effects of a metallic source/drain on device performance. A review from 2006 describes earlier devices [7], while Valentin [61–63], Pearman [64, 65], Raskin [66] and Du [67] have documented the differences in transconductance  $(g_m)$ , gate capacitance  $(C_{gg})$  and unity current gain frequency  $(f_T)$  between SBMOSFETs and conventional DSDFETs. All of these investigations show that despite reductions in  $g_{\rm m}$ ,  $f_{\rm T}$  is higher for SBMOSFETs compared to DSDFETs because of significant reductions in  $C_{\rm gg}$ . The root cause of the reductions in  $C_{\rm gg}$  with finite SB height at the source/drain junctions remains unclear, but we see two possibilities. The first is that the SB limits transport in the channel resulting in less charge and therefore less sensitivity in the channel region to changes in gate voltage, as explored by Valentin [61] and Pearman [64]. The second one is that strong lateral electric fields near the source result in 'hot' charge carriers—carriers not in thermal equilibrium with the lattice-transiting the channel at a depth somewhat beneath the gate oxide. These carriers are likely 'hot', due to large initial velocities when emitted from the metallic source electrode, where Fermi velocities can be 10-20 times the saturation velocity of carriers in silicon. A qualitative comparison of the inversion layers—not based on simulation but rather educated approximation—is shown in figure 6. Within the Thomas–Fermi approximation, carriers leaving the source will travel approximately the Debye length before their velocity adjusts to that of the semiconductor [5]. Such effects have been especially observed to result in a strong injection of charges from the source into the gate in asymmetric transistors with a single source SB, such as in [68]. This effect should become more important as device dimensiond approach the Debye length, (20 nm at a doping of  $1 \times 10^{17} \,\mathrm{cm}^{-3}[5]$ ). Its existence could explain, at least in part, the observed decrease in  $C_{\rm gg}$ .

A series of papers by Shih, Luo and co-authors [69–73] have examined, both via 2D TCAD simulation and experiment, the effects of metallic source and drain electrodes on the performance of both floating gate and charge trapping non-volatile memory cells. Their results show how charge carriers near the source attain velocities large enough to enable charge trapping in oxide-nitride-oxide (ONO) structures, something that is not observed in conventional DSDFETs, in accordance with the schematic depiction in figure 6. Further, programming efficiencies are observed to be several orders of magnitude larger for SBMOSFETs, which can be explained by large velocities near the source. Simulations of injected charge in ONO films show the lateral

**Figure 6.** Schematic depiction of carrier injection from the source into the channel region for: (a) an SBMOSFET and (b) a conventional DSDFET. In the case of (a), large lateral electric fields near the source are postulated to produce hot carriers, that is, carriers not in thermal equilibrium with the silicon lattice, a phenomena that is not observed in (b), which features a conventional inversion layer in thermal equilibrium with the lattice at the source-end of the device.

extent of the charge distribution to be around 20 nm, about  $3 \times \text{smaller}$  than for conventional DSDFETs, and in agreement with the order of magnitude of the Debye length.

The effects of these source-side hot-carriers on long-term device degradation and reliability has received little attention in the literature and is a field of study that deserves significant attention.

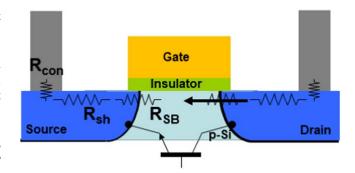

1.3.2. Lower parasitics and off current. There are two parasitics that can be significantly different in SBMOSFET devices: the parasitic series resistance, the parasitic bipolar gain. The parasitic series resistance, defined as unwanted resistance external to the channel of the transistor, is greatly reduced in an SBMOSFET compared to a conventional DSDFET. The MSJ resistance, which is the largest component in a DSDFET, is now technically part of the channel in an SBMOSFET and is therefore no longer parasitic. While this may seem a mere exercise in semantics, there are important differences. In DSDFETs, the resistance associated with the SB,  $R_{SB}$  is generally a fixed, constant number and depends only on the SB height and doping density on the semiconductor side. Often, a mid-gap SB system is used (for both p and n-FETs), with a high doping density.

As we saw from our discussion above,  $R_{\rm SB}$  for an SBMOSFET strongly depends on the gate voltage. Typically a metal with a low SB to the conduction band of the semiconductor is used for n-type devices and a metal with a low SB to the valence band is used for p-type devices, with the exception of RFETs, which require mid-gap SB heights. The overall channel resistance of an SBMOSFET, including the Schottky junctions on either end, is therefore a strong function of the gate voltage. The sheet resistance of the metal,  $R_{\rm sh}$ , which is 1–2 orders of magnitude smaller than that of doped silicon, is still present, depicted in figure 7. There is also the very small metal-to-metal contact resistance  $(R_{con})$  to the plugs, which connect to upper metal layers. The parasitic resistance in an SBMOSFET is therefore an almost negligible fraction of the total resistance (typically  $\sim 1\%$  or less [7]). For a conventional DSDFET the parasitic resistance can be much larger, as high as 50% in highly scaled devices.

An n-type DSDFET typically has heavily doped n-type source/drain regions and an oppositely doped (p-type) body region. As a result, there is an unavoidable parasitic NPN

**Figure 7.** Parasitics in SBMOSFETs. For SBMOSFETs  $R_{\rm SB}$  is technically part of the channel and is therefore not parasitic. The relatively small sheet resistance  $(R_{\rm sh})$  of the metallic source (and drain), along with the very small metal-to-metal contact resistances  $(R_{\rm con})$  of the plugs from the upper layers of metal make up the total parasitic resistance for the SBMOSFET. The intrinsic parasitic bipolar transistor is also shown.

bipolar transistor. Under normal operating conditions this NPN is dormant, as the base-emitter junction is not forward biased because the source and body potentials are usually tied together or, in some cases, reverse biased. However, the body can become forward biased with respect to the source if, for example, the p-type body is filled with holes resulting from either impact ionization in the inversion layer or from an ionstrike. The NPN can then become activated and will amplify the original hole current into a much larger electron current. Bipolar amplification gains of around  $\sim 200 \times$  are typical for silicon NPN devices. Worse, this mechanism can, under the right conditions, become self-sustaining and uncontrolled by the gate electrode, usually resulting in the destruction of the device and the surrounding circuitry. This positive feedback loop can occur within single transistors or in CMOS circuits with complementary n- and p-type devices. Modern device designs such as fully depleted silicon on insulator, FDSOI, Tri-Gate FETs, FinFETs, and GAAFETs attempt to mitigate this problem by operating at low supply voltages to minimize impact ionization and also by minimizing the volume of the body region to limit charge collection during an ion-strike. SBMOSFETs, however, have a key advantage in this respect: the gain of the NPN device is much less than unity, and therefore the positive feedback loop mentioned previously cannot exist. This is due to differences between the physics of current transport across a Schottky junction (thermal emission) vs a p-n junction (drift-diffusion). As a result, SBMOSFETs are inherently immune to all parasitic bipolar action. This is true regardless of device profile, doping profiles, ionization radiation intensity, temperature, device layout, operating voltage, etc. Device design is thus liberated from having to consider unwanted bipolar gain, providing a real advantage especially in some cases, for example in power devices.

Minimizing the off-state leakage between source and drain in DSDFETs is a major challenge for highly scaled devices where direct source-to-drain tunneling currents can occur. The presence of a finite SB at the source/channel interface therefore provides SBMOSFETs with a built-in advantage. Modern device designs such as the tri-gate FET, FinFETs and gate-all-around FETs (GAAFETs) are all attempts to exert greater gate control over the channel in order to reduce off-state leakage while keeping on-state drive current large.

The leakage currents in a conventional DSDFET are controlled by creating electrostatic barriers in the channel, denoted as  $\phi_{es}$ , by introducing dopants of the appropriate type, concentration and location into the substrate, and/or gate material engineering. These techniques work equally well in an SBMOSFET and serve to augment the existing SB,  $\phi_{\rm SB}$ , in order to create a larger total barrier ( $\phi_{\rm tot}$ ) and lower the leakage current. The presence of a finite  $\phi_{SB}$  allows for a measure of flexibility in device design. Specifically,  $\phi_{\rm es}$  can be reduced via channel doping and/or gate material engineering, to keep the leakage current constant compared to the zero- $\phi_{\rm SB}$  case. Simulations have shown that the channel doping for a 25 nm SBMOSFET can be reduced by as much as 1–2 orders of magnitude [7]. Reductions in channel doping may also lead to beneficial reductions in gate and junction capacitance, due to the wider extension of depletion regions. Of course, the presence of a SB will also impede the flow of current in the on state. The net effects of the SB on both the drive and leakage currents will depend on the details of the device architecture: SB height, source and drain position and profile, channel dopants, channel length, etc.

As devices approach the sub-10 nm regime, direct source-to-drain tunneling becomes important in MOSFETs. Simulations by Cho *et al* used NEGF simulations to compare sub-10 nm SB and double-gate MOSFETs and showed that methods such as source/drain underlap and optimization of the body thickness can suppress direct source-to-drain tunneling in both devices, but that the double-gate MOSFETs show higher performance due to higher drive currents [8]. The caveat of this work, however, is that the SB was assumed to be 0.1 eV, and image charge lowering was not considered. Semiclassical simulations that do take this into account suggest that at nanoscale sizes the image charge lowering can reduce the barrier sufficiently to make it transparent [9].

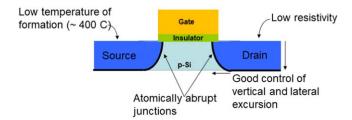

1.3.3. Improved Manufacturability. If the metallic source/drain regions of an SBMOSFET are silicides, as is almost always the case in Si devices, there are several manufacturability advantages compared to a conventional

**Figure 8.** An illustration of the manufacturability advantages of the SBMOSFET over conventional DSDFETs.

DSDFET (figure 8). Most important are the simplicity and lower energy associated with the silicide formation. Metal deposition, anneal and unreacted-metal strip are done at much lower processing temperatures compared to doping, and are high-throughput and high-yield steps. Silicides for both p and n-type devices, for example PtSi and ErSi2 respectively, are typically formed at 450 °C, cause no damage to the lattice, and result in low-resistance films that have atomically abrupt interfaces to the silicon substrate. The final lateral and vertical extent of the silicide film is determined by the thickness of the original metal layer, which, once reacted to completion, is invariant with additional annealing, thus providing a wide process margin. The contact resistance of these silicides to metal 'plugs' from upper metal layers is also very small, as expected for metal-to-metal contacts. Overall the SBMOSFET will have fewer processing steps and also consume less energy due to removal of the doping steps. Therefore, it remains a very interesting device for industrial use, especially for applications seeking to reduce energy consumption and process complexity.

## 2. Schottky barrier transistors in high performance computing applications

A large part of the semiconductor industry focuses on realizing the fastest and smallest transistors for intensive computing applications such as data centers, scientific calculations and artificial intelligence. Conventional techniques to improve MOSFET performance are (1) reducing the channel length (and simultaneously scaling the other parameters to limit short channel effects); (2) thinning the transistor's body (as in FDSOI devices) or wrapping the gate all-around the channel (as in trigate or GAA transistors) to improve electrostatic control over the channel potential; and (3) increasing the channel carrier mobility using a combination of materials and strain engineering.

Shrinking transistor dimensions using a top-down approach becomes increasingly difficult at nanoscale sizes. For this reason, there is great interest in bottom-up fabrication strategies, and in particular synthesizing nanoscale building blocks such as nanowires, nanotubes, graphene and transition metal dichalcogenides for use as starting materials. Transistors made from these nanomaterials can be considered as TFTs, but historically, these two communities have had limited interactions. A recent article makes important inroads into developing benchmarks and performance metrics [74].

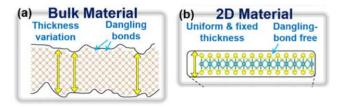

**Figure 9.** Schematic representation of (a) a very thin bulk material and (b) a 2D material with atomic thickness levels. © [2015] IEEE. Reprinted, with permission, from [81].

An overview of nanomaterials in transistor geometries can be found in [75], the use of 2D materials for future integrated circuits is discussed in [76], and [77] provides a recent overview of digital electronics using carbon nanotubes. Excellent reviews on the state of the art of nanowire electronics and bottom-up silicon nanowires can be found in [78] and [79, 80] respectively.

There has become a fine line between technologies meant to target high performance computing applications and those that can be used for ubiquitous electronics, discussed in section 3 of this article, as what might be a detriment in one may serve as an advantage in the other. In this section, we consider devices realized in 1D and 2D materials and focus on how the SB can be problematic for high performance devices. This leads to section 3, ubiquitous electronics, where the focus is on devices that can take advantage of the SB.

#### 2.1. 2D materials

2D materials are an ultimate solution to thinning the transistor body to improve electrostatics. The atomic thickness may enable very small gate length 2D FETs, thus paving the way for gate length scaling into the nanometer and even subnanometer regime [76, 81]. The significant ongoing research and development effort has resulted in the technology being identified by the international roadmap for devices and systems (IRDS) as a potential candidate for devices beyond CMOS [2]. Nevertheless, a large contact resistance is observed in 2D devices, typically preventing experimental realizations that are competitive with contemporary Si or even Carbon NanoTube CNT technology.

These materials exist in a large variety of classes including metallic, semiconducting, insulating, and recently even magnetic and superconducting. The schematic comparison of 2D and bulk materials in figure 9 [81] shows how the surfaces of 2D materials are free from dangling bonds, consistent with physical properties at the monolayer regime [82–84]. A dominant critical issue is therefore the interface engineering and especially the optimization of the contacts. Several proposed solutions include inserting a buffer layer between semiconductor and metal, realizing van der Waals (VdW) contacts, edge contacts, novel doping and surface engineering. These techniques have been described in an excellent recent review [20]. Nevertheless, SBs can easily dominate the transport and many 2D semiconducting transistors are essentially small-scale SBFETs [85].

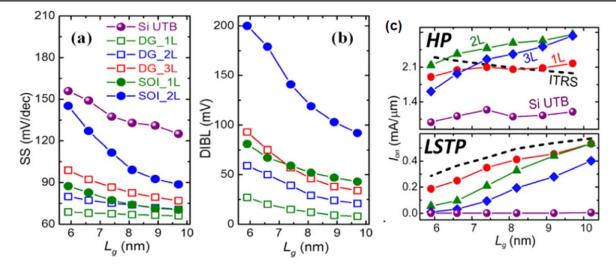

Although the first exfoliated 2D semiconductor was reported in 1986 [86], it was the demonstration of the electric field-effect in single layer graphene, exhibiting unprecedented carrier mobilities and ballistic transport at room temperature [87], that sparked the recent intensive research effort. Graphene, however, has a zero band gap and is not suitable for logic applications, although it may find use in radio frequency applications [88]. Numerous 2D materials have been explored in this context for the past 10 years and are the subject of ongoing research to develop potential electronic applications [89, 90]. Of particular importance are single-layer 2D FET devices based on the transition metal dichalcogenide (TMDs) family, which have a general formula MX2, where M is a transition metal (e.g. Mo, W) and X is a chalcogen atom (eg. S, Se, Te) [91]. Mo and W-based TMDs are semiconducting with a thickness-dependent band gap that transitions from indirect (bulk) to direct (up to a few-monolayers) [92]. Cao et al rigorously analyzed the performance and scalability of 2D semiconductors, especially MoS<sub>2</sub>, through dissipative quantum transport simulations for sub-10 nm technology nodes [81]. Figure 10 clearly demonstrates that MoS<sub>2</sub> transistors outperform Si devices in terms of (a) evaluated SS and (b) drain induced barrier lowering (DIBL). In (c), calculated Ion for devices with different numbers of layers of MoS<sub>2</sub> and Si are compared for high performance and low standby power technologies. It is observed that MoS<sub>2</sub> devices show higher  $I_{\rm on}$  compared to Si devices because of the poor electrostatics in the latter. More than 3 layers of MoS<sub>2</sub> must be avoided for sub-10 nm nodes, however, because of worsening electrostatics. Experimental MoS<sub>2</sub> FETs have indeed shown superior immunity to short-channel effects [93], and also high saturation velocity  $(2.8 \times 10^6 \,\mathrm{cm \, s^{-1}})$  in few-layer devices [94]. Nevertheless, the main problem remains the high source/ drain contact resistance. Shen et al have recently reported breakthrough results of ultra-low contact resistance using Bi contacts to MoS<sub>2</sub> transistors, and proposed that Bi-TMD technology could potentially meet the IRDS targets for logic transistors [95]. Nevertheless the thermal stability of this solution may prevent its large scale implementation.

It has been more difficult to realize p-type TMD FETs due to strong Fermi-level pinning at the semiconductor interface with most metals, which also results in large contact resistances [96]. Li *et al* fabricated p-FETs based on few-layer black phosphorus (BP) that demonstrated reliable performance and ambipolar behavior [97]. Realization of transistors in ambipolar materials such as WSe<sub>2</sub> and WS [98] have also been explored. To date their device performance for high performance computing has not been assessed as well as the MoS<sub>2</sub> devices.

In order to improve the performance of existing FET technology based on 2D materials, different device architectures are also being investigated. These include devices based on vertical and lateral heterostructures of 2D materials. 2D–2D heterostructures are known to form either Schottky contacts or PN junctions, depending on the type of material used. Graphene is generally used as the contact material, while semiconducting 2D materials are used as the channel or junction materials, and hBN is used as the gate dielectric [99].

Figure 10. A comparison of (a) SS, (b) DIBL, and (c) on-current vs gate length for ultra thin body Si, and one to three layer (L)  $MoS_2$  FETs that are double-gated or semiconductor-on-insulator (SOI) structures. HP and LSTP stand for high performance and low STandby power technologies. © [2015] IEEE. Reprinted, with permission, from [81].

Heterojuction FETs based on heterostructures of 2D/3D materials are also being investigated. Here, 2D materials have an edge over conventional channel materials such as Si for the fabrication of ultimately scaled heterojunction FETs, as field-effect modulation of the current transport through the heterojunction provides a unique opportunity to realize band-to-band tunneling devices.

Perhaps the greatest promise for 2D materials for high performance computing is the possibility to design novel devices, and ultimately architectures based on stacking, that is not possible in conventional silicon technologies. Two recent review articles have detailed this in greater depth [100, 101]. In this way, the disadvantage of the source/drain contact resistance is offet by an advantage not possible in conventional semiconductor technologies.

#### 2.2. Carbon Nanotubes

Single-walled carbon nanotubes (SWNTs) and nanowires have been considered as potential building blocks for future microelectronic devices because of their very small diameters and the excellent properties exhibited by single-transistor devices. Like 2D materials, the connection between nanotube and metallic contacts results in a SB, but solutions are now available to render the barrier negligible in the on-state. Simulations predict impressive 5-fold [102] to 9-fold [103] improvements in the energy-delay product (EDP) (notably coming from lower-bias operation) in comparison to Si or Si/ SiGe FinFETs. The two main difficulties have been synthesizing only semiconducting SWNTs and doping the nanotubes, but some laboratories have now met the criteria for ultra large scale integration [77]. In order to do justice to this very large body of work, we first provide an overview of the advantages and disadvantages of this technology. We then focus on the role of the SB between the nanotube and the metallic contacts.

SWNTs are hollow cylinders made of sp2-bonded carbon atoms, with a diameter in the 0.7–3 nm range. Their structure,

properties and applications have been thoroughly reviewed [104–106], as well as their specific electronic and transport properties [107, 108]. Depending on their chirality (diameter and helicity), they can have a metallic or semiconducting character. In the latter case, their direct band gap scales as  $\sim 0.8/d$  (with d the diameter in nm) so that typical diameters (1–1.4 nm) yield sizable band gaps (0.6–0.8 eV).

The most important assets of SWNTs in the context of carbon nanotube FETs (CNTFETs) are: (i) their atomic structure is free of dangling bounds and rugosity (which notably makes them compatible with high- $\kappa$  gate dielectrics without mobility degradation [109-111]); (ii) their band structure is symmetric for holes and electrons (resulting in similar  $m^*$  for both types of charge carriers); (iii) their capacitance is low [112], which is particularly advantageous at high-frequency [113, 114]; (iv) they have exceptionally high carrier mobility for both electrons and holes; (v) they can withstand extremely high current densities (>0.5 mA  $\mu$ m<sup>-2</sup> for arrays) [2]; and (vi) charge back-scattering processes associated to defects are not efficient; (vii) at low electric field the electron (and hole) mean free path associated with acoustic phonons is as high as 300-500nm. It is reduced to  $\sim$ 20 nm at high electric field due to optical phonons [108, 115, 116].

Transport in SWNTs is mostly ballistic at low bias in long-channel devices (<300 nm) and at all biases in aggressively scaled devices (<20 nm). The mobility in long SWNTs (corresponding to low electric field) scales as  $d^2/T$  [117], and at RT it has been estimated to be  $>10^5$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for large diameter nanotubes [115]. The highest experimentally measured value, however, is  $\mu = 79\,000$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for an ultralong SWNT ( $L>300\,\mu\text{m}$ ) [118] but values in the  $2500-20\,000$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> range are more typical.

This technology also has some disadvantages. The main one is the difficulty in synthesizing uniquely semiconducting nanotubes. In addition, substitutional doping, which is one of the great strengths of silicon technologies, is not possible in carbon nanotubes. Alternative chemical and electrostatic doping strategies exist but are often unstable (such as potassium or molecular doping) and/or poorly scalable (such as multiple gates). It also remains extremely difficult to control the selective placement of SWNTs. To obtain high enough drive currents, optimized CNTFETs need to be composed of several parallel nanotubes with an optimized CNT–CNT pitch (5 nm) [75, 102], small enough to allow high current densities but not too small to ensure that the advantage of 1D electrostatics can be maintained. Research therefore focuses either on demonstrating devices and circuits using FETs made up of arrays of CNTs, or transistors with an individual nanotube, to explore device properties and scaling. Arrays typically exhibit a degraded SS and leakage current [119], due to the presence of metallic nanotubes.

Individual SWNTs were integrated as channels in FETs as early as 1998 [120, 121]. In these devices and in most of the following ones, metallic source and drain electrodes directly connect the undoped nanotube channel so that they operate as Schottky-barrier FETs [122]. Such SBMOSFET operation is notably central to understand their (lateral and vertical) scaling behavior [109, 123-125]. The change in band gap with diameter renders large diameters subject to ambipolar leakage currents, and very small diameters susceptible to large contact resistance. The ideal diameter has been predicted to be  $\sim 1.7$  nm [102]. It is important to note that n- and p-type CNFETs operating as conventional MOS-FETs (i.e. not as SBMOSFETs) were also fabricated by doping sections of the nanotube close to the metal source and drain electrodes. This resulted in improved performance but, as mentioned, the unstable chemical doping or poorly scalable multi-gate designs used strongly limit their applications when compared with simpler, more scalable self-aligned gate SBMOSFET designs [126]. Recent work has demonstrated a new electrostatic doping strategy to realize excellent control over the p-type and n-type CNTFETs using non-stoichiometric oxides [127].

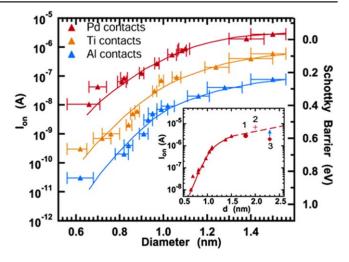

A crucial difference between conventional metal/semiconductor Schottky contacts and nanotube/metal interfaces is the limited effect of Fermi-level pinning in the latter case. As a result, the SB heights in both p- and n-type nanotube SBMOSFETs were shown to principally depend on the metal work function and on the nanotube diameter (through its impact on the band gap), as shown in figure 11. High workfunction metals (e.g. Au, Pd [128]) typically result in good p-type FETs, while low work-function metals (Sc [129], Y [130]) allow good n-type FETs. Interestingly, mid-gap alignment (i.e. high SB height for both electrons and holes) results in low drive currents for bulk-silicon SBMOSFETs, but on the contrary, leads to efficient ambipolar SBMOSFETs with carbon nanotubes [131]. Indeed in SWNTs, band bending occurs at the nm scale and the low  $m^*$  favors tunneling through high (yet thin) barriers. Note that ambipolar nanotube SBMOSFETs were shown to be important in carbon nanotube optoelectronics, as reviewed in [132, 133].

Another important observation is the significantly different device performance obtained with metals of rather similar work function. In particular, palladium was shown to

**Figure 11.**  $I_{\rm ON}$  and Schottky barrier height of carbon nanotube SBFETs as a function of nanotube diameter for Pd, Ti, and Al metal contacts. Devices are fabricated on 10 nm SiO<sub>2</sub>, with channel length of 300 nm and  $V_{\rm ds} = -0.5$  V. Reprinted with permission from [134]. Copyright (2005) American Chemical Society.

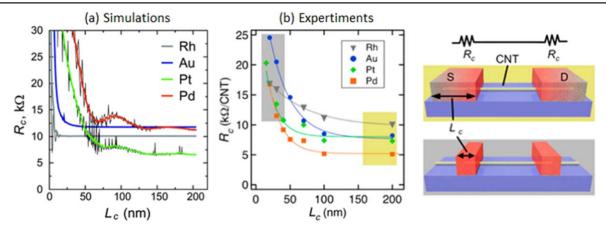

be the ideal metal for p-type CNTFET, which cannot be accounted for by its work function alone. This led to a vast number of computational studies addressing the details of the metal/nanotube interface and the impact of weak versus strong interactions on the contact resistance (see notably [135] and references therein). In particular, the contact length  $L_{\rm c}$  (the length of the nanotube section embedded below the source and drain metal contacts), which was initially mostly neglected became a central element in determining the ultimate performance of aggressively scaled devices [136, 137]. Weakly interacting metals (such as palladium) usually give the best performance when  $L_{\rm c}$  is kept long enough (typically above 50–100 nm). But for short contacts, the contact resistance  $R_{\rm c}$  scales as  $L_{\rm c}^{-1}$  for most metals (Au, Pt, Pd).

Aggressively scaling the channel length only makes sense if  $L_c$  is also drastically reduced, which is why the details of the  $R_c(L_c)$  scaling are a central issue in the field. Figure 12 from [135] and [138] summarizes simulations and experiments, and highlights a key element going forward: metals with the lowest  $R_c$  at long  $L_c$  (notably Pd) may not be those with the best scaling trends. Conversely, Rh, which is not particularly remarkable for  $L_c = 100 \,\mathrm{nm}$ , becomes a promising choice for  $L_c = 20 \text{ nm}$  [138]. The current state of the art in terms of scaled contact length consists of either: (i) endbonded molybdenum carbide contacts that allow high performance  $(2R_c < 36 \text{ k}\Omega/\text{nanotube})$  down to  $L_c = 9 \text{ nm}$ . Contrary to Pd and Rh contacts, the nanotube section below the annealed molybdenum metal is destroyed and replaced by a Mo<sub>2</sub>C carbide, or (ii) more conventional Pd contacts with  $L_{\rm c} = 10 \, \rm nm$ , which do not require a high temperature annealing step but also yield  $2 \cdot R_c = 36 \,\mathrm{k}\Omega/\mathrm{nanotube}$  as median value (and even  $2 \cdot R_c = 13 \text{ k}\Omega/\text{nanotube}$  for the best device) [139].

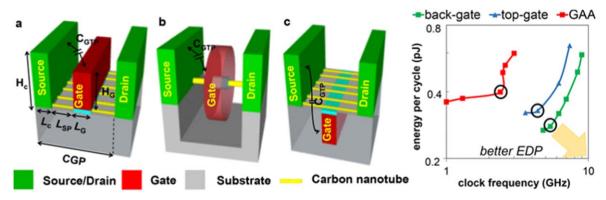

Contact type and contact length optimization is clearly a key aspect for CNT-SBMOSFET improvement. However, the channel length scaling and the choice of the device topology

Figure 12. Dependence of the contact resistance  $R_c$  on the contact length  $L_c$  in carbon nanotube SBFETs. (a) Simulations from Fediai *et al* [135]. (b) Experiments from Franklin *et al* [138]. Reprinted with permission from [138]. Copyright (2014) American Chemical Society.

Figure 13. Schematic of different CNTFET geometries (a)–(c) and total energy versus frequency of a simulated 32-bit processor showing the Energy Delay Product EDP trade-off curves for back-gate, top-gate, and GAA CNFETs. The back-gate technology was subsequently used to realize a RISC-V microprocessor [149]. © [2019] IEEE. Reprinted, with permission, from [147].

(in particular of the gate stack) are equally important issues. Channel length scaling studies started as early as 2004 with  $L_{\rm ch}$  lower than 50 nm [126] and it was later shown that CNT SBMOSFETs with  $L_{\rm ch} = 15 \, \rm nm$  do not suffer from shortchannel effects. High performance CNTFETs with channel length below 10 nm [140, 141], even down to 5 nm, were then achieved [142]. In terms of geometry, a large majority of the experimental studies used planar back-gate or top-gate designs. Due to the cylindrical nature of SWNTs, it was naturally considered that a gate-all-around geometry would be ideal from an electrostatic point of view and this geometry was routinely used in calculations [124, 125, 143] In addition, its high symmetry makes the simulation less demanding. Such gate-all-around designs were successfully realized experimentally [144–146]. The cylindrical geometry efficiently shields the channel from parasitic charges, although it is not clear yet whether it actually leads to the best performance. Not only is it much more difficult to engineer, but recent studies have also shown that higher clock frequencies can be obtained with simpler geometries, as exemplified in figure 13 [147, 148], due to reduced parasitics.

Although the material characteristics of carbon nanotubes were recognized as promising when they were discovered in 1991 [150], it took 20 years before their use was demonstrated in significantly complex circuits [151]. The research

described in this section focused on aligned transistors, the channel of which is either an individual CNT or a large number of parallel CNTs with a channel length much shorter than the CNT length. Another class of nanotube-based devices are CNT-TFTs, for which the channel is a dense array of randomly oriented CNTs with a channel length either longer or shorter than the average CNT length. CNT-TFTS were initially considered for applications that required low to moderate performances (in particular for flexible electronics or flexible displays), because either the density of CNTs was not high or because the channel dimensions were micron size, resulting in relatively small mobilities. These types of CNT TFTs are briefly discussed in section 3.4. More recent research has shown how non-aligned arrays of CNT transistors can be used to realize high speed logic (2 GHz) using high-purity solution processing [152] and how high-performance devices are compatible with fabrication in commercial silicon manufacturing facilities [153]. In the latter reference, simulations showed that the impact of non-aligned TFTs, as compared to aligned arrays, is less than 20% when channel lengths are smaller than 500 nm, and the density of tubes is below 56 tubes/micron. We thus see that many of the problems in realizing CNT devices, such as the purity and positioning, have solutions, and we can expect to see demonstrations of high-performing complex circuits of CNTs in the coming years [154], with the potential to move CMOS beyond Si [149, 155].

#### 2.3. Nanowire transistors

Compared to the CNTs described in the last section, semiconductor nanowires are not closed, allowing the possibility to form bonds with a surrounding medium, for instance with a dielectric material. By varying the nanowire diameter, the electronic structure can be tuned from that of the bulk to one exhibiting quantum confinement, occuring when the diameter is comparable to or smaller than the Fermi wavelength of the semiconductor material. In addition to the possibility of exploiting the one-dimensional density of states, nanowires allow for monolithically combining different materials, which is the relevant for MSJs, both in longitudinal and radial coordinates. Here we focus only on how this type of transistor can be used for SBMOSFET devices.

Semiconductor nanowires are highly promising for implementing diverse types of emerging electronic and optoelectronic devices making efficient use of Schottky junctions. Distinctly different from bulk and thin films, this one-dimensional structure allows for an enhanced relaxation of mechanical lattice strain when combining materials with highly mismatching lattice constants and crystal structures [156]. Metal-nanowire SBs can exhibit unique properties related to the diameter [17, 22, 157, 158]. SBMOSFETs built from nanowires can achieve the ultimate electrostatic gate coupling to the channel and SB when a surround gate stack (thin insulator oxide with high dielectric constant and metallic gate electrode) is employed and the semiconductor body is sufficiently thin. A practical method to assess the influence of the channel potential to an externally applied electric gate field and thus the scalability of MOSFETs and SBMOSFETs is given by the so called natural length of the transistor. The method, has been applied to different MOSFETs in analogy to a Debye screening length, considering a specific channel geometry, doping concentration, gate insulator and gate electrode architecture. The natural length describes a critical distance, typically measured from source, across the channel length upon which the potential and thus the bands react to the external field, and is thus often taken as a figure of merit to compare the scaling behavior between different MOSFET architectures. Through this approach Auth and Plummer described the scaling behavior of surround gated semiconductor nanowires [159], proving its efficacy in reducing short channel effects.

Nanowires have been fabricated both by conventional top-down fabrication schemes, i.e. using deterministic lithographic definition and etching or depositing material, as well as by bottom-up growth techniques. In the latter self-assembly features take place, avoiding the need to define geometries via a lithographic mask [80, 156]. Bottom-up approaches like the catalyst particle assisted vapor liquid solid growth mechanism, or the growth in porous filaments in alumina templates, may lead to smooth surfaces and ultra-small diameters, but usually show limitations in deterministic position control. Finally, nanowire conducting channels can also be formed

electrostatically in thin films by multi-gated electrostatic confinement [160].

For Si and Ge nanowires, SBMOSFETs can be built either by covering the nanowires with metallic top electrodes, or by intruding a metal silicide within the nanowire, thus creating a longitudinal nanowire heterostructure [161, 162]. Although the first method typically provides a larger metalsemiconductor junction area (surface contact), the transistor performance is generally degraded as the junction region is shielded from the gate field. In contrast, intruded metal nanowire heterostructures introduce the Schottky junction within the nanowire [156], spanning a nanometer-scale junction area across the nanowire cross-section. This mostly ensures comparable junction areas in the same nanowire. In contrast to thin films and bulk, the nanowire system allows for the creation of the ultimate flat junction with atomic-level precision [163, 164]. Furthermore, the needle-like metallic nanowire segment and exposition of the Schottky junction provides an efficient coupling to external electric fields from the source-drain and gate biases [162].

In addition to compound metallic materials such as metallic silicides and germanides, elemental metal electrodes can be intruded into group-IV semiconductors, creating an atomically sharp and flat junction by an exchange reaction. Therein, the in-diffused metal species replaces the host semiconductor material entirely due to the low solid-state solubility gap, and is driven by a high asymmetry in diffusion coefficients. This was first reported by Lugstein *et al* for the Al–Ge nanowire system [165], and has recently been found to be likewise applicable to the Al–Si nanowire system [166], as well as for Al/Si $_x$ Ge $_{(1-x)}$  nanosheets involving the formation of a small Si interlayer [167].

The behavior of nanowire-based SBMOSFETs follows the description of the two cases described in section 1.3, (a) near-ohmic contacts and dopant segregated contacts and (b) SB contacts. Dopant-segregated contacts have been achieved in Si nanowires via the thermally driven intrusion of  $Ni_xSi_{1-x}$  into Si nanowires [168–170]. Due to this dopant segregation method, several emerging transistor concepts have been implemented, such as accumulation-type FETs similar to junctionless FETs [170], as well as devices with implanted source/drain regions and dopant-segregated sharp junctions, realizing a band-to-band tunnel FET with steep SS with a silicon nanowire material [171, 172]. The mid-gap SB devices are revisited in the next section because their smaller on currents precludes their use in high performance devices.

## 3. Opportunities of SB devices for ubiquitous electronics

In a TFT the channel material is deposited onto a substrate chosen to have an advantageous characteristic, such as transparency, flexibility and/or biocompatibility, which is not possible with a single-crystal bulk wafer. In the past twenty years, an explosion of research has considered the realization of TFTs on flexible and biocompatible substrates using not only poly-Si [173] but also carbon nanotubes, 2D, organic

and oxide materials, opening up new avenues of applications. They are of ever-increasing importance, and we have termed them here as 'ubiquitous electronics'. In addition to displays [174], exploitation of TFTs include flexible integrated circuits for the internet of things and wearable applications [175–178], environmental and biosensors [179, 180], organic memories [181], radio frequency applications [182] and recently for neuromorphic computing [183].

The difficulty in covering TFTs in an article like this one is that each of these different materials has its own challenges. A recent overview and comparison of these technologies can be found in Hosseini and Nawrocki [177]. A recent article explores how to benchmark TFT transistors regardless of the material [74]. One of the main challenges for integrating emerging technologies such as 2D material and carbon nanotubes into flexible electronics is to find processes that have low variability and low cost; characteristics that have been already carefully studied in 'traditional' TFT devices that are widely used industrially, most notably microcrystalline or amorphous silicon and more recently amorphous InGaZnO (IGZO) TFTs.

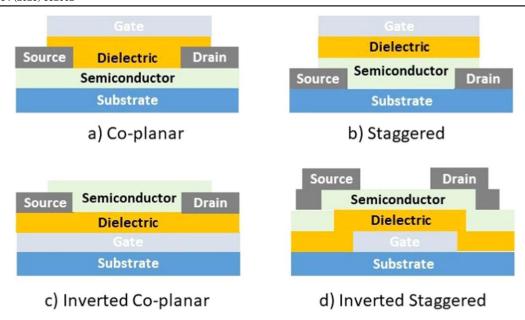

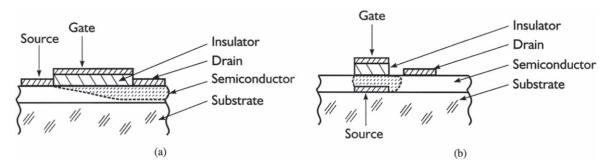

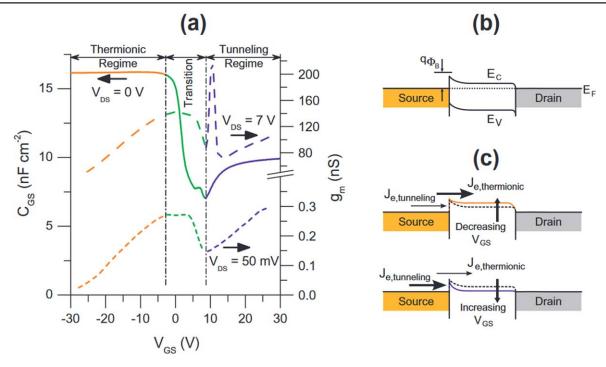

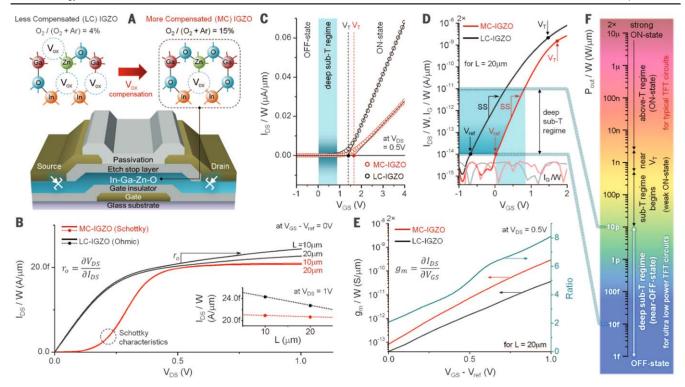

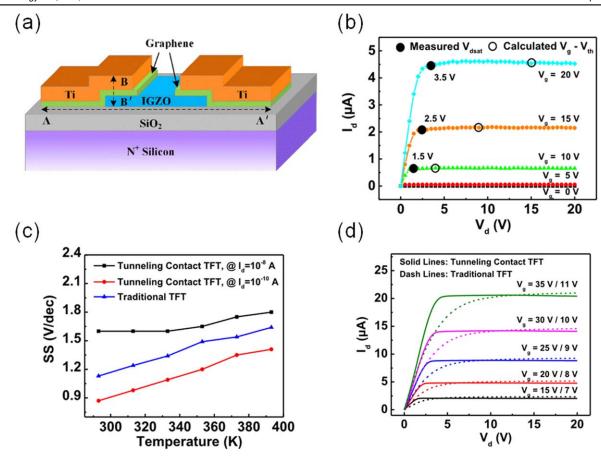

Our focus here is on how the SB can be used advantageously by controlling the flow of carriers into the channel. Two technologies in particular are relevant: SB TFTs or SGTs and RFETs. In order to put this in context and benchmark their performance, however, we also review the state of the art in this field more broadly, starting with an overview of poly and amorphous Si TFTs, whose performance is used to benchmark TFTs realized in emerging materials. We then describe typical TFT geometries. Next an overview of SGT devices and how they differ from conventional device operation is given. Finally, the remaining sub-sections explore the material system in which such devices can be realized and their advantages.

The first TFT transistors were realized in 1962 using a CdS channel and Au electrodes [184], and were in fact SB devices. In its early evolution, TFT technology paralleled the development of liquid crystal displays (LCDs), where the pixels are controlled by transistors that are fabricated on a glass substrate [185]. Initial TFT research and commercial devices were based on hydrogenated amorphous a-Si:H, where the dangling hydrogen bonds permitted controlled doping. It 1986 it was realized that by crystallizing the amorphous silicon using a low-temperature process via a high power excimer laser irradiation [186], significant improvements in the mobility of TFTs could be achieved. State of the poly-Si TFTs can have mobilities  $\mu$  up 300 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, compared to a-Si transistors with typical mobilities in the range of 0.1–1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for electrons and  $10^{-2} \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  for holes [177]. Nevertheless, commercially available low-cost polysilicon TFTs typically have mobilities of  $\approx 10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  [175]. The performance of polysilicon TFTs are used to benchmark emerging devices. Although a-Si:H and poly-Si TFTs have doped source and drain regions and are not SBFETs, as we will see below they can be designed to function as SGT, where the source injection barrier controls the flow of current into the channel. They are thus very relevant for comparing the performance of SGTs with SB contacts.