# Impact of pole-to-pole DC voltage on energy requirement of FB YY-MMC

Downloaded from: https://research.chalmers.se, 2025-06-08 21:28 UTC

Citation for the original published paper (version of record):

Mohtat, S., Bongiorno, M., Beza, M. et al (2023). Impact of pole-to-pole DC voltage on energy requirement of FB YY-MMC. 2023 25th European Conference on Power Electronics and Applications, EPE 2023 ECCE Europe. http://dx.doi.org/10.23919/EPE23ECCEEurope58414.2023.10264684

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

# Impact of pole-to-pole DC voltage on energy requirement of FB YY-MMC

Sohrab Mohtat<sup>1</sup>, Massimo Bongiorno<sup>1</sup>, Mebtu Beza<sup>1</sup>, Jan R. Svensson<sup>2</sup> (1) Chalmers University of Technology, Dept. of Electrical Engineering, Göteborg, Sweden (2) Hitachi Energy, Hitachi Energy Research, Västerås, Sweden E-Mail: sohrab.mohtat@chalmers.se

*Index Terms*—Modular Multilevel Converters (MMC), grid-connected converter, high voltage power converters, energy requirement and losses estimation, submodule capacitor parameter design.

Abstract—The aim of this paper is to investigate the impact of pole-to-pole DC voltage on the energy requirements of a modular multilevel converter with full-bridge submodules (FB-MMC). With focus on energy-storage equipped FB-MMCs, the relation between the pole-topole voltage and the peak-to-peak energy variations in the MMC's arms is derived. Unlike MMC with halfbridge (HB) submodules (SM), in a FB-MMC the poleto-pole DC voltage can be selected independently of the AC voltage; this allows for reduced energy requirements as well as lower number of FB SMs and capacitors for the same converter ratings. Furthermore, the impact of the converter's circulating current on the MMC's energy requirements is investigated. A guideline for the converter design is provided. Theoretical findings are validated via time-domain simulations.

## I. INTRODUCTION

In recent years, Modular Multilevel Converters (MMCs) have become the utility standard for high-power and high-voltage grid applications. The wye- and delta-connected chain-link converters are used for reactive power compensation, while the YY-MMC topology that has a common DC-link is used in HVDC-transmission. The MMC provides a high efficiency, a relatively small footprint, an excellent dynamic performance and robust-ness when connected to weak grids [1], [2]. Moreover, YY-MMCs with Energy Storage (ES) connected to the DC-link have found grid applications, especially to favor integration of renewable energy sources. [3].

In a YY-MMC structure, each phase-leg consists of an upper and lower converter arm. Each arm has several series connected submodules (SM), which can be considered by either a half-bridge (HB) or full-bridge (FB) converter. Based on the required phase voltage, the SMs are inserted or bypassed dynamically to form a sinusoidal voltage at the MMC's terminal.

Studies have shown that YY-MMC topology has a number of challenges [4]. One of the challenges is to reduce the requirement for the SMs' capacitors size in the YY-MMC, as they account for nearly 50% of its total cost [5]. Most studies available in the literature dealing with capacitance energy reduction are focusing on injecting a circulating current or a third-order harmonic voltage in the MMC arms. For example, [6] has proposed a method for injecting a second order harmonic circulating current so the peak SM voltage coincides with the maximum requested arm voltage, resulting in a lower capacitance requirement. The impact of the thirdorder harmonic arm voltage injection on the capacitance requirement of YY-MMC has been analyzed in [7] and [8]. In [9], a hardware-based strategy to achieve a capacitance energy reduction of the YY-MMC has been proposed. However, a way to find the optimal pole-topole dc voltage for an ES-connected MMC which results in the lowest possible capacitors size in the SMs has not been presented yet.

Unlike the DC transmission application, the pole-topole DC voltage of the MMC is a design parameter in ES systems and can be selected in the design stage. For HB YY-MMCs, the AC grid voltage determines the minimum needed pole-to-pole DC voltage, which is not the case for a FB configuration, which do not have the restriction on a certain minimum pole-to-pole DC voltage. A controllable pole-to-pole DC voltage has the advantage of handling faults on the DC side. Moreover, the freedom to choose the pole-to-pole DC voltage enables the search for a minimum SM capacitor energy.

This paper investigates the optimal pole-to-pole DC voltage that reduces the capacitance energy requirement and will result in the minimum number of SMs for the same YY-MMC rating. Furthermore, the impact of the circulating current on the YY-MMC capacitance

requirements is explored. A guideline for the FB-based YY-MMC design based on an optimal pole-to-pole DC voltage selection is provided and theoretical findings are validated through time-domain simulations.

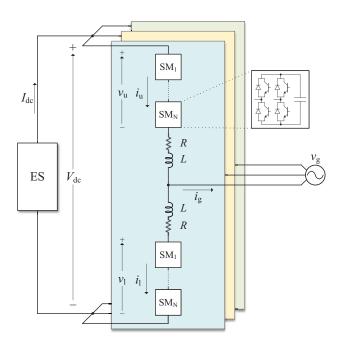

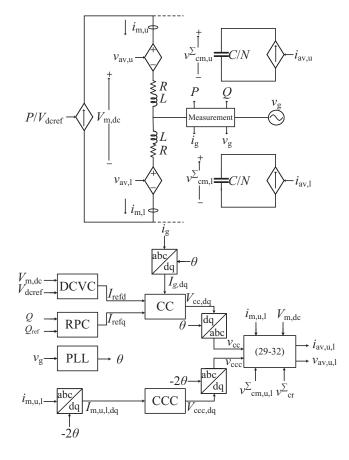

#### II. ENERGY VARIATION IN FB YY-MMC

The FB YY-MMC scheme is shown in Fig. 1. Each arm consists of N SMs in series together with a filter reactor having the inductance and resistance L and R, respectively. The AC side of the YY-MMC is connected to a three-phase grid with voltage of  $v_g$  and the DC side is connected to ES with pole-to-pole DC voltage of  $V_{dc}$  and current of  $I_{dc}$ . The terms  $v_u$  and  $v_l$  are the upper and lower arm voltages of a generic phase, while  $i_u$  and  $i_l$  are the upper and lower arm currents, and  $i_g$  is the phase current.

Fig. 1. Scheme of grid-connected FB YY-MMC.

Assuming inverter reference as in Fig. 1, a generic YY-MMC can be modeled as a voltage source, where  $v_s$  is the YY-MMC output voltage behind the filter and is written

$$v_{\rm s} = \frac{L}{2} \frac{di_{\rm g}}{dt} + \frac{R}{2} i_{\rm g} + v_{\rm g} \tag{1}$$

since the equivalent output filter of YY-MMC is half of the arm filter [2], and  $v_s$  is found to be

$$v_{\rm s} = \frac{v_{\rm l} - v_{\rm u}}{2} \tag{2}$$

From Fig. 1 and neglecting the DC voltage drop of the filter, the relation between  $V_{dc}$  and arm voltages can be found as

$$V_{\rm dc} = v_{\rm l} + v_{\rm u} \tag{3}$$

Combining (2) and (3), the arm voltages are derived as

$$v_{\rm u} = \frac{V_{\rm dc}}{2} - v_{\rm s}$$

$$v_{\rm l} = \frac{V_{\rm dc}}{2} + v_{\rm s}$$

(4)

The next step is to find the upper and lower arm currents. The arm currents consist of three main terms [10]

$$i_{\rm u} = I_{\rm dc,arm} + i_{\rm f,arm} + i_{\rm cir}$$

$$i_{\rm l} = I_{\rm dc,arm} - i_{\rm f,arm} + i_{\rm cir}$$

(5)

where  $I_{dc,arm}$  is the DC current flowing through the upper and lower arm and is 1/3 of  $I_{dc}$ ,  $i_{f,arm}$  is the current at fundamental frequency, which is responsible for exchanging active and reactive power between the YY-MMC and the grid and is assumed to be half of the phase current  $i_g$ . The term  $i_{cir}$  is the circulating current resulting from the capacitors voltage ripple mismatch between the upper arm and lower arm. Here, it is assumed that the circulating current is well suppressed by the circulating current controller (CCC), thus  $i_{cir} = 0$ . This implies that the CCC adds an extra term to the reference voltage of upper and lower arm in (4). However, since this term is very small, it is neglected in the analysis. As a result, the upper and lower arm currents can be rewritten as

$$i_{\rm u} = \frac{I_{\rm dc}}{3} + \frac{i_{\rm g}}{2} i_{\rm l} = \frac{I_{\rm dc}}{3} - \frac{i_{\rm g}}{2}$$

(6)

Considering a steady-state operation, it is assumed that

$$v_{\rm g} = \hat{V}_{\rm g} \cos(\omega t) \tag{7}$$

$$i_{\rm g} = \hat{I}_{\rm g} \cos(\omega t + \varphi) \tag{8}$$

Therefore,  $v_{\rm s}$  can be found in phasor domain

$$\bar{V}_{\rm s} = \hat{V}_{\rm s} \angle \varphi_{\rm s} = \left(j\omega \frac{L}{2} + \frac{R}{2}\right)\bar{I}_{\rm g} + \bar{V}_{\rm g} \tag{9}$$

where  $\bar{V}_{g} = \hat{V}_{g} \angle 0$  and  $\bar{I}_{g} = \hat{I}_{g} \angle \varphi$  are the grid voltage and current phasors, respectively.

After the arms' voltage and current have been determined, the arm power and energy expressions can be found. The upper and lower arm instantaneous power are

$$p_{\mathbf{u},\mathbf{l}} = v_{\mathbf{u},\mathbf{l}}i_{\mathbf{u},\mathbf{l}} \tag{10}$$

replacing (4), (6), and (9) in (10) will result in

$$p_{\rm u} = \frac{V_{\rm dc}I_{\rm dc}}{6} + \frac{V_{\rm dc}\widehat{I}_{\rm g}}{4}\cos\left(\omega t + \varphi\right) - \frac{\widehat{V}_{\rm s}I_{\rm dc}}{3}\cos\left(\omega t + \varphi_{\rm s}\right) \\ - \frac{\widehat{V}_{\rm s}\widehat{I}_{\rm g}}{4}\cos\left(2\omega t + \varphi + \varphi_{\rm s}\right) - \frac{\widehat{V}_{\rm s}\widehat{I}_{\rm g}}{4}\cos\left(\varphi - \varphi_{\rm s}\right)$$

$$p_{l} = \frac{V_{dc}I_{dc}}{6} - \frac{V_{dc}\widehat{I}_{g}}{4}\cos(\omega t + \varphi) + \frac{\widehat{V}_{s}I_{dc}}{3}\cos(\omega t + \varphi_{s}) - \frac{\widehat{V}_{s}\widehat{I}_{g}}{4}\cos(2\omega t + \varphi + \varphi_{s}) - \frac{\widehat{V}_{s}\widehat{I}_{g}}{4}\cos(\varphi - \varphi_{s})$$

(11)

The active power balance between the DC and the AC sides of the YY-MMC is

$$V_{dc}I_{dc} = \frac{3}{2}\hat{V}_{s}\hat{I}_{g}\cos\left(\varphi - \varphi_{s}\right)$$

(12)

Therefore, the DC terms in (11) are cancelled out. The instantaneous power in upper and lower arms become

$$p_{u} = \frac{V_{dc}\widehat{I}_{g}}{4}\cos(\omega t + \varphi) - \frac{\widehat{V}_{s}I_{dc}}{3}\cos(\omega t + \varphi_{s}) - \frac{\widehat{V}_{s}\widehat{I}_{g}}{4}\cos(2\omega t + \varphi + \varphi_{s})$$

$$p_{l} = -\frac{V_{dc}\widehat{I}_{g}}{4}\cos(\omega t + \varphi) + \frac{\widehat{V}_{s}I_{dc}}{3}\cos(\omega t + \varphi_{s}) - \frac{\widehat{V}_{s}\widehat{I}_{g}}{4}\cos(2\omega t + \varphi + \varphi_{s})$$

$$(13)$$

The instantaneous variation of energy in upper and lower arm is determined by integrating the instantaneous power in each arm

$$w_{\rm u} = \int p_{\rm u} dt = \frac{V_{\rm dc} \widehat{I}_{\rm g}}{4\omega} \sin(\omega t + \varphi)$$

$$-\frac{\widehat{V}_{\rm s} I_{\rm dc}}{3\omega} \sin(\omega t + \varphi_{\rm s}) - \frac{\widehat{V}_{\rm s} \widehat{I}_{\rm g}}{8\omega} \sin(2\omega t + \varphi + \varphi_{\rm s})$$

$$w_{\rm l} = \int p_{\rm l} dt = -\frac{V_{\rm dc} \widehat{I}_{\rm g}}{4\omega} \sin(\omega t + \varphi)$$

$$+\frac{\widehat{V}_{\rm s} I_{\rm dc}}{3\omega} \sin(\omega t + \varphi_{\rm s}) - \frac{\widehat{V}_{\rm s} \widehat{I}_{\rm g}}{8\omega} \sin(2\omega t + \varphi + \varphi_{\rm s})$$

(14)

The energy variation of the capacitors in each arm will lead to a voltage modulation across the capacitor in each SM. The peak-to-peak energy value of the (14) is found using

$$W = \max\left(w_{u,l}\right) - \min\left(w_{u,l}\right) \tag{15}$$

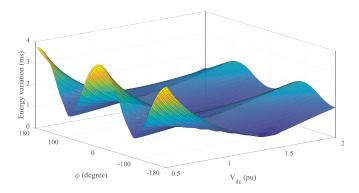

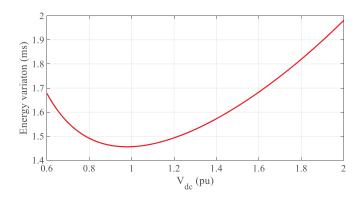

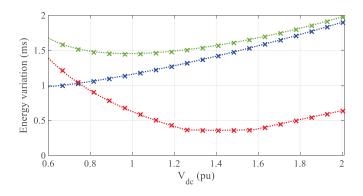

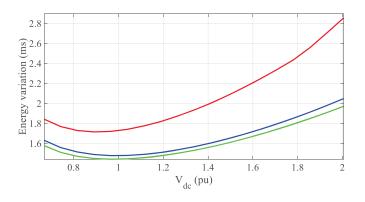

where W is the energy variation, which is a function of the  $V_{dc}$  and the active and reactive power exchange between the YY-MMC and the grid. Fig. 2 shows the energy variation expressed in seconds (energy divided by rated power) as a function of  $V_{\rm dc}$  in pu and the output power angle  $\varphi$ , while keeping  $\hat{V}_{\rm g}$  and the apparent power to 1 pu. Fig. 3 displays W versus  $V_{\rm dc}$  for three different power angles: 0°, 60°, and 90°.

As shown in Fig. 2 and Fig. 3, there is a  $V_{dc}$  for every power angle that corresponds to a minimum energy variation. This pole-to-pole voltage and its corresponding energy variation are referred to as  $V_{dc,min}$  and  $W_{min}$ . As an example, for the power angle of 90°, when only reactive power is injected to the grid,  $V_{dc,min} = 0$  and for the power angle of 0°,  $V_{dc,min} = 1.41$  pu. In case the active and reactive power have the same requirement, the highest energy variation between all the  $V_{dc,min}$ s happens at the power angle of  $60^{\circ}$  and  $V_{dc,min} = 1.03$  pu. From Fig. 2, (14), and (15) it can be shown that while keeping the reactive power constant, the energy variation for the same amount of active power injection or absorption is equal. Furthermore, it is assumed that the converter only injects reactive power to the grid. Therefore, in Section III it is assumed that  $0 \le \varphi \le \frac{\pi}{2}$ .

Fig. 2. Energy variation of YY-MMC for different pole-to-pole dc voltages and power angles.

Fig. 3. Energy variation of YY-MMC for different pole-to-pole DC voltages when  $\varphi = 90^{\circ}$  (blue),  $\varphi = 60^{\circ}$  (red), and  $\varphi = 0^{\circ}$  (yellow).

An interesting range of pole-to-pole DC voltage is for values larger than 2 pu. As discussed in Section I, MMC SMs can be either HB or FB. HB SMs can only generate 0 and positive voltage; hence, the arm voltage should always be positive in a HB YY-MMC. Taking into account (4)

$$V_{\rm dc} \ge 2\widehat{V}_{\rm s} \tag{16}$$

and when neglecting the voltage drop over the filter reactor, the pole-to-pole DC voltage becomes

$$V_{\rm dc} \ge 2 \, \mathrm{pu}$$

(17)

Therefore, the minimum pole-to-pole dc voltage is 2 pu for HB-MMC and is the usual choice for this kind of converters. Since FB SMs can generate negative voltages as well, there is no such limitation for  $V_{dc}$  in FB-MMC. As it can be seen from Fig. 2 and Fig. 3, for every power angle, there is always a  $V_{dc,min}$ , lower than 2pu. Therefore, in case  $V_{dc,min}$  is chosen as the ES DC voltage, the energy variation for FB-MMC is always lower than HB-MMC.

# III. FB YY-MMC DESIGN

The design and sizing of the FB YY-MMC, based on the optimal selection of the pole-to-pole DC voltage to minimize the energy requirement of the YY-MMC is presented in this section. First, the design of components without dependence of  $V_{dc}$  are presented. Next, a flowchart that demonstrates how the optimal pole-to-pole DC voltage ( $V_{dc,opt}$ ) should be selected is proposed. Finally, as  $V_{dc,opt}$  is determined, the design of components that are dependent on  $V_{dc}$  are analyzed.

The first component to be designed is the arm filter, which limits the line harmonics and enable current control. Moreover, it protects the SMs from transient currents and limits high-frequency components in the circulating current. A typical size of the arm filter is 0.10 to 0.20 pu [2], [11] and here it is assumed that the reactance is 10 times larger than the resistance. Here, the arm filter is chosen to 0.15 pu. The YY-MMC should provide the voltage reference generated by the current controller (CC). The maximum YY-MMC output voltage  $\hat{V}_s$  is determined as [12]

$$\widehat{V}_{\rm s} = 1.05 \widehat{V}_{\rm g} (1 + \Delta V_{\rm g} + I_{\rm pu} \frac{Z_{\rm f}}{2}) \tag{18}$$

where  $\Delta V_{\rm g}$  is the maximum grid voltage variation,  $I_{\rm pu}$  is the output current and equals 1 pu, and  $Z_{\rm f}$  is the arm filter impedance. Moreover, a 5% margin is added to guarantee a suitable dynamic response of the CC. Considering an arm filter of 0.15 pu and 10% maximum grid voltage variation,  $\hat{V}_{\rm s}$  is found to be  $1.23\hat{V}_{\rm g}$ . The next design consideration is the pole-to-pole DC voltage limit. From (12), the DC current equals

$$I_{\rm dc} = \frac{3\hat{V}_{\rm s}\hat{I}_{\rm g}\cos\left(\varphi - \varphi_{\rm s}\right)}{2V_{\rm dc}} \tag{19}$$

where P is the active power to the grid. By decreasing  $V_{dc}$ , the arm current increases and semiconductors with larger rated current are required. Hence,  $V_{dc}$  cannot decrease too much and a limit for  $V_{dc}$ , based on the rated current of the semiconductors  $(I_n)$ , should be defined. The maximum current of the arm should be lower than the rated current of the semiconductors

$$\max\left(i_{\mathrm{u}}, i_{\mathrm{l}}\right) \le I_{\mathrm{n}} \tag{20}$$

From (6) and (8), the maximum upper and lower arm current are found to be

$$\max\left(i_{\rm au}, i_{\rm al}\right) = \frac{I_{\rm dc}}{3} + \frac{I_{\rm g}}{2} \tag{21}$$

combining (19), (20), (21) and assuming the apparent power to the grid equals  $S = \frac{3}{2} \hat{V}_g \hat{I}_g$  when neglecting the voltage drop over the filter inductor, the limit for the pole-to-pole DC voltage can be written as

$$\frac{V_{\rm dc}}{\hat{V}_{\rm g}} \ge \frac{P}{3\hat{V}_{\rm g}I_{\rm n} - S} \tag{22}$$

Thus, the pu limit for the pole-to-pole DC voltage can be defined as

$$V_{\text{dclim,pu}} = \frac{P}{3\widehat{V}_{g}I_{n} - S}$$

(23)

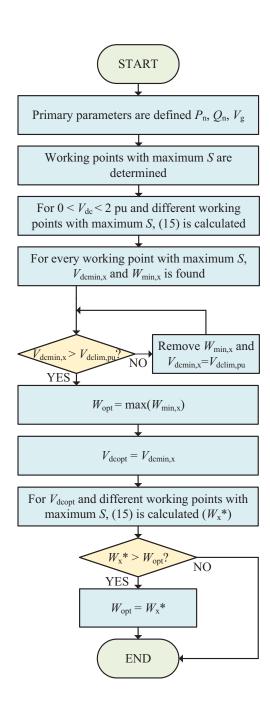

The flowchart in Fig. 4 shows how  $V_{\text{dcopt,pu}}$  and its corresponding energy requirement, which is called optimal energy requirement ( $W_{\text{opt,pu}}$ ), should be chosen so that the least possible capacitor size is selected for the SMs and furthermore, the peak-to-peak voltage variations of SM's capacitors are held below a certain threshold for all the working points of the converter. The relation between the energy requirement and the capacitors and their voltage variations are discussed in the following paragraphs.

In the next step, the number of SMs are selected to guarantee that the YY-MMC is able to generate the needed voltage and does not enter in overmodulation during normal operations. Considering (4), (9) and assuming optimal values from the flow-chart, the maximum needed arm voltage becomes

$$\widehat{V}_{\text{arm}} = \max\left(v_{\text{au}}, v_{\text{al}}\right) = \frac{V_{\text{dcopt}}}{2} + \widehat{V}_{\text{s}}$$

(24)

Fig. 4. Flowchart for  $V_{dcopt}$  and  $W_{opt}$  selection.

In order to find the number of SMs in each arm, the maximum arm voltage should be divided by the rated SM voltage  $V_n$ , which is chosen to fit the 100 FIT (100 failures in 10<sup>9</sup> operating hours) value of the selected semiconductor device [12]. This voltage is inserted to the arm by each SM. Thus, the number of SMs in each arm become

$$N = \frac{\widehat{V}_{\text{arm}}}{V_{\text{n}}} \tag{25}$$

Finally, the energy requirement of the SM capacitor is determined. The energy requirement is defined as the peak-to-peak variation of the arm energy which originates from the voltage ripple of the capacitors. Considering that there are N SMs in each arm, the total arm energy variation will be the sum of the energy variation of each SM capacitor. Selecting the optimal arm energy requirement found from the flow-chart in Fig. 4, the total arm energy variation can be determined as

$$W_{\text{opt}} = \frac{N}{2} C \left( V_{\text{cmax}}^2 - V_{\text{cmin}}^2 \right)$$

=  $\frac{N}{2} C \left( V_{\text{cmax}} + V_{\text{cmin}} \right) \left( V_{\text{cmax}} - V_{\text{cmin}} \right)$  (26)

where  $V_{\rm cmax}$  and  $V_{\rm cmin}$  are the maximum and minimum capacitor voltage, respectively. Assuming  $V_{\rm cmax} + V_{\rm cmin} \approx 2V_{\rm n}$  and defining  $\Delta V$  as the voltage ripple of the capacitor

$$\Delta V = \frac{V_{\rm cmax} - V_{\rm cmin}}{V_{\rm n}} \tag{27}$$

and combining (26) and (27) and solving for C results in

$$C = \frac{W_{\text{opt}}}{N\Delta V V_{\text{n}}^2} \tag{28}$$

## IV. AVERAGED MODEL AND CONTROL

In this section, the control blocks that are used for the time-domain simulations are introduced. Since studying voltage, currents, and switching events of of each SM is not of interest in this work, an averaged model of the YY-MMC has been investigated. The model used in this study is arm-level averaged model [2], in which each arm of the FB YY-MMC is modeled by a controllable voltage source. The capacitors of the SMs are modeled as a series connection of a controllable current source and a capacitor value of C/N, where C is the SM capacitor value. The voltage and current sources are equal to

$$v_{\rm av,u,l} = n_{\rm u,l} v_{\rm cm,u,l}^{\Sigma} \tag{29}$$

$$i_{\rm av,u,l} = n_{\rm u,l} i_{\rm m,u,l} \tag{30}$$

where, as shown in Fig. 5,  $v_{av,u}$ ,  $v_{av,l}$ ,  $i_{av,u}$ , and  $i_{av,l}$  are the voltages and currents of the upper and lower arm sources,  $v_{cm,u}^{\Sigma}$  and  $v_{cm,l}^{\Sigma}$  are the measured sum capacitor voltages of the upper and lower arm,  $i_{m,u}$  and  $i_{m,l}$  are the measured upper and lower arm currents, and  $n_u$  and  $n_l$  are upper and lower arm insertion indices, which are defined as

$$n_{\rm u} = \frac{\frac{V_{\rm m,dc}}{2} - v_{\rm cc} - v_{\rm ccc}}{v_{\rm cr}^{\Sigma}} \tag{31}$$

$$n_{\rm l} = \frac{\frac{V_{\rm m,dc}}{2} + v_{\rm cc} - v_{\rm ccc}}{v_{\rm cr}^{\Sigma}}$$

(32)

In (31) and (32)  $V_{m,dc}$  is the measured pole-to-pole DC voltage,  $v_{cc}$  is generated voltage reference by the CC,  $v_{ccc}$  is the voltage reference for circulating current suppression from the CCC, and  $v_{cr}^{\Sigma}$  is the reference sum capacitor voltage which is equal to  $NV_n$ . For FB YY-MMC, the arm insertion indices is a number between -1 and 1 and shows in average how many SMs are inserted in each arm.

Fig. 5. FB YY-MMC arm-level averaged with controller.

The control system of the FB YY-MMC consists of a reactive power controller (RPC), a DC-link voltage controller (DCVC), a vector CC and a CCC as displayed in Fig. 5. The RPC is a PI controller generating the q-component of the reference current. The DCVC regulates the pole-to-pole DC voltage and provides the d-component of the reference current. A grid-following CC is used to regulate the YY-MMC output voltage and finally, a vector CCC is used to suppress the second-order harmonic in the circulating-current. The ES is modelled as a current source with the current equal to  $P/V_{dc}$ . However, in actual applications, the voltage of the ES decreases as the state of charge of the storage becomes low. This decrease in the voltage will be reflected in the sum capacitors voltage which is neglected in this analysis.

# V. CASE STUDY AND SIMULATION RESULTS

In this section, based on the defined procedure, a FB YY-MMC with an ES is designed. The ES and grid specifications which are the primary design parameters of the FB YY-MMC are shown in TABLE I.

TABLE I ES AND GRID SPECIFICATIONS

| Parameter                 | Symbol      | Unit   | Value |

|---------------------------|-------------|--------|-------|

| ES rated active power     | $P_{n}$     | [MW]   | 50    |

| Rated reactive power      | $Q_{n}$     | [MVar] | 100   |

| Rated apparent power      | $S_{n}$     | [MVA]  | 112   |

| Line to line grid voltage | $V_{g}$     | [kV]   | 33    |

| Grid frequency            | $\tilde{f}$ | [Hz]   | 50    |

As explained in Section III, the two design parameters that are not dependent on  $V_{dc}$  are the arm filter reactor and  $\hat{V}_{s}$  that are selected as 0.15 pu and  $1.23\hat{V}_{s}$ . By using the primary design parameters, the peak-topeak energy value (15) can be found and is displayed in Fig. 6. Since there is only one operating point with a maximum apparent power, as shown in TABLE I, the most suitable candidate candidate for  $V_{dcopt,pu}$  is  $V_{dcmin,pu}$ which is found to be 0.98. For this value the max arm current from (21) is found to be 2016 A. Therefore, the selected semiconductor should have a current rating of at least 2016 A. Here, the semiconductor device with part number of 5SNA2000K450300 which has a rated current of 2500 A [12] is selected for the FB YY-MMC. Replacing P, S, and  $\hat{V}_{g}$  from TABLE I and the semiconductor rated current in (23), the limit for pole-topole DC voltage is found. Considering the rated voltage of the chosen semiconductor device and the maximum voltage ripple of 10% for each SM capacitors, the other parameters of the FB YY-MMC are displayed in TABLE II.

The energy variation for the YY-MMC is simulated using the model presented in Section IV. In Fig. 7, the results are compared with the theoretical calculations for the apparent power exchange of 1 pu (P=50 MW and Q=100 MVar), as well as two other cases with different power ratings. As displayed, the simulation results are in agreement with the theoretical values. The maximum error is about 0.3% which is due to neglecting the voltage added by CCC in (4) and the assumption made in (26). Furthermore, as discussed before, while by regulating  $V_{dc}$ , W can be chosen as low as 1.46 ms for a FB

Fig. 6. Energy variation for the MMC with primary parameters in TABLE I.

TABLE II FB YY-MMC DESIGN PARAMETERS

| Parameter                       | Symbol      | Unit | Value |

|---------------------------------|-------------|------|-------|

| Arm filter                      | $Z_{\rm f}$ | [pu] | 0.15  |

| MMC maximum output voltage      | $V_{\rm s}$ | [kV] | 33.14 |

| Maximum arm current             | $I_{max}$   | [kA] | 2.02  |

| Semiconductor rated current     | $I_{n}$     | [kA] | 2.5   |

| Pole-to-pole dc voltage limit   | $V_{dclim}$ | [pu] | 0.56  |

| Pole-to-pole optimal dc voltage | $V_{dcopt}$ | [pu] | 0.98  |

| Optimal energy requirement      | Wopt        | [ms] | 1.46  |

| Number of SMs per arm           | N           | -    | 23    |

| SM's maximum voltage ripple     | $\Delta V$  | [%]  | 10    |

| SM's rated voltage              | $V_{\rm n}$ | [kV] | 2.5   |

| SM's capacitance                | C           | [mF] | 11.34 |

YY-MMC, according to (17),  $V_{dc}$  has to be greater than 2 pu for a HB YY-MMC which results in a minimum energy requirement of 1.98 ms. As a result, the energy requirement for a FB YY-MMC is 26% lower than HB YY-MMC.

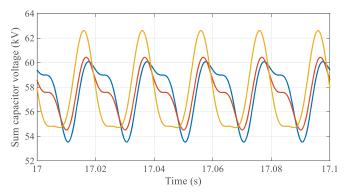

Fig. 8 compares the  $v_{cm,u}^{\Sigma}$  for the estimated optimal DC voltage ( $V_{dcopt} = 0.98$  pu), a lower value ( $V_{dc} = 0.67$  pu) and a higher value ( $V_{dc} = 2$  pu), which is the lowest possible value for HB-MMC. As mentioned in TABLE II, the maximum sum capacitor voltage ripple is designed to be 10% for  $V_{dcopt}$ , which is confirmed by the simulated value of 10.2%. Moreover, the voltage ripple for  $V_{dc}=0.67$  pu and  $V_{dc}=2$  pu are found to be 11.4% and 13.7%, respectively. Therefore, it is verified that  $V_{dcopt}$  leads to the least voltage ripple.

Fig. 8. Sum capacitor voltage ripples for  $V_{dc} = 0.67$  (blue),  $V_{dc} = 0.98$  (red), and  $V_{dc} = 2$  (yellow).

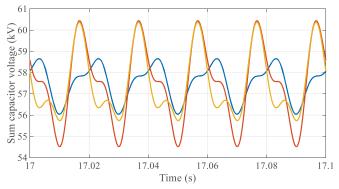

Furthermore,  $v_{cm,u}^{\Sigma}$  for the estimated optimal DC voltage ( $V_{dcopt} = 0.98$  pu) and the three different mentioned power exchange for Fig. 8 can be seen in Fig. 9. As discussed in Section III, the optimal DC voltage is chosen in a way that the capacitors voltage ripple do not exceed a certain threshold ( $\Delta V = 10\%$  in this case study) for all the operating points. This is confirmed by the simulation which shows that the sum capacitors voltage ripple is 8% for P = 10 MW and Q = 100MVar and 4.5% for P = 50 MW and Q = 10 MVar.

Fig. 7. The energy variation calculation (dotted lines) and simulation (crosses) for P = 50 MW and Q = 100 MVar (green), P = 10 MW and Q = 100 MVar (blue), and P = 50 MW and Q = 10 MVar (red).

Fig. 9. Sum capacitor voltage ripple for  $V_{dc} = 0.98$  pu and P = 50 MW and Q = 10 MVar (blue), P = 50 MW and Q = 100 MVar (red), and P = 10 MW and Q = 100 MVar (yellow).

Finally, the effect of the CCC on the energy variation for the FB YY-MMC is investigated. Fig. 10 shows the energy variation for the FB YY-MMC for three case studies: no CCC; proportional CCC; dq-based CCC as the one described in Fig. 5. When the second-order harmonic of the circulating current is completely suppressed by the dq-based CCC, the energy variation is at minimum with respect to the other two cases. For  $V_{dc} = 0.98$  pu, the energy variation for the three cases is 1.73 ms, 1.49 ms, and 1.46 ms, respectively. Therefore, the proper suppression of the second-order circulating current leads to a reduction in the converter's energy requirement of 18%.

Fig. 10. The energy requirement in case no CCC (red), P controller (blue), and dq controller (green) is implemented.

# VI. CONCLUSION

In this paper, the impact of the pole-to-pole DC voltage on the capacitance requirement of the FB YY-MMC has been investigated. It has been found that there exists an optimal pole-to-pole DC voltage that minimizes the capacitance requirement of the converter. Based on this voltage, a design guideline for the FB YY-MMC has been presented. Furthermore, it has been demonstrated that with proper selection of pole-to-pole DC voltage reduction in capacitance requirement for the FB YY-MMC can be achieved.

### REFERENCES

- H. Akagi, "Classification, terminology, and application of the modular multilevel cascade converter (MMCC)," *The 2010 International Power Electronics Conference -ECCE ASIA*, Sapporo, Japan, 2010, pp. 508-515, doi: 10.1109/IPEC.2010.5543243.

- [2] K. Sharifabadi, et al. "Design, control, and application of modular multilevel converters for HVDC transmission systems," John Wiley & Sons, 2016.

- [3] M. Vasiladiotis and A. Rufer, "Analysis and Control of Modular Multilevel Converters With Integrated Battery Energy Storage," in *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 163-175, Jan. 2015, doi: 10.1109/TPEL.2014.2303297.

- [4] Y. Wang, A. Aksoz, T. Geury, S.B. Ozturk, O.C. Kivanc, Hegazy, O. "A Review of Modular Multilevel Converters for Stationary Applications," *Appl. Sci.* 2020, 10, 7719. https://doi.org/10.3390/app10217719.

- [5] G. Wang et al., "A Review of Power Electronics for Grid Connection of Utility-Scale Battery Energy Storage Systems," in *IEEE Transactions on Sustainable Energy*, vol. 7, no. 4, pp. 1778-1790, Oct. 2016, doi: 10.1109/TSTE.2016.2586941.

- [6] K. Ilves, A. Antonopoulos, L. Harnefors, et al.: "Capacitor voltage ripple shaping in modular multilevel converters allowing for operating region extension," *Annual Conf. of the IEEE Industrial Electronics Society*, Melbourne, Australia, November 2011, pp. 4403–4408.

- [7] Y. Xiao, L. Peng, "Submodule capacitance requirement reduction with capacitor voltage ripple suppression in MMC," *IET Gener. Transmiss. Distrib.*, vol. 14, no. 10, pp. 1942-1951, May 2020.

- [8] Li, R., Fletcher, J., Williams, B.: "Influence of third harmonic injection on modular multilevel converter-based high-voltage direct current transmission systems," *IET Gener. Transm. Distrib.*, 2016, 10, (11), pp. 2764–2770

- [9] J. Fang, S. Yang, H. Wang, N. Tashakor and S. M. Goetz, "Reduction of MMC Capacitances Through Parallelization of Symmetrical Half-Bridge Submodules," in *IEEE Transactions on Power Electronics*, vol. 36, no. 8, pp. 8907-8918, Aug. 2021, doi: 10.1109/TPEL.2021.3049389.

- [10] K. Ilves, S. Norrga, L. Harnefors and H. -P. Nee, "On Energy Storage Requirements in Modular Multilevel Converters," in *IEEE Transactions on Power Electronics*, vol. 29, no. 1, pp. 77-88, Jan. 2014, doi: 10.1109/TPEL.2013.2254129.

- [11] S. Du, et al. "Modular multilevel converters: analysis, control, and applications," John Wiley & Sons, 2018.

- [12] S.K. Chaudhary, A.F. Cupertino, R. Teodorescu, J.R. Svensson, "Benchmarking of Modular Multilevel Converter Topologies for ES-STATCOM Realization," *Ener*gies 2020, 13, 3384. https://doi.org/10.3390/en13133384