# A GaN MMIC Wideband Continuous-Mode Doherty Power Amplifier for 6G FR3 cmWave Applications

Citation for the original published paper (version of record):

Zhou, H., Åberg, V., Chang, H. et al (2024). A GaN MMIC Wideband Continuous-Mode Doherty Power Amplifier for 6G FR3 cmWave Applications. 2024 19th European Microwave Integrated Circuits Conference, EuMIC 2024

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

# A GaN MMIC Wideband Continuous-Mode Doherty Power Amplifier for 6G FR3 cmWave Applications

Han Zhou<sup>#1</sup>, Victor Åberg<sup>#2</sup>, Haojie Chang<sup>#3</sup>, Christian Fager<sup>#4</sup>

\*Chalmers University of Technology, Gothenburg, Sweden

han.zhou@{chalmers.se, ieee.org}, {<sup>2</sup>abergy, <sup>3</sup>haojie, <sup>4</sup>christian.fager}@chalmers.se.

Abstract — This paper presents a  $10-14~\mathrm{GHz}$  Doherty power amplifier (PA) implemented in GaN on SiC MMIC process aimed for future 6G FR3 centimeter-wave (cmWave) applications. We propose the theory and design of the continuous-mode (CM) operations to extend Doherty PA bandwidth. To demonstrate the viability of the concept, a prototype GaN MMIC CM Doherty PA was fabricated and fully characterized. Experimental results exhibit a peak power added efficiency (PAE) of 28%-38% and back-off PAE of 21%-31%, respectively, with an output power higher than  $34~\mathrm{dBm}$  across the operating frequencies.

Keywords — Continuous mode, Doherty, 6G, gallium nitride (GaN), load modulation, MMIC, power amplifier (PA), wideband.

#### I. INTRODUCTION

In the evolution toward the sixth generation (6G) wireless communications, the FR3 band (7 - 24 GHz) is anticipated to play an important role due to its superior balance between transmission capacity and coverage area [1]. Specifically, the international mobile telecommunications (IMT) has identified new spectrums within the FR3 band, including the 10.7 - $13.25~\mathrm{GHz}$  and the  $14-15.35~\mathrm{GHz}$ , etc., that are vital for future developments in the telecommunications industry [1], [2]. In this context, the design and development of power amplifiers (PA) for use in handsets, access points, and base stations present significant challenges. These PAs are expected to deliver peak output power within 30 - 35 dBm [3], [4], a requirement that surpasses those for the fifth-generation (5G) millimeter-wave PAs, attributed to the anticipated increase in cell size within the 6G arrays. Furthermore, the evolution toward more complex modulation schemes, required by higher data throughput in 6G mobile wireless communication systems, has resulted in signals with large peak-to-average-power ratios (PAPR).

Load-modulated PA architectures have been widely adopted to enhance system energy efficiency when transmitting high PAPR signals. Key developments include outphasing and Doherty PAs, with recent advancements introducing the load modulated balanced amplifier (LMBA) [5], distributed efficient PA (DEPA) [6], and circulator load modulated amplifier (CLMA) [7], [8]. Despite the emergence of these novel architectures, the Doherty PA remains the most widely employed technique in cellular base stations because of its simple topology and proven reliability, making it a preferred choice for monolithic microwave integrated circuits (MMIC) applications demanding high efficiency and simplicity. In recent years, expanding the bandwidth of

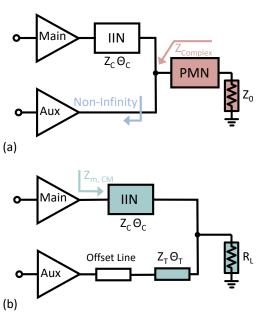

Fig. 1. (a) The conventional CM Doherty PA architecture utilizing the post-matching network or auxiliary non-infinite output impedance and (b) the proposed CM Doherty PA topology.

Doherty PAs has emerged as a key research area. Prior research has effectively incorporated the continuous-mode (CM) technique [9] into Doherty PA designs, achieving bandwidth extension through methods including post-matching in combining networks [10], [11] and employing non-infinite auxiliary output impedance [12] for CM Doherty PAs.

This paper elaborates on the theory and design of a  $10-14~\mathrm{GHz}$  CM Doherty PA, incorporating a novel output combiner network. Fabricated using a  $150~\mathrm{nm}$  GaN on SiC process, this PA is tailored for potential 6G FR3 frequency applications. The following sections demonstrate the theory, design, and characterization of the proposed CM Doherty PA, highlighting its bandwidth performance enhancements.

# II. THEORY

The CM PA operation, analogous to class-B operation, was introduced to expand the design space for the PA output matching network [9]. It allows a range of impedances to yield identical output power and efficiency levels for the PA. Consequently, CM operation facilitates a broader design space without sacrificing RF performance, enabling the development of wideband PAs beyond the constraints of the class-B

Fig. 2. (a) Theoretical block diagram of the proposed CM Doherty PA at back-off power. (b) Simulated back-off impedance of the standard and CM Doherty PA across 50% normalized fractional bandwidth at their main current source generator plane.

operation. The load impedance for the CM mode PA can be expressed as [9]

$$Z_{\rm f_0} = R_{\rm opt} \left( 1 - j\gamma \right) \tag{1}$$

$$Z_{2f_0} = j\gamma \frac{3\pi}{8} R_{\text{opt}} \tag{2}$$

where  $-1 \le \gamma \le 1$ , and  $R_{\rm opt}$  is the class-B optimal impedance. In conventional CM Doherty PAs, the combination of output power from the main and auxiliary amplifiers is facilitated through an impedance inverting network (IIN). Fig. 1 demonstrates that to attain CM impedance at back-off power levels, one can utilize the auxiliary amplifier's non-infinite output impedance, altering the combining load into a complex value for conversion to CM impedance, as proposed in [12]. An alternative strategy involves a post-matching network to directly achieve complex impedances at the combining node, introduced in [11]. However, the dependency on a standard quarter-wavelength ( $\lambda/4$ ) transformer for the load modulation network in conventional CM Doherty PAs inevitably limits the design space, as it necessitates the use of either non-infinite output impedance or a post-matching network to achieve complex impedances.

To further expand the design space of CM Doherty PAs, we introduce a novel output combiner topology, as shown in Fig. 1(b). Unlike the conventional CM Doherty PA, the proposed combiner network provides the CM complex impedance at the back-off power level, enhancing design flexibility and performance. As demonstrated in Fig. 2(a), at the back-off level, an offset line or matching network from the auxiliary path can transform the auxiliary output impedance to exhibit short circuit behavior at the desired point. Consequently, the load resistance at the combining node,  $R_{\rm L}$ ,

and the remaining transmission line, with impedance  $Z_{\rm T}$  and electrical length  $\theta_{\rm T}$  are effectively in parallel combining. The resulting impedance  $Z_{\rm mC}$  is defined as

$$Z_{\rm mC} = \frac{R_{\rm L} Z_{\rm T} \tan{(\theta_{\rm T})}}{Z_{\rm T} \tan{(\theta_{\rm T})} - j R_{\rm L}}$$

(3)

Meanwhile, the impedance at the main current source plane,  $Z_{\rm m}$ , can be expressed as [13]

$$Z_{\rm m} = Z_{\rm C} \frac{Z_{\rm mC} + j Z_{\rm C} \tan \left(\theta_{\rm C}\right)}{Z_{\rm C} + j Z_{\rm mC} \tan \left(\theta_{\rm C}\right)} \tag{4}$$

Assuming the IIN functions as  $\lambda/4$  transmission line, the required characteristic impedance  $Z_C$  is determined by [14]

$$Z_{\rm C} = \sqrt{\frac{R_{\rm opt}R_{\rm L}}{\beta_{\rm B}}} \tag{5}$$

where  $\beta_{\rm B}$ , when set to 0.5, represents the back-off level for a symmetrical Doherty PA targeting a 6-dB back-off efficiency enhancement. With these considerations, the impedance  $Z_{\rm m}$  can be calculated as

$$Z_{\rm m} = \frac{Z_{\rm C}^2}{Z_{\rm mC}} = \frac{R_{\rm opt}}{\beta_{\rm B}} \left( 1 - j \frac{R_{\rm L}}{Z_{\rm T} \tan \left(\theta_{\rm T}\right)} \right). \tag{6}$$

Equation (6) reveals that the proposed Doherty combiner topology effectively exhibits CM operation at the back-off power level, which is further illustrated in Fig. 2(b).

#### III. PROTOTYPE DESIGN

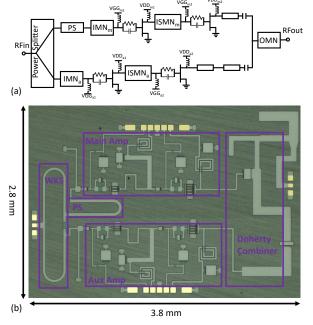

The developed CM Doherty PA, fabricated using a 150 nm GaN on SiC MMIC process from WIN Semiconductors (NP15-00), is a two-stage design with dedicated driver amplifiers for both main and auxiliary paths. To achieve a peak output power beyond 34 dBm,  $8\!\times\!100~\mu\mathrm{m}$  devices are selected for the final power stage, with  $4\times100~\mu\mathrm{m}$  devices employed for the driver stages. The main amplifiers are set to operate in Class-AB, whereas the auxiliary amplifiers are configured in Class-C mode, all biased with a 20 V drain supply voltage.

The block diagram of the designed CM Doherty PA is illustrated in Fig. 3(a). Note that all passive networks were EM simulated using ADS Momentum. A Wilkinson power splitter and a phase shifter were designed and employed at the Doherty PA's input to ensure appropriate signal and phase alignment for both amplifier paths. The design of the output combiner network was initiated with load-pull simulations to determine the optimal load impedance for the final-stage devices, thus optimizing power and efficiency over the targeted frequency range. The simulations facilitated the extraction of equivalent output optimal resistance and parasitic capacitance for subsequent modeling. Building on the insights gained, the output combiner network was then designed following the theoretical analysis presented earlier. Furthermore, the inter-stage matching network (ISMN) incorporates a design approach, as proposed in [15], [16], employing a filter-based matching network. This ISMN design optimizes matching conditions, substantially reducing in-band loss and ripples, which in turn improves the bandwidth performance of the PA.

Fig. 3. (a) The circuit block diagram and (b) chip photograph of the fabricated GaN MMIC CM Doherty PA (Total chip area:  $2.8~\mathrm{mm}\times3.8~\mathrm{mm}$  including DC and RF pads).

The stability of the circuit was carefully simulated using Winslow Stability (WS) probes at all gate and drain terminals, employing various loop gain approaches to test the PA stability. Parallel RC networks were implemented at the gates of both the driver and final stages to mitigate instability across different DC bias bond wire inductances. To counter low-frequency instabilities, a parallel LR network was integrated between the DC pad and the bypass capacitor on the drain bias line. Additionally, series resistors were incorporated into the gate bias lines to enhance stability for similar considerations.

# IV. MEASUREMENT RESULTS

A photograph of the fabricated CM Doherty PA prototype is shown in Fig. 3(b), which occupies a compact chip area of 2.8 mm3.8 mm including the DC and RF pads. The chip was further mounted on a customized printed circuit board (PCB), with the DC pads of the PA connected to decoupling capacitors through wire bonds. Small signal measurements were performed using a vector network analyzer with the calibration reference plane de-embedded to the GSG pads. Large signal testing employed a signal generator to produce static signals and the output power was measured with a power meter and spectrum analyzer.

#### A. Small Signal Measurement

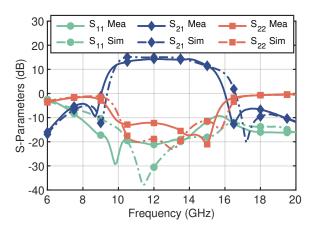

In Fig. 4, we present the small signal characterization of the prototype circuit, alongside a comparison with simulation results. We observe good agreement between the measured and simulated results of both the input and output return loss. Additionally, the measured small signal gain closely matches the simulated predictions, with minor deviations occurring only at the edge frequencies. It is worth mentioning that the

Fig. 4. Measured (solid line) and simulated (dashed line) small-signal results of the fabricated prototype Doherty PA circuit.

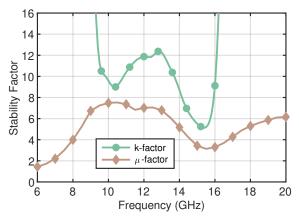

Fig. 5. Measured stability factors of the prototype Doherty PA circuit.

measured 3 dB bandwidth of the small signal gain is across  $9.6-15.1~\mathrm{GHz}$  and the prototype achieves an ultra-flat gain response within the operating frequencies. Furthermore, the prototype circuit is unconditionally stable as shown in Fig. 5.

## B. Large Signal Measurement

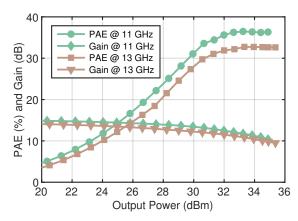

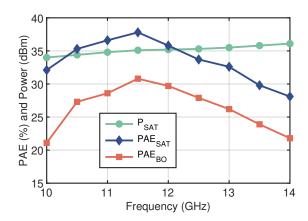

Fig. 6 illustrates the measured power added efficiency (PAE) versus the output power at 11 GHz and 13 GHz, demonstrating the prototype's smooth compression behavior without parametric oscillations. The static measured results in terms of peak power, peak- and 6-dB back-off PAE are further presented versus frequency in Fig. 7. It can be observed that a peak output power of 34.2-36.1 dBm is measured across the entire band within 10-14 GHz. Correspondingly, the measured peak PAE is 28-38%, while the measured PAE at 6-dB back-off power level is 21-31%.

The performance of the fabricated PA is then presented and compared with the state-of-the-art load modulated MMIC PAs in Table I. The comparison reveals that our prototype achieves excellent PAE at both peak and back-off levels compared to existing MMIC PAs designed for back-off efficiency enhancement. Furthermore, the prototype maintains competitive performance over a wide frequency range.

Fig. 6. Measured PAE and gain of the prototype versus output power.

Fig. 7. Measured power and PAE of the prototype versus frequency.

### V. CONCLUSION

This work proposes a novel output combiner network for CM Doherty PA designs, aimed at expanding the bandwidth of Doherty architectures. We present a two-stage, GaN on SiC, CM Doherty PA, capable of delivering over  $34~\mathrm{dBm}$  of power across the  $10{-}14~\mathrm{GHz}$  with a 33% fractional bandwidth. Furthermore, the prototype demonstrates PAE at peak and 6-dB back-off levels of 28%-38% and 21%-31%, respectively. To the best of our knowledge, this represents the first GaN MMIC CM Doherty PA designed for the FR3 cmWave band, highlighting its potential for 6G applications.

#### ACKNOWLEDGMENT

This work has been carried out in the Gigahertz-ChaseOn Bridge Center. We acknowledge WIN Semiconductors for chip fabrication and Keysight for the PNA-X software.

#### REFERENCES

- [1] "6G spectrum-enabling the future mobile life beyond 2030," Ericsson White Paper, Mar. 2023.

- [2] V. Åberg et al, "RF-DAC-based PA pre-distortion using expanding non-linear RF-DAC scaling," in *Proc. 19th Eur. Microw. Integr. Circuits Con. (EuMIC)*, 2024.

- [3] S. Alluri et al, "A compact 27 dBm triple-stack power amplifier for 13 GHz operation in CMOS-SOI," in *Proc. IEEE Topical Conf. RF/Microw. Power Model. Radio Wireless Appl. (PAWR)*, 2024, pp. 13–16.

Table 1. Summary of Load Modulated MMIC PAs.

| Ref.    | Arch. | BW<br>(GHz) | BW<br>(%) | PAE <sub>B</sub> (%) | PAE <sub>S</sub><br>(%) | P <sub>SAT</sub> (dBm) |

|---------|-------|-------------|-----------|----------------------|-------------------------|------------------------|

| [17]'22 | 2-DPA | 16.3-20.3   | 22        | 19-21                | 23-31                   | 36                     |

| [18]'23 | 3-DPA | 27.5-29.5   | 7         | 19-21                | 23-31                   | 34                     |

| [19]'17 | 2-DPA | 13.7-15.3   | 11        | 16*-28*              | 29*-39*                 | 35                     |

| [20]'19 | LMBA  | 10.8        | N.A.      | 26                   | 38                      | 35                     |

| [11]'22 | 2-DPA | 4.1-5.6     | 32        | 32-39                | 41-49                   | 35                     |

| T.W.    | 2-DPA | 10.0-14.0   | 33        | 21-31                | 28-38                   | 34                     |

\* drain efficiency reported,  $PAE_B$  and  $PAE_S$  denotes PAE at the back-off and peak power, respectively, and  $P_{SAT}$  denotes minimum peak power level.

- [4] H. Zhou et al, "A Ku-band GaN MMIC push-pull power amplifier with coupled-line balun and capacitive neutralization for 6G applications," in Proc. IEEE 50th Eur. Solid State Circuits Conf. (ESSCIRC), 2024.

- [5] D. J. Shepphard et al, "An efficient broadband reconfigurable power amplifier using active load modulation," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 6, pp. 443–445, 2016.

- [6] P. Saad et al, "A 1.8–3.8-GHz power amplifier with 40% efficiency at 8-dB power back-off," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 11, pp. 4870–4882, 2018.

- [7] H. Zhou et al, "A wideband and highly efficient circulator load modulated power amplifier architecture," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 70, no. 8, pp. 3117–3129, 2023.

- [8] —, "Wideband sequential circulator load modulated amplifier with back-off efficiency enhancement," in *Proc. 52nd Eur. Microw. Conf.* (EuMC), 2022, pp. 214–217.

- [9] S. C. Cripps et al, "On the continuity of high efficiency modes in linear RF power amplifiers," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 10, pp. 665–667, 2009.

- [10] X. Chen et al, "A broadband Doherty power amplifier based on continuous-mode technology," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 12, pp. 4505–4517, 2016.

- [11] J. Pang et al, "Broadband GaN MMIC Doherty power amplifier using continuous-mode combining for 5G sub-6 GHz applications," *IEEE J. Solid-State Circuits*, vol. 57, no. 7, pp. 2143–2154, 2022.

- [12] W. Shi et al, "Broadband continuous-mode doherty power amplifiers with noninfinity peaking impedance," *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 2, pp. 1034–1046, 2018.

- [13] J. H. Qureshi, L. Nan, E. Neo, F. V. Rijs, I. Blednov, and L. de Vreede, "A wide-band 20W LDMOS Doherty power amplifier," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2010, pp. 1–1.

- [14] H. Zhou et al, "A generic theory for design of efficient three-stage Doherty power amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 2, pp. 1242–1253, 2022.

- [15] D. E. Dawson, "Closed-form solutions for the design of optimum matching networks," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 1, pp. 121–129, 2009.

- [16] H. Zhou et al, "Design of a compact GaN power amplifier with high efficiency and beyond decade bandwidth," *IEEE Microw. Wireless Compon. Lett.*, pp. 1–4, 2022.

- [17] A. Piacibello et al, "A 5-W GaN Doherty amplifier for Ka-band satellite downlink with 4-GHz bandwidth and 17-dB NPR," *IEEE Microw. Wireless Compon. Lett.*, vol. 32, no. 8, pp. 964–967, 2022.

- [18] —, "A 3-way GaN Doherty power amplifier for 28 GHz 5G FR2 operation," in Proc. IEEE MTT-S Int. Microw. Symp. Dig, 2023.

- [19] R. Quaglia et al, "A 4-W Doherty power amplifier in GaN MMIC technology for 15-GHz applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 4, pp. 365–367, 2017.

- [20] A. Duh et al, "A 10.8-GHz GaN MMIC load-modulated amplifier," in *Proc. 49th Eur. Microw. Conf. (EuMC)*, 2019, pp. 408–411.