## A 25-40 GHz Three-Way Power Amplifier with No Load Modulation Achieving Broadband Deep Power Back-Off Efficiency Enhancement

Downloaded from: https://research.chalmers.se, 2024-08-17 01:52 UTC

Citation for the original published paper (version of record):

Liu, E., Zhou, H., Fager, C. et al (2024). A 25-40 GHz Three-Way Power Amplifier with No Load Modulation Achieving Broadband Deep Power

Back-Off Efficiency Enhancement. Digest of Papers - IEEE Radio Frequency Integrated Circuits Symposium: 127-130. http://dx.doi.org/10.1109/RFIC61187.2024.10600051

N.B. When citing this work, cite the original published paper.

© 2024 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, or reuse of any copyrighted component of this work in other works.

This document was downloaded from http://research.chalmers.se, where it is available in accordance with the IEEE PSPB Operations Manual, amended 19 Nov. 2010, Sec, 8.1.9. (http://www.ieee.org/documents/opsmanual.pdf).

# A 25-40 GHz Three-Way Power Amplifier with No Load Modulation Achieving Broadband Deep Power Back-Off Efficiency Enhancement

Edward Liu<sup>#\*</sup>, Han Zhou<sup>\$\*</sup>, Christian Fager<sup>\$</sup>, Hua Wang<sup>#</sup>

#ETH Zürich, Switzerland

\$Chalmers University of Technology, Sweden

edwliu@iis.ee.ethz.ch

Abstract — This paper presents a millimeter-wave (mm-Wave) power amplifier (PA) topology that avoids the trade-off between bandwidth and load modulation. The proposed topology uses three PA paths and can achieve efficiency enhancement at power back-off without load modulation. With a 100 MHz 5G NR FR2 1-CC 64-QAM signal, this PA achieves  $\mathrm{P}_{\mathrm{AVG}}$  and  $\mathrm{PAE}_{\mathrm{AVG}}$  of 6.45 - 12.61 dBm and 5.9 - 16.4% from 25 - 40 GHz, respectively. With a 200 MHz, signal,  $\mathrm{P}_{\mathrm{AVG}}$  and  $\mathrm{PAE}_{\mathrm{AVG}}$  are 5.58 - 11.1 dBm and 4.8 - 13.3%, respectively.

Keywords - 5G, CMOS, Mm-Wave, Power amplifiers.

#### I. Introduction

The use of complex and spectrally efficient modulation schemes (e.g., 64-QAM and higher) is a pre-requisite for multi-Gbps data rates in next-generation wireless communication systems. However, these signals have a high peak-to-average power ratio (PAPR) requiring the power amplifier (PA) to often operate in power back-off (PBO). For example, a 5G NR FR2 1-CC 64-QAM signal has PAPR of approximately 9.6 dB, which is often considered as "deep" PBO. This signifies the importance of deep PBO efficiency enhancement for advanced PA designs [1]. Furthermore, different countries around the world are allocated different FR2 bands, so a broadband PA design covering all FR2 bands will greatly benefit the RF frontend flexibility and cost.

Recently, there have been multiple PA architectures reported that address PBO efficiency enhancement. The load-modulated balanced amplifier (LMBA) is both wideband and efficient at PBO but is difficult to implement on chip due to the required large quadrature coupler and the need for additional baluns to interface this coupler with differential PAs [2]. The Doherty architecture achieves PBO efficiency enhancement by using an auxiliary PA path to perform active load modulation. This architecture requires a  $\lambda/4$  impedance inverter, which inherently limits the load modulation bandwidth. In addition to bandwidth limitations, load modulation also results in degraded AM-AM and AM-PM linearity when deviating from the center frequency [3]. Moreover, deep PBO efficiency enhancement demands multi-way Doherty PAs with high impedance transformation ratios and large ranges of load modulation, which further degrades the output passive efficiency while also severely limiting bandwidth and linearity [4], [5], [6]. Recently, a broadband parallel-series architecture has been reported [7].

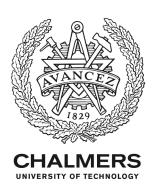

Fig. 1. Schematic of the non-load modulated PA output network.

However, this design is not instantaneously broadband since it requires mode switching. Furthermore, this design exhibits large gain variations across the operating frequency, and requires a large area overhead due to the four PA paths.

Yet another way of achieving broadband PBO efficiency enhancement is to remove the load modulation entirely [8], [9]. The distributed efficient PA (DEPA) architecture utilizes a unique auxiliary PA control and combiner design, resulting in constant PA load impedance vs PBO. This removes the bandwidth limitation due to the load modulation in all load-modulated PAs. However, the architecture in [8] is challenging for CMOS designs, as the required six auxiliary paths are extremely area intensive and complex to coordinate. Additionally, the Main PA is placed furthest from the output, incurring the full loss of the output network, thereby reducing the PA efficiency particularly at deep PBO. In [9], the same no load modulation concept is demonstrated with only two auxiliary paths, but this design has a much smaller fractional bandwidth (33%) compared to [8] (71%).

To address these challenges, this paper presents a new PA topology with no load modulation that is simultaneously broadband and efficient at deep PBO. It uses only two auxiliary PAs and one Main PA, drastically reducing the complexity compared to [8], and has a greater -3dB  $S_{21}$  fractional bandwidth (45%) compared to [9].

<sup>\*</sup> equal contribution

Fig. 2. (a) EM model of the output combiner, simulated passive efficiency, and simulated impedance presented to the Main PA at PBO and peak  $P_{out}$ . (b) EM model of the 1:3 quadrature coupler with simulated phase shift and power splitting.

## II. PROPOSED NON-LOAD MODULATED ARCHITECTURE

As seen in Fig. 1, the proposed PA architecture uses three amplifier paths, which are the Main, auxiliary 1 (Aux1), and auxiliary 2 (Aux2). The Main and Aux1 are parallel combined, then both are series combined with Aux2, with a Main:Aux1:Aux2 sizing ratio of 1:1:2. At PBO, only the Main is turned on, which sees an impedance of  $R_{\rm opt}.$  As the input drive increases, Aux1 and Aux2 are turned on at the same time. At peak  $P_{\rm out}$  Aux1 and Aux2 see impedances of  $R_{\rm opt}$  and  $\frac{R_{\rm opt}}{2}$ , respectively. However, different than a Doherty PA, here the Main PA sees a constant load all the time. Shown in Fig. 1, the Main sees a  $Z_{\rm m}$  which is independent of the Aux currents  $I_{\rm a1}$  and  $I_{\rm a2}.$  This is due to the fact that the current and voltage swing at the drain of the Main PA reaches their maximum at PBO, which also ensures PBO efficiency enhancement.

The 3D electromagnetic (EM) model of the output combiner is shown in Fig. 2. For the on-chip realization of this output combiner, low loss coupled-line based baluns are used

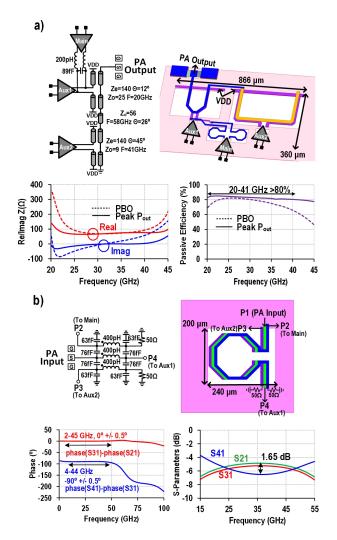

Fig. 3. Full schematic of the proposed PA.

in series to connect the Aux paths, and the Main is connected using an LC-based  $\lambda/4$  line. The resulting Main PA load impedance stays almost constant at both peak power and PBO from 25-40 GHz, verifying the absence of load modulation (Fig. 2(a)). Additionally, the passive efficiency of the output network is shown across frequency and is >80% at peak  $P_{\rm out}$ . Notably, this output network has the Main path much closer to the load compared to that of the DEPA implementation in [8], enabling a higher passive efficiency.

On the other hand, the input network for this PA needs to achieve proper three-way power splitting, phase shifting, and input matching across the full bandwidth. Shown in Fig. 2(b), a 1:3 coupled-inductor quadrature coupler is used to achieve this goal. This coupler fits into a single inductor footprint. Compared to the input networks of other three-way Doherty PAs, which often utilize a complex cascade of power dividers,  $90^{\circ}$  couplers and lengthy transmission lines ([5], [6]), the proposed input network is very compact. By taking the Main PA as the reference, the simulated phases of the input to Aux1/Aux2 are  $-90^{\circ}/0^{\circ}$  over 4-44 GHz with a maximum deviation of only  $\pm$  0.5°. Furthermore, the network also shows the split of input power to the three paths with a maximum difference of 1.65 dB across 25-45 GHz.

## III. CIRCUIT SCHEMATIC

A schematic of the full circuit is shown in Fig. 3. Each of the three paths consists of a driver and a power stage. First, the RF signal is appropriately split and phase shifted by the 1:3 quadrature coupler at the input. Then, a transformer balun is used to convert the single-ended signal to differential. Both the driver and power stage are differential with capacitative neutralization. The power stage is cascoded so that a higher

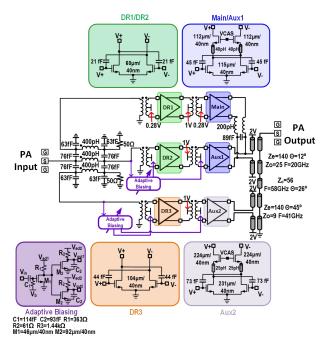

Fig. 4. PA die photo. The total area is  $2.49~\mathrm{mm}^2$ , and the core area is  $1.07~\mathrm{mm}^2$

voltage supply can be used. An inductor between the common source (CS) and common gate (CG) stages is used to absorb the interstage parasitic of the transistors, ensuring that the current from the CS device is transferred to the CG device with minimal loss.

An adaptive biasing circuit is used on both Aux paths, which serves a few purposes. First, at deep PBO when only the Main path is on, both the driver and the power stage of the Aux1 and Aux2 paths are kept off to reduce unnecessary DC power consumption. Second, the adaptive bias ramp-ups the  $V_{\rm gs}$  of the Aux paths so that at peak  $P_{\rm out}$  all PA paths have the same gate bias, maintaining the drive profiles described in Fig. 1. The simulated bandwidth of the adaptive biasing circuit is approximately 2.2 GHz, which is sufficient for supporting signals with modulation bandwidth up to around 700 MHz.

## IV. MEASUREMENT RESULTS

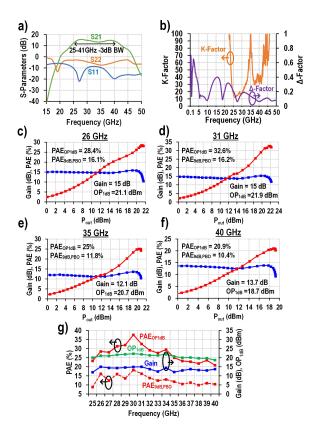

The PA is fabricated in the GF 45nm RFSOI CMOS process, and the chip photo is shown in Fig. 4. The total area including pads is 2.49 mm<sup>2</sup>, with a core area of 1.07 mm<sup>2</sup>. The die is attached to a PCB and wirebonded. RF input/output are measured by on-chip probing. The driver stage/power stage use a  $V_{\rm DD}$  of 1V/2V, respectively. The measured s-parameters, stability factor, and large signal continuous-wave (CW) results across frequency are shown in Fig. 5.

Shown in Fig. 5(a), the  $\rm S_{21}$  -3dB bandwidth is 25 - 41 GHz, with  $\rm S_{11}$  < -10dB from 25 - 30 GHz and 35 - 50 GHz. From 30 - 35 GHz, the  $\rm S_{11}$  is <-8.7 dB. Additionally, the K- $\Delta$  stability factor is shown from 100 MHz to 50 GHz, showing unconditional stability across all frequencies (Fig. 5(b)). With a large-signal CW test, the PA achieves an  $\rm OP_{1dB}$  of 18.7 - 22.2 dBm,  $\rm PAE_{OP1dB}$  of 20.9 - 37.6%, power gain of 12 - 15 dB, and  $\rm PAE_{9dB,PBO}$  of 8.8 - 18.2% from 25 - 40 GHz (Fig. 5(c)-(g)). Efficiency enhancement at deep PBO is clearly shown across frequency, verifying the simultaneous broadband and deep PBO efficiency enhancement capabilities.

Furthermore, the PA is tested using 5G NR FR2 1-CC 64-QAM signals with bandwidths of both 100 MHz and 200

Fig. 5. Measured results for (a) S-parameter (b) k-factor and (c) - (g) large signal CW from 25 - 40 GHz.

Fig. 6. Measured results with modulated signals.

MHz (Fig. 6). With a 100 MHz signal, the PA achieves an average  $P_{\rm out}$  and PAE of 6.45 dBm - 12.61 dBm and 5.9% - 16.4% at an  $EVM_{\rm rms}$  of -25 dB from 25 - 40 GHz. With a 200 MHz signal, the PA achieves an average  $P_{\rm out}$  and PAE

Table 1. Comparison with PBO efficiency enhancement PAs from 20 - 40 GHz.

|                               | This Work                                                |           |           |         | Ma [5]<br>ISSCC 2022                                       | Zhang [6]<br>JSSC 2023                  |          | Mortazavi [10]<br>JSSC 2022 | Hu [11]<br>ISSC 2017      |        | Chappidi [12]<br>VLSI 2019 |                                         |      | Huang [13]<br>ISSCC 2021 |                                |      |      | Liu [7]<br>JSSC 2023 |                                      |        |                           |      |

|-------------------------------|----------------------------------------------------------|-----------|-----------|---------|------------------------------------------------------------|-----------------------------------------|----------|-----------------------------|---------------------------|--------|----------------------------|-----------------------------------------|------|--------------------------|--------------------------------|------|------|----------------------|--------------------------------------|--------|---------------------------|------|

| Technology                    | 45nm SOI CMOS                                            |           |           |         | 55nm CMOS                                                  | 40nm CMOS                               |          | 40nm CMOS                   | 130nm SiGe                |        |                            | 65nm CMOS                               |      |                          | 45nm SOI CMOS                  |      |      |                      | 45                                   | 5nm S0 | OI CM                     | os   |

| Architecture                  | 3-Way Parallel-Series with No Main<br>PA Load Modulation |           |           |         | Transformer-<br>based 3-way<br>Parallel -Series<br>Doherty | Coupled-Inductor-based<br>3-Way Doherty |          | Digital Polar<br>TX         | Multiband Doherty         |        |                            | Broadband<br>Doherty-Like<br>Multi-Port |      |                          | Continuous Coupler             |      |      |                      | Coupler Based Para<br>Series Doherty |        |                           |      |

| Supply (V)                    | 2                                                        |           |           |         | 2.4                                                        | 1.8                                     |          | 1                           | 1.5                       |        |                            | 1.1                                     |      |                          | 2                              |      |      |                      | 2                                    |        |                           |      |

| -3dB S <sub>21</sub> BW (GHz) | 25-41<br>(48%)                                           |           |           |         | 25.9-32.6<br>(23%)                                         | 35.9-39.5<br>(10%)                      |          | 24-31<br>(26%)              | 23.3-39.7<br>(52%)        |        | N/A                        |                                         |      | N/A                      |                                |      | N/A  |                      |                                      |        |                           |      |

| Core Area (mm²)               | 1.07                                                     |           |           |         | 0.54                                                       | 1.4                                     |          | 0.55 <sup>b</sup>           | 1.76(incl. pads)          |        | 1.35 (incl. pads)          |                                         |      | 0.62                     |                                |      |      |                      | 1.                                   | 55     |                           |      |

| Freq (GHz)                    | 26                                                       | 30        | 37        | 40      | 28                                                         | 3                                       | 8        | 29.5                        | 28                        | 37     | 39                         | 28                                      | 37   | 39                       | 26                             | 32.5 | 37.5 | 40                   | 26                                   | 33     | 38                        | 40   |

| Gain (dB)                     | 14.5                                                     | 14.9      | 13.7      | 13.7    | 16.1                                                       | 15                                      |          | N/A                         | 18.2                      | 17.1   | 16.6                       | 15*                                     | 16*  | 17.5*                    | 11*                            | 16*  | N/A  | N/A                  | 12*                                  | 15*    | 12*                       | 13*  |

| P <sub>SAT</sub> (dBm)        | 21.4                                                     | 22.6      | 20.2      | 19.1    | 25.5                                                       | 18.9                                    |          | 18.7                        | 16.8                      | 17.1   | 17                         | 19                                      | 19.6 | 19.2                     | 20.8                           | 22   | 21.8 | 21.8                 | 23.5                                 | 24.1   | 22.8                      | 22.7 |

| OP <sub>1dB</sub> (dBm)       | 21.1                                                     | 22.2      | 20.1      | 18.7    | 24.3                                                       | 18.4                                    |          | N/A                         | 15.2                      | 15.5   | 15.4                       | 19                                      | 16   | 18.1                     | 18.3                           | 21.5 | 20*  | 20*                  | 22.8                                 | 23.9   | 22.7                      | 22.5 |

| PAE <sub>1dB</sub> (%)        | 28.4                                                     | 37.6      | 22.8      | 20.9    | 24.4                                                       | 23                                      |          | 36° (PAE <sub>max</sub> )   | 19.5                      | 21.6   | 20.7                       | 21.6                                    | 21.9 | 21.7                     | 20.4                           | 39.9 | 30*  | 25*                  | 27.6                                 | 38.2   | 26.8                      | 26.2 |

| PAE@9dB PBO (%)               | 16.1                                                     | 18.2      | 11.3      | 10.4    | 18*                                                        | 13.7**                                  |          | 26°*                        | 13*^                      | 17.5*^ | 15*^                       | 7*                                      | 13*  | 12*                      | 8*                             | 23*  | N/A  | N/A                  | 18*                                  | 29*    | 15*                       | 12*  |

| Modulation                    | 5G NR FR2 1-CC 64-QAM OFDM                               |           |           |         | Single-Carrier<br>64-QAM                                   | 5G NR FR2<br>1-CC 64-<br>QAM OFDM       | 2-CC 64- | 64-QAM<br>OFDM (/w<br>DPD)  | Single-Carrier 64-<br>QAM |        |                            | 64-QAM OFDM                             |      |                          | 5G NR FR2 1-CC 64-<br>QAM OFDM |      |      |                      | 5G NR 1-<br>CC 64-<br>QAM            |        | 5G NR 1-<br>CC 16-<br>QAM |      |

| PAPR (dB)                     | 9.64                                                     |           |           |         | 6                                                          | 9.64                                    | 11.85    | 10.7                        |                           | 6      |                            | N/A<br>1000 2000                        |      |                          | 9.64                           |      |      |                      | 9.64                                 |        | 9.64                      |      |

| Bandwidth(MHz)                | 100/200                                                  |           |           | 250     | 100                                                        | 100                                     | 300      |                             | 500                       |        | 1000                       |                                         |      |                          |                                | _    |      |                      |                                      | _      | 00                        |      |

| Freq. (GHz)                   | 28                                                       | 30        | 37        | 40      | 28                                                         |                                         |          |                             | 30                        | 32.5   | 40                         |                                         |      | 35                       |                                |      |      |                      |                                      |        |                           |      |

| EVMrms (dB)                   | -25                                                      |           |           | -25.2   | -25                                                        | -25.1                                   | -27.58   | -27ª                        | -30.3ª                    | -28.7ª | -22                        | -24                                     | -23  | -25                      | -25                            | -25  | -25  |                      |                                      | -20    |                           |      |

| Pout <sub>avg</sub> (dBm)     |                                                          | 11.8/10.5 |           | 9/8.04  | 17.7                                                       | 11.3                                    | 10       | 7.9                         | 9.2                       | 9.5    | 9.3                        | 7.5                                     | 9.8  | 9.1                      | 7*                             | 8*   | 9.5  | 8.9                  |                                      |        |                           | .55  |

| PAE <sub>avg</sub> (%)        | 13.2/11                                                  | 16.4/13.2 | 12.6/10.6 | 8.9/7.4 | 17.5                                                       | 14.7                                    | 13.4     | 18°                         | 18.5^                     | 19.2^  | 17.2^                      | 5.1                                     | 10.2 | 8.5                      | 6*                             | 8*   | 15.5 | 10.5                 | .5 25.2                              |        | 26                        | 6.4  |

\*Estimated from figures \*\*9.6 dB PBO ^Collector Efficiency °Drain Efficiency <sup>a</sup>EVM normalized to peak signal

bCore Area consisting of I/Q splitter, DPM, DPA, and SDC

of 5.58 dBm - 11.1 dBm and 4.8% - 13.3% at an  $\rm EVM_{rms}$  of -25 dB from 25 - 40 GHz.

### V. CONCLUSION

This paper describes a PA architecture that achieves broadband and deep PBO efficiency enhancement. From Table 1, previous works using higher-order output networks at mm-Wave are mostly narrowband. Other works that are broadband do not have deep PBO efficiency enhancement. In comparison, this work can achieve both. As demonstrated with 5G NR FR2 64-QAM signals, this PA is suitable for use in the 5G n257 - 261 bands.

#### ACKNOWLEDGMENT

The authors would like to thank GlobalFoundries for chip fabrication and Keysight Technologies for measurement equipment support.

## REFERENCES

- H. Wang et al., "Power Amplifiers Performance Survey 2000-Present," [Online]. Available: https://ideas.ethz.ch/Surveys/pa-survey.html.

- [2] D. J. Shepphard, J. Powell, and S. C. Cripps, "An Efficient Broadband Reconfigurable Power Amplifier Using Active Load Modulation," *IEEE Microwave and Wireless Components Letters*, vol. 26, no. 6, pp. 443–445, 2016.

- [3] M. Pashaeifar, L. C. N. de Vreede, and M. S. Alavi, "A Millimeter-Wave CMOS Series-Doherty Power Amplifier With Post-Silicon Inter-Stage Passive Validation," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 10, pp. 2999–3013, 2022.

- [4] H. Zhou et al., "A Generic Theory for Design of Efficient Three-Stage Doherty Power Amplifiers," IEEE Transactions on Microwave Theory and Techniques, vol. 70, no. 2, pp. 1242–1253, 2022.

- [5] Z. Ma, K. Ma, K. Wang, and F. Meng, "A 28GHz Compact 3-Way Transformer-Based Parallel-Series Doherty Power Amplifier With 20.4%/14.2% PAE at 6-/12-dB Power Back-off and 25.5dBm PSAT in 55nm Bulk CMOS," in 2022 IEEE International Solid-State Circuits Conference (ISSCC), vol. 65, 2022, pp. 320–322.

- [6] X. Zhang, S. Li, D. Huang, and T. Chi, "A Millimeter-Wave Three-Way Doherty Power Amplifier for 5G NR OFDM," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 5, pp. 1256–1270, 2023.

- [7] E. Liu and H. Wang, "A Broadband Four-Way Parallel-Series Doherty Power Amplifier for 5G Communications," *IEEE Journal of Solid-State Circuits*, pp. 1–11, 2023.

- [8] P. Saad, R. Hou, R. Hellberg, and B. Berglund, "A 1.8–3.8-GHz Power Amplifier With 40% Efficiency at 8-dB Power Back-Off," *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 11, pp. 4870–4882, 2018.

- [9] P. Saad, R. Hou, R. Hellberg, and B. Berglund, "A 65W Power Amplifier Without Load Modulation to Achieve 50% Efficiency at 8dB Power Back-Off over 1.8-2.5 GHz," in 2020 50th European Microwave Conference (EuMC), 2021, pp. 1095–1098.

- [10] M. Mortazavi, Y. Shen, D. Mul, L. C. N. de Vreede, M. Spirito, and M. Babaie, "A Four-Way Series Doherty Digital Polar Transmitter at mm-Wave Frequencies," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 3, pp. 803–817, 2022.

- [11] S. Hu, F. Wang, and H. Wang, "A 28-/37-/39-GHz Linear Doherty Power Amplifier in Silicon for 5G Applications," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 6, pp. 1586–1599, 2019.

- [12] C. R. Chappidi and K. Sengupta, "A 26-42 GHz Broadband, Back-off Efficient and Vswr Tolerant CMOS Power Amplifier Architecture for 5G Applications," in 2019 Symposium on VLSI Circuits, 2019, pp. C22–C23.

- [13] T.-Y. Huang et al., "26.1 A 26-to-60GHz Continuous Coupler-Doherty Linear Power Amplifier for Over-An-Octave Back-Off Efficiency Enhancement," in 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64, 2021, pp. 354–356.