# Gate control of superconducting current: Mechanisms, parameters, and technological potential

Downloaded from: https://research.chalmers.se, 2024-11-19 10:23 UTC

Citation for the original published paper (version of record):

Ruf, L., Puglia, C., Elalaily, T. et al (2024). Gate control of superconducting current: Mechanisms, parameters, and technological potential. Applied Physics Reviews, 11(4). http://dx.doi.org/10.1063/5.0222371

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

REVIEW ARTICLE | OCTOBER 31 2024

# Gate control of superconducting current: Mechanisms, parameters, and technological potential

L. Ruf ⑩ ; C. Puglia ⑩ ; T. Elalaily ⑩ ; G. De Simoni ⑩ ; F. Joint ⑩ ; M. Berke ⑩ ; J. Koch ⑩ ; A. Iorio ⑩ ; S. Khorshidian ⑩ ; P. Makk ⑪ ; S. Gasparinetti ⑩ ; S. Csonka ⑩ ; W. Belzig ⑩ ; M. Cuoco ⑩ ; F. Giazotto ⑩ ; E. Scheer ➡ ⑩ ; A. Di Bernardo ➡ ⑪

Appl. Phys. Rev. 11, 041314 (2024) https://doi.org/10.1063/5.0222371

### **Articles You May Be Interested In**

Dynamics of gate-controlled superconducting Dayem bridges

Appl. Phys. Lett. (August 2024)

A gate- and flux-controlled supercurrent diode effect

Appl. Phys. Lett. (January 2023)

Tunable coupling of widely separated superconducting qubits: A possible application toward a modular quantum device

Appl. Phys. Lett. (July 2022)

# Gate control of superconducting current: Mechanisms, parameters, and technological potential

Cite as: Appl. Phys. Rev. 11, 041314 (2024); doi: 10.1063/5.0222371 Submitted: 7 June 2024 · Accepted: 19 September 2024 · Published Online: 31 October 2024

B. Heating due to phonons excited in the substrate

```

L. Ruf, D. C. Puglia, D. T. Elalaily, A. D. G. De Simoni, D. F. Joint, D. M. Berke, D. Koch, D. A. Iorio, D. S. Khorshidian, D. P. Makk, A. D. S. Casparinetti, D. S. Csonka, M. Belzig, D. M. Cuoco, D. F. Giazotto, D. S. Csonka, D. A. Di Bernardo D. G. Giazotto, D. S. Csonka, D. G. Bernardo D. G. Giazotto, D. S. Csonka, D. G. Giazotto, D. G. Scheer, D. Giazotto, D. G. Giazotto, D. G. Giazotto, D. G. Giazotto, D. Giazot

```

#### **AFFILIATIONS**

#### **ABSTRACT**

In conventional metal-oxide semiconductor (CMOS) electronics, the logic state of a device is set by a gate voltage ( $V_{\rm G}$ ). The superconducting equivalent of such effect had remained unknown until it was recently shown that a  $V_{\rm G}$  can tune the superconducting current (supercurrent) flowing through a nanoconstriction in a superconductor. This gate-controlled supercurrent (GCS) can lead to superconducting logics like CMOS logics, but with lower energy dissipation. The physical mechanism underlying the GCS, however, remains under debate. In this review article, we illustrate the main mechanisms proposed for the GCS, and the material and device parameters that mostly affect it based on the evidence reported. We conclude that different mechanisms are at play in the different studies reported so far. We then outline studies that can help answer open questions on the effect and achieve control over it, which is key for applications. We finally give insights into the impact that the GCS can have toward high-performance computing with low-energy dissipation and quantum technologies.

© 2024 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0222371

#### **TABLE OF CONTENTS**

| I. INTRODUCTION                                 | 2  | (phonon heating)                                   | 12 |

|-------------------------------------------------|----|----------------------------------------------------|----|

| II. REPRODUCIBILITY AND UNIVERSAL FEATURES      | _  | C. Out-of-equilibrium state due to high-energy     |    |

| OF THE GCS                                      | 3  | electrons and/or phonons excited in the            |    |

| A. Integration of GCS devices into more complex |    | substrate (phase fluctuations)                     | 13 |

| device structures                               | 6  | D. V <sub>G</sub> -induced mechanism (direct field |    |

| III. PHYSICAL MECHANISMS PROPOSED FOR THE       |    | effect)                                            | 15 |

| GCS                                             | 6  | IV. EXPERIMENTAL PARAMETERS AFFECTING              |    |

| A. Tunneling of high-energy electrons through   |    | THE GCS AND THE PERFORMANCE OF GCS                 |    |

| vacuum (field emission)                         | 11 | DEVICES                                            | 18 |

Department of Physics, University of Konstanz, Universitätsstraße 10, 78464 Konstanz, Germany

$<sup>^2</sup>$ NEST, Istituto Nanoscienze-CNR and Scuola Normale Superiore, Piazza san Silvestro 12, 56127 Pisa, Italy

<sup>&</sup>lt;sup>3</sup>MTA-BME Superconducting Nanoelectronics Momentum Research Group, Müegyetem rkp. 3., 1111 Budapest, Hungary

Department of Physics, Budapest University for Technology and Economics, Müegyetem rkp. 3., 1111 Budapest, Hungary 🕯

$<sup>^5</sup>$ Department of Physics, Faculty of Science, Tanta University, Al-Geish St., 31527 Tanta, Gharbia, Egypt

<sup>&</sup>lt;sup>6</sup>Department of Microtechnology and Nanoscience, Chalmers University of Technology, 41296 Göteborg, Sweden

$<sup>^{7}</sup>$ CNR-SPIN, c/o Università degli Studi di Salerno, via Giovanni Paolo II 132, 84084 Fisciano, Salerno, Italy

<sup>&</sup>lt;sup>8</sup>Dipartimento di Fisica "E. R. Caianiello," Università degli Studi di Salerno, via Giovanni Paolo II 132, 84084 Fisciano, Salerno, Italy

b) Authors to whom correspondence should be addressed: elke.scheer@uni-konstanz.de and angelo.dibernardo@uni-konstanz.de

| A. Effects of material parameters, device geometry,        |    |

|------------------------------------------------------------|----|

| and fabrication process                                    | 18 |

| 1. Influence of S type and structural disorder             | 18 |

| 2. Influence of the substrate material                     | 19 |

| 3. Influence of the device geometry                        | 20 |

| 4. Influence of the fabrication process                    | 21 |

| B. $I_{leak}$ -induced effects toward prevalent mechanism. | 22 |

| V. TECHNOLOGICAL APPLICATIONS BASED ON                     |    |

| THE GCS                                                    | 24 |

| A. GCS for superconducting logics                          | 24 |

| B. Other applications of GCS devices for                   |    |

| superconducting electronics                                | 25 |

| C. Applications of GCS devices for quantum                 |    |

| computing                                                  | 26 |

| VI. OUTLOOK AND FUTURE CHALLENGES                          | 27 |

| VII. CONCLUSIONS                                           | 28 |

| SUPPLEMENTARY MATERIAL                                     | 29 |

### I. INTRODUCTION

The operation principle of modern computers based on complementary metal-oxide semiconductor (CMOS) technology relies on three-terminal transistors, which can be reversibly switched between two states via the application of a gate voltage (V<sub>G</sub>) modulating the charge carrier density.<sup>1,2</sup> Thanks to the development of nanoscale fabrication technologies, the density of devices in CMOS circuits has steadily increased. However, the size node (currently ~7 nm) of transistors has recently reached a regime where further downscaling has got challenging for both technological and physical reasons.<sup>3,4</sup> To keep up with the constant demand for faster and more efficient electronics, alternative technologies to CMOS are therefore emerging.<sup>5</sup> In this context, the steadily growing power dissipation and related thermal management issues of CMOS computing platforms have become reasons of concern. Large-scale computers (supercomputers) currently under development, which can process up to 1018 floating point operations per second (flops), have in fact power requirements close to 1 GW, meaning that they need their own power plants to operate.

Hybrid computing architectures, which consist of low-dissipation superconducting logics combined with CMOS memories (still better than any superconducting memories), are seen as promising solution to reduce the power dissipation of supercomputers. Such hybrid architectures can reduce the power consumption of supercomputers by a factor  $\sim 10^2$ , even after considering the cooling costs for their operation at cryogenic temperature (T). We note that cryogenic cooling of CMOS supercomputers alone would not solve the problem of their large power dissipation. <sup>6,8</sup>

Hybrid computing systems would be easier to realize if  $V_G$ -controlled superconducting devices were employed for their logic operations, since these devices can be interfaced more easily with  $V_G$ -controlled CMOS circuits. Nonetheless, the application of a  $V_G$  to control the state of a three-terminal device made from a metallic superconductor (S) had remained unexplored for years. It is generally accepted that, unlike for doped semiconductors under a  $V_G$  which enable CMOS operation, a metallic S should instead behave like any other normal metal (N). In a N, the electric field (E) induced by  $V_G$  is screened within the Thomas–Fermi length  $^{9,10}$  (typically of a few angstroms  $^{11}$ ) from its surface, which would hinder any gate control in metallic systems.

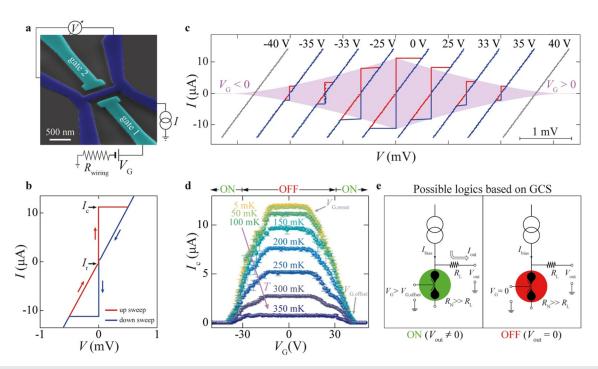

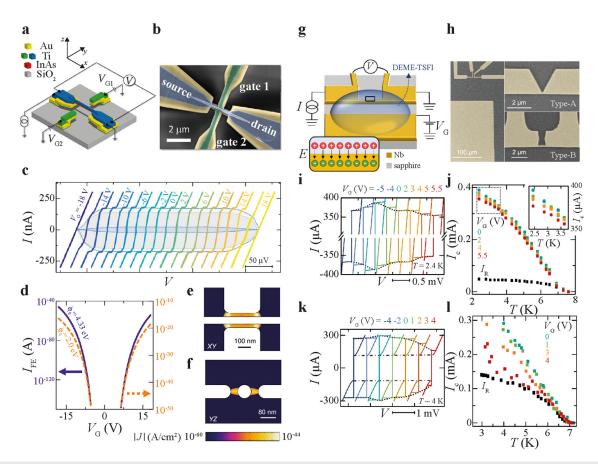

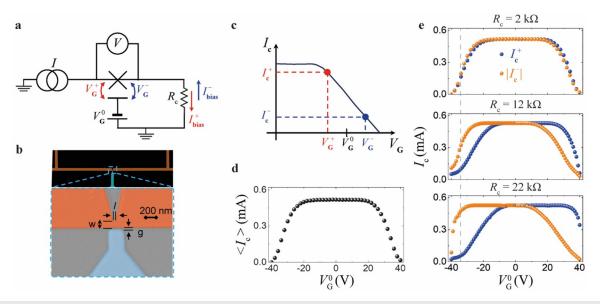

Surprisingly, an experiment performed in 2018<sup>12</sup> on gated superconducting Ti nanowires [Fig. 1(a)] has shown that these nanowires can also be switched between two different states with an applied  $V_{G}$ , similar to CMOS transistors. By measuring current vs voltage, I(V), characteristics of the gated Ti nanowires, the authors of Ref. 12 have shown that the superconducting critical current  $I_c$  (see Box 1 for an explanation of  $I_c$  and for an introduction to other basic concepts of superconductivity) measured without gate voltage [i.e., at  $V_G = 0$ ; Fig. 1(b)] can be reduced as V<sub>G</sub> is progressively increased, until it gets completely suppressed. Evidence for this result has been experimentally obtained by measuring a series of I(V) curves at different  $V_G$ , as shown in Fig. 1(c), and observing a progressive reduction of the vertical segment of the I(V) curve for increasing  $V_G$ , until the I(V) characteristic becomes fully linear. The presence of a vertical segment in the I(V) characteristic is a signature of the device being in its superconducting state because the voltage drop V measured across the device remains equal to zero despite a non-null I flowing through the device [this holds true up to a maximum I which defines the device  $I_{\mathcal{O}}$  Fig. 1(b)]. When the I(V) characteristic becomes linear upon the application of a certain  $V_G$  [see Fig. 1(c) for  $V_G = \pm 40$  V], the device has a finite resistance (i.e., it has ohmic behavior), and it gets out of the superconducting state, meaning that its  $I_c$  is equal to 0.

In gated superconducting devices, the behavior just described has been also observed upon reversal of the  $V_{\rm G}$  polarity (i.e., when an increasingly large negative  $V_{\rm G}$  is applied), meaning that the  $V_{\rm G}$ -induced suppression of  $I_{\rm c}$  has a bipolar nature [Fig. 1(c)]. For this reason, to neglect the dependence of the  $I_{\rm c}$  suppression on the  $V_{\rm G}$  polarity, below we refer to  $|V_{\rm G}|$  without specifying the sign of the applied  $V_{\rm G}$ .

The transition from a superconducting to a resistive state under an increasing  $V_{\rm G}$  in gated superconducting devices is usually not sharp. This transition can be better visualized by determining, for each I(V) measured at a certain  $V_{\rm G}$ , the corresponding  $I_{\rm c}$  [Fig. 1(c)] and then plotting the  $I_{\rm c}$  vs  $V_{\rm G}$  characteristic, as shown in Fig. 1(d). The  $I_{\rm c}(V_{\rm G})$  curve shows that, as  $V_{\rm G}$  is increased,  $I_{\rm c}$  remains equal to its value measured at  $V_{\rm G}=0$  ( $I_{\rm c0}$ ), until  $|V_{\rm G}|$  reaches a certain threshold, which we name here  $V_{\rm G,onset}$ . As  $|V_{\rm G}|$  is further increased above  $V_{\rm G,onset}$   $I_{\rm c}$  gets reduced progressively (other than abruptly) until it becomes zero at an even higher  $|V_{\rm G}|$  value ( $V_{\rm G,offset}$ ).

A gated superconducting device is therefore in a state with zero resistance (i.e., superconducting) with  $I_{\rm c} \neq 0$  for  $|V_{\rm G}| < V_{\rm G,offset}$  and in state with non-zero resistance (i.e., resistive) with  $I_{\rm c} = 0$  for  $|V_{\rm G}| > V_{\rm G,offset}$ . This observation has been first interpreted in Ref. 12 as an effect of the *E*-field induced by the  $V_{\rm G}$  applied to the gate separated from the nanowire. Nonetheless, since after this first study, 12 other explanations have been proposed for the gate-controlled supercurrent (GCS) observation, as discussed in Sec. III.

To associate each of the two states ( $I_c \neq 0$  and  $I_c = 0$ ) to a different voltage output ( $V_{\rm out}$ ) level like in CMOS transistors, a load resistor ( $R_{\rm L}$ ) can be connected to the output of the gated superconducting device, as shown in Fig. 1(e). When  $|V_{\rm G}| < V_{\rm G,offset}$  a zero-voltage signal ( $V_{\rm out}$ ) would be measured at the  $R_{\rm L}$  terminals because the bias current ( $I_{\rm bias}$ ), which always flows through the lowest resistance path, would flow through the superconducting channel of the device connected to ground, thus giving  $V_{\rm out} = 0$  (OFF state). When a  $|V_{\rm G}| > V_{\rm G,offset}$  is applied, the superconducting device gets in its resistive state and, if the normal-state resistance of the device ( $R_{\rm N}$ ) is engineered to be much larger than  $R_{\rm L}$ , then  $I_{\rm bias}$  would flow through  $R_{\rm L}$  giving a non-zero  $V_{\rm out}$  (ON state).  $R_{\rm N}$  is the resistance measured across the superconducting device in a four-point measurement setup right before the onset of its

### BOX 1. Basics of superconductivity and superconducting devices

Differently from normal conductors, where the electrical resistance gradually decreases until reaching a minimum non-zero value as temperature is reduced, superconductors (Ss) are materials where the electrical resistance vanishes, as they are cooled down below their characteristic *critical temperature* ( $T_c$ ). In addition to zero resistance, the superconducting state is also characterized by other macroscopic properties like the Meissner–Ochsenfeld effect, which consists in the expulsion of a magnetic field from the S interior up to a certain threshold (*upper critical field*), above which superconductivity is eventually suppressed.

As a result of the vanishing resistance of a S below  $T_c$ , it is possible to inject a current through a S, which does not dissipate energy as Joule heating. Like for the magnetic field, also the dissipationless current (*supercurrent*) injected in S can be sustained by S only up to a threshold value known as *switching supercurrent* (in this work identified with the critical current and hence denoted as  $I_c$ ). Above this current value, S turns again into a conventional dissipative conductor and its resistance becomes finite. The switching supercurrent  $I_c$  decreases in amplitude as temperature is increased, since superconductivity gets weaker with increasing temperature, until vanishing at  $T_c$ .

If the injected bias current is progressively lowered from a value above  $I_c$  meaning from a restive (dissipative) state, a S recovers its ability to support a supercurrent, although this can occur at a value of the bias current called *retrapping current* ( $I_r$ ), which do not have to be always equal to  $I_c$  but can also be lower. Such hysteretic behavior stems from the Joule heating that is generated in S, after it is driven in the resistive state.

Superconductivity is a quantum phenomenon, which is microscopically described, at least in most Ss made of a single chemical element, by the Bardeen–Cooper–Schrieffer (BCS) theory. The BCS theory shows that, at sufficiently low temperatures, pairs of conduction electrons can correlate in space and time forming the so-called *Cooper pairs*. The length scale over which this correlation occurs in space, which can also be seen as the size of the Cooper pair, is known as superconducting coherence length  $\xi$ .

The formation of Cooper pairs is due to the presence of a net attractive potential, no matter how weak, stemming from the interaction of the electrons within the S material lattice. According to the BCS theory, superconductivity originates from the condensation of Cooper pairs into the same ground state. Excitations of Cooper pairs above the ground state, which are superpositions of negatively charged electrons and positively charged holes, are called Bogoliubov quasiparticles after Nikolay Bogoliubov. The minimum energy needed to excite a quasiparticle electron–hole couple from a Cooper pair in its ground state is the superconducting energy gap ( $\Delta$ ). Like the supercurrent, also  $\Delta$  decreases as the temperature is increased and it vanishes at  $T_c$ . The presence of this gap is key toward enabling dissipationless transport.

Thanks to the *Josephson effect*, named after the physicist Brian Josephson who discovered it, a supercurrent can flow without any voltage applied not only in bulk Ss, but also in devices (*Josephson Junctions*, or JJs) consisting of two or more superconductors coupled by a *weak link*. Possible weak links include a thin insulating barrier (superconductor–insulator–superconductor or S-I-S JJ), a short normal metal bridge (S-N-S JJ), and a geometric constriction, with typical width of the order of few hundreds of nanometers where superconductivity is weakened (S-S'-S JJ). The latter type of weak link is also referred to as *Dayem Bridge*.

superconducting transition [or equivalently the inverse of the slope of the I(V) curve when I overcomes  $I_c$  and V becomes non-null; Fig. 1(b)].

Although the reversible suppression of  $I_c$  under an applied  $V_G$ —to which we refer hereafter as gate-controlled supercurrent (GCS)—paves the way for the development of the superconducting equivalent of CMOS logics, the physical mechanism underlying the GCS remains under debate. Understanding the physical mechanism responsible for the observation of a GCS is important from a basic science point of view. Furthermore, understanding the mechanism is also crucial to predict performance parameters such as speed, power consumption, and heat generation of future logic devices based on the GCS. Similarly, studying material properties and device parameters that allow to reproduce the GCS in a systematic way is a crucial step to control this phenomenon and to develop applications based on it.

After reviewing the main features of the GCS and the different mechanisms proposed to explain it along with the evidence in support of each of them, in this article we also discuss the main material and device parameters that mostly affect the GCS, based on the studies reported to date. Throughout the review, we also outline which studies can be carried out to better understand the microscopic nature of the GCS and highlight emerging research trends in the field of the GCS that are promising for future device-oriented applications. We also

discuss the open challenges that must be overcome to develop GCS-based superconducting logics with better performance than CMOS logics and than other commercially available superconducting logics like rapid single flux quantum logic. The impact of the GCS on emerging research areas like quantum computing is also briefly outlined.

# II. REPRODUCIBILITY AND UNIVERSAL FEATURES OF THE GCS

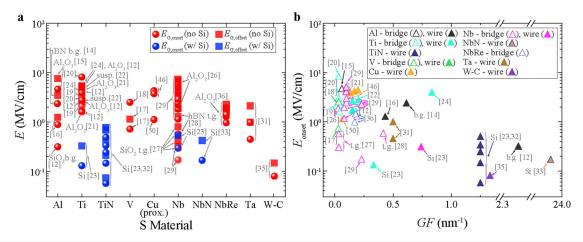

Over the past 6 years since its first observation in Ref. 12, several research groups have reproduced the GCS using a variety of superconductors (Ss) and device geometries. The Ss in which a GCS has been observed include elemental metallic Ss like Al,  $^{12-16}$  V,  $^{17,18}$  Ti,  $^{12,19-24}$  Nb,  $^{23,25-30}$  Ta,  $^{31}$  superconducting nitrides like TiN,  $^{23,32}$  NbN $^{33}$  and NbTiN,  $^{34}$  carbides like W-C,  $^{35}$  and non-centrosymmetric Ss like Nb<sub>0.18</sub>Re<sub>0.82</sub> (NbRe).  $^{36}$  In only two studies,  $^{27,37}$  an enhancement other than a reduction in  $I_c$  under  $V_G$  application has been observed which, for one of these two cases,  $^{27}$  occurs only for a specific temperature T range.

For completeness, we note that a GCS is a phenomenon commonly observed also in three-terminal S/semiconductor/S devices, where it emerges as result of a control of the charge carrier density in the semiconductor weak link via an applied  $V_{\rm G}$ .  $^{38-42}$  Two-dimensional Ss also reveal a suppression of superconductivity under an applied  $V_{\rm G}$ .

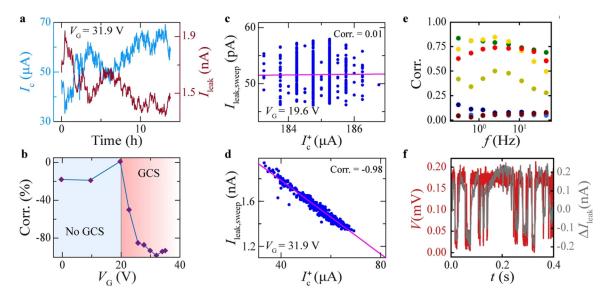

FIG. 1. Phenomenology of gate-controlled supercurrent. Schematic of a superconducting Ti nanowire on  $SiO_2/Si$  with side-gate electrodes for gate voltage  $V_G$  application (a), with corresponding current vs voltage I(V) characteristic measured at  $V_G = 0$  (b) and at a few other positive and negative  $V_G$  values indicated on top of each I(V) characteristic (c), for which a progressive reduction in the critical current  $I_C$  is observed as  $V_G$  is increased. (d)  $I_C$  vs  $V_G$  characteristics measured at different temperatures  $T_S$  (indicated next to each curve) showing that, independently on  $T_C$  is gets progressively reduced as  $I_C$  overcomes a certain threshold  $V_G$  onset, until it becomes fully suppressed at an even higher value ( $V_{G,OffSec}$ ). (e) Possible circuit consisting of a gated superconducting device (represented with a colored symbol), with logic state defined by the voltage drop ( $V_{Out}$ ) on a load resistor  $T_C$  one top of horizonal axis in panel (d). Panels from (a) to (d) are adapted with permission from De Simoni et aI, Nat. Nanotechnol. 13, 802–805 (2018). Copyright 2018 Springer Nature.

due to a modulation in their charge carrier density.  $^{43,44}$  In this review article, however, we focus on gated devices made entirely of metallic Ss, which have high electron density and short Thomas–Fermi screening length. In these materials, the  $V_{\rm G}$ -induced control of superconductivity based on the tuning of charge carrier density does not apply.

Since the metallic Ss investigated to date have different structural properties (e.g., different average grain size and degree of crystallinity) and different superconducting properties ranging from higher critical temperature ( $T_c$ ) and shorter superconducting coherence length ( $\xi_S$ ) for Ss like NbN to lower  $T_c$  and longer  $\xi_S$  for Ss like Al, it may be inferred that a GCS can be observed independently on the metallic S used in a gated superconducting device. Nonetheless, even when the same S material is used, the S growth and/or the device fabrication process can determine whether a GCS is observed or not, <sup>36</sup> as well as affect the GCS device performance (e.g., the  $V_{G, offset}$  of the device), as further discussed in Sec. IV A.

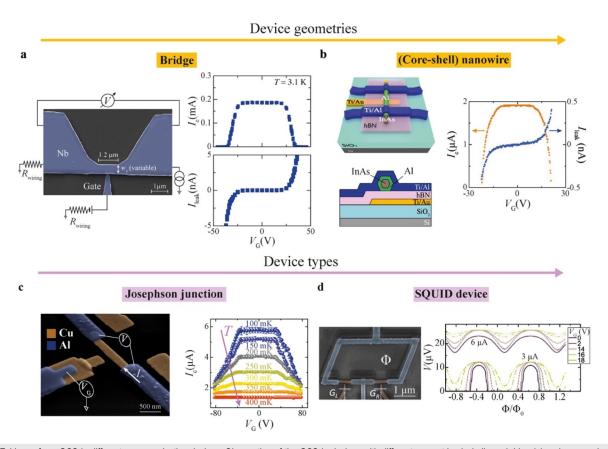

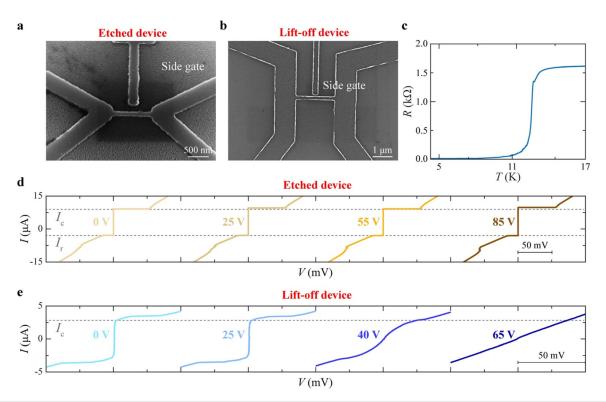

Figures 2(a)–2(d) also show that the GCS can be observed in devices with different geometries ranging from superconducting nanowires,  $^{12,23,32}$  also with a core–shell structure  $^{14,16,31}$  meaning made of a S core grown onto a semiconducting shell [Fig. 2(b)], to Dayem bridges (see Box 1) having widths  $(w_S)$  of few hundreds of nanometers,  $^{15,17,19,21,25,26}$  to wider bridges with  $w_S$  of several hundreds of nanometers.

The experiments performed to date show that there exist several other experimental features that are quite reproducible across devices supporting a GCS, which can be therefore regarded as "universal signatures" of a GCS. As discussed in Sec. I, the GCS is mainly independent of the  $V_{\rm G}$  polarity, meaning that the  $I_{\rm c}$  suppression is approximately the same for a given  $|V_{\rm G}| > V_{\rm G,offset}$  as also shown by  $I_{\rm c}(V_{\rm G})$  characteristics at a certain  $V_{\rm G}$  for opposite polarities in Figs. 1 and 2. This holds true for various device realizations and gate geometries including tip-shaped 15,17,21,26 or planar 16,19,22-24 side gates, back gates, 12,14 top gates, 27,28 and top gate with ionic liquid. However, small asymmetries of the order of a few percent in  $V_{\rm G,offset}$  (at opposite  $V_{\rm G}$  polarity) have been reported by several groups 14,17,22 [see also representative asymmetric  $I_{\rm c}(V_{\rm G})$  curve in supplementary material Fig. 1]. Such small asymmetries become more pronounced when non-insulating substrates like Si are used, 32 although these effects are most likely due to an asymmetric response of the substrate dependent on  $V_{\rm G}$  polarity (see also discussion below).

Another main feature of the GCS is its robustness against T and applied magnetic field (B), meaning that  $V_{\rm G,offset}$  does usually not change as a function of T or B.  $^{12,14,17,19,21-23,26-28,31,33,35,36,46}$  The T-independence of the GCS is evident from the  $I_{\rm c}(V_{\rm G})$  curves measured as a function of T (for B=0) that are shown in Figs. 1(d) and 2(c). These  $I_{\rm c}(V_{\rm G})$  curves show that, although  $I_{\rm c0}$  gets reduced in amplitude as T approaches  $T_{\rm c}$  due to the weakening of superconductivity,  $V_{\rm G,offset}$  remains approximately the same independently on T. A similar behavior is also observed when the  $I_{\rm c}(V_{\rm G})$  characteristics are measured as a function of B (at fixed T), for B approaching the upper critical field of the S (Box 1).

**FIG. 2.** Evidence for a GCS in different superconducting devices. Observation of the GCS in devices with different geometries including a bridge (a) and a nanowire (b) with device schematic shown in the left section of each panel, and critical current  $I_c$  vs applied gate voltage  $V_G$ ,  $I_c(V_G)$ , and leakage current  $I_{leak}$  vs  $V_G$ ,  $I_{leak}(V_G)$ , curves shown in the right section of each panel. Panel (a) is reproduced with permission from Ruf *et al.*, ACS Nano **18**, 20600 (2024). Copyright 2024 Authors, licensed under a Creative Commons Attribution (CC BY) license. Panel (b) is reproduced with permission from Elalaily *et al.*, Nano Lett. **21**, 9684–9690 (2021). Copyright 2021 Authors, licensed under a CC BY license. (c) GCS in an Al/Cu/Al JJ (left panel) and corresponding  $I_c(V_G)$  curves measured at different temperature T (right panel). Reproduced with permission from De Simoni *et al.*, ACS Nano **13**, 7871–7876 (2019). Copyright 2019 American Chemical Society. (d) GCS devices inside an interferometer with a superconducting quantum interference device (SQUID) geometry (left panel) and corresponding voltage vs flux Φ (normalized to the flux quantum Φ<sub>0</sub>), V(Φ/Φ<sub>0</sub>), curve (right panel) measured under current bias exceeding the critical current  $I_c$  of the SQUID of 6  $\mu$ A (top curves) and at current bias of 3  $\mu$ A <  $I_c$  (bottom curves) for different applied  $V_G$  (applied to the right gate electrode of the interferometer), with  $V_G$  values labeled in the panel legend. Reproduced with permission from De Simoni *et al.*, ACS Appl. Electron. Mater. **3**, 3927–3935 (2021). Copyright 2021 Authors, licensed under a CC BY license.

The experiments performed to date also show that, upon  $V_{\rm G}$  application, a finite leakage ( $I_{\rm leak}$ ) current is always measured between the gate electrode and the electrical ground [to which one of the device terminals is also connected; Fig. 2(a)]. Although it is often difficult to quantify the exact amount of the  $I_{\rm leak}$  that flows in the S constriction (other than along a different substrate path that does not involve the S constriction) and despite a large variation in the magnitude of  $I_{\rm leak}$  has been reported across the devices made by different groups (see discussion in Sec. IV),  $I_{\rm leak}$  is present in devices with a side-gate or top-gate geometry where a dielectric connects the gate electrode to the S constriction. For this reason, the presence of a non-null  $I_{\rm leak}$  (independently on its magnitude) concurrent with a  $V_{\rm G}$  application can be considered as another typical characteristic of the GCS.

Apart from the above features, which are common to all studies reported to date, there are several other features, which vary depending on the specific study considered, and which can be hence not considered as universal characteristics of the GCS.

Earlier studies, for example, suggested that a  $w_S$  of the same order of magnitude as  $\xi_S$  is needed for a GCS to be observed, which is the reason why side-gated devices consisting of narrow S constrictions (i.e., with  $w_S$  typically up to  $\sim 200 \,\mathrm{nm}$ ) have been mostly studied. However, Ruf and coworkers have recently shown<sup>29</sup> that a GCS can also be observed in devices with  $w_S \gg \xi_S$ . In their study,<sup>29</sup> the authors have also not been able to define an upper limit for  $w_S$  or even to observe a progressive decrease in  $V_{G,offset}$  as  $w_S$  gets larger. This observation is consistent with the earlier results of Ref. 12, where the authors have fabricated a series of electrodes placed at increasing distance over an elongated wire (parallel to the direction of the side gate) and found that the GCS vanishes over a length scale, which is not of the same order of magnitude as  $\xi_S$  but rather comparable to the London magnetic penetration depth  $\lambda_{\rm L}$  (> 700 nm for Ti used as S in Ref. 12). For a S,  $\lambda_L$  defines the decay length of the exponential suppression that an applied electrostatic field experiences inside S, according to London theory.4

A small separation of the gate electrode from the S constriction ( $d_{\rm gate}$ ) seems important for a GCS to be observed. Most of the experiments performed to date have been realized with  $d_{\rm gate}$  < 100 nm, <sup>15,17,23,24,26</sup> although the GCS has been also observed in devices with much larger  $d_{\rm gate}$ . <sup>36</sup> Also, it has been observed that parameters like  $V_{\rm G,offset}$  do not get reduced as  $d_{\rm gate}$  is reduced, even in the same device with two side gates placed at different  $d_{\rm gate}$  from the S constriction. <sup>31</sup> Therefore, although statistically one can say that a smaller  $d_{\rm gate}$  is preferrable for a GCS to be observed, this cannot be considered as a strict requirement and therefore as a feature universal to all devices showing a GCS.

The last feature of the GCS proposed by earlier studies is its independence on the substrate choice.  $^{12}$  In these studies, it has indeed been shown that, once a certain device geometry and S material are fixed, the GCS can be observed on different types of insulating substrates (e.g.,  $\rm Al_2O_3$  and  $\rm SiO_2$ ). Nonetheless, recent experiments  $^{16,29}$  have clearly shown that the substrate can significantly affect the device performance because the applied  $V_{\rm G}$  can induce stress in the substrate itself, which can in turn shift the  $V_{\rm G, offset}$  of the device and its working point over time.  $^{16,29}$

A list of the features typical of the GCS and discussed in this section is provided in Table I. This list can possibly serve also as a reference for future studies on the GCS, to help confirm that the observation of a GCS is in line with previous reports.

# A. Integration of GCS devices into more complex device structures

The versality in the type of Ss and geometry of the devices supporting a GCS (Fig. 2) also suggests that GCS devices can be integrated into more complex superconducting devices and used as a knob to achieve tunability in their functionality.

To date, the GCS has been not only reproduced in S/N/S Josephson junctions (JJs), where  $V_{\rm G}$  is applied to the N weak link to modulate the  $I_{\rm c}$  of the JJ as shown in Fig. 2(c),  $^{46,50}$  but also in more complex devices embedding a three-terminal GCS device into their layout such as superconducting resonators,  $^{13,18,30}$  and interferometers with a superconducting quantum interference device (SQUID) geometry.  $^{20,47}$

In the case of superconducting resonators, the integration of a GCS device as a  $V_{\rm G}$ -tunable element results in the possibility of tuning the resonant frequency  $f_0$  of the resonator under  $V_{\rm G}$  application. This shift can be helpful to match the resonant frequency of other elements

TABLE I. List of experimental observations that are common to GCS devices.

| Experimental observation                                        | Typical of GCS           |

|-----------------------------------------------------------------|--------------------------|

| $I_{\rm c}$ suppression independent on $V_{\rm G}$ polarity     | YES                      |

| $V_{G,offset}$ mainly independent on $T$ and $B$                | YES                      |

| Non-null $I_{\text{leak}}$ present under applied $V_{\text{G}}$ | YES                      |

| Substrate has little effects on $V_{G,offset}$ and              | NO                       |

| other device parameters                                         |                          |

| Small device width $w_S$                                        | NO                       |

| (i.e., comparable to $\xi_S$ ) needed                           |                          |

| Small gate-to-channel separation $d_{ m gate}$                  | YES/NO                   |

| needed                                                          | (smaller usually better) |

like, for example, superconducting qubits coupled to the resonator for their readout (see Sec. V). Nonetheless, in resonators embedding a GCS element, the shift in  $f_0$  occurs alongside with a reduction in the quality factor Q, which corresponds to a decrease in the resonator performance. From a more technical point of view, this observation also suggests that the GCS device induces a change in the kinetic inductance of the resonator with the appearance of a real part in its impedance. <sup>13,18</sup> Y. Ryu and co-workers have suggested that the tuning of the  $f_0$  of a superconducting resonator achieved with the insertion of a GCS device can be exploited with a tool to match  $f_0$  to the frequency of excitations like phonons or magnons that are usually not tunable and/or difficult to exactly match due to possible imperfections occurring in the fabrication process of a resonator with a desired  $f_0$ . <sup>51</sup>

For SQUIDs, which are the devices most used for ultrasensitive magnetometry,<sup>52</sup> the integration of a GCS device into a SQUID leads to a  $V_G$ -enabled tunability in the voltage vs flux,  $V(\Phi)$ , characteristic of the SQUID.47 This change is different, for example, compared to that obtained by injecting a current above the  $I_c$  of the SQUID. In the latter case, the SQUID operates in the fully dissipative regime and a nonnull voltage is developed at its terminal independently on  $\Phi$ . The difference between the maximum and minimum of  $V(\Phi)$ , which is in turn related to the SQUID sensitivity, is fixed in this regime [Fig. 2(d); top]. When a  $V_G$  is instead applied and the  $I_c$  of the SQUID is reduced, it is possible to operate the SQUID in a regime where the maximum in  $V(\Phi)$  is the same as in the resistive state, while the minimum in  $V(\Phi)$ can be modulated (from zero to non-zero values) through  $V_G$ , meaning that the device can be still partially operated in the superconducting state (depending on  $V_G$ ), where it has a different response to the external  $\Phi$  [Fig. 2(d); bottom]. The integration of a GCS device in a SQUID therefore provides an additional knob, for example, when it is necessary to operate the SQUID over a wider  $\Phi$  dynamic range, without reducing the overall change in voltage and in turn the SQUID sensitivity.4

#### III. PHYSICAL MECHANISMS PROPOSED FOR THE GCS

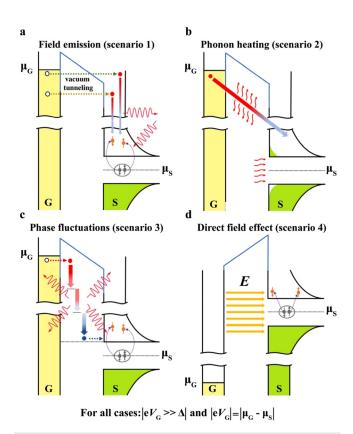

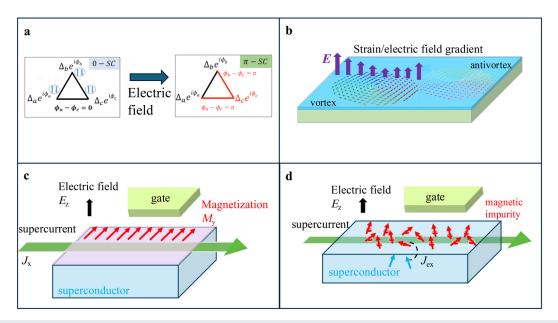

The microscopic mechanism underlying a GCS in devices based on a metallic S remains under debate. The various mechanisms suggested to date to explain the GCS are those illustrated in Fig. 3, which we categorize as follows:

- (1) emission of high-energy electrons through vacuum, relaxing into phonons and/or quasiparticles in the S, labeled in this review as "field emission"; 18,23,24,28,53

- (2) phonon-induced heating of the electronic system due to injection of charges into the substrate and/or into the S that can lead to an increase in the local bath temperature, in short referred to as "phonon heating"; 13,14,23,32,36

- (3) phase fluctuations in the S associated with an out-of-equilibrium state induced by phonons and/or high-energy electrons injected into the substrate and/or into the S, but without sizable heating of the electronic system, in short "phase fluctuations";<sup>14,16,29,31-33,50</sup>

- (4) another effect driven by the electric field associated with the applied  $V_{\rm G}$ , henceforth called "direct field effect." 12,15,17,19–22,25–27,35,36,46,47

We note that the borders between some of the above categories are not easy to trace. Furthermore, the assignment of a given manuscript into one of these four main categories is not exclusive, since the authors in some cases do not specify a single scenario active in their

**FIG. 3.** Mechanisms proposed for the GCS. Illustration of physical mechanisms proposed to explain GCS based on band diagrams of gate (G) and superconductor (S) separated by an insulator under an applied  $V_{\rm G}$  shifting their corresponding chemical potentials ( $\mu_{\rm S}$  for S and  $\mu_{\rm G}$  for G). The mechanisms include (a) tunneling across vacuum of high-energy electrons between G and S relaxing into phonons (wavy arrows) and/or quasiparticles (orange dots) in S, (b) phonon heating (red arrows) populating quasiparticle states in S, (c) phase fluctuations induced by phonons triggered by high-energy electrons flowing between G and S, and (d) *E*-field induced distortions of the superconducting phase like, for example, breaking of Cooper pairs (gray ellipses) into quasiparticles.

study, or the responsible mechanism was not yet identified at the publication date, or even several mechanisms may be at play simultaneously.

Scenario 1 explains the GCS as the result of the field emission<sup>54</sup> or direct tunneling of high-energy electrons from the gate electrode into the S nanoconstriction across vacuum (or vice versa for opposite  $V_{\rm G}$  polarity). The hot electrons injected into the S would then relax as phonons or quasiparticles inside the S, thus heating up the electronic system and hereby leading to the GCS [Fig. 3(a)]. We note that in this scenario an  $I_{\rm leak}$  tunnels across vacuum from the gate electrode into the S nanoconstriction.

The mechanisms proposed under scenarios 2 and 3 are also both triggered by  $I_{\rm leak}$ . However, these are not related to vacuum tunneling, but rather to charge carriers that propagate via the substrate and thereby lose energy and excite phonons [Figs. 3(b) and 3(c)]. The energy of the leaking charge carriers when they arrive at the S would hence be smaller on average than in scenario 1, and the phonons would be mostly created inside the substrate.

In the case of scenario 2, the electronic system of the S would again be heated up because it is in contact with the warmer phonon bath, resulting in a non-equilibrium occupation of the quasiparticle system that can be described by an increased electronic temperature. According to scenario 3 instead, the superconducting condensate would be disturbed and brought into a non-equilibrium state, where the quasiparticle distribution cannot be described with an effective temperature matching that of the bath temperature.

The difference between scenarios 1 and 2 is subtle, since scenario 1 can also include heating by phonons. However, since the energy of the charge carriers is different and the position of their decay and heat release is different, also the phenomenology related to each of these scenarios is different. Since the spatial position of charge carrier relaxation in the two scenarios is different, a way to distinguish between scenarios 1 and 2 is by the  $V_G$  polarity dependence of the  $I_c$  suppression. While in scenario 1 an asymmetric suppression is expected, scenario 2 should give rise to a symmetric suppression. Also, the distinction between scenario 2 and 3 is often not easy to make and might just be quantitative. Experiments on devices supporting scenario 3 (see below) clearly show a GCS, but no substantial increase in the electronic T, despite showing similar parameters ( $I_c$ ,  $V_{G,offset}$ ) to those measured for devices categorized under scenario 2. Because of these subtle differences, scenarios from 1 to 3 are often referred to collectively as "leakage effects."

In contrast to the first three scenarios, scenario 4 assumes an electrostatic field effect, which can induce a GCS even in the absence of charge transfer between the S and the gate [Fig. 3(d)], i.e., without  $I_{\rm leak}$ . Proving this scenario experimentally requires at first place ruling out scenarios 1–3, i.e., increasing the gate isolation so that the impact of  $I_{\rm lesk}$  can be excluded. Strictly speaking, this task cannot be fulfilled, as long as scenarios 1–3 and the  $I_{\rm leak}$  level required for them to be at play are not clear, since there will always be a non-vanishing  $I_{\rm leak}$  associated with  $V_{\rm G}$ , unless the resistance between the gate and the S channel increases to an unphysically infinite value.

One important message of this review is that none of these four scenarios covers the multitude of the reported phenomena. Instead, the dominating mechanism varies across experiments. In particular, we will explain that, although the majority of the experiments reported by different groups other than by single groups might fall into scenarios 2 and 3, neither scenario 1 nor scenario 4 can be fully ruled out to be at the origin of the individual experimental findings reported to date.

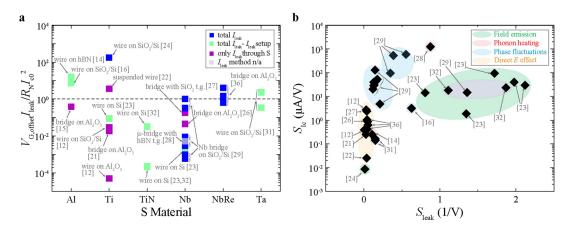

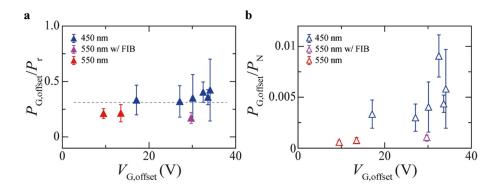

In Table II, we have listed the studies on the GCS reported to date with the corresponding parameters (specified below) and grouped them according to the scenario proposed to explain the GCS observation, using differently colored boxes to identify each mechanism. The boxes overlap for those studies where more than a single mechanism can be identified or where the mechanism cannot be clearly identified. Evidence for a specific mechanism often stems from specific measurements, which have not been reproduced by other groups. For each study in Table II, we list the material parameters (i.e., type of S and substrate), the main steps of the fabrication process used, and other parameters measured by characterizing the device for the GCS (i.e.,  $V_{G,\text{onset}}$ ,  $V_{G,\text{offset}}$ , and the corresponding  $I_{\text{leak}}$  at these two  $V_{G}$  values),  $d_{\text{gate}}$  and the gate type, the ratio between the power dissipated by the gate at  $V_{G,offset}$  (i.e.,  $P_{G,offset}$ ) and the power dissipated by the device when in the normal state  $P_N$ . The relevance of these parameters is discussed in more details in Sec. IV.

15 November 2024 09:22:50

**Applied Physics Reviews**

**TABLE II.** Experimental parameters of studies on the GCS grouped based on the physical mechanism proposed. Studies where the possible mechanism is specified by the authors are listed in a single shaded colored box, whereas studies for which the mechanism at place is not exactly specified are listed within more than one box. For parameters depending on temperature, the values reported are those measured at the base temperature of the setup (typically between 5 and ~110 mK), unless otherwise specified (see more detailed table in the supplementary material).

| Proposed<br>mechanism | S type, thickness<br>(nm)<br>and geometry                                     | Substrate                      | Fab. process                              | $V_{ m G,onset}$ (Volts) | $V_{G,offset}$ (Volts) | $I_{ m leak}$ @ $V_{ m G,onset}$ $({ m pA})$        | $I_{ m leak}$ @ $V_{ m G,offset}$ $({ m pA})$ | $d_{ m Gate}$ (nm), type          | $P_{ m G,offset}/P_{ m N}$ | Ref. |

|-----------------------|-------------------------------------------------------------------------------|--------------------------------|-------------------------------------------|--------------------------|------------------------|-----------------------------------------------------|-----------------------------------------------|-----------------------------------|----------------------------|------|

|                       | V(30) bridge in resonator                                                     | SiO <sub>2</sub> /Si           | EBL, Cl <sub>2</sub> , dry etching        | > 25                     | n/a                    | ~10                                                 | n/a                                           | $\sim$ 100 (pointy, on 2 sides)   | n/a                        | 18   |

|                       | Ti (30) nanowire                                                              | SiO <sub>2</sub> /Si           | EBL, evap., lift off                      | ~ 27                     | ~37                    | ~70                                                 | $\sim$ 98                                     | $\sim$ 70 (round, 2 on same side) | $1.84\times10^{2}$         | 24   |

|                       | TiN (20) nanowire                                                             | Si                             | EBL, HBr<br>etching                       | 2.6                      | 5.5                    | ~ 0.67                                              | $\sim$ 1.37 $\times$ 10 $^2$                  | > 80 (narrow flat, on 2 sides)    | $2.27 \times 10^{-4}$      |      |

| Field                 | TiN (20) nanowire                                                             | Si                             | EBL, HBr<br>etching                       | 1.9 ÷ 2.3                | ~ 3.3                  | $0.5 \div 0.6$                                      | $(0.7 \div 4.4) \times 10^2$                  | 80, 160 (wide flat, on 2 sides)   | n/a                        | _ 22 |

| emission              | Nb (13.5) nanowire                                                            | Si                             | EBL, Ar/Cl <sub>2</sub> etching           | 2.4                      | 4.2                    | ~ 6.21                                              | $8.32 \times 10^{3}$                          | 80 (flat, on 2 sides)             | $1.5 \times 10^{-3}$       | - 23 |

|                       | Ti (30) nanowire                                                              | Si                             | EBL, evap., lift off                      | 1.0                      | 2.6                    | ~ 0.2                                               | ~26.6                                         | 80 (flat, on 2 sides)             | $8.9 \times 10^{-2}$       |      |

|                       | Au(3 – 5)/Nb(3 – 5)<br>with scanning<br>tunneling micro-<br>scope (STM) setup | Si/SiO <sub>2</sub>            | EBL, etching, evap.                       | n/a                      | n/a                    | Varying<br>(equal to injected<br>tunneling current) |                                               | n/a (STM tip-<br>to-sample gap)   | n/a                        | 53   |

|                       | Al (30) strip in Nb<br>resonator                                              | Si                             | EBL, evap., lift off                      | n/a                      | n/a                    |                                                     | < 10 <sup>5</sup> for<br>le effects           | $\sim$ 80 (flat, 3 on 1 side)     | n/a                        | 13   |

| Phonon<br>heating     | Al (20)/InAs<br>nanowire                                                      | hBN/SiO <sub>2</sub>           | EBL, evap., lift off                      | 14.1                     | 20.8                   | $\sim$ 74.2                                         | ~ 388                                         | $\sim$ 20 (back gate)             | 16.4                       | 14   |

|                       | Au(2)/Nb(10)<br>(bridge) w/ Nb/<br>hBN top gate                               | $Al_2O_3$                      | EBL, sputt., lift<br>off, hBN<br>transfer | 1.02                     | 2.35                   | $\sim$ 4.6 $\times$ 10 $^4$                         | $\sim$ 6.7 $\times$ 10 $^{5}$                 | Nb/hBN (6)<br>(top gate)          | $5.3 \times 10^{-3}$       | 28   |

|                       | NbRe (20) Dayem<br>bridge                                                     | Al <sub>2</sub> O <sub>3</sub> | EBL, Ar/Cl <sub>2</sub> etching           | ~41                      | 65.7                   | ~ 530                                               | $\sim$ 6.6 $\times$ 10 <sup>3</sup>           | $\sim$ 291 (pointy, on 1 side)    | 4.05                       | 36   |

**Applied Physics Reviews**

### TABLE II. (Continued.)

| Proposed<br>mechanism | S type, thickness<br>(nm)<br>and geometry | Substrate                                               | Fab. process               | $V_{ m G,onset}$ (Volts) | $V_{G,offset}$ (Volts) | $I_{ m leak}$ @ $V_{ m G,onset}$ $({ m pA})$ | $I_{ m leak} @ \ V_{ m G,offset} \ ( m pA)$ | $d_{ m Gate}$ (nm), type                                       | $P_{ m G,offset}/P_{ m N}$                    | Ref. |

|-----------------------|-------------------------------------------|---------------------------------------------------------|----------------------------|--------------------------|------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|------|

|                       | TiN (20) nanowire                         | Si                                                      | EBL, HBr<br>etching        | 3.9 ÷ 5.6                | 6.1 ÷ 7.4              | 0.4 ÷ 9.4                                    | $(0.1 \div 16) \times 10^3$                 | 80 (1 flat, 1 side)<br>and 10 <sup>3</sup> (2 flat, 1<br>side) | $2.05 \times 10^{-4} \div 3.3 \times 10^{-2}$ | . 32 |

|                       | Ta (20) /InAs<br>nanowire                 | SiO <sub>2</sub> /Si                                    | EBL, evap., lift<br>off    | 5.1 ÷ 6.3                | 11.4 ÷ 13.9            | 2 ÷ 25                                       | $(0.2 \div 2.2) \times 10^2$                | 65, 115 (2 opposite sides)                                     | $3.49 \times 10^{-1} \div 2.37$               | 31   |

| Phase                 | Al/Cu(45)/Al<br>junction                  | SiO <sub>2</sub> /Si                                    | EBL, evap., lift off       | ~ 5.6                    | n/a                    | $\sim 1.2 \times 10^{-2}$                    | $\sim$ 2.9 @10 V                            | $\sim$ 50 (wide, T-shape, one side)                            | n/a                                           | 50   |

| fluctuations          | Al (20)/InAs<br>nanowire                  | SiO <sub>2</sub> /Si                                    | EBL, evap., lift           | 4.43                     | 6.25                   | 275                                          | $3.8\times10^3$                             | 50, 70 (2 flat, on opposite sides)                             | 7.36                                          | 16   |

|                       | NbN (6) nanowire                          | Si                                                      | Sputt., EBL,<br>etching    | ~1.67                    | 4.2                    | n/a                                          | $14.8 \times 10^{3}$                        | 100 ÷ 300 (several types)                                      | n/a                                           | 33   |

|                       | Nb (27) bridge                            | SiO <sub>2</sub> /Si                                    | EBL, sputter.,<br>lift off | $0.85 \div 28.5$         | 1.6 ÷ 37               | $(0.07 \div 1.4) \times 10^3$                | $(0.9 \div 25.3) \times 10^3$               | 50 ÷ 100 (one,<br>on 1 side)                                   | $5.92 \times 10^{-4} \div 1.03$               | 29   |

|                       | Ti (30) nanowires                         | SiO <sub>2</sub> /Si,<br>Al <sub>2</sub> O <sub>3</sub> | EBL, evap., lift<br>off    | 16.6 ÷ 26.2              | 26 ÷ 53                | 0.004 ÷ 21                                   | $0.006 \div 41$                             | < 100 (flat, on 2 sides)                                       | $4.9 \times 10^{-5} \div 3.0 \times 10^{-2}$  | 12   |

|                       | Al (11) nanowire                          | SiO <sub>2</sub> /Si<br>(doped)                         | EBL, evap., lift           | ~ 38                     | n/a                    | not re                                       | eported                                     | 300 (back gate)                                                | n/a                                           | 12   |

|                       | Al/Cu (30)/Al<br>junction                 | SiO <sub>2</sub> /Si                                    | EBL, evap., lift off       | 37 ÷ 43                  | n/a                    | ~ 22                                         | n/a                                         | < 100 (flat, on 1 side)                                        | n/a                                           | 47   |

| Direct E effect       | Ti (30) Dayem<br>bridge                   | SiO <sub>2</sub> /Si                                    | EBL, evap., lift off       | ~17                      | ~ 28                   | not re                                       | eported                                     | 80 ÷ 120<br>(round, on 2<br>sides)                             | n/a                                           | 19   |

|                       | Ti (30)<br>interferometer                 | SiO <sub>2</sub> /Si                                    | EBL, evap., lift           | $8.9 \div 40.6$          | n/a                    | $\sim$ 10.6 (for 1 gate)                     | n/a                                         | 30 ÷ 50 (pointy,<br>2 same side)                               | n/a                                           | 20   |

|                       | Nb (40) Dayem<br>bridge                   | $Al_2O_3$                                               | EBL, evap., lift off       | ~13                      | $\sim$ 44              | ~ 0.8                                        | > 30                                        | 70 (pointy, on 1 side)                                         | $4.6 \times 10^{-2}$                          | 26   |

|                       | V (60) Dayem<br>bridge                    | SiO <sub>2</sub> /Si                                    | EBL, evap., lift off       | ~5                       | ~8                     | not re                                       | eported                                     | 70 (pointy, on 1 side)                                         | n/a                                           | 17   |

|                       | Ti (30) Dayem<br>bridge                   | $Al_2O_3$                                               | EBL, evap., lift off       | ~12.7                    | ~ 34.3                 | 2.94                                         | 11.3                                        | 80 (pointy, on 1 side)                                         | $1.89 \times 10^{-2}$                         | 21   |

**Applied Physics Reviews**

## TABLE II. (Continued.)

| Proposed<br>mechanism         | S type, thickness<br>(nm)<br>and geometry | Substrate            | Fab. process                                                 | $V_{ m G,onset} \  m (Volts)$      | $V_{G,offset}$ (Volts) | $I_{ m leak}$ @ $V_{ m G,onset}$ $({ m pA})$ | $I_{ m leak}$ @ $V_{ m G,offset}$ $({ m pA})$ | $d_{\mathrm{Gate}}$ (nm),<br>type                                 | $P_{ m G,offset}/$ $P_{ m N}$ | Ref.            |

|-------------------------------|-------------------------------------------|----------------------|--------------------------------------------------------------|------------------------------------|------------------------|----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------|-------------------------------|-----------------|

|                               | Ti (70) nanowire<br>(suspended)           | n/a                  | 3 EBL steps,<br>evap.                                        | ~11.0                              | ~17.5                  | 1                                            | 1.7                                           | 40 (flat, on 2 sides)                                             | 3.67                          | 22              |

|                               | Al (14) Dayem<br>bridge                   | $Al_2O_3$            | EBL, evap., lift off                                         | ~13.8                              | ~ 22.7                 | n/a                                          | < 70                                          | 30 (pointy, on 1 side)                                            | $3.8 \times 10^{-1}$          | 15              |

|                               | Al/Cu(30)/Al<br>interferometer            | SiO <sub>2</sub> /Si | EBL, evap., lift off                                         | 14 ÷ 46                            | n/a                    | < 1                                          | n/a                                           | $45 \div 60$ (round, 2 same side)                                 | n/a                           | 47              |

|                               | Nb (50) Dayem<br>bridge                   | $Al_2O_3$            | EBL, sputter.,<br>lift off or sput-<br>ter.,<br>EBL, etching | > 1 for lift off<br>> 5 for etched | n/a                    | n/a                                          | n/a                                           | $\sim$ 1 $	imes$ 10 $^5$ (to gate electrode)  Ionic liquid gating | n/a                           | 25              |

|                               | W-C (45) nanowire                         | SiO <sub>2</sub> /Si | EBL, evap. FIB                                               | ~1.5                               | ~3                     | n/a                                          | n/a                                           | 200 (flat, on 2 sides)                                            | n/a                           | 35              |

|                               | NbRe (20) Dayem<br>bridge                 | $Al_2O_3$            | EBL, Ar/Cl <sub>2</sub> etching                              | ~ 30 ÷ 41                          | ~53.7 ÷ 62             | $ \sim 2 \times 10^2  \div 2.3 \times 10^3 $ | $\sim 2.8 \times 10^3 \div 2.3 \times 10^4$   | $\sim$ 312 $\div$ 321 (pointy, on 1 side)                         | $0.64 \div 7.46$              | 36              |

|                               | 3D Nb (12) Dayem<br>bridge                | SiO <sub>2</sub> /Si | EBL steps w/<br>sputter. and lift<br>off                     | 15.3 ÷ 36.6                        | 22.0 ÷ 53              | n/a                                          | $\sim 10^2$ (for gate at 130 nm)              | $\sim 130 \div 165$<br>(top gate w/ $SiO_2$ )                     | $\sim 1.78 \times 10^{-1}$    | <sup>1</sup> 27 |

| Increase in $I_c$ under $V_G$ | NbN (7–10) nano-<br>wire                  | SiO <sub>2</sub> /Si | Sputter., EBL,<br>Ar <sup>+</sup> milling                    | n/a                                | n/a                    | < 10 <sup>3</sup> (u <sub>2</sub>            | p to 80 V)                                    | 300 (back gate)                                                   | SiO <sub>2</sub> /Si n/a      | 37              |

For the experimental device parameters, we have also adopted common criteria to extract them identically from all studies (see Fig. S1 in the supplementary material). A more detailed table with additional details on the device geometry (i.e., channel length and width), other experimental parameters (e.g.,  $I_{c0}R_N$  product), and comments on the main findings from the authors is also reported in the supplementary material.

# A. Tunneling of high-energy electrons through vacuum (field emission)

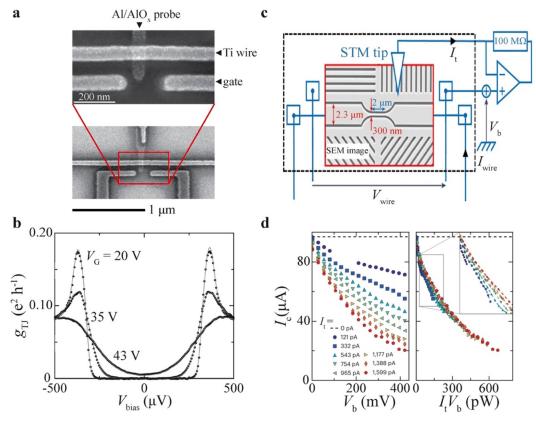

Field emission (i.e., scenario 1) has been suggested by Alegria and coworkers based on measurements of the superconducting density of states (DoS) of a S nanoconstriction (made of Ti) under an applied  $V_G$ . To probe the DoS of a S using a tunneling device, it is necessary to fabricate a tunnel junction on top of the S of interest, which consists of an insulating layer with a N or S electrode on top of it. In the case of Ref. 24, the authors have used  $AlO_x$  as insulator with an Al (S) electrode on top, to fabricate the tunnel device on the Ti nanoconstriction [Fig. 4(a)].

The reason for choosing tunneling spectroscopy in Ref. 24 to study the mechanism underlying the GCS is due to the fact that tunneling spectroscopy is a well-established technique to study how different effects such as proximity effects with a different material coupled to a S (e.g., a magnetic material) or phonons—the latter can be relevant as already discussed in GCS devices—affect superconductivity inside the S material. All these effects in fact lead to changes in the non-linear DoS of the S, which is proportional to the differential conductance  $g_{TJ} = dI_{TJ}/dV_{\rm bias}$ , where  $I_{TJ}$  is the current measured through the tunnel junction, while  $V_{\rm bias}$  is the bias voltage applied between the tunnel probe and the S layer.

By probing the DoS by spectroscopy with a tunneling device, in Ref. 24, the authors have shown that the DoS broadens as  $V_{\rm G}$  is increased [Fig. 4(b)]. This effect is ascribed to the tunneling of quasiparticles with very high energy ( $\sim\!eV_{\rm G}\gg\Delta$ ,  $\Delta$  being the superconducting gap energy) into the S, which emit phonons that can excite further quasiparticles until the phonons escape. <sup>56</sup> We note that a similar broadening could also arise in scenario 2, although this was not considered at the time of the study in Ref. 24.

In another experiment performed by Jalabert and co-workers,  $^{53}$  a scanning tunneling microscope (STM) setup has been used to study the GCS in a Nb nanowire [Fig. 4(c)]. Although a STM can be used to

**FIG. 4.** Experimental evidence for tunneling of high-energy electrons. Tunneling device consisting of an Al/AlO<sub>x</sub> probe fabricated on top of a Ti nanowire with lateral gate electrodes to study the evolution of the superconducting density of states (DoS) under an applied  $V_{\rm G}$  (a) and corresponding density of states determined from differential conductance  $g_{\rm TJ}$  measured as a function of the bias voltage  $V_{\rm bias}$  applied between the probe and the Ti nanowire (b). Reproduced with permission from Alegria et al., Nat. Nanotechnol. **16**, 404–408 (2021). Copyright 2021 Springer Nature. Scanning tunneling microscope setup used to inject a tunnel current  $I_{\rm t}$  (at fixed bias voltage  $V_{\rm b}$ ) into a superconducting device (gray area) and determine its effect on the superconducting critical current  $I_{\rm c}$  (measured with a four-probe setup) (c) and dependence of  $I_{\rm c}$  on  $V_{\rm b}$  and on injected power  $I_{\rm t}V_{\rm b}$  (d) for the device shown in (c). Reproduced with permission from Jalabert et al., Nat. Phys. **19**, 956–960 (2023). Copyright 2023 Springer Nature.

measure the tunneling DoS like in Ref. 24 but on a more local scale, in this study,<sup>53</sup> the STM has not used to probe the DoS, but rather as a tool to inject quasiparticles directly from the STM tip into the underlying Nb (S) nanowire across vacuum. The motivation of the authors is that, since no solid-state tunnel junction or dielectric substrate is present in their setup, any contributions to the GCS coming from charges or photons usually excited in these materials can be excluded. As a result, the authors argue that GCS effect, which they manage to reproduce, can be only due the injection of high-energy electron from the STM tip into the Nb nanowire across vacuum. The measurements reported in Ref. 53 also show that, when the energy of the quasiparticles injected e $V_G$  is larger than the S gap energy  $\Delta$ , the  $I_c$  suppression scales with the injected power—which is given by the product of the injected tunneling current  $I_t$  and the bias voltage  $V_b$  applied between the STM tip and the S nanowire [Fig. 4(d)]. Also, the authors find that  $I_c$  is almost unaffected by the injection rate of quasiparticles, which is interpreted as a signature of the quasiparticle relaxation occurring in the first tens of picoseconds after their injection. Within these tens of picoseconds, the injected quasiparticles would relax into phonons. The as-generated phonons would in turn break many Cooper pairs and generate other quasiparticles that eventually thermalize through inelastic electron-phonon and electron-electron interaction.

Other groups, however, give arguments against field emission as the dominating mechanism in their experiments. In some studies, <sup>14</sup>, for example, the authors note that field emission is inconsistent with the symmetric nature of the  $I_c(V_G)$  characteristics, which is observed in most GCS devices (see Sec. II). According to this argument, in case field emission was responsible for the GCS, the  $I_c(V_G)$  curves should be asymmetric, especially when  $V_{\rm G}$  is applied with a single electrode placed only on one side of the S nanoconstriction. As argued in Ref. 14, this is because, while hot electrons tunneling from the gate into the S relax then in S inducing a large number of quasiparticles (and hence a significant heat load), hot electrons pulled from the S into the gate (for opposite  $V_{\rm G}$ ) heat the metal block of the gate electrode, which should in turn have a much smaller effect on S (separated by the gate through the insulator). Finite element simulations reported in Ref. 22 also show that the  $I_c(V_G)$  characteristics cannot be symmetric in the case of field emission, if the device has an asymmetric geometry (i.e., the gate is only placed on one side of the nanoconstriction).

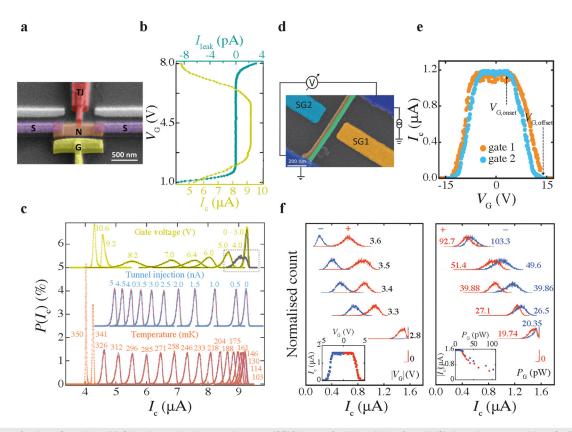

A second argument reported against field emission is based on measurements of switching current distributions (SCDs) reported in Ref. 31. For a superconducting device under  $I_{\text{bias}}$ , measuring the statistics of the current  $(I_c)$  required to switch from the device from a superconducting state (zero-voltage state) to a state of finite voltage is a very informative type of measurement. For a Josephson tunnel device, for example, the dynamics of the transition between the two states is equivalent to the process of escape of a particle from a potential well (tilted washboard potential) to a state where it runs down the potential.<sup>57,58</sup> At high temperature, the process is dominated by thermal activation through the barrier,<sup>59</sup> while at low temperature it is dominated by quantum tunneling through the barrier. 60 The measurement of the SCD in these devices provides information about the escape of the phase inside the junction and whether the dynamics of this phase escape is dominated by thermal activation or by quantum mechanical tunneling.6

In Ref. 31, like in other similar studies of the SCD in superconducting devices, the measurement of the SCD is done by biasing the

device with a certain current I that is ramped at a constant rate, to then measure the current value at which the device switches to a finite voltage state. The process is repeated multiple times, to accumulate many measurements of the switching current and generate a histogram of the probability of switching at a certain I. According to the authors of Ref. 31 field emission should in principle yield SCDs (and also average switching current  $\langle I_c \rangle$ , if this is the only parameter measured) that are asymmetric not only when measured at the same  $V_{\rm G}$  with opposite polarities, but also when measured at the same power dissipated by the gate  $P_G = V_G I_{leak}$  at opposite  $V_G$  polarities. As explained already above, if the S nanoconstriction is grounded and  $V_G$  is measured with respect to ground, for a negative  $V_{\rm G}$ , high-energy electrons are injected from the gate into the S and hence heat the S, while, for opposite (positive)  $V_{\rm G}$ polarity, high-energy electrons are injected from the S into the gate and heat the gate. Under these assumptions, a stronger suppression of superconductivity should be observed, at fixed  $P_G$ , when  $V_G$  is negative. Nonetheless, the SCDs reported in Ref. 31 are symmetric when measured at the same  $P_G$  for opposite  $V_G$  polarities, which is argued to be inconsistent with field emission. It is important to note that the evidence against field emission given in Refs. 14, 22, and 31 does not exclude that this mechanism exists and would be the dominating one as reported in Refs. 18, 23, 24, and 53.

# B. Heating due to phonons excited in the substrate (phonon heating)

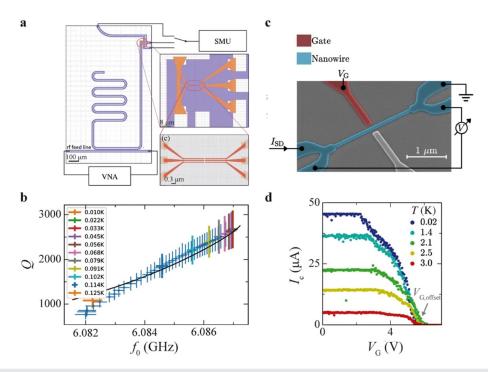

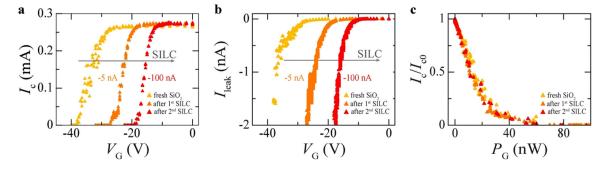

Scenario 2, meaning phonon-mediated heating by charge carriers that leak through the substrate, clearly triggers a GCS and a rise in the sample T, which can be measured concurrently with the application of  $V_G$  like in Ref. 13. The main difference between reports falling under these scenarios compared to scenario 1 or 3, for example, is that the injection of an  $I_{\text{bias}}$  (simulating the effect of  $I_{\text{leak}}$ ), without an applied  $V_G$ , between the gate and the S nanoconstriction produces features that are identical to those that are measured just when increasing the sample T. For example, Catto and coworkers  $^{13}$  have observed that, by recording the quality factor Q and resonant frequency  $f_0$  of their resonators for increasing  $I_{\text{leak}}$  between the gate and an Al strip, they can reproduce the same Q and  $f_0$  obtained by increasing the sample T [Fig. 5(a)]. As a result, the authors conclude that the observed shift in  $f_0$  and Q is not due to any direct field effect (scenario 4).

In general, like in Ref. 13, a good approach to understand whether scenario 2 is that mostly at play in a specific experiment consists in tracking how a certain parameter related to the GCS (i.e., to the suppression of  $I_{\rm c}$ ) evolves for increasing  $V_{\rm G}$  (this in turn corresponds to an increasing  $I_{\rm leak}$ ), and to then compare the evolution of the same parameter with that observed by increasing the device T up to the critical temperature  $T_{\rm c}$  of the device at  $V_{\rm G}=0$ . If the two trends are similar, scenario 2 is most likely the dominant mechanism toward the GCS.

Another experimental signature typically observed for devices falling under scenario 2 is a systematic shift of device parameters (>10%) like  $V_{\rm G,onset}$  or  $V_{\rm G,offset}$  occurring as the T of the sample is increased. This shift has been measured in particular for devices falling under scenario 2, which are made on non-insulating substrates like Si,  $^{23}$  as shown in Fig. 5(d). However, the same behavior has been observed also in other devices, where the gate has poor electrical decoupling (i.e., the gate-to-channel resistance is of hundreds of k $\Omega$  or less) from the S nanoconstriction like for one the devices in Ref. 36, or in devices where lab-grown SiO<sub>2</sub> has been used as dielectric to separate

**FIG. 5.** Experimental evidence for phonon heating. Schematic of a co-planar waveguide resonator made of Nb (purple area) with an Al structure (orange area) used to connect the resonator to the ground plane and to study its response (a) and corresponding quality factor Q vs resonant frequency  $f_0$  measured at base T for different values of the injected current  $I_{leak}$  (blue markers) from 0 to 0.35 μA and at different temperatures as indicated by the colors in the legend (b). The data show that the dependence of Q on  $f_0$  for increasing  $I_{leak}$  is like that measured for increasing T. Reproduced with permission from Catto *et al.*, Sci. Rep. **12**, 6822 (2022). Copyright 2022 Authors, licensed under a CC BY license. Colored scanning electron microscope image of a gated TiN nanowire on Si substrate (c) and corresponding critical current  $I_c$  vs gate voltage  $V_G$  curves measured at different  $T_S$  marked in the legend (d). Except for the  $I_c(V_G)$  curve measured at  $T_S = T_S$  of the  $T_S = T_S$  increased. Reproduced with permission from Ritter *et al.*, Nat. Commun. **12**, 1266 (2021). Copyright 2021 Authors, licensed under a CC BY license.

the gate from the S channel in a top-gate geometry. If the GCS is due to  $I_{\rm leak}$ -induced heating (scenario 2), it is in fact reasonable to expect that, as the sample T gets closer to  $T_{\rm c}$  and superconductivity gets weaker,  $I_{\rm c}$  can be suppressed with a smaller  $I_{\rm leak}$  and hence with a lower  $V_{\rm Goffset}$ -

In other devices made on commercial insulating substrates (possibly with lower density of pinholes) and with good electrical decoupling between gate and S nanoconstriction, scenario 2 has been ruled out, as explained above, by comparing the evolution of SCDs under an applied  $V_{\rm G}$  with that measured for increasing T at  $V_{\rm G}=0$ . In these studies,  $^{21,31,50}$  it has been shown that the  $V_{\rm G}$  application results in much broader SCDs than those measured while increasing the sample T (for the same  $I_{\rm c}$  suppression). For these reasons, a mechanism different from  $I_{\rm leak}$ -induced heating (scenario 2) has been proposed, although phonons are still at play.

To exclude Joule heating related to  $I_{\rm leak}$  as an explanation for the GCS also in devices reported in other studies, we have also calculated the ratio between the power dissipated by the gate ( $P_{\rm G}$ ) at full suppression,  $P_{\rm G,offset} = V_{\rm G,offset}$   $I_{\rm leak}$ ) with the power  $P_{\rm N} = R_{\rm N} \ I_{\rm c0}^{-2}$  that the device dissipates when it switches to the resistive state, for all the studies where these parameters are available. The obtained  $P_{\rm G}$  values shown in Table II suggest that, with a few exceptions,  $^{14,16,22,24}_{\rm G,offset}$  is usually much smaller than  $P_{\rm N}$ , from which one can infer that the contribution from Joule heating may be minimal.

We also note that most of the devices studied to date have hysteretic current-voltage characteristics [see Fig. 1(b)], meaning that the

transition from the superconducting to the normal state occurs at a higher absolute current (the critical current  $I_c$ ) than the reverse transition from the normal back to the superconducting state, which happens at the smaller so-called retrapping current  $(I_r)$ . This means that, for current amplitudes between  $I_r$  and  $I_o$ , the system is in a metastable state. It could be therefore argued that  $I_r$  at  $V_G = 0$  ( $I_{r0}$ ), other than  $I_{c0}$ should be considered when estimating  $P_N$ , which would result in a higher  $P_{G,offset}/P_N$  ratio. Unfortunately, however,  $I_{r0}$  values are not systematically provided. For those works where the  $I_{r0}$  values have been reported, we observe a large variation in the ratio of  $P_{G,offset}$  to  $R_N I_{r0}^2$ across devices, independently on the scenario suggested by the authors. In particular, there are certain studies, mostly supporting scenarios 3 and 4, where  $P_{G,offset}$  is smaller than  $R_N I_{r0}^{2,12,28,32}$  and studies where scenarios from 1 to 4 have been suggested, where  $P_{G,offset}$  is either of the same order but larger<sup>21,23,26,32</sup> or a few order of magnitudes larger than  $R_{\rm N} I_{\rm ro}^{2.14,15,22,31}$  These considerations suggest that, even in devices where relatively low  $I_{leak}$  is measured at  $V_{G,offset}$  (of few pA), it cannot be fully excluded that  $I_{leak}$ -induced Joule heating still plays a role.

# C. Out-of-equilibrium state due to high-energy electrons and/or phonons excited in the substrate (phase fluctuations)

Phase fluctuations (scenario 3) are supported by other studies  $^{29,31,50}$  where, even in the presence of a small  $I_{\rm leak}$  and without

substantial increase in the bath T, the authors show that high-energy electrons in  $I_{\text{leak}}$  can activate phonons in the substrate and bring the S into an out-of-equilibrium state.