# Scaling Superconducting Quantum Processors

Coherence, Frequency Targeting and Crosstalk

#### AMR. OSMAN

Quantum Technology Laboratory

Department of Microtechnology and Nanoscience (MC2)

Chalmers University of Technology

Gothenburg, Sweden, 2024

Scaling Superconducting Quantum Processors Coherence, Frequency Targeting and Crosstalk

AMR OSMAN ISBN 978-91-8103-139-3

Copyright © 2024 AMR OSMAN All rights reserved.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr. 5597 ISSN 0346-718X

Quantum Technology Laboratory Department of Microtechnology and Nanoscience (MC2) Chalmers University of Technology SE-412 96 Gothenburg, Sweden Phone: +46 (0)31 772 1000

Printed by Chalmers Reproservice Gothenburg, Sweden, November 2024 To my beloved sister Heba

Your memory lives forever in my heart

This is for you

#### **Abstract**

The advancement of quantum computing hinges on the scalability and performance of quantum processors. Superconducting qubits require precision engineering to achieve long coherence times and high gate fidelities. However, their performance remains constrained by challenges such as fabrication uncertainty, imperfections in materials, and unintended signal crosstalk, all of which impose significant limitations on scalability and reliability.

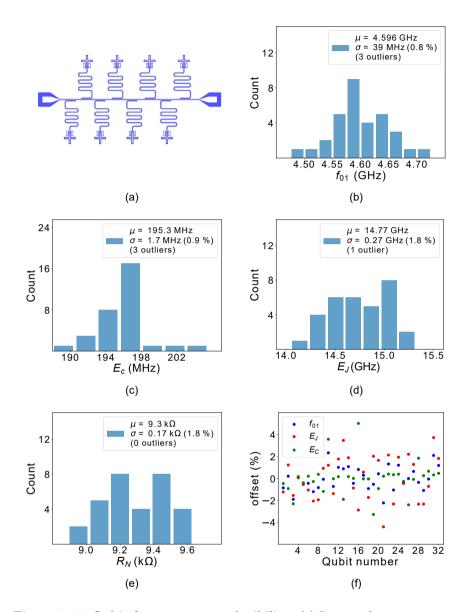

A significant portion of this work investigates the reproducibility of Josephson junctions, essential components of superconducting qubits. Variations in these junctions lead to deviations in qubit frequencies, degrading gate fidelity. A streamlined fabrication process using Patch-Integrated Cross-Type (PICT) junctions reduces the steps for junction fabrication while maintaining reproducibility and qubit coherence. Further improvements are achieved by optimizing the fabrication process and using slightly larger junction sizes, leading to a qubit frequency reproducibility of 40 MHz (1%) on a planar chip.

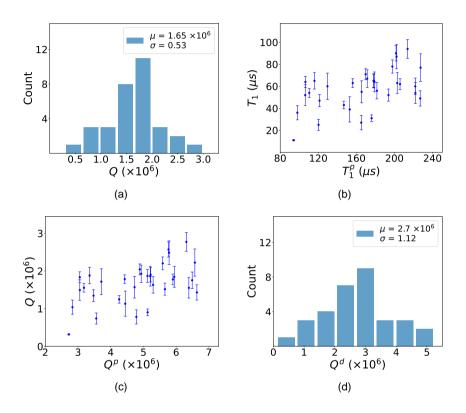

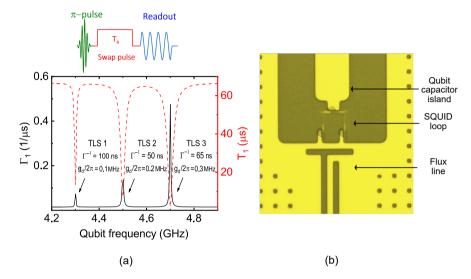

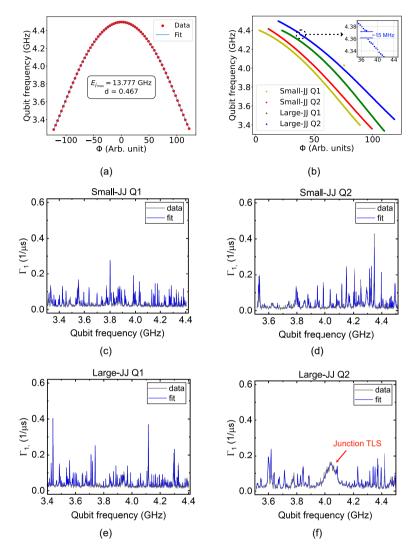

Qubit coherence, essential for maintaining quantum states and enabling error-free operations, is investigated from a material perspective. Two-level systems (TLS) at material interfaces are identified as dominant sources of decoherence. Through TLS spectroscopy, we probe the density of defects in the vicinity of the qubit and their presence within the junction's tunnel barrier. Additionally, we evaluate the impact of fabrication steps on the performance of superconducting circuit and improve the qubit quality factor up to 5 million.

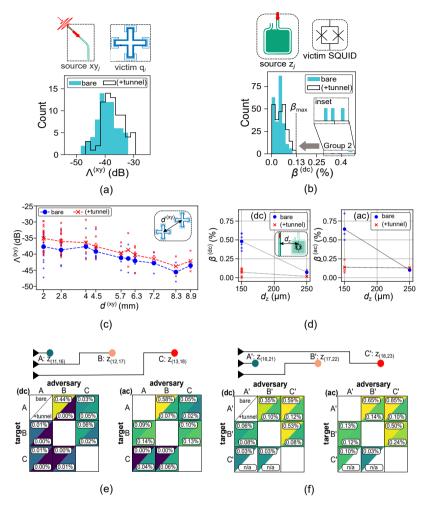

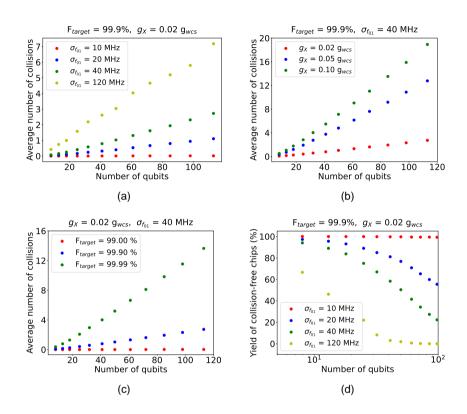

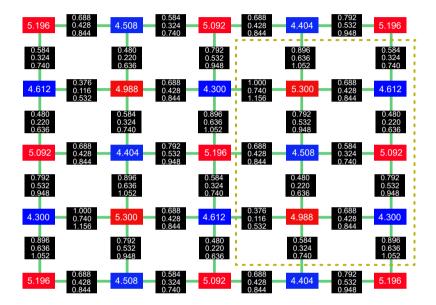

Crosstalk, arising from unintended drive-line interactions, degrades gate fidelity. On the first-generation 25-qubit flip-chip quantum processing unit (QPU), the average drive-line crosstalk was benchmarked at 40 dB. The second-generation QPU enables studies on parameter targeting, including the influence of chip-to-chip spacing on qubit frequencies and crosstalk's impact on gate fidelity. Advanced frequency allocation strategies are introduced to account for fabrication uncertainties while maximizing frequency separation between neighboring qubits. While these approaches effectively mitigate gate collisions, our results emphasize the need for further suppression of crosstalk and active mitigation techniques to achieve higher fidelities in large-scale quantum processors.

**Keywords:** Superconducting qubits, quantum computing, Josephson junction reproducibility, TLS spectroscopy, 3D integration, quantum processor

#### List of Publications

This thesis is based on the following publications:

- [A] A. Osman, J. Simon, A. Bengtsson, S. Kosen, P. Krantz, D. P. Lozano, M. Scigliuzzo, P. Delsing, J. Bylander and A. Fadavi Roudsari, "Simplified Josephson-junction fabrication process for reproducibly high-performance superconducting qubits". Appl. Phys. Lett. 118, 064002 (2021).

- [B] Amr Osman, Jorge Fernández-Pendás, Christopher Warren, Sandoko Kosen, Marco Scigliuzzo, Anton Frisk Kockum, Giovanna Tancredi, Anita Fadavi Roudsari, and Jonas Bylander, "Mitigation of frequency collisions in superconducting quantum processors". Phys. Rev. Research 5, 043001 (2023).

- [C] J. Biznárová, A. Osman, E. Rehnman, L. Chaynun, C. Križan, P. Malmberg, M. Rommel, C. Warren, P. Delsing, A. Yurgens, J. Bylander, and A. Fadavi Roudsari, "Mitigation of interfacial dielectric loss in aluminum-on-silicon superconducting qubits". npj Quantum Inf 10, 78 (2024).

- [D] Lert Chayanun, Janka Biznárová, Lunjie Zeng, Per Malmberg, Andreas Nylander, **Amr Osman**, Marcus Rommel, Pui Lam Tam, Eva Olsson, Per Delsing, August Yurgens, Jonas Bylander, and Anita Fadavi Roudsari, "Characterization of process-related interfacial dielectric loss in aluminum-on-silicon by resonator microwave measurements, materials analysis, and imaging". APL Quantum 1, 026115 (2024).

- [E] Christopher W. Warren, Jorge Fernández-Pendás, Shahnawaz Ahmed, Tahereh Abad, Andreas Bengtsson, Janka Biznárová, Kamanasish Debnath, Xiu Gu, Christian Križan, **Amr Osman**, Anita Fadavi Roudsari, Per Delsing, Göran Johansson, Anton Frisk Kockum, Giovanna Tancredi and Jonas Bylander, "Extensive characterization and implementation of a family of three-qubit gates at the coherence limit". npj Quantum Information 9, 44 (2023).

- [F] Sandoko Kosen, Hang-Xi Li, Marcus Rommel, Daryoush Shiri, Christopher Warren, Leif Grönberg, Jaakko Salonen, Tahereh Abad, Janka Biznárová, Marco Caputo, Liangyu Chen, Kestutis Grigoras, Göran Johansson, Anton Frisk Kockum, Christian Križan, Daniel Pérez Lozano, Graham J Norris,

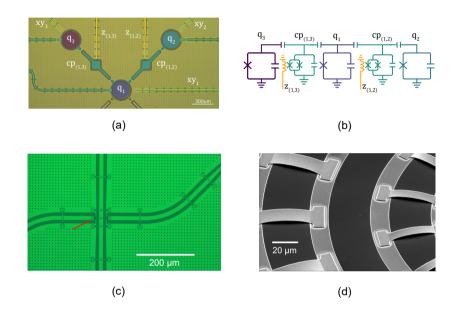

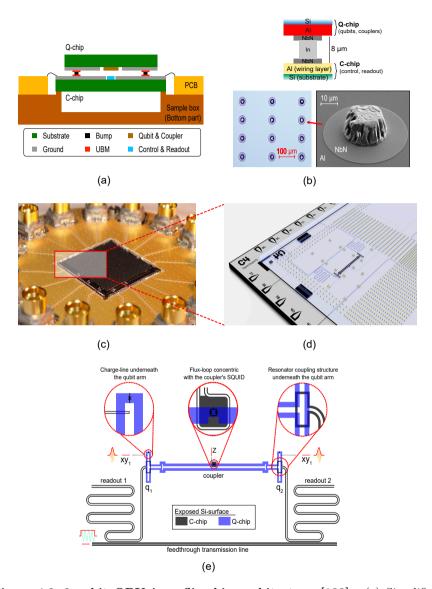

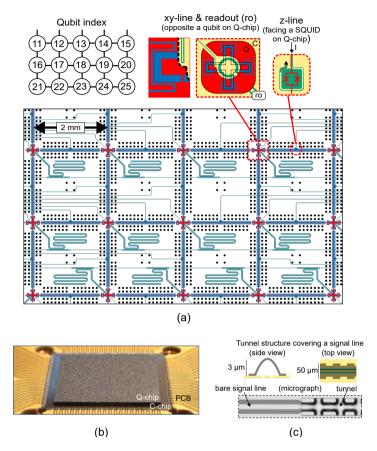

Amr Osman, Jorge Fernández-Pendás, Alberto Ronzani, Anita Fadavi Roudsari, Slawomir Simbierowicz, Giovanna Tancredi, Andreas Wallraff, Christopher Eichler, Joonas Govenius, and Jonas Bylander, "Building blocks of a flipchip integrated superconducting quantum processor". Quantum Sci. Technol. 7, 035018 (2022).

[G] Sandoko Kosen, Hang-Xi Li, Marcus Rommel, Robert Rehammar, Marco Caputo, Leif Grönberg, Jorge Fernández-Pendás, Anton Frisk Kockum, Janka Biznárová, Liangyu Chen, Christian Križan, Andreas Nylander, **Amr Osman**, Anita Fadavi Roudsari, Daryoush Shiri, Giovanna Tancredi, Joonas Govenius, and Jonas Bylander, "Signal crosstalk in a flip-chip quantum processor". PRX Quantum 5, 030350 (2024).

Other publications by the author, not included in this thesis, are:

[H] Liangyu Chen, Simon Pettersson Fors, Zixian Yan, Anaida Ali, Tahereh Abad, Amr Osman, Eleftherios Moschandreou, Benjamin Lienhard, Sandoko Kosen, Hang-Xi Li, Daryoush Shiri, Tong Liu, Stefan Hill, Abdullah-Al Amin, Robert Rehammar, Mamta Dahiya, Andreas Nylander, Marcus Rommel, Anita Fadavi Roudsari, Marco Caputo, Grönberg Leif, Joonas Govenius, Miroslav Dobsicek, Michele Faucci Giannelli, Anton Frisk Kockum, Jonas Bylander, Giovanna Tancredi, "Fast unconditional reset and leakage reduction in fixed-frequency transmon qubits". arXiv:2409.16748 (2024).

[I] Marina Kudra, Mikael Kervinen, Ingrid Strandberg, Shahnawaz Ahmed, Marco Scigliuzzo, **Amr Osman**, Daniel Pérez Lozano, Mats O. Tholén, Riccardo Borgani, David B. Haviland, Giulia Ferrini, Jonas Bylander, Anton Frisk Kockum, Fernando Quijandría, Per Delsing, and Simone Gasparinetti, "Robust Preparation of Wigner-Negative States with Optimized SNAP-Displacement Sequences". PRX Quantum 3, 030301 (2022).

[J] Anita Fadavi Roudsari, Daryoush Shiri, Hampus Renberg Nilsson, Giovanna Tancredi, **Amr Osman**, Ida-Maria Svensson, Marina Kudra, Marcus Rommel, Jonas Bylander, Vitaly Shumeiko, Per Delsing, "Three-wave mixing traveling-wave parametric amplifier with periodic variation of the circuit parameters". Appl. Phys. Lett. 122, 052601 (2023).

- [K] Liangyu Chen, Hang-Xi Li, Yong Lu, Christopher W. Warren, Christian J. Križan, Sandoko Kosen, Marcus Rommel, Shahnawaz Ahmed, **Amr Osman**, Janka Biznárová, Anita Fadavi Roudsari, Benjamin Lienhard, Marco Caputo, Kestutis Grigoras, Leif Grönberg, Joonas Govenius, Anton Frisk Kockum, Per Delsing, Jonas Bylander and Giovanna Tancredi, "Transmon qubit readout fidelity at the threshold for quantum error correction without a quantum-limited amplifier". npj Quantum Information 9, 26 (2023).

- [L] K. Grigoras, N. Yurttagül, J.-P. Kaikkonen, E. T. Mannila, P. Eskelinen, D. P. Lozano, H.-X. Li, M. Rommel, D. Shiri, N. Tiencken, S. Simbierowicz, A. Ronzani, J. Hätinen, D. Datta, V. Vesterinen, L. Grönberg, J. Biznárová, A. Fadavi Roudsari, S. Kosen, A. Osman, M. Prunnila, J. Hassel, J. Bylander, and J. Govenius, "Qubit-Compatible Substrates With Superconducting Through-Silicon Vias". IEEE Trans. Quantum Eng. 3, 5100310 (2022).

- [M] Phalgun Lolur, Mårten Skogh, Werner Dobrautz, Christopher Warren, Janka Biznárová, **Amr Osman**, Giovanna Tancredi, Göran Wendin, Jonas Bylander, Martin Rahm, "Reference-State Error Mitigation: A Strategy for High Accuracy Quantum Computation of Chemistry". J. Chem. Theory Comput. 2023, 19, 3, 783–789.

- [N] Mohammed Ali Aamir, Claudia Castillo Moreno, Simon Sundelin, Janka Biznárová, Marco Scigliuzzo, Kowshik Erappaji Patel, **Amr Osman**, D. P. Lozano, Ingrid Strandberg, and Simone Gasparinetti, "Engineering Symmetry-Selective Couplings of a Superconducting Artificial Molecule to Microwave Waveguides". Phys. Rev. Lett. 129, 123604 (2022).

- [O] Claudia Castillo-Moreno, Kazi Rafsanjani Amin, Ingrid Strandberg, Mikael Kervinen, **Amr Osman**, Simone Gasparinetti, "Dynamical excitation control and multimode emission of an atom-photon bound state". arXiv:2404.05547 (2024).

- [P] Mårten Skogh, Werner Dobrautz, Phalgun Lolur, Christopher Warren, Janka Biznárová, **Amr Osman**, Giovanna Tancredi, Jonas Bylander and Martin Rahm, "The electron density: a fidelity witness for quantum computation". Chem. Sci., 2024, 15, 2257-2265 (2023).

# **Acknowledgments**

I would like to express my heartfelt gratitude to several individuals who have played a pivotal role in my journey to this point.

First, I am grateful to my supervisor, Jonas Bylander. Thank you for the opportunity to be part of your research group and for trusting me to work on projects that inspire me. Your support in making things possible rather than imposing obstacles has been invaluable. I look forward to continuing working with you in the future.

A heartfelt thank you to Anita. You have been more than just a co-supervisor; you have been a mentor from the moment I joined QTL six years ago. Your unlimited patience in guiding me through my first steps in the cleanroom, your constant availability for discussions, and your meticulous feedback on my manuscripts have been truly invaluable. I am deeply grateful for all that you have done for me, and I truly hope we can maintain a strong connection beyond this PhD journey.

I would also like to thank my co-supervisor, Avgust Jurgens, for his valuable insights on materials and fabrication, my examiner, Per Delsing, for his support and unmistakable interest in discussing new ideas, and the current head of our division, Witlef Wieczorek, for ensuring healthy and efficient work environment.

During the second half of my PhD, I had the privilege of working closely with Giovanna Tancredi, the current PI of our quantum computing effort. Your hard work and dedication, from ensuring everyone can run their experiments to discussing even the minor details, have been incredible. I also appreciate your valuable feedback on this manuscript.

A special thank you to Philip Krantz. Before coming to Chalmers for my second year of master's as part of the Erasmus Mundus program, I was planning to go to Dresden instead. But after your lecture in Leuven about the quantum computing effort at Chalmers, I changed my mind just two weeks before the decision dead-line—and I believe it was the right choice. You later helped me land a master's thesis project in the group, and that's where it all began.

The achievements in this thesis and in our division over the past five years would not have been possible without our alumni, who laid a strong foundation of knowledge that provided a head start for my research. Thank you to Andreas Bengtsson, Marco Scigliuzzo, David Niepce, Gustav Andersson and Marina Kudra.

In every experimental group, it's great to have that go-to experimentalist who, for some reason, knows more about the theory than the rest—and even better, is willing to drop whatever they're doing to explain it to you. Chris, you have been a great companion throughout my PhD journey. Thank you for the countless discussions (sometimes arguments as you referred to them) and the probably over 500 hundred lunch meals we had together.

Christian Križan, thank you for always being there to help at work and outside.

Linda Brånell, you make our lives so much easier. We're really lucky to have you! I had the privilege of working with and learning from many incredible individuals throughout this journey, without whom, a lot of the work in this thesis wouldn't have been possible. Thank you to Sandoko (and your great sense of humor), Hang-Xi, Michele, Liangyu, Daryoush, Marcus, Andreas, Daniel Pérez, Janka, Lert, Emil, Halldor, Lefty, Stefan, Jorge, and Anton.

Our collaboration does not stop at shared projects, but it extends to discussions over lunch, seminars or casual office chats. Thank you to Simone, Tom, Anuj, Nermin, Robert, Lunjie, Irshad, Anna, Filip, Tangyou, Tong, Olga, Achintya, Aditya, Marti, Claudia, Simon, Aamir, Claire, and Maurizio. Thank you to all current and previous members of QTL and AQP.

A huge portion of this thesis revolves around fabrication, and it wouldn't have been possible without the pioneering cleanroom infrastructure we have at Myfab Chalmers. Thank you to Henrik, Johan, Niclas, Mattias, Marcus, Ruggero, Mahdad, and Petra for your invaluable support. Thank you to Lars for skillfully and reliably machining our packages and sample boxes.

Now, outside work ...

To Eliott, Pierluigi, Alessio, Timo, Erik, Maria, Anton, Anna, Camilla, Chiara, Valeria, Jonas, Emma, Andreas and all those I was blessed with their friendship and companionship. Obviously, you guys had no contribution whatsoever to this thesis, but you gave me something far greater—joy, laughter, sadness, silly and serious conversations, sports, celebrations, and navigating tough pandemic times. That, without a doubt, helped me keep going with my work. Thank you!

I am deeply grateful to my parents who never spared an effort to give me opportunities they never had, and for always having my best interest at heart. I could write a whole thesis about that, but I will keep it brief. I am also lucky to have my sister Salma, with her unmatched love, care, strength and sense of responsibility. Thank you to all my family.

Lena, there are no words to describe my gratitude to you. Since I met you, no one has supported me through tough times the way you have. No one understands me as deeply as you do. I consider myself fortunate in life, but I am without a doubt the luckiest for having you in it. You are my partner and my best friend, and I am blessed with our love. I am also deeply thankful to your family for welcoming me with open arms and making me feel like part of their own. Their kindness and support have meant so much to me.

To my beloved sister Heba, to whom I dedicate this thesis. You have always been the closest human to my heart. Losing you was an immeasurable sorrow, but your memory never fades. This memory has been a constant source of strength and inspiration.

# Contents

| ΑI | bstra | t                                           | i   |

|----|-------|---------------------------------------------|-----|

| Li | st of | Papers                                      | iii |

| Αd | cknov | vledgements                                 | vii |

| ı  | Tł    | nesis                                       | 1   |

| 1  | Intr  | oduction                                    | 3   |

|    | 1.1   | From classical to quantum                   | 4   |

|    | 1.2   | Current state of quantum computers          | 6   |

|    | 1.3   | Why is it hard to build a quantum computer? | 7   |

|    | 1.4   | In this thesis                              | 8   |

|    |       | 1.4.1 Frequency collision and crosstalk     | 9   |

|    |       | 1.4.2 Qubit coherence                       | 9   |

|    |       | -                                           | 10  |

| 2  | Jose  | phson Junctions                             | 11  |

|    | 2.1   | Josephson junctions in transmon qubits      | 12  |

|    |       | 2.1.1 The Josephson effect                  | 12  |

|    |       | 2.1.2 Transmon qubits                       | 14  |

|   |      | 2.1.3    | Uncertainty in qubit frequency               |

|---|------|----------|----------------------------------------------|

|   | 2.2  | Fabric   | ation process                                |

|   |      | 2.2.1    | Wiring layer                                 |

|   |      | 2.2.2    | Two-step fabrication process                 |

|   |      | 2.2.3    | Patch-integrated cross-type junctions        |

|   | 2.3  | Repro    | ducibility of $R_N$                          |

|   |      | 2.3.1    | $R_N$ characterization setup                 |

|   |      | 2.3.2    | PICT-junctions reproducibility               |

|   |      | 2.3.3    | Decoupling sources of variations in $R_N$    |

|   |      | 2.3.4    | Larger, thick-oxide Josephson junctions      |

|   | 2.4  | Qubit    | frequency reproducibility                    |

|   | 2.5  | Furthe   | er insight into Josephson junctions          |

|   |      | 2.5.1    | Aging of Josephson junctions                 |

|   |      | 2.5.2    | Low temperature vs Room temperature $R_N$ 39 |

| 3 | Qub  | it Cohe  | erence 41                                    |

| • | 3.1  |          | hannels                                      |

|   |      | 3.1.1    | Two-level systems                            |

|   |      | 3.1.2    | Purcell decay                                |

|   | 3.2  |          | ence characterization                        |

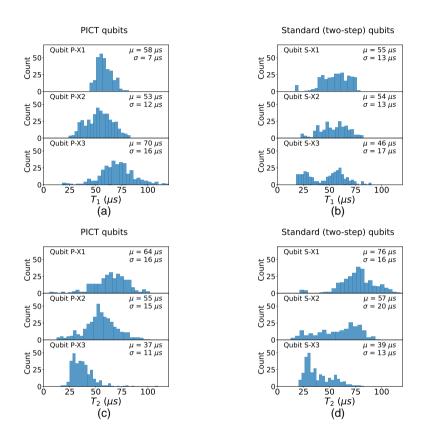

|   |      | 3.2.1    | PICT transmons                               |

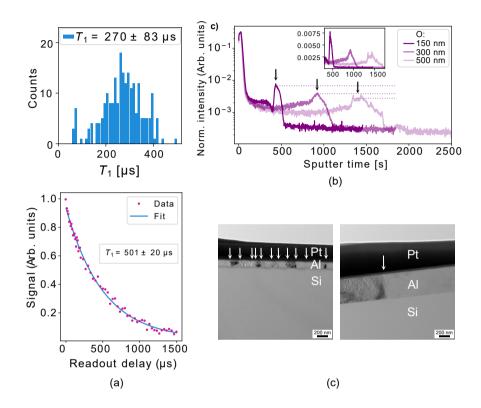

|   |      | 3.2.2    | Larger-junction transmons                    |

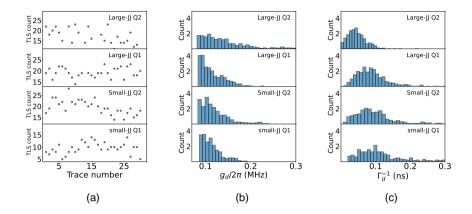

|   |      | TLS s    | pectroscopy                                  |

|   |      | 3.3.1    | TLS characterization                         |

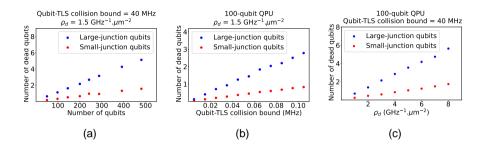

|   |      | 3.3.2    | Implications on the QPU 55                   |

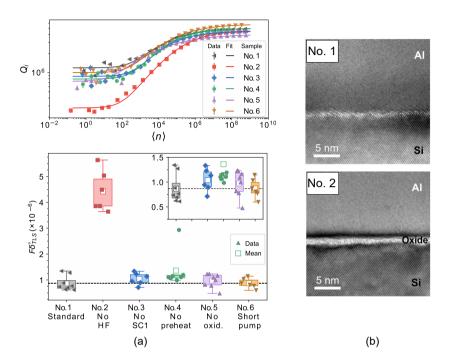

|   | 3.4  | Mitiga   | ting loss in aluminum-on-silicon qubits      |

|   |      | 3.4.1    | Systematic study of the process steps        |

|   |      | 3.4.2    | Thicker aluminum films for lower loss 59     |

| 4 | Cros | sstalk a | nd frequency collisions in a QPU 63          |

|   | 4.1  |          | t planar QPU                                 |

|   | 4.2  |          | nip architecture                             |

|   | 4.3  |          | oit flip-chip QPU                            |

|   | -    | 4.3.1    | XY crosstalk                                 |

|   |      | 4.3.2    | Z crosstalk                                  |

|   | 4.4  | Freque   | ency allocation on a QPU                     |

|   | 4.5  | _        | ating frequency collisions on a OPII 78      |

| 5  | QPU                                                                        | J Design                                                                                            | 81         |  |

|----|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------|--|

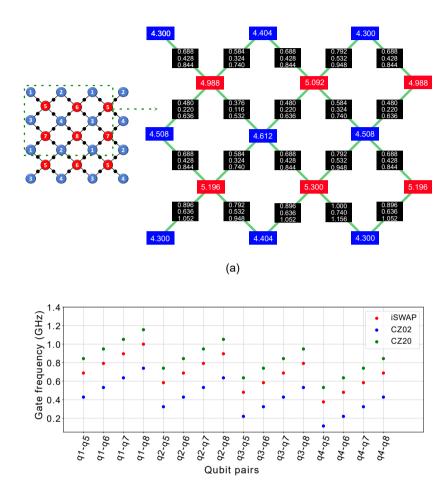

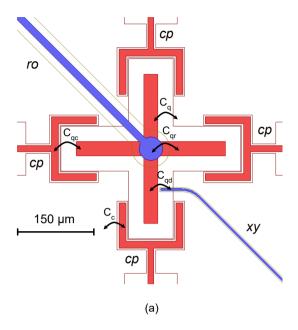

|    | 5.1                                                                        | Design overview                                                                                     | 82         |  |

|    |                                                                            | 5.1.1 Qubit lattice                                                                                 | 82         |  |

|    |                                                                            | 5.1.2 Qubit design                                                                                  | 84         |  |

|    |                                                                            | 5.1.3 Qubit control and readout                                                                     | 84         |  |

|    |                                                                            | 5.1.4 Qubit-qubit coupling                                                                          | 87         |  |

|    |                                                                            | 5.1.5 Parameter sensitivity to chip-to-chip spacing                                                 | 92         |  |

|    | 5.2                                                                        | Flip-chip module selection                                                                          | 92         |  |

| 6  | QPU                                                                        | J Benchmarking                                                                                      | 95         |  |

|    | 6.1                                                                        | Measurement setup                                                                                   | 96         |  |

|    | 6.2                                                                        | Device calibration                                                                                  | 96         |  |

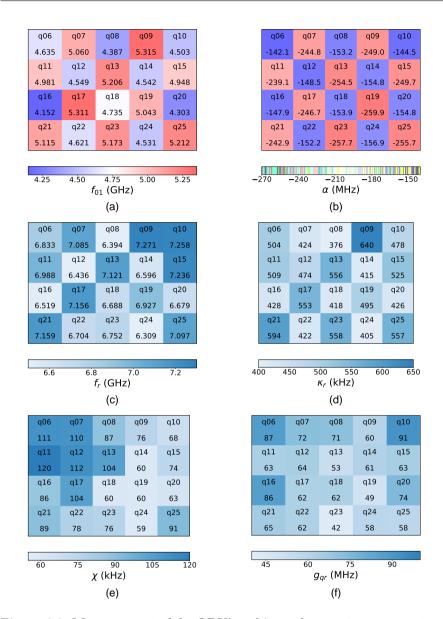

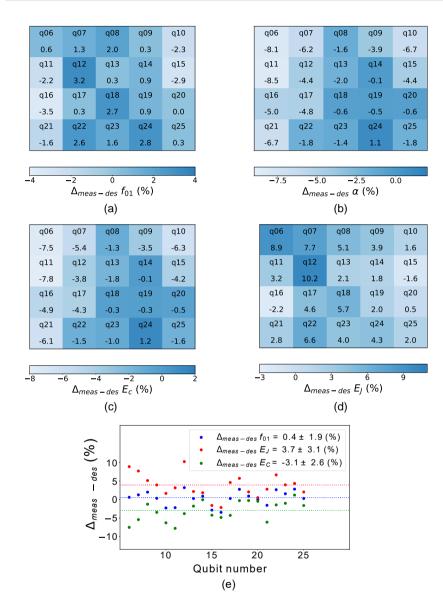

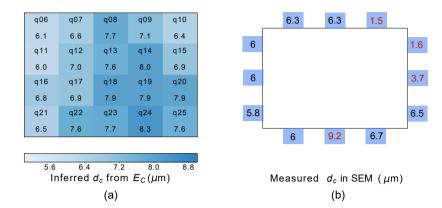

|    | 6.3                                                                        | Parameter Targeting                                                                                 | 99         |  |

|    |                                                                            |                                                                                                     | 102        |  |

|    |                                                                            | 6.3.2 Resonator-qubit coupling                                                                      | 105        |  |

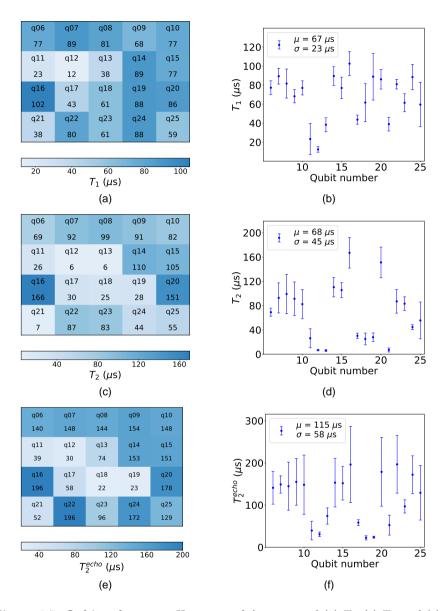

|    | 6.4                                                                        | Qubit coherence                                                                                     | 105        |  |

|    | 6.5                                                                        | Crosstalk and gate fidelity                                                                         | 108        |  |

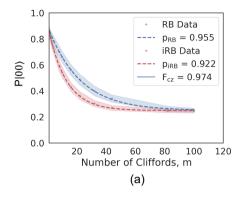

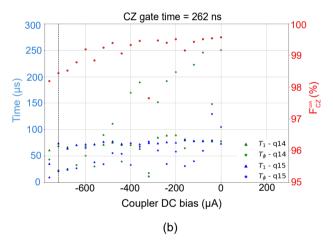

|    |                                                                            | 6.5.1 Randomized Benchmarking                                                                       | 109        |  |

|    |                                                                            | 6.5.2 01 and 12 crosstalk                                                                           | 112        |  |

|    |                                                                            | 6.5.3 Preliminary conclusions                                                                       | 114        |  |

|    | 6.6                                                                        | Two-qubit gate                                                                                      | 114        |  |

|    | 6.7                                                                        | Future work                                                                                         | 116        |  |

| 7  | Sum                                                                        | mary and Contributions                                                                              | 119        |  |

| Re | feren                                                                      | nces 1                                                                                              | 123        |  |

|    |                                                                            |                                                                                                     |            |  |

| П  | Co                                                                         | re papers                                                                                           | 137        |  |

| Α  |                                                                            | plified Josephson-junction fabrication process for reproducibly -performance superconducting qubits | Α1         |  |

|    | 6"                                                                         | performance superconducting quoits                                                                  | ~1         |  |

| В  | B Mitigation of frequency collisions in superconducting quantum processors |                                                                                                     |            |  |

| C  |                                                                            | gation of interfacial dielectric loss in aluminum-on-silicon su-<br>conducting qubits               | <b>C</b> 1 |  |

| D | Characterization of process-related interfacial dielectric loss in aluminum-on-silicon by resonator microwave measurements, materials analysis, and imaging | D1         |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| E | Extensive characterization and implementation of a family of three-<br>qubit gates at the coherence limit                                                   | <b>E</b> 1 |

| F | Building blocks of a flip-chip integrated superconducting quantum processor                                                                                 | F1         |

| G | Signal crosstalk in a flin-chin quantum processor                                                                                                           | G1         |

# Part I

# **Thesis**

# CHAPTER 1

#### Introduction

Technology evolves as a direct response to human needs and the challenges we encounter. Over time, these needs have transformed from basic pursuits, such as developing tools for farming and food preservation millennia ago, to more intricate ones, like powering large cities and establishing telecommunication networks. Today, we grapple with even more sophisticated challenges, including drug development, combating climate change, cryptography, and the search for materials with unique properties. Drug development, for instance, is a lengthy process that may take over a decade to identify molecules that exhibit the required medicinal activity against a biological target [1]. While the advent of computers and computational chemistry transformed drug discovery from an *in vitro* process with a low success rate to an accelerated, more efficient process, classical computations still rely on approximate and comparative modeling. Accurate simulation of protein folding and chemical interactions between large molecules can be prohibitively resource-intensive [2, 3]. Similarly, finding new efficient materials for batteries and photovoltaic cells, or as catalysts in chemical reactions, relies on approximate solutions that can be computationally infeasible [4-7]. A few decades ago, quantum computing emerged as a possible solution to these bottlenecks. By leveraging new logic, beyond that which is allowed classically, a quantum computer can implement highly efficient and accurate processing of complex computational tasks.

## 1.1 From classical to quantum

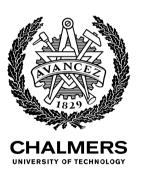

Classical computations rely on encoding discrete information in bits, where each bit is either 0 or 1. Think of it as a light switch; it can either be on or off. A collection of bits forms a number, a character, or a logical operation within an algorithm. A quantum computer, similarly, encodes information in a quantum bit or a qubit. Unlike classical bits, the state of a qubit can exist in a superposition of  $|0\rangle$  and  $|1\rangle$ . The Bloch sphere in Fig. 1.1(a) is a standard representation of such a superposition, where the blue vector on that sphere represents the qubit state

$$|\psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{-j\phi}\sin\frac{\theta}{2}|1\rangle,$$

(1.1)

where  $\theta$  and  $\phi$  can take any arbitrary values. Scaling this argument, a set of 3 classical bits can only be in one of 8 possible permutations: 000, 001, ..., or 111, while a set of 3 qubits can be in all 8 permutations at the same time with different probabilities [Fig. 1.1(b)]. To generalize, an N-qubit computer spans over  $2^N$  possible states.

To further expand on this, for a quantum computer with N qubits, a classical computer would need to store  $2^N$  numbers that represent the state of the quantum computer. Each of these numbers consists of m classical bits, depending on the desired precision, resulting in a total storage requirement of  $m \times 2^N$  classical bits. This exponential scaling demonstrates the inherent limitations of classical computers in handling quantum systems. This realization further inspired the idea of using quantum computers to simulate the quantum mechanical systems of nature [8].

"And therefore, the problem is, how can we simulate the quantum mechanics? There are two ways that we can go about it. We can give up on our rule about what the computer was, we can say: Let the computer itself be built of quantum mechanical elements which obey quantum mechanical laws. Or we can turn the other way and say: Let the computer still be the same kind that we thought of before."

— Richard Feynman, 1981

To illustrate with real numbers: If we want to store the spin state of 40 electrons in a molecule, a quantum computer would require 40 qubits. A

Figure 1.1: Comparison between classical and quantum bits. (a) Representation of a single classical bit and a quantum bit (qubit). A classical bit can exist in one of two states, 0 or 1, while a qubit state, represented by a unit vector on the Bloch sphere, can exist in an arbitrary superposition of  $|0\rangle$  and  $|1\rangle$ . (b) Extension of this comparison to three classical bit and three qubits. Three classical bits can exist in one of  $2^3$ =8 distinct states, whereas three qubits can exist in a superposition of all  $2^3$ =8 states simultaneously.

classical computer, however, would require  $2^{40}$  numbers; a total of 4 TB of memory for a single-precision number (32 bits). Just doubling the number of electrons to 80 would require  $5\times10^{12}$  TB of memory. That is almost a hundred times more than the total volume of digital data stored and consumed worldwide in 2020 [2, 9, 10].

Now, how do we make a qubit? When envisioning a qubit, the first idea might be to use a component that is inherently quantum, such as a nucleus of an atom or an electron. In 1995, the first quantum logic gate was demonstrated with trapped ions at NIST [11]. In 1997 and 1998, the quantum gates were demonstrated at MIT and Oxford using nuclear magnetic resonance (NMR), where magnetic fields manipulate nuclear spins within molecules [12–16]. A year later, in Japan, researchers demonstrated that superconducting circuits could create an artificial atom, effectively functioning as a qubit [17]. This approach quickly gained traction, as the well-established fabrication techniques for superconducting circuits could later leverage advancements from the CMOS industry, which offered a robust technological foundation. As a result, superconducting qubits became one of the most promising and widely adopted technologies for building qubits, forming the architecture chosen by leading research groups and companies such as Google and IBM. Superconducting qubits are also the platform we adopt in our research group and are the focus of this thesis. Alongside superconducting qubits, other technologies such as trapped ions [18], quantum dots [19], and photonic qubits [20] are actively explored as alternative pathways.

## 1.2 Current state of quantum computers

It is essential to recognize that quantum computers are not expected to solve all computational problems, nor will they replace classical computers. Quantum computers rely on classical computers and electronics to control and interrogate them. The real advantage of quantum computers lies in their ability to handle a specific set of problems more efficiently than classical computers. When we say "more efficiently", the difference can be staggering: a problem that would take thousands to millions of years to solve on a classical computer might be solvable by quantum computers in just hours [21].

So, where do quantum computers stand today? To answer this question, perhaps, it is useful to divide quantum algorithms into two broad classes.

The first class, fault-tolerant algorithms [22], assumes that qubits are error-free during the algorithm runtime. This class includes Shor's algorithm [23], intended for RSA decryption, Grover's algorithm [24], which can speed up database search exponentially, and Quantum Fourier Transform [25], which is essential for simulating the dynamics of quantum systems in material science and drug development.

The second class encompasses Noisy Intermediate-Scale Quantum (NISQ) algorithms [26], which are designed to run on quantum processors with noisy, error-prone qubits. These algorithms are heuristic, aiming to provide approximate solutions that are closer to the exact solution than what their classical counterparts can achieve. Examples of these algorithms include Quantum-Approximate Optimization Algorithms (QAOA) [27], and Variational Quantum Eigensolvers (VQE) [28].

Returning to the question of where we are now, a fault-tolerant quantum computer remains a distant goal. Boston Consultancy Group predicts that such a machine could become a reality around the year 2040, with a forecast economic value of \$450 billion to \$850 billion from quantum computing [29]. Meanwhile, the potential of NISQ algorithms to outperform classical algorithms and artificial intelligence is still uncertain. While the ultimate goal is to achieve fault tolerance, NISQ algorithms will offer useful insights and applications as we advance toward this goal.

# 1.3 Why is it hard to build a quantum computer?

Building quantum computers is a remarkably challenging endeavor, with most of our current hurdles rooted in engineering. To start, qubit decoherence (the general term for loss of information in a quantum computer) poses a constant challenge across most qubit platforms. Qubits are surrounded by and interacts with a noisy environment. This environment makes it difficult for qubits to maintain their exotic superposition state long enough to execute quantum algorithms effectively. Superconducting qubits typically decohere within a few hundred microseconds—insufficient to implement fault-tolerant algorithms. For instance, implementing Shor's algorithm to factor a 2048-bit RSA integer, which requires hundreds of seconds, becomes infeasible with such short-lived coherence times.

Error correction codes, however, offer a solution by mitigating decoher-

ence [30]. They encode a single logical qubit into hundreds to thousands of physical qubits [31, 32]. Despite the substantial overhead—potentially requiring up to 20 million qubits and over 8 hours of runtime to factor a 2048-bit RSA integer [21]—error correction remains the only feasible approach to implement these fault-tolerant algorithms.

Beyond coherence, we must also control these qubits by applying quantum gates to shift their state by a specific angle around the Bloch sphere or mediate interactions between them. The quality of such quantum gates is captured by the gate fidelity, which quantifies the accuracy of the target operation. Eventually, we must read out the state of the qubit to extract the results of our computation. The accuracy of reading out a qubit state that reflects its true state is quantified by the readout fidelity.<sup>1</sup>

High qubit coherence, gate fidelity, and readout fidelity are three of the main objectives toward the goal of building a quantum computer. Both fault-tolerant and NISQ algorithms benefit from their improvement. Higher qubit coherence and quantum gate fidelity for fault tolerance mean fewer physical qubits required for every logical qubit, while fast and high-fidelity readout is crucial for accurate and fast error detection, hence, shorter algorithm runtime. For NISQ algorithms, high qubit coherence, gate fidelity, and readout fidelity facilitate more complex algorithms with more quantum operations and reliable measurement outcomes.

### 1.4 In this thesis

Addressing these challenges and scaling a quantum processing unit (QPU) toward fault tolerance, or quantum advantage with NISQ algorithms demands interdisciplinary engineering efforts, each contributing from a unique perspective to the solution. In this thesis, we present modest yet critical steps in this direction by addressing specific engineering challenges at the level of single qubits and a 25-qubit QPU, and the potential scalability to a larger number of qubits. The following subsections explore these engineering perspectives, emphasizing the challenges that are central to this thesis.

<sup>&</sup>lt;sup>1</sup>Readout fidelity is not a topic that is addressed further in this thesis.

#### 1.4.1 Frequency collision and crosstalk

To run a quantum algorithm on a QPU, we implement sequences of single-and two-qubit gates. Single-qubit gates are microwave pulses with a frequency equal to the qubit transition frequency (typically 3—6 GHz). To implement two-qubit gates, we parametrically modulate the frequency of a mediating element (a coupler) between two qubits at a frequency corresponding to various two-qubit transitions (typically 50—1000 MHz). These control pulses travel from room-temperature electronics down through signal lines patterned on the QPU, which is housed in a dilution refrigerator at 10 mK. Achieving high gate fidelities requires precise calibration of the pulse amplitude, frequency, duration, and phase. This is feasible when controlling individual qubits. However, simultaneous control of multiple qubits introduces the risk of unintended pulses reaching neighboring qubits, altering their states—a phenomenon known as signal crosstalk, which degrades gate fidelity.

One solution to mitigate crosstalk is to design a qubit frequency allocation scheme that maximizes the frequency spacing between neighboring qubits. In this arrangement, even if a signal leaks to a neighboring qubit, it remains off-resonance and therefore minimally affects the unintended qubit. However, fabrication uncertainties lead to deviations in qubit frequencies from their design targets. These frequency shifts are primarily due to variations in the Josephson junction, a fundamental component of superconducting qubits.

Josephson junction fabrication and improving the reproducibility of qubit frequency are discussed in detail in Chapter 2, focusing on planar chips and uncoupled qubits. Chapter 4 delves into crosstalk characterization on our first-generation 25-qubit QPU and the frequency allocation strategies adopted to mitigate crosstalk. In the same chapter, I introduce our flip-chip architecture, an essential technology for scaling up to tens of qubits on a single QPU. In Chapter 6, I characterize our second-generation 25-qubit QPU, assessing both the frequency targeting and the impact of crosstalk on single-qubit gate fidelity.

#### 1.4.2 Qubit coherence

Improving qubit coherence is an ongoing pursuit. No matter how high coherence times reach, the quest for further enhancement will continue. Although sources of decoherence arise from various channels, fabrication quality and

material purity remain the primary bottlenecks for superconducting qubits. Material interfaces are often riddled with defects, known as two-level system (TLS) defects. These defects interact with the qubit, leading to energy dissipation and loss of coherence. Probing these TLS defects and their impact on the performance of superconducting circuitry is discussed in Chapter 3, along with the methods we employ to enhance qubit quality.

#### 1.4.3 Design and simulation

The design of a QPU begins with defining polygons in computer-aided design (CAD) software. The dimensions of these polygons and their proximity determine the QPU parameters, such as the qubit frequency, the couplings between neighboring qubits, as well as the couplings between the qubit and its readout and control elements. To define the optimal dimensions, circuits are simulated using microwave simulation tools, with a parametrized sweep of device geometry, until the simulation converges to the target circuit parameters. It is crucial to capture all circuit parameters that influence the simulation, while at the same time keeping the simulation as resource-efficient as possible.

Additionally, design and simulation do not always match the real circuit parameters, and therefore, there must always be a constant feedback loop between design, fabrication, and measurement. As qubit counts and circuit complexity increase, optimizing qubit placement and routing of control and signal lines becomes even more critical. Chapter 4 and Chapter 5 discuss some of the design aspects of the QPU, while Chapter 6 evaluates the accuracy of parameter targeting.

# CHAPTER 2

## Josephson Junctions

The Josephson junction (JJ) stands as a fundamental building block in the construction of qubits within superconducting circuits. The qubit's distinct states,  $|0\rangle$  and  $|1\rangle$ , emerge from the nonlinearity of the junction's inductance—an essential factor that disrupts the otherwise evenly spaced energy levels typical of linear harmonic oscillators. Due to its small size, Josephson junction fabrication presents significant challenges, particularly in superconducting qubit circuits.

When designing a quantum processor, an intricately developed qubit frequency crowding scheme is crucial for executing quantum gates, while minimizing crosstalk between qubits. Achieving the target qubit frequencies strongly depends on the reproducibility of Josephson junction parameters. Over the past five years, considerable efforts have been dedicated to advancing various aspects of Josephson junction fabrication, including improvements in lithography, junction deposition, and oxidation techniques [33–38], along with strategies to compensate for size drifts arising from angular evaporation [39]. Beyond fabrication advancements, notable progress has been made in post-fabrication tuning of junction resistance [40–44].

Section 2.1 provides an overview of the Josephson effect, its significance in

superconducting qubits, and its influence on the reproducibility of the transmon qubit frequency. Section 2.2 outlines the JJ fabrication process, emphasizing the simplifications introduced through the Patch-Integrated Cross-Type (PICT) junctions. The reproducibility of the JJ's normal-state resistance,  $R_N$ , and its impact on qubit frequency reproducibility, is discussed in Sections 2.3 and 2.4. Finally, Section 2.5 delves into preliminary studies on various aspects of Josephson junctions, including aging effects, and the dependence of normal-state resistance on temperature.

## 2.1 Josephson junctions in transmon qubits

In this section, I present the theoretical framework underpinning the work discussed in this chapter. Without delving into detailed derivations, I focus on key equations and concepts that motivate the use of Josephson junctions in transmon qubits and help understand key aspects, especially their impact on qubit frequency targeting. The following subsections address the Josephson effect, the transmon qubit, and the factors influencing qubit frequency stability. This provides essential context for the experimental results discussed later.

### 2.1.1 The Josephson effect

In 1962, 22-year-old graduate student Brian D. Josephson made a ground-breaking theoretical prediction in superconductivity [45, 46]. Josephson postulated that a supercurrent  $I_s$  flows between two superconducting electrodes separated by a thin insulating barrier (or a weak link) in the absence of applied voltage. This supercurrent is described by the relation

$$I_s = I_c \sin \varphi, \tag{2.1}$$

where  $\varphi$  is the phase difference between the cooper pair wave functions in both electrodes, and  $I_c$  is the **critical current** of the junction. This is known as the DC Josephson effect. He further postulated that applying a voltage V across this junction leads to evolution of  $\varphi$  according to the relation

$$\frac{\partial \varphi}{\partial t} = \frac{2\pi}{\Phi_0} V,\tag{2.2}$$

where  $\Phi_0 = h/2e$  is the magnetic flux quantum. (e is the electron charge, and h is Planck's constant.) This leads to an alternating  $I_s$  (Eq. 2.1) with frequency 2eV/h, resulting in what is known as the AC Josephson effect.

From these relations, it can be shown that the current-voltage relation of the junction has the characteristics of an inductor [47], where

$$V = L(\varphi) \frac{\partial I}{\partial t}.$$

(2.3)

$L(\varphi) = \Phi_0/(2\pi I_c\cos\varphi)$  is the junction's kinetic inductance, where the phase-independent term is referred to as the Josephson Inductance  $L_J = \Phi_0/(2\pi I_c)$ . This kinetic inductance is associated with stored energy  $E(\varphi)$  in the junction analogous to that of a coil inductor.  $E(\varphi)$  is calculated by integrating the electric power  $\int I_s V dt = \int I_s(\Phi_0/2\pi) \ d(\varphi)$  of the circuit, eventually leading to

$$E(\varphi) = E_J(1 - \cos \varphi), \tag{2.4}$$

where

$$E_J = \frac{\Phi_0 I_c}{2\pi} \tag{2.5}$$

is known as the **Josephson Energy**, an important parameter that will be referred to frequently throughout this thesis.

I conclude this introductory subsection with the **Ambegaokar-Baratoff** relation, which states that

$$I_c R_N = \frac{\pi \Delta}{2e} \tanh \frac{\Delta}{2k_B T},\tag{2.6}$$

where  $R_N$  is the **normal state resistance** of the junction,  $\Delta$  is the material-dependent superconducting gap,  $k_B$  is the Boltzman constant, and T is the temperature [48]. For practical values of  $\Delta$  and typical operating temperature of junctions at  $\sim 10$  mK, the tanh term approaches one. The Ambegaokar-Baratoff relation is monumental for any technology that utilizes Josephson junctions as it allows one to infer  $I_c$  through relatively simple room temperature resistance measurements, as well be shown in the remainder of this chapter. Although there may be an offset in  $R_N$  from the measured resistance at room temperature, it can be compensated for as will be presented in Section 2.5.

#### 2.1.2 Transmon qubits

To effectively prepare and manipulate quantum information, a quantum system with well-defined, discrete energy levels is required [49]. Quantum harmonic oscillators are exemplary systems that can be initialized in their ground state and possess equally spaced energy levels. However, this equal spacing renders them inefficient for the task, as distinct energy level differences are necessary for controlled quantum operations. To address this, a non-linear element is introduced to break the equal spacing between energy levels. The Josephson junction serves as an ideal element for this purpose due to its non-linear dependence of  $I_c$ ,  $L_J$ , and  $E_J$  on the phase difference  $\varphi$ , as discussed in the previous section.

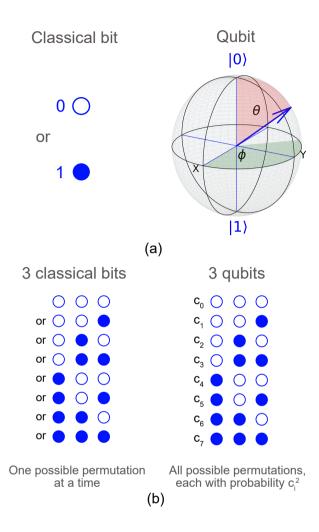

When incorporated into a harmonic oscillator circuit, the Josephson junction transforms the system into an anharmonic oscillator. Figure 2.1(a)-top illustrates the circuit schematic of the transmon anharmonic oscillator [17, 50, 51]. The Hamiltonian governing this circuit is given by:

$$H = 4E_C(\hat{n} - n_g)^2 - E_J \cos \hat{\varphi}, \qquad (2.7)$$

where  $E_C = e^2/2C_{\Sigma}$  is the capacitive charging energy, with  $C_{\Sigma}$  representing the total capacitance, composed of the shunt capacitance  $C_s$  and the junction capacitance  $C_J$ , i.e.,  $C_{\Sigma} = C_s + C_J$ . (Notably, the junction also behaves as a parallel plate capacitor.) Different types of superconducting qubits operate in different  $E_J/E_C$  regimes, and a characteristic feature of the transmon qubit is the large ratio  $E_J/E_C \gg 1$ , which significantly enhances its robustness against charge noise [50]. Typical  $E_J/E_C$  ratios for the transmon qubit are greater than 50.

The energy difference,  $E_{01}$ , between the two lowest energy levels of the transmon qubit, crucial for quantum operations, is given by

$$E_{01} = h f_{01} = \sqrt{8E_J E_C} - E_C, \tag{2.8}$$

where  $f_{01}$  is the qubit's resonant frequency. For a single-junction transmon,  $f_{01}$  is fixed. However, if two junctions are connected in a loop, as shown in Fig. 2.1(a)-bottom, this frequency becomes tunable by threading a magnetic

Figure 2.1: Transmon qubit. (a) Circuit schematic of the transmon qubit. The Josephson junction (blue) has a Josephson energy  $E_J$  and self-capacitance  $C_J$  and is shunted to ground (green) through a shunt capacitor (red) with capacitance  $C_S$ . The top schematic is a fixed-frequency version of the transmon, while the bottom schematic is a tunable-frequency version with the flux  $\Phi$  threading the loop of the two Josephson junctions. (b) SEM image of a transmon qubit, with false colors to match the circuit schematic. The black dashed square highlights where the Josephson junction is. The blue region is the coupling arm of a coplanar waveguide resonator (not shown in (a)). (c) Illustration of a Josephson junction with the superconductor layers typically made of aluminum, and the insulating layer made of aluminum oxide. (d) A Josephson junction (J), galvanically connected by the patches (P) to the capacitor (C) and ground plane (G).

flux  $\Phi$  which tunes  $E_J$  based on the relation

$$E_J(\Phi) = E_{J\text{max}} \cos\left(\frac{\pi\Phi}{\Phi_0}\right) \sqrt{1 + d^2 \tan^2\left(\frac{\pi\Phi}{\Phi_0}\right)}, \tag{2.9}$$

where  $E_{J\text{max}}$  is the sum of the Josephson energies of the two junctions, and  $d = (E_{J2} - E_{J1})/E_{J\text{max}}$  is the junctions asymmetry. This relation will be useful when I address tunable qubits in Section 3.3.

#### 2.1.3 Uncertainty in qubit frequency

Equation 2.8 shows that  $f_{01}$  depends on both  $E_C$  and  $E_J$ . Contributions to  $E_C$  arise from both  $C_J$  and  $C_s$ . In a transmon qubit,  $C_J$  is typically around 1–4 fF, significantly smaller than  $C_s$ , which is approximately 100 fF. Using Eqs. 2.5 and 2.6,  $E_J$  can be expressed in terms of  $R_N$  as

$$E_J = \frac{\Phi_0 \Delta}{4eR_N}. (2.10)$$

The precise control of qubit frequency demands a precise control over  $C_s$ ,  $C_J$ , and  $R_N$ . The latter two are properties of the junction, and their reproducibility depends on the accurate control of the junction area, as well as the thickness uniformity and stoichiometry of the oxide barrier. In contrast,  $C_s$  is determined by a large planar capacitor that is 5–6 orders of magnitude larger than the junction (on the scale of  $\sim 0.5$  mm), as shown in Fig. 2.1(b). Consequently, the reproducibility of the qubit frequency is primarily limited by the Josephson junction.<sup>1</sup> Its small size makes it highly sensitive to dimensional variations, and the dependence of its properties on the uniformity of an oxide layer, approximately 2 nm thick, further complicates the matter. In this thesis, I focus solely on the reproducibility of  $R_N$  for two main reasons. Firstly, both  $R_N$  and  $C_J$  are governed by the same junction parameters, meaning that achieving reproducible  $R_N$  inherently ensures reproducibility in  $C_J$ . Secondly, the small  $C_J/C_s$  ratio implies that any variations in  $C_J$  have a negligible impact on the total capacitance (see Appendix B of **Paper B**).

If we ignore variations in  $E_C$ , the coefficient of variation (CV) in the qubit

<sup>&</sup>lt;sup>1</sup>In Chapter 6, we will see that in the flip-chip architecture, variations in  $C_s$  play a non-negligible role in qubit frequency reproducibility, due to variations in the chip-to-chip spacing.

frequency can be derived as follows. Using Eqs. 2.8 and 2.10, the qubit frequency can be expressed as

$$hf_{01} = \sqrt{2\frac{\Phi_0 \Delta}{eR_N} E_C} - E_C.$$

(2.11)

Using error-propagation rule, the standard deviation in  $f_{01}$ ,  $\sigma_{f_{01}}$ , and the standard deviation in  $R_N$ ,  $\sigma_{R_N}$ , have the relation

$$\sigma_{f_{01}} \approx \frac{1}{2} \frac{f_{01}}{R_N} \cdot \sigma_{R_N}.$$

(2.12)

Finally, the coefficient of variation in qubit frequency  $CV_{f_{01}} = \sigma_{f_{01}}/f_{01}$  relates to  $CV_{R_N} = \sigma_{R_N}/R_N$  via the relation

$$CV_{f_{01}} \approx \frac{1}{2}CV_{R_N}.\tag{2.13}$$

Equation 2.13 serves as our foundation for characterizing the reproducibility of qubit frequency through room temperature characterization of the junction resistance. Although we ignored variations in  $C_s$ , with the level of variation in  $R_N$  achieved in our work, the qubit's total capacitance begins to play a non-negligible role.<sup>2</sup> This aspect will be briefly addressed in this thesis.

# 2.2 Fabrication process

As mentioned earlier, the Josephson junction is essentially two superconductors separated by a week link. The most commonly used type of junctions in superconducting qubits is a sandwich of aluminum/aluminum-oxide/aluminum [Fig. 2.1(c)]. Such a trilayer structure is relatively easy to fabricate with metal deposition and oxidation tools that were developed several decades ago. Simply, deposit a layer of aluminum, oxidize it (or let native oxide grow), then deposit another layer of aluminum. The difficulty, however, is manifested in three caveats. Firstly, both superconducting electrodes must be electrically accessible, separately. Secondly, we need to have precise control over the

$$\sqrt{0.25 \ CV_{R_N}^2 + 0.25 \ CV_{E_C}^2 + 0.0625 \ CV_{R_N}^2 CV_{E_C}^2}$$

<sup>&</sup>lt;sup>2</sup>Additionally considering variations in  $E_C$ ,  $CV_{f_{01}}$  becomes

area of the junction. Finally, the oxide layer thickness in-between the two superconducting layers must be controlled as well. Several techniques have been developed to tackle the first issue [36, 38, 52–56]. The second and third conditions are criteria for precise control over  $E_J$ .

The most commonly used junction fabrication techniques have been the Dolan bridge and the Manhattan style. The former was developed in 1977 [52], while the latter was developed in 1999 [53]. However, other techniques have recently been developed to avoid angular evaporation and lift-off [36, 55, 56. In our research group, we adopted the Manhattan-style junction, and so are all junctions in this work. Figure 2.2 illustrates the process of making Manhattan junctions utilizing shadow evaporation for selective deposition of the two junction electrodes with *in-situ* controlled oxidation. Our choice of the Manhattan junction over the Dolan junction is motivated by its relative simplicity. While in the former, variations in the junction area are caused by lithographic uncertainty and sidewall metal deposition, in the latter, the thickness of the bridge, its height and the possibility of sagging constitute additional sources of variations. Lithographic uncertainties include those attributed to electron-beam lithography exposure, resist development and descumming. Both techniques, however, suffer from systematic drift in their junction size across the wafer, due to the point-source nature of the evaporated metal. More details on sources of deviations in the Manhattan junctions are discussed in Section 2.3.3

### 2.2.1 Wiring layer

Our junctions are typically fabricated after the wiring layer is fully ready. On a qubit wafer, the wiring layer is the base metal, which may include features like coplanar waveguide resonators, qubit capacitors and a ground plane. On a test wafer for calibrating the Josephson junction normal resistance, the wiring layer is typically the contact pads used for four-point probe measurements as will be explained later.

The wafers used in this work are either 2 or 3-inch intrinsic (100) silicon wafers, with resistivity of  $10-20~\mathrm{k}\Omega$  cm. Before any processing, wafers undergo

<sup>&</sup>lt;sup>3</sup>The Dolan-Bridge Josephson junction is named after its inventor, Gerald J. Dolan. In the original work, Manhattan-style junctions were never called by this name. The name was given retrospectively due to their step-like structure, which resembles the grid layout of Manhattan streets.

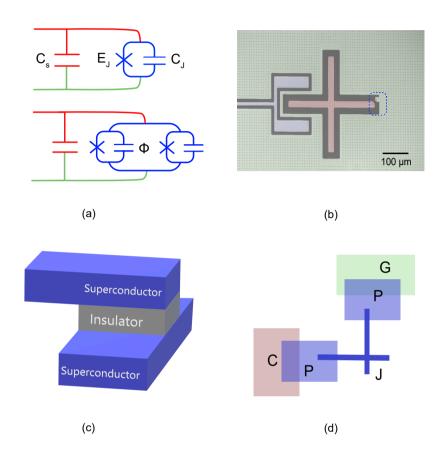

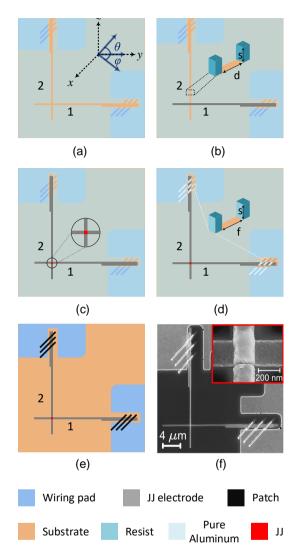

Figure 2.2: Illustration of the fabrication process of Manhattan-style Josephson junctions. (a) Top view of a pattern stack of PMMA/MMA on a silicon substrate after exposure and development. Isometric view of (b) developed stack of PMMA/MMA, (c) evaporation of the first (bottom) junction electrode at 45°, (d) in-situ oxidation of the bottom electrode, (e) evaporation of the second (top) junction electrode at 45° tilt and 90° planar rotation with the respect to the first electrode, and (f) Josephson junctions after oxidation of the top electrode and lift-off. The junction is formed at the overlap between the two electrodes. Note that part of the PMMA/MMA stack is removed from (b)-(e) for better illustration.

the standard cleaning (SC-1) process, where they are dipped in a bath of ammonium hydroxide (NH<sub>4</sub>OH) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) and Deionized (DI) water (1:1:5), heated to 80° for 10 minutes, and then rinsed in DI water.<sup>4</sup> To ensure that our aluminum is grown on a clean silicon substrate, we chose to pattern our wiring layer through etching instead of lift-off. However, before depositing aluminum, the wafer is dipped in a 2% hydrofluoric acid (HF) solution for 1 minute, then rinsed in DI water. This step etches away the native-oxide grown on the silicon substrate. The wafer is then quickly loaded into an aluminum deposition tool (Plassys MEB 550s), where it is pumped to  $\sim 10^{-6}$  mbar in about 10 minutes. The wafer holder is then heated to 300° for 10 minutes to dehydrate the silicon surface and prevent the regrowth of native oxide. After about four hours and when the pressure drops to  $\sim 8 \times 10^{-8}$  mbar, we deposit (150—500 nm) aluminum film at a rate of 1 nm/s. Finally, we chose to controllably oxidize our base metal in-situ. This ensures a cleaner aluminum surface than if it was left to oxidize natively in air. In chapter 3, I will discuss the implications of the different aforementioned treatments on the quality factors of our quantum circuits.

To pattern the wiring layer, we spin-coat a layer of photoresist (typically AZ 1512), which we pattern using a laser-writer tool (DWL 2000 or MLA 150). After resist developing and descumming, aluminum is then wet-etched in Transene-A, a standard wet-etchant of aluminum, containing phosphorice, nitric acid, acetic acid, and DI water. After rinsing in DI water, the photoresist is then stripped using our standard resist stripping and lift-off process, which consists of remover 1165 at 80°C,<sup>5</sup> sonication for 5 minutes in the same remover, sonication for 3 minutes in methanol, and finally sonication for 3 minutes in isopropyl alcohol (IPA).

### 2.2.2 Two-step fabrication process

Our two-step fabrication process of Manhattan junctions is laid out in Fig. 2.2, where junctions are fabricated in one lithography step and a bandage/patch layer is fabricated in an additional lithography step. The patch forms a galvanic connection between the junction electrodes and the rest of the wiring layer [Fig. 2.1(d)] by removing the interfacial oxide, which is known to cause qubit losses [57].

<sup>&</sup>lt;sup>4</sup>We skip the SC-2 process as we observed no effect on the quality of our devices.

<sup>&</sup>lt;sup>5</sup>This is done for at least 10 minutes but may take longer in the case of the lift-off process.

As shown in Fig. 2.2, Manhattan junctions are fabricated using angular evaporation and lift-off process. To ensure a smooth lift-off, sidewall deposition during metal evaporation must not form a continuous film with the junction electrodes. Therefore, it is crucial to form an undercut profile. To achieve such an undercut, we use a resist stack of PMMA (poly methyl methacrylate) on top and MMA (methyl methacrylate) below. This positive resist stack is commonly used for lift-off of metalic structures. Both resists are composed of long polymer chains of carbon atoms, with PMMA having a higher molecular weight than MMA. When the junction features are exposed using an electron beam, the low molecular weight of the MMA compared to PMMA makes it more sensitive to the electron beam breaking down its polymer chains, rendering it easily soluble during the development process. This contrast in sensitivity between the two stack layers creates the necessary undercut profile required for a clean lift-off process.

The process starts with spin-coating of MMA El 12 at 3000 rpm for 1 minute, which is then baked on a hotplate at 160°C for 5 minutes, resulting in a  $\sim$  700-nm-thick layer. Then PMMA 950 A6 is spincoated at 6000 rpm for 1 minute, which is then backed on a hotplate at 160°C for 5 minutes, which results in a  $\sim$  250-nm-thick layer [58]. Features are exposed in EBL - JEOL JBX 9300FS or Raith EBPG 5200 electron-beam lithography (EBL) systems; both with 100 kV acceleration voltage. Since PMMA is less sensitive than MMA to electron beam, it controls the minimum required dose for exposure. The base dose used is 1600  $\mu \rm C/cm^2$  on average after implementing proximity error correction (PEC), which accounts for electron scattering during the exposure. Junctions are exposed with a beam current of 2–10 nA.

The exposed features are then developed in a solution of MIBK:IPA 1:1 for 90 seconds, rinsed in IPA for 30 seconds, then immediately blow dried with  $N_2$ . Before depositing the junctions, the exposed features are descummed with oxygen plasma in a reactive-ion etching (RIE) system at low power, calibrated to remove  $\sim 10$  nm of resist. Removing the resist residues before junction deposition is crucial for qubit coherence, and to avoid junction aging [57, 59].

The wafer is subsequently loaded to Plassys for junction formation. The first junction electrode is created by depositing 50 nm of aluminum at a 0° planetary rotation and  $45^{\circ}$  tilt. Accounting for the tilt, the final thickness of the bottom electrode is  $45 \times \cos(45^{\circ}) = 35$  nm. To form the tunnel barrier, we oxidize the bottom electrode under a specific pressure and time, which I

will discuss in Section 2.3.4. The top junction electrode is then deposited at  $90^{\circ}$  planetary angle and  $45^{\circ}$  tilt with a final thickness of 78 nm. The standard deposition rate of junction electrodes is 1 nm/s. Finally, the surface of the two junction electrodes is controllably oxidized *in-situ*, similar to the wiring layer's base aluminum. Junctions then undergo the standard lift-off process in remover 1165.

Patches are subsequently fabricated using the same lithography process and similarly deposited in Plassys. However, before deposition, the aluminum oxide  $(AlO_x)$  on the junction electrodes and the wiring layer is milled away in-situ using a normally incident  $Ar^+$  beam that is neutralized before hitting the substrate to avoid charge accumulation. More than 10 nm of  $AlO_x/Al$  is removed to ensure a galvanic connection between the junction electrodes and wiring layer when depositing the patches. The milling calibration for our process can be found in [60]. The patches are typically 200-nm thick.

Angular evaporation imposes limitations on the junction sizes that can be formed. These limitations depend on the resist height s and tilt angle  $\phi$  [Figs. 2.3(a) and 2.3(b)]. The maximum junction electrode width d is given by  $s/\tan(\phi)$ . Since  $\phi=45^{\circ}$  and s=950 nm, the maximum junction electrode width is 950 nm. In practice, this limit is well below  $s/\tan(\phi)$  to avoid aluminum deposition in the undercut region. For a typical undercut of 200 nm, the maximum electrode width that avoids this residual deposition is 750 nm. Typical junction sizes used in our qubit devices are below this limit.

# 2.2.3 Patch-integrated cross-type junctions

As mentioned earlier, a galvanic and superconducting connection between the junction electrode and the wiring layer was proven to be crucial for qubit coherence [57]. However, making patches in an additional lithography step is a lengthy process that consumes valuable resources, increases the probability of error, and exposes the loss-sensitive junction area to additional processing. Therefore, we invented the patch-integrated cross-type (PICT) junction to mitigate those three issues, which is presented in **Paper A**.

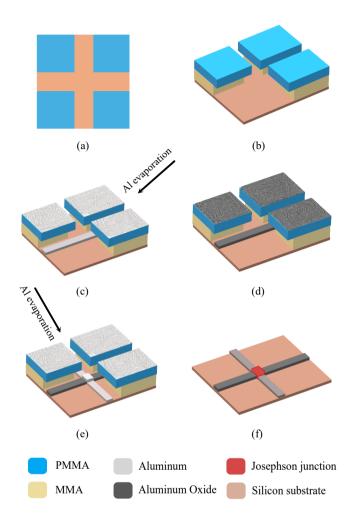

The idea behind the integrated patch initiates from the Manhattan-style junction itself. We again utilize the selectivity of angular evaporation to different patterned trenches, except that this time, we add a third trench at a 45° tilt between the two junction electrodes to form the patches. The process steps are illustrated in Fig. 2.3. The 45° fringes overlap with the junction

electrodes and the wiring layer.

The lithography steps of patterning the PICT junctions are identical to the process explained in Section 2.2.2. Deposition of the junction electrodes [Figs. 2.3(b) and 2.3(c)] is also identical to that explained in Fig. 2.2. For the PICT process, we subsequently mill away  $AlO_x/Al$  at 45° planetary rotation and 45° tilt using an Ar+ beam [Fig. 2.3(d)]. At the same angles, aluminum patches are deposited in the fringes to form the galvanic connection, followed by a final protective oxide [Fig. 2.3(e)]. PICT junctions are similarly lifted-off in remover 1165. Fig. 2.3(f) shows an SEM image of the PICT junction after lift-off.

Similar to the two-step process, PICT junctions are limited in size. However, the limitation here is more stringent due to the addition of the fringes. The maximum junction electrode width that avoids undesired aluminum deposition on the junction electrodes trenches during milling and deposition of the patches is  $d=s\times\cos(\zeta)/\tan(\phi)$ , where  $\zeta$  is the angle between the fringes and the two junction electrodes. Since  $\zeta$  is always 45° and  $\phi$  is set to 45° in our case, the maximum d is 670 nm. Accounting for an undercut of 200 nm, the maximum d becomes 470 nm. Finally, I would like to note that, although we use three fringes per junction electrode, it is possible to pattern only one fringe, as was replicated in [61] and [62]. This may alleviate concerns about superconducting loops trapping flux near the qubit.

# 2.3 Reproducibility of R<sub>N</sub>

The focus of this section is on the reproducibility of Josephson junctions  $R_N$  and its impact on qubit frequency targeting. To ensure robust statistical analysis, all studies discussed here are conducted at the wafer scale. First, I start with laying out the standard designs and measurement infrastructure for characterizing  $R_N$ . Then, I present our baseline PICT junctions reproducibility and investigate the potential sources of variations. I end this section with our lowest achieved wafer-level standard deviation of 2% in  $R_N$ .

# $2.3.1\ R_N$ characterization setup

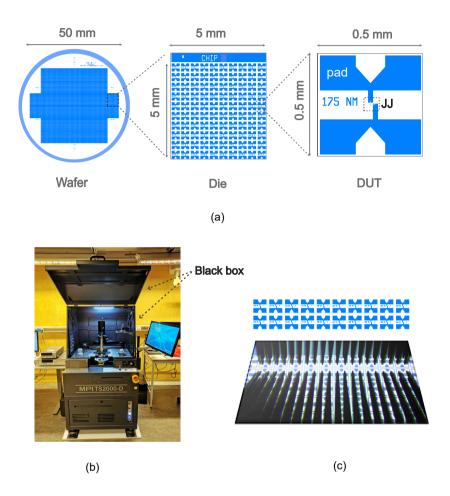

The junction resistance  $R_N$  is measured using a 4-point-probe setup. A standard wafer layout is shown in Fig. 2.4(a). Each wafer contains 40 5×5 mm<sup>2</sup>

Figure 2.3: PICT junction process steps. (a)-(e) Schematic of the PICT process flow, showing the layout after (a) development, (b) first electrode deposition and oxidation to form the tunnel barrier, (c) second electrode deposition and oxidation, (d) ion milling of the aluminum oxide at the fringes, and (d) deposition of the patches.  $\theta$  and  $\phi$  are the planetary and tilt angles of the sample holder, respectively. Deposition of Al on top of the resist is not shown for clarity. (f) SEM image of a fabricated junction with the patch layer.

dies, and each die contains 100 Devices Under Test (DUT). Each of the four pads of a DUT is  $150\times150~\mu\text{m}^2$ , and the junction lies in the middle. In total, each wafer contains 4000 test devices, with each row of a die containing 10 different junction sizes, ranging from  $100\times100$  to  $400\times400$  nm<sup>2</sup>. All junctions in this thesis are formed by two perpendicular electrodes with the same nominal design width.

Junctions are then characterized in an automated probe-station MPI TS2000 [Fig. 2.4(b)], where a probe card containing 80 pins (4 pins for each DUT) measures  $R_N$  of 20 DUTs during a single touchdown [Fig. 2.4(c)]. Each vertical DUT pair is measured simultaneously with two different SMUs of a single Keithly 2612b sourcemeter, that iterate over each pair sequentially via a Keithley 3706A-S system switch. After measuring each block, the probe card moves to the following block of 20 devices. All measurements are current biased, where the current is swept between  $-1\mu$ A to  $1\mu$ A through a vertical pair of pins on a DUT, and the voltage drop is measured across the other pair of pins. For each DUT, an I-V curve has 20 points that are fit linearly to extract the slope  $R_N$ . For each  $R_N$ , there is an associated  $r^2$  representing the coefficient of determination (or goodness of fit). DUTs with  $r^2$  below 0.99 are excluded from our statistics.

### 2.3.2 PICT-junctions reproducibility

To qualify PICT as a standard process for fabricating superconducting qubits, we characterized both qubit coherence and  $R_N$  reproducibility. Coherence is discussed in Chapter 3. Here, I present our study on  $R_N$  reproducibility.

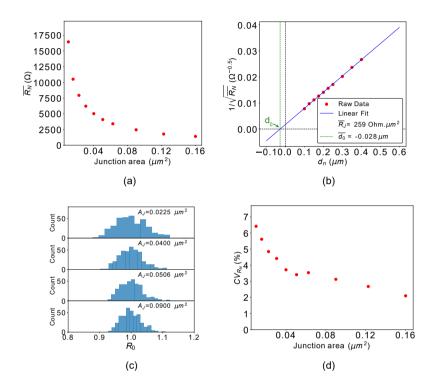

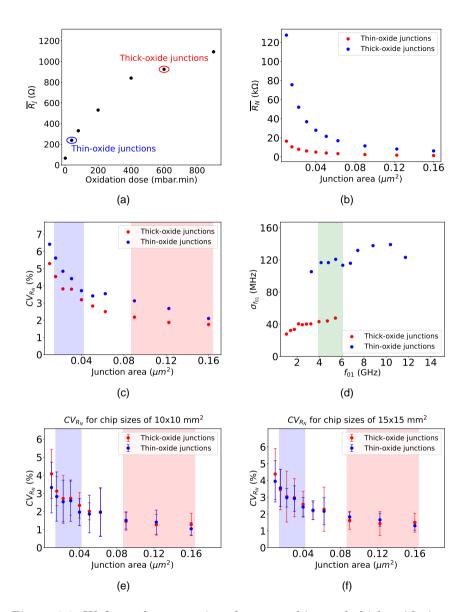

The dependence of  $\overline{R_N}$  (mean  $R_N$ ) on junction area is shown in Fig. 2.5(a).  $R_N$  is given by  $R_J/A_J$ , where  $R_J$  is the junction's resistance per unit area, and  $A_J$  is the junction area. To account for the lithography bias in the junction area,  $R_N$  can be expressed in terms of the junction width  $d_J = d_n - d_0$  as  $R_N = R_J/(d_n - d_0)^2$ , where  $d_n$  is the nominal design width and  $d_0$  is the bias in junction width, to account for the deviation from the nominal. To better illustrate  $R_J$  and  $d_0$ , Fig. 2.5(b) shows a fit of  $1/\sqrt{\overline{R_N}}$  versus  $d_n$ . The slope s of such a fit reveals  $R_J$  as  $1/s^2$ , while the intersection with the x-axis is  $d_0$ . The extracted  $R_J$  for the junctions shown in the figure is 260  $\Omega \cdot \mu m^2$ , while  $d_0$  is -28 nm.  $^6$

<sup>&</sup>lt;sup>6</sup>In **Paper B**, we reported  $R_J$  to be 240  $\Omega \cdot \mu \text{m}^2$ ; however, that value, incorrectly, did not account for the bias  $d_0$ .

Figure 2.4: Josephson junction characterization design and setup. (a) Layout of the wafer, die and DUT. (b) A picture of the MPI TS2000 automated probe station, equipped with a black box to shield the DUTs from light during measurements. (c) A block of  $10\times2$  DUTs measured by an 80-pin probe card.

Figure 2.5: Wafer-level reproducibility of PICT junctions. (a) Mean  $R_N$  as a function of the junction area. (b)  $1/\sqrt{\overline{R_N}}$  as a function of junction nominal design width  $d_n$ . The junction unit area resistance  $R_J$  is given by  $1/s^2$ , where s is the slope of the linear fit. (c) Histograms of the normalized resistance  $R_0 = R_N/\overline{R_N}$  for four different junction areas. (d) Dependence of  $R_N$ 's coefficient of variation  $(CV_{R_N})$  on junction area  $A_J$ .

Histograms of the normalized resistance,  $R_0 = R_N/\overline{R_N}$ , are shown in Fig. 2.5(c), resembling normal distributions with Kolmogorov-Smirnov p-values of 0.52, 0.83, 0.44 and 0.21 from top to bottom, respectively [63]. One clearly notices the narrowing of the distribution of these histograms from smaller to larger junction sizes, meaning that larger junctions are more reproducible in their resistance. The coefficient of variation in  $R_N$ ,  $CV_{R_N}$  (also referred to as the relative standard deviation), is shown in Fig. 2.5(d) as a function of the junction area  $A_J$ . Such reproducibility levels were on par with the best reported  $R_N$  reproducibility levels (see Table II in **Paper A**).

## 2.3.3 Decoupling sources of variations in $R_N$

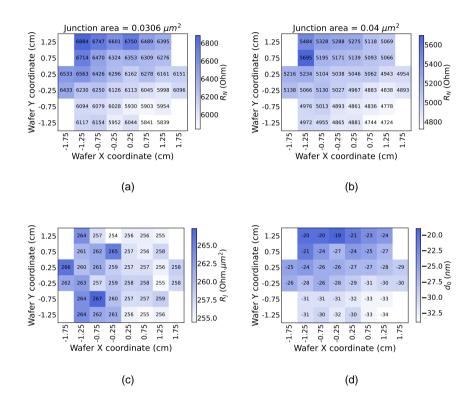

The spread in  $R_N$  is attributed to both non-uniformity in oxide-barrier thickness, and variations in the junction area  $A_J$ . The latter affects  $R_J$  and it depends on the *in-situ* oxidation conditions, surface morphology, and grain size of the bottom electrode. Variations in  $A_J$  are attributed to lithographic uncertainties in exposure, development, descumming and sidewall deposition, and angular evaporation of aluminum electrodes. Figures. 2.6(a) and 2.6(b) show wafer heatmaps of the measured  $R_N$  for two different junction sizes.

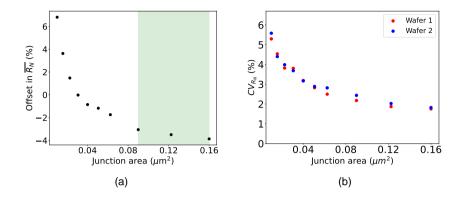

To decouple these two sources of variations, the heatmaps in Figs. 2.6(c) and 2.6(d) show the extracted  $R_J$  and  $d_0$ , respectively. The inter-chip standard deviation in  $R_J$  is 3.3  $\Omega \cdot \mu \text{m}^2$  ( $CV_{R_J}=1.3\%$ ), while  $d_0$  has a standard deviation of 4 nm. While the gradient in  $d_0$  can be explained by sidewall deposition and angular evaporation [39], the gradient in  $R_J$ , albeit small, is not readily understood. Since  $R_J$  depends on the surface morphology, the surface of the bottom electrodes on the left side of the wafer could lead to a thicker tunnel-barrier oxide, hence, higher  $R_J$ . The rougher surface on the left side of the wafer could be attributed to the steeper deposition angle compared to the right side [34].

Another method of decoupling the two sources of uncertainties is to fit the  $CV_{R_N}$  data in Fig. 2.5(d) to the model proposed in **Paper A**, where

$$CV_{R_N}^2 = CV_{R_I}^2 CV_{A_I}^2 + CV_{R_I}^2 + CV_{A_I}^2. (2.14)$$

Since  $CV_{A_J} = \sigma_{A_J}/A_J = 2\sigma_{d_J}/\sqrt{A_J}$ , one extracts  $CV_{R_J}$  of 1.8%, and  $\sigma_{d_J} = 4$  nm. This comes to a close agreement with the previous method, with the higher value of 1.8% instead of 1.3% in  $CV_{R_J}$ . One important difference

Figure 2.6: Wafer-level heatmaps of junction resistance. (a) and (b) Wafer heatmaps of the measured  $R_N$  for two different junction sizes. (c) and (d) Wafer heatmaps of the extracted junction's resistance per unit area  $R_J$ , and the bias in junction width  $d_0$ , respectively.

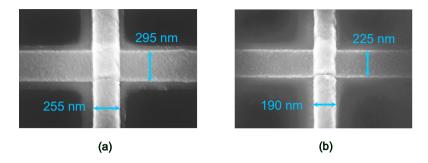

Figure 2.7: Difference in electrode width due to sidewall deposition. SEM images of two junctions, designed to be nominally the same width, where the junction in (a) is near the center of the wafer, and the junction in (b) is near the edge. The difference in their measured widths is an artifact of the angular evaporation.

between the two methods is that in the second method,  $CV_{R_J}$  is calculated between all individual junctions on the wafer, leading to a higher spread than taking the mean  $R_J$  of each chip and then calculating the standard deviation.

Although both methods provide an insightful understanding of the two sources of uncertainty in  $R_N$ , we consider them qualitative models since they rely on two imperfect assumptions. The first assumption is that  $R_J$  is independent of  $A_J$ . The second assumption is that the junctions have square areas. While junctions are designed to be so, the deposition of the first (bottom) electrode causes sidewall deposition on the resist wall of the second (top) electrode, resulting in a narrower top junction electrode [37]. Specifically, near the center of the wafer, the width of the top electrode is  $t_b \times \cos(45^\circ)$  narrower than the bottom electrode, where  $t_b$  is the nominal thickness of the bottom electrode (50 nm in our case). This results in the top electrode being approximately 35 nm narrower than the bottom one. This difference varies as we move away from the center since the deposition angle deviates from 45°. Figure 2.7 shows SEM images of two junctions, which were designed to be nominally the same, but in practice, their width differs.

For accurate separation of the two error sources, a comprehensive wafer-

scale SEM analysis of junction dimensions is essential. This process can be greatly accelerated by utilizing automated SEM machines, which are capable of scanning thousands of junctions within a few hours. To better understand the uncertainty in  $R_J$ , a deeper comprehension of the uniformity of oxide barrier thickness and its relationship with junction area is required. However, achieving this is more complex, as conducting statistically significant TEM studies on the tunnel barrier is resource-intensive. Furthermore, linking oxide barrier thickness to  $R_J$  requires modeling the thickness distribution within the barrier [64].

### 2.3.4 Larger, thick-oxide Josephson junctions

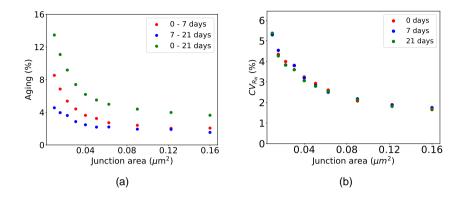

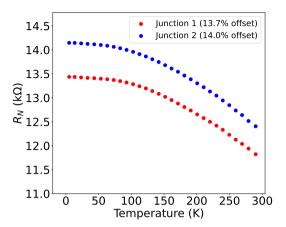

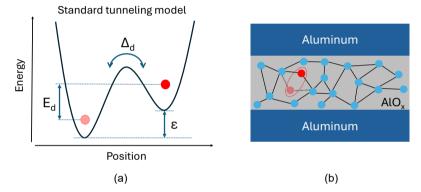

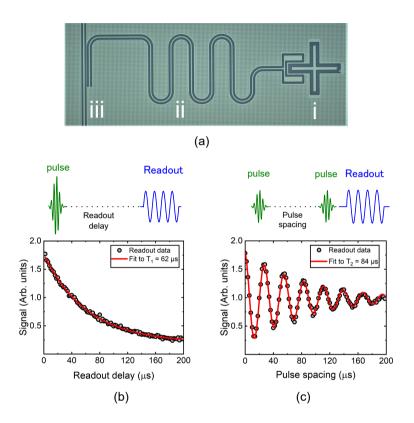

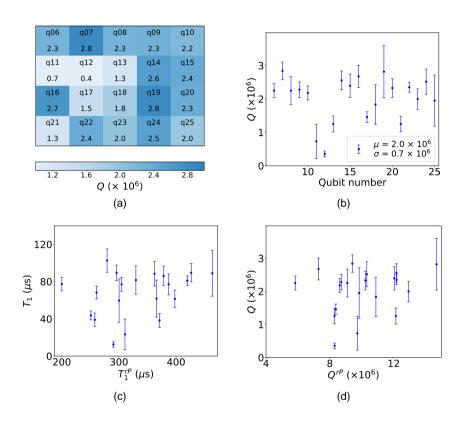

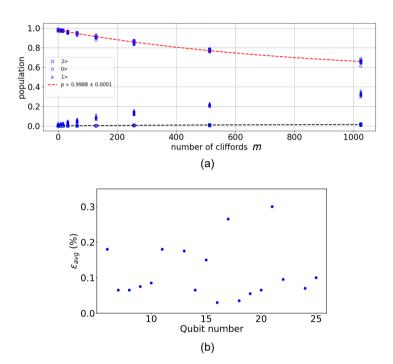

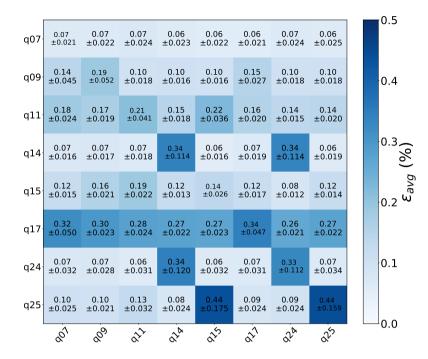

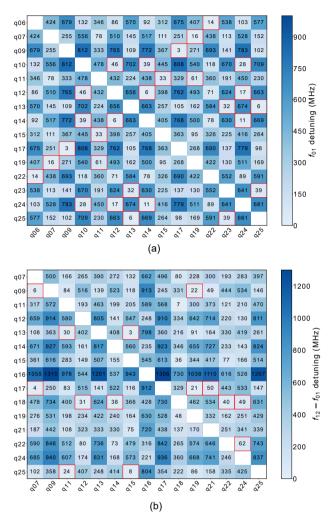

To scale beyond a few tens of qubits in a quantum processor, better reproducibility of junction fabrication is required compared to the values reported in Section 2.3.2.<sup>7</sup> To achieve a lower spread in  $R_N$ , in **Paper B**, we proposed fabricating junctions with larger areas. As Fig. 2.5(d) shows, the larger the junction area is, the lower  $CV_{R_N}$  becomes, due to the lower sensitivity to lithographic errors. There, the low spread in  $R_N$  for larger junctions was not utilized, as qubit junctions had small areas between 0.02–0.04  $\mu$ m<sup>2</sup>. This size range is limited by the target  $R_N$  required to satisfy a typical transmon qubit frequency range between 4 and 6 GHz.