#### Characterisation of Dynamic Effects in Compact GaN Microwave Front Ends

ANDREAS DIVINYI

Microwave Electronics Laboratory

Department of Microtechnology and Nanoscience – MC2

Chalmers University of Technology

Göteborg, Sweden, 2024

#### Characterisation of Dynamic Effects in Compact GaN Microwave Front Ends

ANDREAS DIVINYI

#### © Andreas Divinyi, 2024

Chalmers University of Technology

Department of Microtechnology and Nanoscience – MC2

Microwave Electronics Laboratory

SE-412 96 Göteborg, Sweden

+ 46 (0) 31-772 1000

ISSN 1652-0769 Technical report MC2-467

Printed by Chalmers Reproservice Göteborg, Sweden 2024

# **Abstract**

GaN HEMT technology exhibits dynamic behaviour due to thermal and electrical memory effects, which reduce the performance of GaN MMICs used in compact microwave front ends. Addressing these challenges requires careful characterisation under realistic operating conditions to identify, mitigate, or compensate for these effects. This thesis investigates the thermal and electrical effects in two main ways.

The characterisation of thermal effects focuses on accurately monitoring on-chip hotspots caused by high-power operations. The surrounding thermal environment, including packaging and thermal management components, complicates this task. The proposed solution involves the use of on-chip sensors integrated into both dedicated test structures and actual circuits, enabling real-time, package-independent, and electrical measurements for thermal characterisation of device operation.

The trapping-induced effects risk unpredictable performance degradation, especially in GaN HEMT switch devices, where drift conditions are not yet fully characterised. The second part of this thesis aims to develop a method for determining the impact of trapping on the recovery time of GaN HEMT switches used in frontend applications. This method quantifies the effects of recovery, allowing for comparing different devices and technologies.

Keywords: GaN MMIC, Thermal, Transient, HEMT, Dynamic effects, Trapping

# List of Publications

#### **Appended Publications**

This thesis is based on work contained in the following papers:

- [A] A. Divinyi, T.M.J. Nilsson, N. Rorsman, T. Kristensen, H. Hultin, S.E. Gunnarsson and M. Thorsell, "On-Chip Sensors for Temperature Monitoring of Packaged GaN MMICs", IEEE Transaction on Components Packaging and Manufacturing Technology, 2024

- [B] A. Divinyi, N. Rorsman, N. Billström and M. Thorsell, "Transition Time of GaN HEMT Switches and its Dependence on Device Geometry", IEEE European Microwave Integrated Circuits Conference, Sept. 2023

- [C] A. Divinyi, N. Rorsman, N. Billström and M. Thorsell, "Short Term Drift in the Recovery Time of GaN HEMT Switches", *IEEE European Microwave Integrated Circuits Conference*, Sept. 2024

#### Other Publications

The content of the following publications partially overlaps with the appended papers or is out of the scope of this thesis

- [a] T. Kristensen, A. Divinyi, J. Bremer, Torbjörn M.J Nilsson, M. Thorsell, "Thermal Transient Measurements of GaN HEMT Structures by Electrical Measurements", IEEE European Microwave Integrated Circuits Conference, 2023

- [b] T. Kristensen, T.M.J. Nilsson, A. Divinyi, J. Bremer, M. Thorsell, "Characterization and Modeling of Dynamic Thermal Coupling in GaN MMIC Power Amplifiers", 2024 IEEE/MTT-S International Microwave Symposium – IMS 2024, Washington DC, USA, 2024

- [c] T. Kristensen, T.M.J. Nilsson, A. Divinyi, J. Bremer, M. Thorsell, "Dynamic Thermal Coupling in GaN MMIC Power Amplifiers", Accepted 2024 T-MTT

- [d] T. Kristensen, T.M.J. Nilsson, A. Divinyi, J. Bremer, M. Thorsell, "Numerical Modeling of Dynamic Thermal Coupling in GaN HEMTs Calibrated by Transient Measurements", T-ED

# Contents

| 1 | Abstract                                             | iii |

|---|------------------------------------------------------|-----|

| 2 | List of Publications                                 | v   |

| 3 | Introduction                                         | 1   |

| 4 | GaN in Radar Systems                                 | 3   |

|   | 2.1 Monolithic Microwave Integrated Circuits (MMICs) | 5   |

|   | 2.2 Integration of GaN MMIC                          | 6   |

| 5 | Thermal Characterisation of GaN MMIC                 | 7   |

|   | 3.1 Temperature in Packaged GaN MMIC                 | 8   |

|   | 3.2 Temperature Measurements                         | 9   |

|   | 3.2.1 Optical Measurement Techniques                 |     |

|   | 3.2.2 Electrical Sensors                             |     |

|   | 3.2.3 Thermal Test Structures                        | 11  |

|   | 3.3 Thermal Modeling                                 | 13  |

| 6 | Memory Effects in GaN                                | 17  |

|   | 4.2 Amplifiers                                       | 18  |

|   | 4.3 Front End Switches                               | 19  |

|   | 4.4 Compensating for the Impact of Memory Effects    | 23  |

| 7 | Conclusions                                          | 25  |

|   | Future Work                                          | 26  |

| 8 | Acknowledgements                                     | 27  |

# Chapter 1

# Introduction

Radar technology is vital in an insecure world where its role in defence systems for object detection is pivotal [1]. There has been a clear trend towards the adoption of digital technology in radar systems, in part replacing highly specialised analogue components with more versatile off-the-shelf solutions such as Field Programmable Gate Arrays (FPGAs) and CPUs for signal processing [1]. This added processing power offers advantages, such as increased versatility in designing microwave systems. This has led to further developing microwave systems such as active electronically scanned arrays (AESA), which relies on multiple compact microwave front ends or transmitter and receiver modules (TRMs). These have been enabled using solid state components (SSD) such as gallium nitride (GaN) high electron mobility transistors (HEMTs) due to their ability to provide high output powers at microwave frequencies.

GaN HEMT is a commercially available technology but remains a vibrant research area with numerous challenges and possible improvements. Firstly, with demonstrated power densities in GaN HEMT devices up to 24.4 W/mm [2] at X-band has been accomplished with additional effort dedicated to further increasing the breakdown voltage [3]. Secondly, through scaling the size of the device dimensions, such as the gate length reaching 40 nm [4] and even 20 nm [5], thus improving the cut-off frequency  $f_T$ , which has enabled GaN HEMTs to be operated at frequencies up to 200 GHz [3]. Furthermore, as part of a continuous desire to reduce size and weight, as seen in the integration of GaN HEMTs with new or existing technologies, either through heterogeneous integration [3], [6] or the development of GaN on Si [7], [8].

However, increasing the level of integration and power density causes challenges with thermal effects and trapping contributing to dynamic behaviour, which degrade device performance [9] and reliability [10]. Similarly, a well-known challenge with GaN technology is the presence of time-dependent memory effects caused by electron trapping. This causes the device to be partly dependent on previous bias and operating conditions [11]. The fundamental principles of memory effects are well understood in terms of, e.g., trapping where electron states in the semiconductor are charged and discharged. However, the current transistor models do not always capture the gradual time-dependent behaviour associated with both trapping and thermal effects, which constitutes a considerable challenge [12]. This has been

CHAPTER 1. INTRODUCTION

demonstrated to degrade both amplifier operation [5] and switch operation [13], [14] which all contribute to decreasing system performance.

These are, therefore, significant challenges in the context of multifunctional GaN microwave front ends. Consequently, it is essential to have methods for characterising dynamic effects caused by thermal and trapping in GaN HEMTs. Chapter 3 discusses on-chip sensors compatible with packaged devices for temperature monitoring and thermal characterisation of GaN HEMTs during operation. This is approached by using sensors based on GaN resistor, which can be readily integrated into MMIC circuits, and which is compatible with most processes. The sensors concept is demonstrated using a thermal test structure which reflects the use of the sensor by dissipating power thus causing an increase in temperature captured using the sensor. Furthermore, the impact of trapping on device performance is investigated in Chapter 4, focusing on GaN HEMT switch devices intended for front-end operation, a topic often neglected in favour of the more common amplifier-relevant use cases. Investigating the impact of device geometry and technology choices for the switch time degradation caused by recovery. By characterising these effects could help designer decreasing the sensitivity to dynamic effects as well as to better predict the behaviour of compact GaN MMIC transceivers.

# Chapter 2

# GaN in Radar Systems

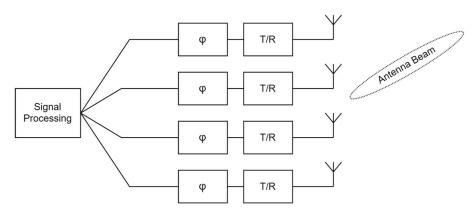

Increasing the level of integration using GaN poses some challenges with dynamic effects but has considerable advantages. Depending on the specific application and platform limitations, numerous considerations are required for implementing the microwave front end. For example, size, weight and power (SWaP) requirements pose exceptionally high demands for compact designs. These demands have been met by replacing older magnetron and travelling wave tubes (TWT) with SSDs, which are significantly smaller and lightweight [1]. The reduced size has been one enabling factor for the success of AESA, systems which rely on multiple TRMs. Using multiple TRMs, signal processing allows for electrical beam steering by introducing different phase delays  $\varphi$  in the systems. Instead of physically aiming the antenna in the direction to transmit and receive signals from, in an AESA. The TRMs can be configured to achieve this through clever use of additive and negative interference from the different elements, the combined signal that is radiated, i.e. the sum of all the radiated energy from the antenna [1], will act as an antenna directed in a particular direction (Figure 1).

**Figure 1** Illustration of AESA, different elements each containing an antenna, transmit/receive module and phase shifter function. Resulting signals are summed and processed.

Additional advantages of this include increased resilience to system breakdown. Previously, if just one transmitter breaks, the whole system goes down. Instead, with tens to thousands of TRMs, it is possible to achieve a graceful degradation, with each broken TRM having a limited impact on system performance. This decreases the urgency of system repair and ensures that some functionality remains instead of a critical failure occurring. Previously, AESAs relied on analogue equipment to introduce the necessary phase delays. Still, with the increasing performance and capabilities of FPGAs, it is possible to digitise the different channels, which enables a greater degree of freedom in both design and operation. Thus, opening up for new high-performance radar systems with the potential of realising new exciting applications with even smaller form factors while simultaneously making use of the increased processing power using technologies such as artificial intelligence (AI) and machine learning (ML).

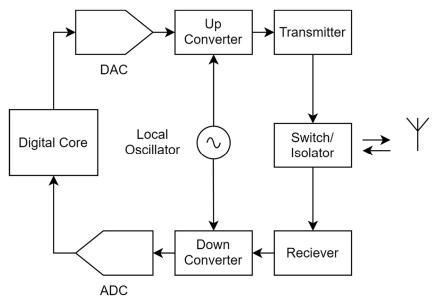

Modern microwave systems (Figure 2) can, therefore, be described as consisting of a digital core, including the digital signal processor (DSP), which processes sensor data. Starting from a digital waveform, the radar signal can be converted to and from an analogue signal using a digital-to-analogue converter (DAC) and analogue-to-digital converter (ADC) [1]. Currently, it is still necessary for the signal to require up conversion from an intermediate frequency (IF) to the desired microwave frequency using an up converter and a down conversation back to be processed by the digital core. However, the frequency at which DACs/ADCs operate steadily increases, and devices operating for lower GHz signals are readily available.

**Figure 2** Example Microwave System containing parts necessary to go from digital to analog signals and to both transmit and receive these.

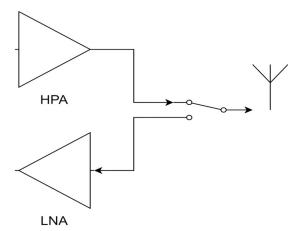

Similarly, one system critical component is the front end, which enables the transmission and reception of microwave signals and typically includes two amplifiers. Firstly, the High-Power Amplifier (HPA) for amplifying the signal for transmission, especially important in radar applications is to maximise the available output power in order to increase range and increasing the signal to noise ratio (SNR). Secondly a Low-Noise Amplifier (LNA) to amplify and maintain the integrity of the received signal by minimising the noise in order to extract useful information. These two functions are frequently consolidated into a single TRM that uses one antenna, with a switch or circulator to select between sending and receiving modes, as illustrated in Figure 3.

**Figure 3**. An example transceiver consists of LNA, HPA and a switch before the antenna to select between the two for outgoing or incoming signals.

# 2.1 Monolithic Microwave Integrated Circuits (MMICs)

Therefore, the choice of technology is critical to fulfilling all the requirements from performance to size. GaN HEMT technology is currently the primary alternative for high-power applications at microwave frequencies. The key technical advantage of using SSD for compact and lightweight transceiver design is realised through a monolithic microwave integrated circuit (MMIC) with the components manufactured directly from a substrate using photolithography [15]. Thus, MMIC enables a designer to realise entire circuits and functions on a single chip, such as a GaN transceiver. However, the design of a GaN MMIC transceiver requires appropriate MMIC processes with high overall performance. The viability of this approach was demonstrated with Saab and Raytheon winning the Aviation Week Laureate Innovation Award in 2015 for their work with GaN in a defence setting and pioneering the use of the technology in products [16] and emerged from a series of works demonstrating a process aimed at transceiver functionality [17]. The demonstration of individual building blocks [17] and the subsequent demonstration

of a GaN MMIC front end has since further demonstrated the validity of the concept [18], [19].

Further advancements in GaN MMIC have improved performance [20] and the state-of-the-art GaN on SiC MMIC chipsets for transceiver design for military applications, including scaled-down devices and increased power densities [21]. GaN transceivers have been implemented for a wide array of applications such as 5G [25], synthetic aperture radar (SAR) [26] and use for satellites [22]. Other trends includes, for example, the DARPA DREaM program investigating novel epitaxial structures [23].

A limitation that needs consideration is the design of the LNA and front-end switch in GaN MMIC technology. For example, the noise figure in GaN LNAs has historically been considerably higher than alternatives such as gallium arsenide (GaAs) [24]. However, the use of GaN in LNAs also presents some attractive advantages, such as utilising the material's robustness, which allows the LNA to survive higher input powers and maintain linearity at comparably higher input powers [25]. This is highly relevant since the receiver can be subject to unintentional and intentional jamming. Previously, this was only possible by including protective circuitry such as limiters, which is commonplace to protect technologies that are more sensitive than GaN but at the cost complexity and, in some instances, also size.

#### 2.2 Integration of GaN MMIC

Since, size is an essential consideration as miniaturisation is in demand, and continuous efforts are being made to increase the integration of components, including the GaN microwave front end. One approach to this is GaN-on-Si MMIC processes that could provide the potential for further integration with Si technology at the cost of thermal performance, e.g., at the risk of decreasing output power [26]. A similar level of integration could also be achieved through the heterogeneous integration of GaN and Si for example attaching two different wafers to each other [27].

Circuits utilising both Si and GaN transistors have yet to be widely adopted. This could be partly due to difficulties achieving high performance using this approach and the added complexity of additional manufacturing steps. An alternative to this could be improvements and advancements in technologies similar to or further developments of multi-chip modules (MCM) or chiplets, which are compact multichip packages consisting of an interposer or similar to host the different chips with the potential of including GaN [6] [28].

Furthermore, as GaN HEMT transceivers are increasingly adopted in more sophisticated applications, the need to properly characterise individual aspects of the GaN front end from the impact of epitaxial structure, device processing, circuit design and packaging increases. Part of this is the careful characterisation of the dynamic effects in a relevant context for GaN transceiver operation to fully capture the different use cases.

# Chapter 3

# Thermal Characterisation of GaN MMIC

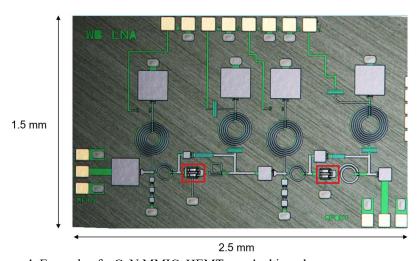

Self-heating is present in all microwave devices to a certain extent and is an inherent consequence that efficiency can never reach 100%. Consequently, some energy is inevitably converted to heat. Despite being able to withstand higher temperatures than the alternatives, thermal effects are still a concern for GaN HEMT devices [9], [10]. Even though GaN HEMTs comprise only a fraction of the MMIC chip surface, they comprise most of the dissipated power (Figure 4). In the HEMTs, most of the heat is generated right next to the gate on the drain side, where the electric field becomes strong in a common source configuration [29]. These localised heat sources pose challenges for characterisation and risk reducing long-term reliability [9], [10].

Figure 4. Example of a GaN MMIC, HEMTs marked in red.

Conduction is the dominant process of heat transfer closest to the active device, with heat spreading laterally and vertically into the rest of the epitaxial structure and the surrounding package. The device performance is correlated with temperature, the

amount of power dissipated during operation, and the capacity of the surrounding chip and packaging to transfer the heat away from the device are essential [30]. Additionally, thermal behaviour is an essential input for the device model since it considerably impacts device performance and contributes to memory effects. It is, therefore, imperative to gain insight into the impact of device operating conditions on temperature and evaluate the effectiveness of thermal management [30]. To account for the temperature of e.g., a pulsed HPA requires a method that capture the dynamic behaviour which is non-trivial but essential to predict performance. This chapter explores the challenges and solutions associated determining device temperature, focusing on GaN MMIC.

#### 3.1 Temperature in Packaged GaN MMIC

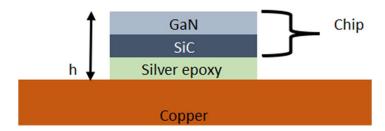

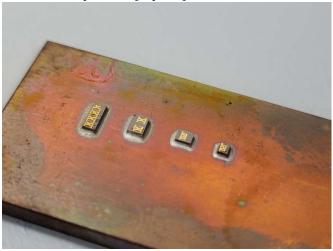

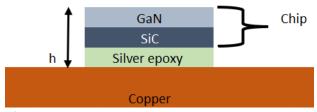

Packaging of microelectronics protects chip physically and also acts as the thermal environment. It is also especially important to consider for high power semiconductors such as GaN since an estimated 30% of the temperature increase during operation can be attributed to packaging [31]. This is essential since thermal management and packaging are usually application-specific. It is therefore of interest to evaluate circuit performance and be able to monitor temperature in a relevant setting such as the specified packaging environment, one possible packaging could be copper coin/heatsink, such as in Figure 5.

**Figure 5.** GaN chip mounted on copper carrier using a silver epoxy TIM [Paper A]

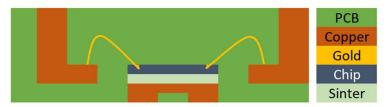

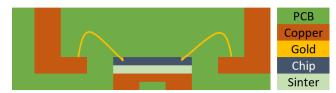

The temperature is especially problematic for highly integrated systems since high-power components such as the power amplifier are close to the temperature-sensitive low-noise amplifier, making proper thermal environment evaluation crucial. Further complicating the temperature estimation by limiting direct access to the device e.g., be fully encapsulated using polymers or equivalent (Figure 6). This, combined with the desire to limit the size and weight, restricts available cooling solutions and results in a thermal environment caused by the chip and its surrounding environment, increasing the risk of overheating.

**Figure 6.** Chip encapsulated in PCB [Paper A] with gold bond wires connecting the chip to PCB.

#### 3.2 Temperature Measurements

One way to address the risk of overheating is to purposefully operate the device at lower power to decrease the temperature but at the cost of reduced performance. This is not ideal, since it might introduce unnecessary reduction in performance instead it would be more beneficial to monitor the chip temperature and make decisions from information about temperature. There are several approaches to temperature measurements, which all have their advantages and disadvantages depending on the use case. The temperature should ideally be accurately predicted to the degree necessary for the intended application to avoid unacceptable degradation in performance and reliability.

#### 3.2.1 Optical Measurement Techniques

Different properties of light can be used to determine temperature, such as registering infrared radiation, which is a common method of determining temperature using an IR camera [32]. These measurements require a certain amount of a priori information about the devices for increased accuracy since they cannot be assumed to be perfect blackbodies. A material-dependent coefficient is required to compensate for this [33]. The technique can map surface temperature but with lesser spatial resolution than other optical methods [32]. In part due to the size of the wavelength of around 3  $\mu$ m, which is a considerable dimension in GaN HEMTs with gate lengths for many commercial processes in the range of 0.1  $\mu$ m to 0.25  $\mu$ m.

An alternative is to study the temperature-dependent optical properties of the materials used. In thermal reflectance imaging, the change in reflected light from a surface characterises the temperature. In Raman spectroscopy, the changes in scattered incident light by the crystal structure of a semiconductor material are sufficient to determine the temperature [33]. The advantages of using optical methods are that they enable good spatial resolution, which makes them helpful in characterising local hotspots. The disadvantage is that they require dedicated, complex, and expensive equipment that requires optical access to the device, so the possibility of using these methods for packaged devices is reduced. For example, devices packaged similarly to Figure 6 would be ill-suited for these methods.

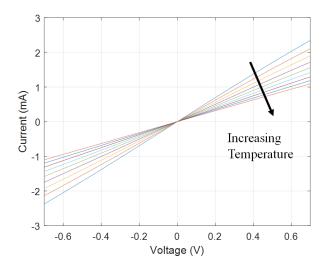

#### 3.2.2 Electrical Sensors

Another approach is to measure temperature-dependent electrical properties of the GaN HEMT itself, which could be an attractive option since it has several metrics that vary with temperature, e.g., properties of the gate diode or gain [32]. However, when integrated into a circuit, this is not always practical since, for example, the difficulties of correlating gain and temperature in a multi-stage amplifier. Similarly, using the drain current or  $R_{\text{on}}$  can be used to monitor temperature, state, but the dynamic behaviour will be filtered through the device bias network and therefore more suitable for steady state temperature measurements.

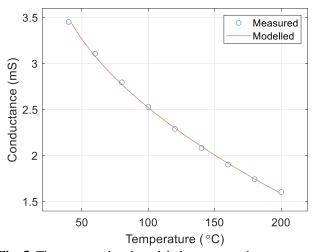

Instead, dedicated sensors consisting as diodes or resistors could be used to monitor temperature since these can be biased independently. One key advantage of using electrical sensors is that they do not require physical access to the device which makes them interesting for packaged circuits. Generally, there are several parameters to consider when implementing a temperature sensor, such as availability, size and sensitivity. Ideally, the sensor should be as sensitive as possible to temperature changes, enabling a relevant measurement resolution. It should also dissipate as little power as possible to minimise sensor self-heating and the impact of temperature chip temperature. Another metric usually used to describe a sensor is how linear this response is concerning temperature, as this could be useful to simplify characterisation and, in some instances, use the sensor response to compensate for thermal effects.

The diode-based temperature sensor monitors the shift in threshold voltage by having well-defined voltage and current measurements. In the context of GaN MMIC, Schottky barrier diodes (SBD) have primarily been used since they are commonly available components in most processes. The use of diodes for measuring temperature has been previously explored and demonstrated [34], [35]. Other possible implementations of diodes have been demonstrated mainly in experimental MMIC processes, which indicate high performance and appear very suitable for temperature sensing [36]. Another approach is GaN mesa resistors, where the 2DEG's mobility significantly varies with temperature, with the potential use as temperature sensors previously investigated [37] and are widely available. Depending on application the sensor size could also be of significance since a large sensor placed at a distance from the active regions registers more of an average chip temperature compared to a small one.

The benefit of this is that it is possible to place the sensors considerably closer to the active areas. A comparison in Table 1, illustrates that the metrics vary between sensor implementations but remain comparable overall.

**Table 1 Sensor Characteristics**

| Sensor                 | Sensitivity<br>/K   | Linearity | Size μm <sup>2</sup> | Ref       |

|------------------------|---------------------|-----------|----------------------|-----------|

| Circuit                | 0.35 mV             | 0.993     | 250x200              | [38]      |

| Circuit                | 31.28 mV            | 0.995     | -                    | [39]      |

| Integrated<br>Resistor | 0.36 Ω              | 0.9997    | Small                | [40]      |

| Integrated<br>Resistor | 10 Ω                | -         | Small                | [41]      |

| Resistor               | 0.4 Ω               | -         | -                    | [42]      |

| PIN Diode              | 19.7 mV             | 0.938     | 50 diameter          | [36]      |

| SBD Diode              | 1.61 mV             | -         | 20x100               | [34]      |

| SBD Diode              | 2.54 mV             | 0.992     | 90 diameter          | [35]      |

| GaN Resistor           | 2.17 mV<br>Or 3.3 Ω | 0.9785    | 10x4                 | [Paper A] |

Still, the main advantage of the approach is that resistor require few manufacturing steps and are readily available in all processes. The sensor size is also an advantage with an active sensor area of  $40~\mu m^2$ , magnitudes smaller than most other proposed sensors. This is limited to how small different MMIC processes can reliably manufacture resistors. The small sensor size, therefore, not only reduces the required chip area but also to a larger extent resembles a point like measurement of the chip compared to other sensors [37]. The small form factor of this sensor also enables a higher degree of flexibility.

#### 3.2.3 Thermal Test Structures

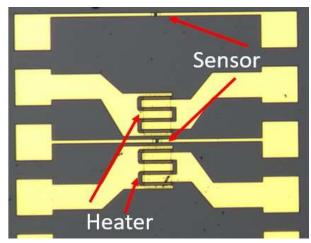

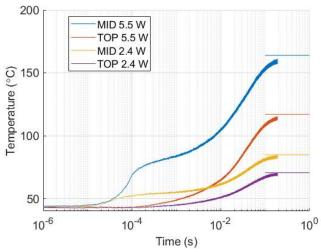

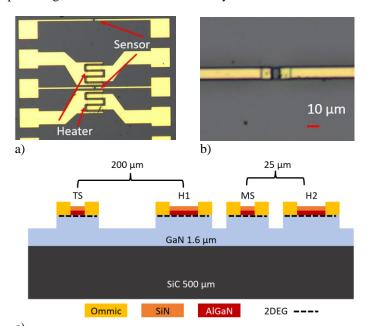

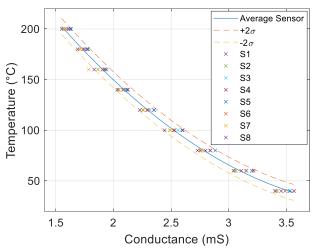

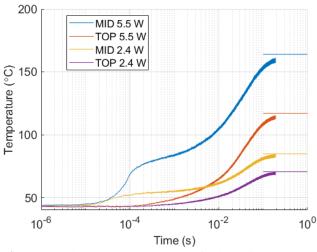

The validity of GaN resistor-based temperature sensors is demonstrated in [Paper A] using a thermal test structure. The idea with a thermal test structure is relatively straightforward: an active part that dissipates heat and another active part that registers the change in temperature using a temperature sensor. Thermal test structures have previously been demonstrated [43] an iteration of a previously suggested thermal test structure is included in [Paper A]. With even closer distance to the active heater, as seen in Figure 7. The sensor has been integrated as if it were the middle finger in a nine-finger GaN HEMT. Furthermore, the structure also includes additional sensors, such as a top sensor that can be seen at a distance of 200  $\mu$ m away from the active area.

**Figure 7.** Thermal test structure, including a heater consisting of two parts as well as two sensors. One sensor embedded into the heater and one place further away.

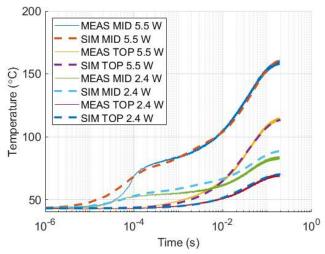

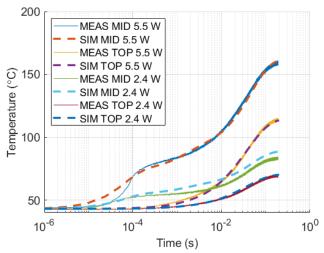

The idea of using two sensors is to correlate the temperature recorded using both the sensors in the middle of the device and with the temperature sensor further away. The results for a test structure mounted on copper (Figure 8) can be seen in Figure 9, for different power dissipations using both the middle and top sensors. The sensor temperature is captured during 200 ms with a complementary measurement after 1 s from the applied voltage step. Firstly, what can be noticed is that the two sensors differ in both recorded temperatures and characteristics. The top sensor registers, as expected, a low pass filtered dynamic temperature compared to the middle sensor, which is further explored in [Paper A].

**Figure 8**. Differently sized thermal test structures mounted on a copper carrier using silver epoxy.

**Figure 9.** Dynamic temperature response registered at the top and middle sensor in test structure during different power dissipations.

#### 3.3 Thermal Modeling

The proposed test structure and measurement method [37], [44], [45], [46], [47] used in [Paper A] has enabled the thorough characterisation of the thermal coupling between transistors in HPA and can be used as input for formulating models. It can also be used to predict the gradual temperature increase during continuous pulsed operation corresponding to realistic PA operation. [43]. There are different approaches to modelling the effects of self-heating in GaN HEMT devices

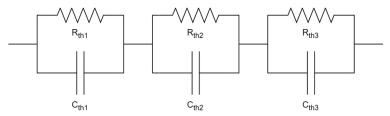

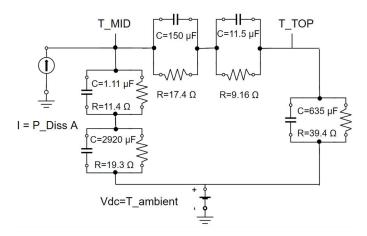

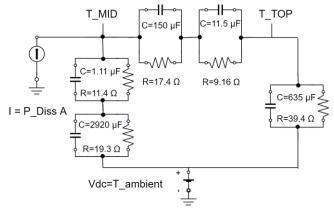

One approach which is highly suitable for compact device modelling is to use an electro-thermal RC network [48]. While consistent with the physical behaviour, this allows for a more empirical approach to modelling self-heating effects, which do not require detailed knowledge of the epitaxial structure. This also enables the temperature to be modelled using circuit design tools such as ADS. The thermal circuits are constructed using thermal resistor R<sub>th</sub> to describe the resistor of the heat flow through materials, while the dynamic and time-dependent part is described using thermal capacitances C<sub>th</sub> (Figure 10), which is used to describe the time delay contribution of the different layers [48].

**Figure 10.** Example of Thermal lowpass RC network in series for modelling the thermal response of the device. The resistor describes the ability to conduct heat with the time dependent properties described using the capacitance.

A thermal network can be used to describe how heat flows in a GaN HEMT, and the temperature of different locations of a GaN MMIC, as demonstrated in [Paper A]. The power dissipation level in the heaters describes a current source, and the ambient temperature is applied as a constant DC source to set the circuit's ambient temperature. The equivalent temperature at the different nodes is then synonyms with the circuit voltage and can, as such, be easily extracted as seen in in Figure 11.

**Figure 11.** Extracted thermal network for test structure and package. T\_MID and T\_TOP corresponds with middle and top sensor locations. P\_Diss is the dissipated power in the heater and T ambient the starting temperature.

The middle sensors, is placed close enough to the heat source which enables a more accurate temperature reading and registration of the dynamic behaviour. The values for the corresponding components in the thermal low pass filters are experimentally derived to match the derived temperatures and correspond with the recorded power dissipations using an ideal power step. During actual operation, the step is non-ideal, and the heater elements themselves display a nonlinear temperature dependence, which impacts the dissipated power, which would be required to be considered if a more precise analysis is to be performed. However, using the acquired model, it is still possible to estimate the temperature for an arbitrary power dissipation, as seen in Figure 12. Except for the initial high-frequency temperature increase, the model faithfully replicates the measured temperature for both the top and middle sensors.

**Figure 12.** Transient thermal behaviour, agreement between simulation using proposed thermal network and measured temperature as registered by the sensors in thermal test structure.

This is highly advantageous since the test structure can, therefore, be used to formulate a model for how the temperature in the middle of the device behaves. This knowledge of how the two sensors are corelated can then be transferred to a real-life application where a temperature sensor is placed at a distance can be used to estimate the temperature in the transistor.

Another approach is to create physical models of the device and package and perform numerical simulations, for example, by solving the Fourier equations of thermal conduction describing thermal propagation through the physical properties of a GaN HEMT model using the finite element method (FEM). The configuration of these simulations requires detailed insight into the structure of the device and package being simulated and the effort to set it up. In return, the physical description provides significant insight and valuable information for thoroughly analysing the behaviour.

While FEM simulations can be used to replicate the registered thermal response of the sensor, the actual temperature of the GaN HEMT channel is more challenging describing thermal processes at the micro to nanoscale. [49]. One challenge when simulating semiconductor devices is the difficulty of determining the temperature of the active part constituting the hot spot at the gate or channel temperature [50]. Using a Fourier analysis significantly underestimates the device peak temperature as it is not valid at the small dimensions at the scale of  $\mu m$  and nm that constitute the channel hotspot [50]. This is caused by the limitations in accurately capturing the impact of phonons using Fourier equations [49],

Instead, Monte Carlo Method can be used, which has been shown to provide more realistic values of the channel temperature. However, at the cost of computational complexity, it is possible to improve this by compartmentalising the simulation into one part using the Monte Carlo method closest to the active device to describe heat generation and Fourier analysis to determine the impact of the surrounding geometry [50]. This approach can therefore help with identifying the contributions of individual layers in the epitaxial structure and the cooling solution, such as the thermal interface between the chip and substrate or mounting. Since the heat spreads vertically into the epitaxial structure, the interaction with the underlying TIM below the chip and underlying structures is also significant [48].

# Chapter 4

# Memory Effects in GaN

Different mechanisms can cause memory effects in GaN, such as thermal, as discussed in Chapter 3, which impacts device operation. Memory effects can also be caused by electron trapping and manifest as the build-up of electric charge, which has been thoroughly researched and increasingly well understood. The traps originate from within the device's epitaxial structure and can be caused by intentional and unintentional doping or other defects. These traps result in undesired energy states in the semiconductor bandgap, which become occupied when a high electric field is applied. Causing electrons to collect at different locations in the device, such as at the surface [51], [52], in the AlGaN barrier [52] and the GaN buffer [53], [54]. The presence of trapped electrons causes a negative charge, which can act as a virtual gate. This virtual gate interferes with the effect of the applied gate voltage, as the effective device threshold voltage becomes unstable. The prevalence of traps and the associated time scales could differ since the manufacturing process, materials, and epitaxial structure vary between the foundries, resulting in different characteristics [55], [56]. Still, dynamic non-ideal behaviour degrades device performance as the electric field changes, introducing time constants ranging from ns to ms and in some instances, trapping effects can impact the device over several hours or even longer.

Processing improvements in the manufacturing of GaN HEMTs have diminished electric field-induced surface trap charging partly by introducing surface passivation as well as a GaN cap layer along with buffer engineering [57]. Additionally, improvements in device geometry such as the use of field plates has also reduced the impact of trapping, but the phenomenon remains as an issue [57].

Therefore, the impact of memory effects in GaN HEMT must be characterised and modelled. For example, similar thermal effects, trapping can also be described using RC networks [58]. Alternatively, a more physics-oriented approach, such as the Shockley-Read-Hall model [59], has been implemented and demonstrated to predict trapping-related effects accurately These approaches are included in the compact models used by circuit designers [60]. Currently, the two most prominent approaches to device modelling are empirical and physical-based devices, exemplified by the Angelov model [61], [62] and the ASM-HEMT model [63], [64], respectively, which both have certain approximations of these effects but are often simplified. Improving these models would enable circuit designers to evaluate the

impact of memory effects during circuit design. It could be used to compensate for the dynamic effects, such as biasing of the circuit to compensate for decreases in performance [65]. Some methods also include the necessary components for describing gradual effects, such as varying inter-pulse stability in HPAs [66] or increasing memory effects in switches, as investigated in [Paper C], but it remains a nontrivial challenge to address [67]. This is important, especially when adapting GaN technology to high-power and high-performance applications and how memory effects affect circuit operation. This is nontrivial to predict in the design stage and sometimes only becomes apparent when subjecting the circuit to actual operating conditions.

#### 4.2 Amplifiers

For radar applications, HPAs are driven in deep compression to maximise output power. These operating conditions result in high electric fields and significant power dissipation. The power consumption and heat generation associated with continuously operating power amplifiers would be considerable. Instead, the device is often operated in a pulsed mode where the gate voltage is switched from below the threshold voltage to the active operating point to decrease average power dissipation. While this significantly reduces the heat generation, it can also cause issues with trapping in terms of gate lag, which reduces the output power and, in turn, reduces system performance [57], [68]. Furthermore, pulse-to-pulse instabilities can be caused by both gradual heating of the device and gradually increasing or varying trapping effects [66]. This means that the properties of the initial pulses will differ over time, which could introduce uncertainties when performing the final analysis. Another effect to consider for multifunctional systems is how selecting between different waveforms, such as pulses with varying amplitude and duration, affects operation since this has been demonstrated to cause memory effects [69]. The result of this distorts the shape of the original waveform or signal with in-pulse trapping and thermal effects [69].

On the other hand, LNAs have different conditions since the use case and design differ from HPAs. Instead of pulsed operation, they are usually continuous on during operation to enable the detection of incoming signals. They are also typically biased with lower drain voltages and drain currents to reduce heat generation caused by continuous operation, and compared to HPA, the device is not intended to be subject to varying high fields, which could cause complex memory effects. However, since the LNAs are designed to amplify weak signals requiring high sensitivity, they make them vulnerable to intentional and unintentional jamming. While the robustness of GaN reduces the risk of permanent damage, high input signals can disrupt signal reception during jamming [70]. More probable, it could cause the LNA to experience temporary gain collapse [71] and degrade signal detection during recovery as charged trap states are discharged.

#### 4.3 Front End Switches

The front-end switch is another component whose operation condition differs from amplifiers since the dedicated switch transistor is not biased to provide gain and is often integrated into circuits using a common gate configuration. Additionally in a transceiver, the switch should affect the signal as little as possible. Especially, in terms of electron trapping since this would result in unwanted dynamic behaviour in both the send and receive signal. Therefore, it is highly relevant to characterise this effect to evaluate the impact on circuit performance in front-end switch devices and to determine the technology's stability over time.

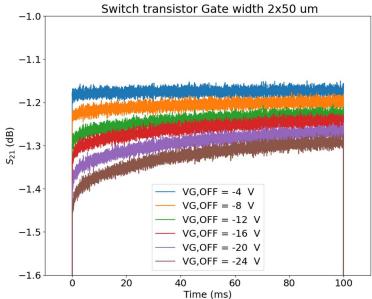

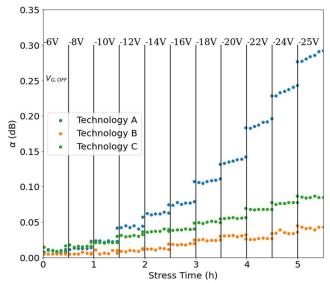

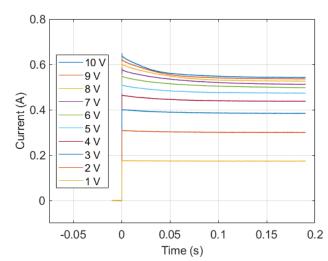

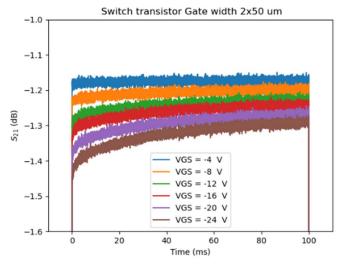

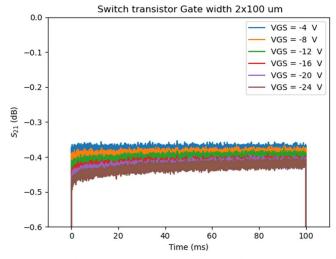

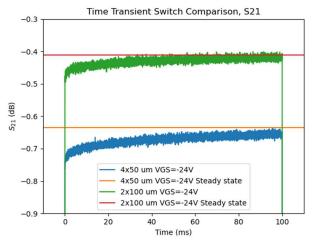

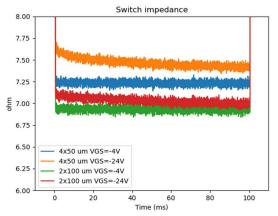

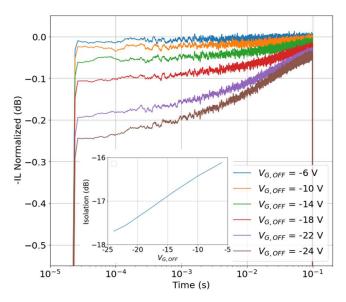

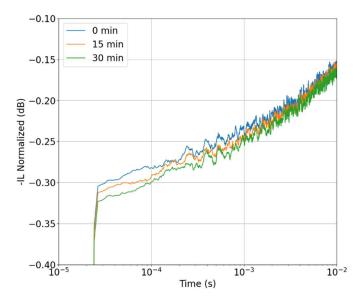

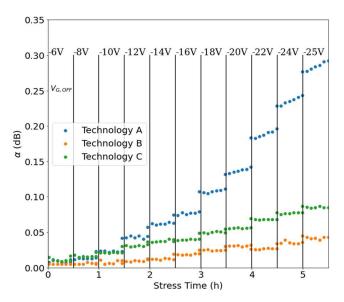

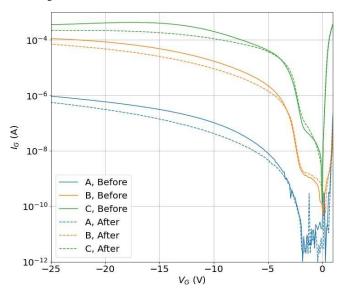

There are significant trade-offs and challenges to consider since significant trapping has been demonstrated when the switch is operated with highly negative voltages [14] [13]. One trade-off in the biasing of the switch with highly negative off voltages is to increase isolation in off-state and prevent self-biasing if the device is subjected to high input powers. However, the high electric fields cause trap states to be charged. When the switch is turned on, the turn-on time is ideally only limited by the technology cut-off frequency  $f_{T_i}$  in the order of ns for GaN HEMTs. Instead, the behaviour will initially display a quick rise time, which then transitions to a transient with a time constant of 100 ms or more. The results can be seen in Figure 13, which illustrates the recovery of the  $S_{21}$  of a GaN HEMT switch transistor as the device is switched from off to on state for increasingly negative off voltages ( $V_{G,OFF}$ ) seen in [13], [14].

**Figure 13**. Increasing recovery time with increased off-voltage for GaN HEMT switch devices [Paper B].

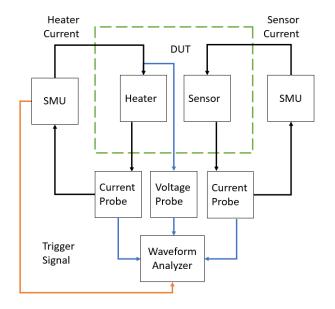

Therefore, it is of interest to evaluate this recovery for transceiver operation, which is performed in [Paper B] and [Paper C]. This is achieved by approximating realistic operating conditions where the device is continuously pulsed from off to on, a measurement setup (Figure 14) is proposed to characterise this effect.

Figure 14. Switch characterisation lab setup.

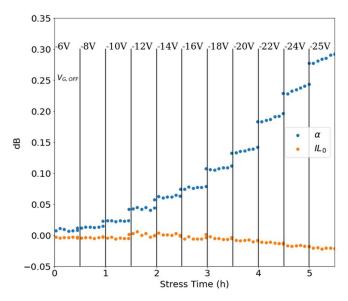

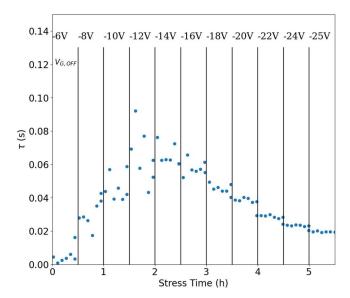

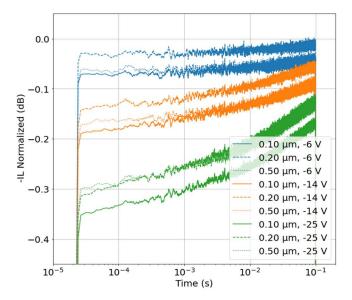

Furthermore, a method to quantify the transient recovery of the IL is used to estimate the impact of recovery, outlined in [Paper B] and relies on a simplified approach to describe the impact of trapping for amplifier operation by studying the transient response in the drain current. Since the switch devices do not have a drain current that can be used to model this behaviour, the IL is used instead, as can be seen in (1). The transient recovery is described using an exponential part where the term  $\alpha$  is useful for demonstrating the dependence of the  $V_{G,OFF}$ .

$$IL = IL_0 - \alpha e^{-\left(\frac{t}{\tau}\right)^{\beta}} \tag{1}$$

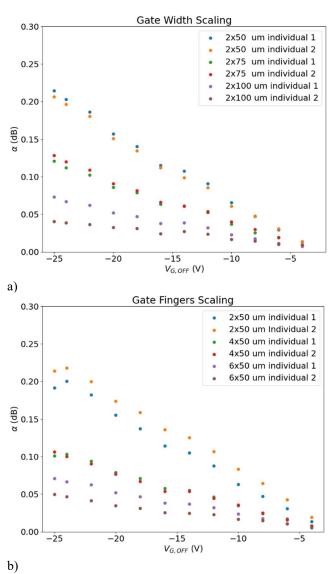

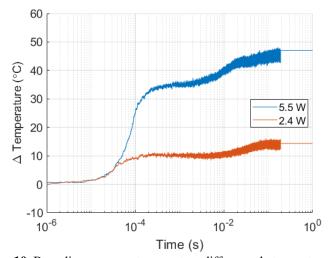

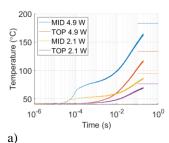

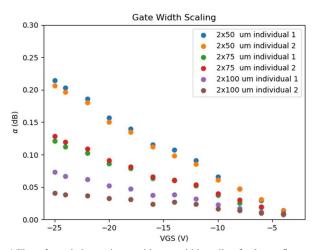

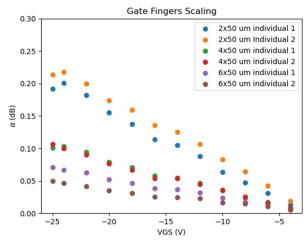

This approach is used in [Paper B] to study how the total gate width and the gate width distribution amongst different gate fingers impact the amount of trapping. As expected, the amount of trapping increased with decreased  $V_{G,OFF}$  as indicated with higher values of  $\alpha$ , with the smaller devices displaying a higher impact of trapping (Figure 15a). Additionally, the distribution of the gate width can also be shown to impact the amount of experienced trapping (Figure 15b). Interestingly, two devices with the same total gate width, such as  $2x100~\mu m$  and  $4x50~\mu m$ , showed differences in recovery, indicating the importance of carefully selecting device geometries during circuit design.

**Figure 15.** Differences in recovery depending on device geometry illustrated by using amplitude  $\alpha$  against off voltage  $V_{G,OFF}$ . With a) variations in gate width and b) variations in number of gate fingers.

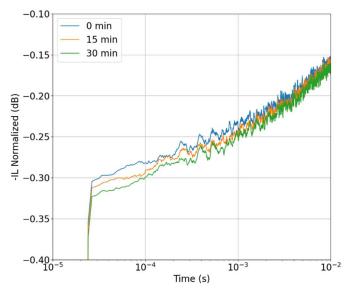

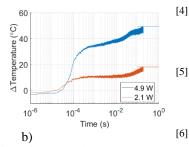

Another aspect to consider is the stability of recovery during continuous operation. Therefore, the switch setup [Paper B] was complemented to allow for an investigation of the stability of the recovery over time in combination with a gradual decrease of V<sub>G,OFF</sub>. The topic is of interest since the amount of trapping can potentially increase over time as illustrated in Figure 16. In [Paper C] the same model as in [Paper B] is used for quantifying the recovery using three different technologies which are studied over time. The drift in memory effects can be observed during continuous operation, illustrated in Figure 17, especially for one particular technology denoted "A", as outlined in [Paper C]. For all technologies studied the

recovery increase with varying sensitivity to decreased off voltage but for "A" there is also a drift over time as outlined in [Paper C]. The potential instability in recovery could, therefore, be a relevant aspect to consider for circuit designers depending on the requirements of consistency for example the pulse-to-pulse stability.

**Figure 16.** Drift in recovery of GaN HEMT Switch due to dynamic memory effects for continuous operation during 30 minutes.

**Figure 17**. Increased impact and drift of switch recovery over time for continuous operation indicated with increasing  $\alpha$  vs  $V_{G,OFF}$  for different technologies.

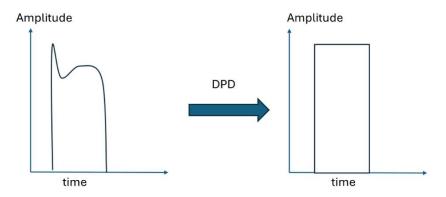

#### 4.4 Compensating for the Impact of Memory Effects

Thanks to extensive research into characterising memory effects, different strategies have been formulated to mitigate their impact on performance. Improving the compact models to accurately predict the effect of trapping techniques such as digital pre-distortion (DPD) can decrease the impact of memory effects further (Figure 18). For example, taking the effects studied in [Paper B], [Paper C] into consideration could contribute to the work on DPD already during the design phase of the GaN HEMT front end instead of characterising already manufactured transceivers. These methods rely on being able to predict the behaviour of the trapping to compensate for, e.g., an increase or decrease in output power in pulsed operation to achieve the desired waveform [72] [73]. Alternatively, DPD has also been shown to be possible by formulating behaviour models based on measurement data of a circuit, which can be used to predict or adapt to memory effects [66]. The effectiveness of this has also been demonstrated to significantly decrease inter-pulse instabilities and improve the output signal when selecting between different waveforms, e.g. amplitudes and pulse lengths.

**Figure 18**. Example of a waveform (pulse) distorted by nonlinear effects (left) and the desired waveform after DPD (right).

CHAPTER 5. CONCLUSIONS 25

# Chapter 5

# Conclusions

The continuous adaptation of GaN HEMTs as the primary technology for highpower applications at microwave frequencies is unlikely to stop in the foreseeable future. Increasing demands for higher performance drive the improvement of the technology itself and the models used to realise circuit functionality, package, and integration.

As part of this effort, this thesis has briefly outlined the challenges with the dynamic properties of GaN in terms of electrical and thermal effects and the issue of heat generation because of high-power operation. In this regard, the temperature sensors with complementing measurement techniques detailed in [Paper A] constitute a valuable contribution to monitoring temperature in packaged devices with the potential to contribute to evaluating the effectiveness of thermal management as well as measurement data to be used to calibrate physical simulations, especially on circuit and package levels.

The importance of estimating the impact of electron trapping on the circuit level for the continuous operation of front-end switches in multifunctional GaN MMICs is investigated. For example, it is essential to consider bias conditions, device geometries and technologies for the front-end switches to reduce the impact of the off voltage on switch recovery as demonstrated in [Paper B], [Paper C].

Both of these aspects contribute to a deeper understanding of the operating conditions of GaN MMIC front ends. Improving the description of the thermal and trapping effects could, by extension, also improve the conditions for using methods such as DPD.

26 CHAPTER 5. CONCLUSIONS

#### Future Work

There are many interesting further studies within the context of the nonlinear effects and the use of GaN technology for compact systems. Below are a few topics that could constitute the work's relevant and exciting continuation.

- Investigate temperature-insensitive power amplifiers using the proposed method to extract the thermal RC network and apply it to an actual packaged GaN HEMT. Included thermal sensors will extract temperature and use this information to bias the device dynamically

- Including the thermal test structures in packages to evaluate the impact of

different thermal management techniques, such as TIMs, heat spreaders, and

active cooling solutions, could be interesting as it would help clarify which

applications require active cooling and which can suffice using passive

cooling.

- Further investigating the impact on continuous operation using switch devices by including a medium to high input to study the impact of jamming on the switch device performance.

Investigate, if any, or to what degree the switch device performance permanently degrades during high-off voltages and the possibility of restoring the switch time performance by trying to decrease the electron charge by, for example, placing the device at an elevated temperature to reduce the emission time.

# Acknowledgements

I would like to thank all those who have supported me during this journey. Without their support, this thesis would not have been possible.

I am grateful to my supervisor, Dr. Mattias Thorsell, for his expertise and the time he has invested in my project. I also wish to express my thanks to my industrial supervisor, Niklas Billström, for his expert knowledge, patience, and openness. Similarly, Adjunct Professor Sten Gunnarsson, deserves recognition for his insightful discussions and the energy and cheer he brings to our work. Torbjörn Nilsson has been a significant support in providing feedback, helping me formulate my research results into publishable results and being such a conscientious reader of my manuscripts.

I appreciate my examiner, Christian Fager, not only for his valuable feedback but also for his role in fostering a positive work environment at the Electronics Microwave Laboratory. Similarly, I am thankful to Professor Niklas Rorsman for allowing me to contribute to the wide bandgap research group and the C3NiT center, and other initiatives under his leadership. I also appreciate Dr Marie Ström at Saab for her support and dedication to managing, developing, and furthering the research initiative I participate in.

I have my employer, Saab, to thank for my role in the industry, to be part of groundbreaking work within such a welcoming and dynamic environment. The support and collaboration of my colleagues at Saab have been not just crucial, but transformative to the success of this project. Therefore, I extend a heartfelt thank you to all of them. Special thanks to my direct managers, Dr. Fredrik Ingvarson and Johan Carlert, whose trust and investment in my capabilities have been crucial to this project's success. I am also thankful for my fellow PhD candidates, the ever-cheerful Tobias Kristensen and Johan Bremer, for our discussions, friendly conversations, and productive collaboration.

This work would not have been possible without the unwavering love and support from my family for which I am profoundly grateful. You have always believed in me. I would like to thank all of my friends for their company and support.

28 CHAPTER 5. CONCLUSIONS

### References

- S. J. A. H. W. A. Richards Mark A., Principles of Modern Radar, Volume I

Basic Principles. SciTech Publishing, 2010. [Online]. Available: https://app.knovel.com/hotlink/toc/id:kpPMRVIBP8/principles-modern-radar/principles-modern-radar

- [2] J. Kotani *et al.*, "24.4 W/mm X-Band GaN HEMTs on AlN Substrates With the LPCVD-Grown High-Breakdown-Field SiNxLayer," *IEEE Journal of the Electron Devices Society*, vol. 11, pp. 101–106, 2023, doi: 10.1109/JEDS.2023.3234235.

- [3] R. Nikandish, "GaN Integrated Circuit Power Amplifiers: Developments and Prospects," *IEEE Journal of Microwaves*, vol. 3, no. 1, pp. 441–452, 2023, doi: 10.1109/JMW.2022.3221268.

- [4] D. Fanning *et al.*, "Millimeter-Wave Gallium Nitride Maturation of 40nm T3 Gallium Nitride Monolithic Microwave Integrated Circuit Process," in *2023 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS)*, 2023, pp. 141–144. doi: 10.1109/BCICTS54660.2023.10310792.

- [5] Y. Tang *et al.*, "Ultrahigh-Speed GaN High-Electron-Mobility Transistors With fT/fmax of 454/444 GHz", *IEEE Electron Device Letters*, vol. 36, no. 6, pp. 549–551, 2015, doi: 10.1109/LED.2015.2421311.

- [6] D. S. Green, C. L. Dohrman, J. Demmin, Y. Zheng, and T.-H. Chang, "A Revolution on the Horizon from DARPA: Heterogeneous Integration for Revolutionary Microwave\/Millimeter-Wave Circuits at DARPA: Progress and Future Directions," *IEEE Microw Mag*, vol. 18, no. 2, pp. 44–59, 2017, doi: 10.1109/MMM.2016.2635811.

- [7] W. Ciccognani *et al.*, "Comparative noise investigation of high-performance GaAs and GaN millimeter-wave monolithic technologies," in *2019 14th European Microwave Integrated Circuits Conference (EuMIC)*, 2019, pp. 192–195. doi: 10.23919/EuMIC.2019.8909484.

- [8] S. S. H. Hsu, C.-W. Tsou, Y.-W. Lian, and Y.-S. Lin, "GaN-on-silicon devices and technologies for RF and microwave applications," in 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 2016, pp. 1–3. doi: 10.1109/RFIT.2016.7578151.

[9] S. Nuttinck et al., "Thermal analysis of AlGaN-GaN power HFETs.," *IEEE Transactions on Microwave Theory and Techniques, Microwave Theory and Techniques, IEEE Transactions on, IEEE Trans. Microwave Theory Techn*, vol. 51, no. 12, pp. 2445–2452, 2003

- [10] Z. Gao et al., "Thermally-activated failure mechanisms of 0.25 \ μm RF AIGaN/GaN HEMTs submitted to long-term life tests," in 2023 IEEE International Reliability Physics Symposium (IRPS), 2023, pp. 1–5. doi: 10.1109/IRPS48203.2023.10118131.

- [11] J. Pedro *et al.*, "A Review of Memory Effects in AlGaN/GaN HEMT Based RF PAs," in *2021 IEEE MTT-S International Wireless Symposium (IWS)*, 2021, pp. 1–3. doi: 10.1109/IWS52775.2021.9499373.

- [12] H. Luo, W. Hu, and Y. Guo, "On large-signal modeling of GaN HEMTs: past, development and future," *Chip*, vol. 2, no. 3, p. 100052, 2023, doi: https://doi.org/10.1016/j.chip.2023.100052.

- [13] C. Florian, G. P. Gibiino, and A. Santarelli, "Characterization and Modeling of RF GaN Switches Accounting for Trap-Induced Degradation Under Operating Regimes," *IEEE Trans Microw Theory Tech*, vol. 66, no. 12, pp. 5491–5500, 2018, doi: 10.1109/TMTT.2018.2857825.

- [14] M. Thorsell, A. Tengs, J. Hedman, and N. Billström, "Transition speed of GaN HEMTs for microwave switching applications 9th Wide Bandgap Semiconductors and Components Workshop ESA-ECSAT, Harwell, United Kingdom", 2018.

- [15] C. Mahle and H. Huang, "MMIC's in communications," *IEEE Communications Magazine*, vol. 23, no. 9, pp. 8–16, 1985, doi: 10.1109/MCOM.1985.1092639.

- [16] "Previous Winners: 1988 Present.", AviationWeek.com, Accessed: Oct 11, 2024. [Online]. Available: https://aviationweek.com/aerospace/innovation-laureate-raytheon-saab-gan-galvanizers,

- [17] M. Sudow *et al.*, "An AlGaN/GaN HEMT-Based Microstrip MMIC Process for Advanced Transceiver Design," *IEEE Trans Microw Theory Tech*, vol. 56, no. 8, pp. 1827–1833, 2008, doi: 10.1109/TMTT.2008.927317.

- [18] N. Billström, J. Nilsson, A. Tengs, and N. Rorsman, "High performance GaN front-end MMICs," in *2011 6th European Microwave Integrated Circuit Conference*, 2011, pp. 348–351.

- [19] M. Thorsell, M. Fagerlind, K. Andersson, N. Billström, and N. Rorsman, "An X-Band AlGaN/GaN MMIC Receiver Front-End," *IEEE Microwave and Wireless Components Letters*, vol. 20, no. 1, pp. 55–57, 2010, doi: 10.1109/LMWC.2009.2035968.

- [20] P. Schuh, H. Sledzik, and R. Reber, "High performance GaN single-chip frontend for compact X-band AESA systems," in 2017 12th European

*Microwave Integrated Circuits Conference (EuMIC)*, 2017, pp. 41–44. doi: 10.23919/EuMIC.2017.8230655.

- [21] D. F. Brown, P. Srivastava, K. Chu, W. Zhu, D. Dugas, and M. Litchfield, "Millimeter Wave GaN MMIC Technologies for Next-gen Defense Applications," in 2023 IEEE/MTT-S International Microwave Symposium IMS 2023, 2023, pp. 101–104. doi: 10.1109/IMS37964.2023.10188181.

- [22] M. van Heijningen *et al.*, "C-Band Single-Chip Radar Front-End in AlGaN/GaN Technology," *IEEE Trans Microw Theory Tech*, vol. 65, no. 11, pp. 4428–4437, 2017, doi: 10.1109/TMTT.2017.2688438.

- [23] T. E. Kazior, G. M. Jones, and T.-H. Chang, "Emerging Millimeter-Wave Device Technology - Next Generation GaN and Beyond," in 2022 IEEE/MTT-S International Microwave Symposium - IMS 2022, 2022, pp. 287–290. doi: 10.1109/IMS37962.2022.9865442.

- [24] L. Letailleur, M. Villegas, A. A. Hajjar, and C. E. Kacou, "Performance analysis of GaN/Si versus GaAs LNAs in 5G mm-wave frontend context," in 2022 14th Global Symposium on Millimeter-Waves & Terahertz (GSMM), 2022, pp. 9–11. doi: 10.1109/GSMM53818.2022.9792324.

- [25] S. Colangeli, A. Bentini, W. Ciccognani, E. Limiti, and A. Nanni, "GaN-Based Robust Low-Noise Amplifiers," *IEEE Trans Electron Devices*, vol. 60, no. 10, pp. 3238–3248, 2013, doi: 10.1109/TED.2013.2265718.

- [26] Q. Yu *et al.*, "Advancements in 300 mm GaN-on-Si Technology With Industry's First Circuit Demonstration of Monolithically Integrated GaN and Si Transistors," *IEEE Microwave and Wireless Technology Letters*, vol. 34, no. 6, pp. 745–748, 2024, doi: 10.1109/LMWT.2024.3383390.

- [27] H.-S. Lee, K. Ryu, M. Sun, and T. Palacios, "Wafer-Level Heterogeneous Integration of GaN HEMTs and Si (100) MOSFETs," *IEEE Electron Device Letters*, vol. 33, no. 2, pp. 200–202, 2012, doi: 10.1109/LED.2011.2174136.

- [28] R. Nikandish, "GaN System-on-Chip: Pushing the Limits of Integration and Functionality," *IEEE Journal of Microwaves*, pp. 1–11, 2024, doi: 10.1109/JMW.2024.3429615.

- [29] X. Chen, S. Boumaiza, and L. Wei, "Self-Heating and Equivalent Channel Temperature in Short Gate Length GaN HEMTs," *IEEE Trans Electron Devices*, vol. 66, no. 9, pp. 3748–3755, 2019, doi: 10.1109/TED.2019.2926742.

- [30] R. R. Tummala, Ed., "Anatomy of a Thermal Package System," in Fundamentals of Device and Systems Packaging: Technologies and Applications, 2nd Edition., New York: McGraw-Hill Education, 2019.

[Online]. Available: https://www.accessengineeringlibrary.com/content/book/9781259861550/to c-chapter/chapter3/section/section3

[31] R. Guggenheim and L. Rodes, "Roadmap review for cooling high-power GaN HEMT devices," in 2017 IEEE International Conference on Microwaves, Antennas, Communications and Electronic Systems (COMCAS), 2017, pp. 1–6. doi: 10.1109/COMCAS.2017.8244734.

- [32] D. L. Blackburn, "Temperature measurements of semiconductor devices a review," in *Twentieth Annual IEEE Semiconductor Thermal Measurement and Management Symposium (IEEE Cat. No.04CH37545)*, 2004, pp. 70–80. doi: 10.1109/STHERM.2004.1291304.

- [33] L. Baczkowski et al., "Thermal Characterization Using Optical Methods of AlGaN/GaN HEMTs on SiC Substrate in RF Operating Conditions," IEEE Trans Electron Devices, vol. 62, no. 12, pp. 3992–3998, 2015, doi: 10.1109/TED.2015.2493204.

- [34] T. Pu *et al.*, "Recessed Anode AlGaN/GaN Schottky Barrier Diode for Temperature Sensor Application," *IEEE Trans Electron Devices*, vol. 68, no. 10, pp. 5162–5166, 2021, doi: 10.1109/TED.2021.3105498.

- [35] Z. Yan *et al.*, "A Novel AlGaN/GaN-Based Schottky Barrier Diode With Partial P-GaN Cap Layer and Semicircular T-Anode for Temperature Sensors," *IEEE Trans Electron Devices*, vol. 70, no. 10, pp. 5087–5091, 2023, doi: 10.1109/TED.2023.3306736.

- [36] J. Chang *et al.*, "On-Chip Integrated High-Sensitivity Temperature Sensor Based on p-GaN/AlGaN/GaN Heterostructure," *IEEE Electron Device Letters*, vol. 44, no. 4, pp. 594–597, 2023, doi: 10.1109/LED.2023.3244821.

- [37] J. Bremer *et al.*, "Analysis of Lateral Thermal Coupling for GaN MMIC Technologies," *IEEE Trans Microw Theory Tech*, vol. 66, no. 10, pp. 4430–4438, 2018, doi: 10.1109/TMTT.2018.2848932.

- [38] A. M. H. Kwan, Y. Guan, X. Liu, and K. J. Chen, "A Highly Linear Integrated Temperature Sensor on a GaN Smart Power IC Platform," *IEEE Trans Electron Devices*, vol. 61, no. 8, pp. 2970–2976, 2014, doi: 10.1109/TED.2014.2327386.

- [39] A. Li *et al.*, "A 4-Transistor Monolithic Solution to Highly Linear On-Chip Temperature Sensing in GaN Power Integrated Circuits," *IEEE Electron Device Letters*, vol. 44, no. 2, pp. 333–336, 2023, doi: 10.1109/LED.2022.3226684.

- [40] F. Cozette *et al.*, "Resistive Nickel Temperature Sensor Integrated Into Short-Gate Length AlGaN/GaN HEMT Dedicated to RF Applications," *IEEE Electron Device Letters*, vol. 39, no. 10, pp. 1560–1563, 2018, doi: 10.1109/LED.2018.2864643.

- [41] R. Reiner *et al.*, "Linear temperature sensors in high-voltage GaN-HEMT power devices," in *2016 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2016, pp. 2083–2086. doi: 10.1109/APEC.2016.7468154.

[42] M. Basler, R. Reiner, S. Moench, P. Waltereit, R. Quay, and J. Haarer, "Compact GaN Power ICs with Power HEMT, Gate Driver, Temperature Sensor, Current Sense-FET and Amplifier," in 2023 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2023, pp. 191–194. doi: 10.1109/ISPSD57135.2023.10147498.

- [43] T. Kristensen, A. Divinyi, J. Bremer, T. M. J. Nilsson, and M. Thorsell, "Thermal Transient Measurements of GaN HEMT Structures by Electrical Measurements," in 2023 18th European Microwave Integrated Circuits Conference (EuMIC), 2023, pp. 293–296. doi: 10.23919/EuMIC58042.2023.10288814.

- [44] J. Bremer *et al.*, "Electric-Based Thermal Characterization of GaN Technologies Affected by Trapping Effects," *IEEE Trans Electron Devices*, vol. 67, no. 5, pp. 1952–1958, 2020, doi: 10.1109/TED.2020.2983277.

- [45] J., R. N. T. M. Bremer, "A Novel Test Structure for Electrothermal Assessment of GaN Technologies," 9th Wide Bandgap Semiconductors and Components Workshop, 2018.

- [46] M. Thorsell, K. Andersson, H. Hjelmgren, and N. Rorsman, "Electrothermal Access Resistance Model for GaN-Based HEMTs," *IEEE Trans Electron Devices*, vol. 58, no. 2, pp. 466–472, 2011, doi: 10.1109/TED.2010.2093012.

- [47] M., A. K., H. H. R. N. Thorsell, "Characterization of Electro-Thermal Effects in GaN Based HEMTs," 5th Space Agency-MOD Round Table Workshop on GaN Component Technologies, 2010.

- [48] D. Gryglewski, W. Wojtasiak, E. Kamińska, and A. Piotrowska, "Characterization of self-heating process in GaN-based HEMTs," *Electronics (Switzerland)*, vol. 9, no. 8, pp. 1 14, 2020, doi: 10.3390/electronics9081305.

- [49] H. Bao, J. Chen, X. Gu, and B. Cao, "A Review of Simulation Methods in Micro/Nanoscale Heat Conduction," *ES Energy & Environment*, vol. 1, pp. 16–55, 2018, doi: 10.30919/esee8c149.

- [50] H.-L. Li, Y. Shen, Y.-C. Hua, S. L. Sobolev, and B.-Y. Cao, "Hybrid Monte Carlo-Diffusion Studies of Modeling Self-Heating in Ballistic-Diffusive Regime for Gallium Nitride HEMTs," *J Electron Packag*, vol. 145, no. 1, p. 11203, Jun. 2022, doi: 10.1115/1.4054698.

- [51] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans Electron Devices*, vol. 48, no. 3, pp. 560–566, 2001, doi: 10.1109/16.906451.

- [52] G. Meneghesso *et al.*, "Trapping phenomena in AlGaN/GaN HEMTs: a study based on pulsed and transient measurements," *Semicond Sci Technol*, vol. 28, no. 7, p. 74021, Jun. 2013, doi: 10.1088/0268-1242/28/7/074021.

[53] J. Bergsten *et al.*, "Electron Trapping in Extended Defects in Microwave AlGaN/GaN HEMTs with Carbon-Doped Buffers," *IEEE Trans Electron Devices*, vol. 65, no. 6, pp. 2446–2453, Jun. 2018, doi: 10.1109/TED.2018.2828410.

- [54] M. Meneghini et al., "Buffer Traps in Fe-Doped AlGaN/GaN HEMTs: Investigation of the Physical Properties Based on Pulsed and Transient Measurements," *IEEE Trans Electron Devices*, vol. 61, no. 12, pp. 4070–4077, 2014, doi: 10.1109/TED.2014.2364855.

- [55] P. Beleniotis, S. Krause, C. Zervos, and M. Rudolph, "A Physics-Based Model for Slow Gate-Induced Electron Trapping in GaN HEMTs," *IEEE Trans Electron Devices*, vol. 71, no. 7, pp. 4058–4065, 2024, doi: 10.1109/TED.2024.3397234.

- [56] S. A. Albahrani, A. Parker, and M. Heimlich, "Circuit Model for Double-Energy-Level Trap Centers in GaN HEMTs," *IEEE Trans Electron Devices*, vol. 64, no. 3, pp. 998–1006, 2017, doi: 10.1109/TED.2017.2650241.

- [57] R. Ye *et al.*, "An Overview on Analyses and Suppression Methods of Trapping Effects in AlGaN/GaN HEMTs," *IEEE Access*, vol. 10, pp. 21759–21773, 2022, doi: 10.1109/ACCESS.2021.3139443.

- [58] O. Jardel et al., "An Electrothermal Model for AlGaN/GaN Power HEMTs Including Trapping Effects to Improve Large-Signal Simulation Results on High VSWR," IEEE Trans Microw Theory Tech, vol. 55, no. 12, pp. 2660– 2669, 2007, doi: 10.1109/TMTT.2007.907141.

- [59] J. Rathmell and A. Parker, "Circuit Implementation of a Theoretical Model of Trap Centres in GaAs and GaN Devices," *Proc SPIE*, vol. 6798, Dec. 2007, doi: 10.1117/12.758711.

- [60] A. Prasad, M. Thorsell, H. Zirath, and C. Fager, "Accurate Modeling of GaN HEMT RF Behavior Using an Effective Trapping Potential," *IEEE Trans Microw Theory Tech*, vol. 66, no. 2, pp. 845–857, 2018, doi: 10.1109/TMTT.2017.2748950.

- [61] I. Angelov, L. Bengtsson, and M. Garcia, "Extensions of the Chalmers nonlinear HEMT and MESFET model," *IEEE Trans Microw Theory Tech*, vol. 44, no. 10, pp. 1664–1674, 1996, doi: 10.1109/22.538957.

- [62] I. Angelov, H. Zirath, and N. Rorsman, "A new empirical nonlinear model for HEMT and MESFET devices," *IEEE Trans Microw Theory Tech*, vol. 40, no. 12, pp. 2258–2266, 1992, doi: 10.1109/22.179888.

- [63] S. Khandelwal *et al.*, "ASM GaN: Industry Standard Model for GaN RF and Power Devices—Part 1: DC, CV, and RF Model," *IEEE Trans Electron Devices*, vol. 66, no. 1, pp. 80–86, 2019, doi: 10.1109/TED.2018.2867874.

- [64] S. A. Albahrani, D. Mahajan, J. Hodges, Y. S. Chauhan, and S. Khandelwal, "ASM GaN: Industry Standard Model for GaN RF and Power Devices—

Part-II: Modeling of Charge Trapping," *IEEE Trans Electron Devices*, vol. 66, no. 1, pp. 87–94, 2019, doi: 10.1109/TED.2018.2868261.

- [65] J. Bremer, L. Hanning, N. Rorsman, and M. Thorsell, "Compensation of Performance Degradation Due to Thermal Effects in GaN LNA Using Dynamic Bias," in 2018 48th European Microwave Conference (EuMC), 2018, pp. 1213–1216. doi: 10.23919/EuMC.2018.8541789.

- [66] C. G. Tua, T. Pratt, and A. I. Zaghloul, "A Study of Interpulse Instability in Gallium Nitride Power Amplifiers in Multifunction Radars," *IEEE Trans Microw Theory Tech*, vol. 64, no. 11, pp. 3732–3747, 2016, doi: 10.1109/TMTT.2016.2604808.

- [67] P. Song, Z. Mokhti, and Q. Mu, "Investigation on a Desirable DPD Architecture and Trapping Characteristics for GaN Power Amplifier Linearization," in 2021 IEEE MTT-S International Microwave Symposium (IMS), 2021, pp. 531–533. doi: 10.1109/IMS19712.2021.9574877.

- [68] S. C. Binari, P. B. Klein, and T. E. Kazior, "Trapping effects in wide-bandgap microwave FETs," in 2002 IEEE MTT-S International Microwave Symposium Digest (Cat. No.02CH37278), 2002, pp. 1823–1826 vol.3. doi: 10.1109/MWSYM.2002.1012217.

- [69] C. Florian, T. Cappello, D. Niessen, R. P. Paganelli, S. Schafer, and Z. Popović, "Efficient Programmable Pulse Shaping for \$X\$ -Band GaN MMIC Radar Power Amplifiers," *IEEE Trans Microw Theory Tech*, vol. 65, no. 3, pp. 881–891, 2017, doi: 10.1109/TMTT.2016.2631171.

- [70] O. Axelsson, N. Billström, N. Rorsman, and M. Thorsell, "Impact of Trapping Effects on the Recovery Time of GaN Based Low Noise Amplifiers," *IEEE Microwave and Wireless Components Letters*, vol. 26, no. 1, pp. 31–33, 2016, doi: 10.1109/LMWC.2015.2505641.

- [71] S. Krause, P. Beleniotis, O. Bengtsson, M. Rudolph, and W. Heinrich, "Characterization of the Impairment and Recovery of GaN-HEMTs in Low-Noise Amplifiers under Input Overdrive," in 2021 IEEE MTT-S International Microwave Symposium (IMS), 2021, pp. 515–518. doi: 10.1109/IMS19712.2021.9574839.

- [72] P. M. Tome, F. M. Barradas, T. R. Cunha, and J. C. Pedro, "Compensation of the Pulse-to-Pulse Instability of GaN HEMT-Based Power Amplifiers," in 2019 IEEE MTT-S International Microwave Symposium (IMS), 2019, pp. 408–411. doi: 10.1109/MWSYM.2019.8700957.

- [73] J. L. Gomes *et al.*, "The Impact of Long-Term Memory Effects on the Linearizability of GaN HEMT-Based Power Amplifiers," *IEEE Trans Microw Theory Tech*, vol. 70, no. 2, pp. 1377–1390, 2022, doi: 10.1109/TMTT.2021.3132930.

### Paper A

On-Chip Sensors for Temperature Monitoring of Packaged GaN MMICs

A. Divinyi, T.M.J. Nilsson, N. Rorsman, T. Kristensen, H. Hultin, S.E. Gunnarsson and M. Thorsell

Published in *IEEE Transaction on Components Packaging and Manufacturing Technology*, 2024

# On-Chip Sensors for Temperature Monitoring of Packaged GaN MMICs

Andreas Divinyi, Torbjörn M.J. Nilsson, *Member*, *IEEE*, Niklas Rorsman, Tobias Kristensen, Harald Hultin, Sten E. Gunnarsson, *Senior Member*, *IEEE* and Mattias Thorsell, *Member*, *IEEE*

Abstract—A novel approach to on-chip temperature sensors for non-invasive thermal characterization and monitoring of packaged GaN MMICs is presented. The proposed sensor is fully compatible with commercial GaN foundry processes and enables improved reliability estimation of highly integrated systems. A dedicated test structure is developed to demonstrate the capabilities of the sensor, and an accurate calibration method of its temperature response is proposed. This combination allows for continuous temperature monitoring during operation with electrical acquisition of temperature transients. The method also enables the thermal characterization of the device and package.

Index Terms—Electro-thermal effects, GaN, MMIC, Semiconductor device packaging, Thermal sensors

#### I. INTRODUCTION

HE primary semiconductor technology for high-performing radar and communication systems is gallium nitride (GaN) high electron mobility transistors (HEMT) due to its high cutoff frequency and power density. Until recently, the demonstrated output power densities for gate lengths between 0.10 and 0.15 µm have typically been around 4 W/mm at frequencies of 30 GHz [1]. However, as the technology is continuously evolving, even higher power densities of 10 W/mm at both 30 GHz and 94 GHz is targeted in, e.g., the DARPA DREaM program [1]. Furthermore, the use of AlN substrates has recently enabled power densities up to 24.4 W/mm for gate lengths of 0.25 µm at X-band [2].

This technological development results in smaller transistors with higher levels of dissipated power. Higher power densities will increase the operating temperature of the HEMT, which impair its long-term reliability and performance, especially in a package [3]. This may impose system designs with a backed-off performance to ensure reliable operation.

This work was supported in part by the Swedish Agency for Innovation Systems Vinnova. A.Divinyi and T. M.J. Nilsson are with Saab, Gothenburg, Sweden (e-mail:andreas.divinyi3@saabgroup.com, torbjorn.mj.nilsson@saabgroup.com). M.Thorsell is with the Microwave Electronics Laboratory, Department of Microtechnology and Nanoscience, Chalmers University Gothenburg, SE-41296, Sweden, as well as Saab, Gothenburg, SE-41289 Sweden (e-mail: mattias.thorsell@saabgroup.com). N.Rorsman and T.Kristensen are with the Microwave Electronics Laboratory. Department of Microtechnology and Nanoscience, Chalmers University, SE-41296 Sweden (e-mail: rorsman@chalmers.se. tobias.kristensen@chalmers.se) H.Hultin and S.E.Gunnarsson is with Saab, Järfälla, SE-175 88 Sweden (e-mail:harald.hultin@saabgroup.com; sten.gunnarsson@saabgroup.com).

Several methods can be used to measure the temperature of GaN HEMTs, e.g. optical techniques, temperature-dependent device parameters or dedicated on-chip sensors. Optical methods like Infrared thermography (IR), Raman spectroscopy, and thermoreflectance [4] can be accurately calibrated to measure the device temperature provided optical access and dedicated equipment, which is not feasible for realtime monitoring of packaged components. The use of temperature-dependent device properties such as onresistance (Ron) [5] is not always practical for real-time monitoring since the operating conditions of the HEMT could vary depending on the application. Dedicated on-chip temperature sensors can be realized by, e.g., HEMTs with integrated special temperature-dependent thin film resistances [6], AlGaN/GaN Schottky barrier diodes (SBD) [7], or GaN resistors [8]. A key advantage is that dedicated sensors do not require optical access and can be operated independently of the monitored GaN MMIC. Furthermore, onchip circuits for temperature readout have been successfully demonstrated, but at the cost of more area and the need for enhancement mode HEMTs [9] [10]. However, not all integrated temperature sensors are compatible commercially available GaN MMIC foundries.

This paper proposes using an on-chip temperature sensor placed close to the device while not impairing device performance [8][11]. This sensor is based on a GaN resistor, which does not require additional manufacturing steps and is fully compatible with commercial GaN MMIC foundries. Furthermore, it is demonstrated to be compatible with bare-die as well as encapsulated MMICs, as no optical access is required. This facilitates improved reliability estimations of encapsulated devices through the capability of continuous temperature monitoring and, e.g., adaptation of operational conditions.

### II. FABRICATION AND PACKAGING

Dedicated GaN on silicon carbide (SiC) test dies is fabricated to demonstrate the operating principle of the proposed sensor. The fabrication is done using the Chalmers University of Technology in-house GaN technology [12]. The GaN HEMT structure consists of an  $Al_{0.25}Ga_{0.75}N$  barrier with a thickness of 25 nm followed by a Fe-doped GaN buffer and a 500  $\mu m$  thick SiC substrate. The fabricated sample of 16 x 16 mm² is diced into smaller dies of around 1 x 2 mm² that each contain a single test structure. The backside of the substrate is metalized with Ti/Au to enable the use of an adhesive for the packaging.

1

### A. Bare Die Mounting

The individual test chip is mounted on a copper carrier using a silver epoxy adhesive (ABLEBOND 84-1LMINB1) to examine the feasibility of the thermal test structures and the proposed method for real time temperature monitoring. The copper carrier simplifies handling and, combined with the silver epoxy improves the interface of the chip backside. The silver epoxy is manually dispensed, and the thickness of the interface is calculated by measuring the distance between the top of the chip and the copper carrier h, as seen in Fig. 1. The thermal properties and dimensions of bare-die mounting is summarized in Table 1.

### B. Embedded Die Mounting

The method is evaluated for packaged devices by encapsulating the test chip in PCB, as illustrated in Fig. 2. Connection to the chip is accomplished by gold bond wires and connectors on the top of the PCB. The chip is attached to the ground plane by use of a pressureless silver sinter paste (Heraeus DA295A, Table 1) and copper-filled thermal vias through a 254  $\mu m$  thick PCB layer.

### III. THERMAL TEST STRUCTURE

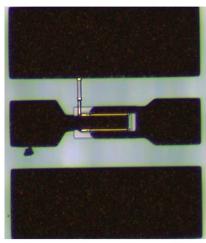

The purpose of the thermal test structure is to replicate the power dissipation of a GaN HEMT and to monitor the device temperature. In this case, an  $8 \times 75 \, \mu m^2$  HEMT is approximated with 8 parallel  $3 \times 75 \, \mu m^2$  GaN resistors used as heaters. The fabrication of the test structure did not include air bridges, and hence, the heater is split into two equal parts with four fingers in each, as seen in Fig. 3 a).

The temperature monitoring is achieved by the placement of a GaN resistor at the center point of the heating structure. This sensor is ideally as small as possible [8] while complying with process design rules, resulting in the dimensions  $10 \times 4 \mu m^2$ , as seen in Fig. 3 b).

Fig. 1. Cross section of bare die on copper, not to scale.

TABLE I

THERMAL PROPERTIES AND DEVICE GEOMETRY

| Layer     | Area                       | Thickness | Thermal conductivity W/m K |

|-----------|----------------------------|-----------|----------------------------|

| GaN       | 875 x 1975 μm <sup>2</sup> | 1.6 µm    | 160 [13]                   |

| SiC       | 875 x 1975 μm <sup>2</sup> | 500 μm    | 400 [13]                   |

| Ag Epoxy  | Similar to chip            | 25 μm     | 3.9 [14]                   |

| Ag Sinter | Similar to chip            | -         | 150 [15]                   |

| PCB       | 25 x 25 mm <sup>2</sup>    | 254 µm    | -                          |

| Copper    | 25 x 20 mm <sup>2</sup>    | 2 mm      | 387.6                      |