#### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Flip-chip Integrated Superconducting Quantum Processors

#### HANG-XI LI

Quantum Technology Laboratory Department of Microtechnology and Nanoscience (MC2) Chalmers University of Technology Göteborg, Sweden 2025 Flip-chip Integrated Superconducting Quantum Processors HANG-XI LI ISBN 978-91-8103-153-9

#### © HANG-XI LI, 2025

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr. 5611 ISSN 0346-718X

Quantum Technology Laboratory Department of Microtechnology and Nanoscience (MC2) Chalmers University of Technology SE-412 96 Göteborg Sweden Telephone: +46 (0)31-772 1000

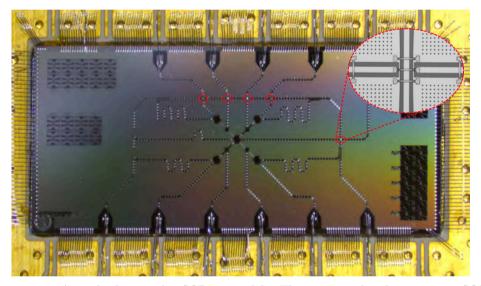

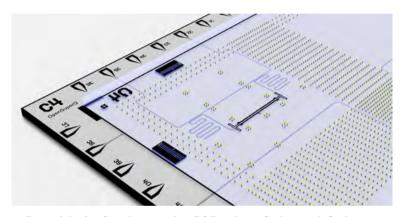

#### Cover:

A flip-chip integrated superconducting quantum processor sitting inside a printed circuit board

Chalmers Digitaltryck Göteborg, Sweden 2025 Flip-chip Integrated Superconducting Quantum Processors HANG-XI LI Quantum Technology Laboratory Department of Microtechnology and Nanoscience (MC2) Chalmers University of Technology

#### Abstract

On the path toward fault-tolerant quantum computing—an endeavor motivated by the prospect of solving otherwise intractable computational problems in fields such as quantum chemistry, materials, and optimization—a key challenge is to scale up the number of quantum bits of information (qubits) a quantum computer can host while not degrading their performance. To this end, the superconducting quantum processor (SQP) has its advantages due to its flexible design, compatibility with microchip manufacturing processes, and addressability by microwaves generated by commercially available equipment.

This thesis is a demonstration of the scalability of SQPs. By adopting 3-dimensional integration technologies used in semiconductor manufacturing, flip-chip integrated SQPs can host dozens to hundreds of qubits, compared to the smaller number of qubits a single-chip architecture can accommodate. The first part of this thesis shows how we transferred the design of individual components of the SQP—qubits, couplers, readout resonators, and Purcell filters—into a flip-chip architecture while maintaining good qubit coherence and high control-and-measurement performance with additional fabrication processes. We pay special attention to the interchip spacing, an additional design parameter introduced in the flip-chip architecture, which has a large influence on the parameter predictability and performance of the SQP.

The second part of the thesis shows how we used these individual components to design a scaled-up SQP. The design workflow of a multi-qubit SQP, from parameter design to layout, is elaborated in detail. This workflow has resulted in a 25-qubit flip-chip integrated SQP, without degrading the qubit coherence and gate performance, further demonstrating the scalability of flip-chip integrated SQPs. We speed up this design workflow by introducing an analytic design method for superconducting resonators based on conformal mapping techniques, which we use to design readout resonators with parameters that are not affected by variations of the interchip spacing.

Keywords: quantum computing, superconducting quantum processor, 3D integration, flip-chip integration, design workflow, simulation and design speed-up.

#### LIST OF PUBLICATIONS

This thesis is based on the work contained in the following papers:

#### Paper A

S. Kosen, H.-X. Li, M. Rommel, D. Shiri, C. Warren, L. Grönberg, J. Salonen, T. Abad, J. Biznárová, M. Caputo, L. Chen, K. Grigoras, G. Johansson, A. F. Kockum, C. Križan, D. P. Lozano, G. J. Norris, A. Osman, J. Fernández-Pendás, A. Ronzani, A. F. Roudsari, S. Simbierowicz, G. Tancredi, A. Wallraff, C. Eichler, J. Govenius, and J. Bylander, "Building blocks of a flip-chip integrated superconducting quantum processor", Quantum Science and Technology 7, 035018 (2022)

#### Paper B

K. Grigoras, N. Yurttagul, J.-P. Kaikkonen, E. T. Mannila, P. Eskelinen, D. P. Lozano, **H.-X. Li**, M. Rommel, D. Shiri, N. Tiencken, S. Simbierowicz, A. Ronzani, J. Hatinen, D. Datta, V. Vesterinen, L. Gronberg, J. Biznarova, A. F. Roudsari, S. Kosen, A. Osman, M. Prunnila, J. Hassel, J. Bylander, and J. Govenius, "Qubit-compatible substrates with superconducting through-silicon vias", IEEE Transactions on Quantum Engineering **3**, 5100310 (2022)

## Paper C

L. Chen, **H.-X. Li**, Y. Lu, C. W. Warren, C. J. Križan, S. Kosen, M. Rommel, S. Ahmed, A. Osman, J. Biznárová, A. Fadavi Roudsari, B. Lienhard, M. Caputo, K. Grigoras, L. Grönberg, J. Govenius, A. F. Kockum, P. Delsing, J. Bylander, and G. Tancredi, "Transmon qubit readout fidelity at the threshold for quantum error correction without a quantum-limited amplifier", npj Quantum Information **9**, 26 (2023)

## Paper D

H.-X. Li, D. Shiri, S. Kosen, M. Rommel, L. Chayanun, A. Nylander, R. Rehammar, G. Tancredi, M. Caputo, K. Grigoras, L. Grönberg, J. Govenius, and J. Bylander, "Experimentally Verified, Fast Analytic, and Numerical Design of Superconducting Resonators in Flip-Chip Architectures", IEEE Transactions on Quantum Engineering 4, 3101312 (2023)

## Paper E

S. Kosen, **H.-X. Li**, M. Rommel, R. Rehammar, M. Caputo, L. Grönberg, J. Fernández-Pendás, A. F. Kockum, J. Biznárová, L. Chen, C. Križan, A. Nylander, A. Osman, A. F. Roudsari, D. Shiri, G. Tancredi, J. Govenius, and J. Bylander, "Signal crosstalk in a flip-chip quantum processor", PRX Quantum **5**, 030350 (2024)

Other papers that are outside the scope of this thesis:

#### Paper I

Y. Lu, M. Kudra, T. Hillmann, J. Yang, **H.-X. Li**, F. Quijandría, and P. Delsing, "Resolving Fock states near the Kerr-free point of a superconducting resonator", npj Quantum Information **9**, 114 (2023)

Paper II

L. Chen, S. P. Fors, Z. Yan, A. Ali, T. Abad, A. Osman, E. Moschandreou, B. Lienhard, S. Kosen, **H.-X. Li**, D. Shiri, T. Liu, S. Hill, A.-A. Amin, R. Rehammar, M. Dahiya, A. Nylander, M. Rommel, A. F. Roudsari, M. Caputo, G. Leif, J. Govenius, M. Dobsicek, M. F. Giannelli, A. F. Kockum, J. Bylander, and G. Tancredi, "Fast unconditional reset and leakage reduction in fixed-frequency transmon qubits", arXiv, 2409.16748 (2024)

## Contents

| Al | stract                                                                                                                                                                                                                                                                                                                                                  | i                                                  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Li | t of publications                                                                                                                                                                                                                                                                                                                                       | iii                                                |

| Co | ntents                                                                                                                                                                                                                                                                                                                                                  | $\mathbf{v}$                                       |

| A  | knowledgements                                                                                                                                                                                                                                                                                                                                          | ix                                                 |

| Al | breviations                                                                                                                                                                                                                                                                                                                                             | xi                                                 |

| Ι  | Thesis                                                                                                                                                                                                                                                                                                                                                  | 1                                                  |

| 1  | Introduction  1.1 Why quantum computation?  1.2 Superconducting quantum processor (SQP)  1.3 Scaling up is necessary  1.4 Challenges ahead  1.5 Thesis outline  1.7 Thesis outline                                                                                                                                                                      | 3<br>3<br>4<br>5<br>6<br>7                         |

| 2  | 3-dimensional (3D) integration technology 2.1 Advanced packaging in semiconductor industry 2.2 3D integration in SQP 2.2.1 Separating the qubits from their control lines 2.2.2 Controlling the qubits vertically 2.2.3 Differences from classical advanced packaging technologies 2.2.4 Implementation requirements 2.3 Discussion of the future trend | 9<br>11<br>11<br>12<br>13<br>14<br>14              |

| 3  | Flip-chip integrated SQPs 3.1 3D structures in flip-chip integrated SQPs 3.2 Fabrication process 3.3 Individual qubit performance 3.4 Two-qubit pair as a unit cell 3.5 Purcell filter for qubit readout 3.6 Interchip spacing variation effect 3.6.1 Global variation 3.6.2 Local variation 3.7 Further developments in flip-chip architecture         | 17<br>19<br>20<br>22<br>23<br>27<br>27<br>29<br>30 |

| 4  | Design of a multi-qubit, flip-chip integrated SQP 4.1 General design workflow                                                                                                                                                                                                                                                                           | <b>31</b> 31                                       |

|              | 4.2   | Architecture design                                                 | 32  |

|--------------|-------|---------------------------------------------------------------------|-----|

|              | 4.3   | Parameter design                                                    | 33  |

|              |       | 4.3.1 Constraints on the unit cell level                            | 33  |

|              |       | 4.3.2 Constraints on the chip level                                 | 34  |

|              |       | 4.3.3 Parameter optimization                                        | 34  |

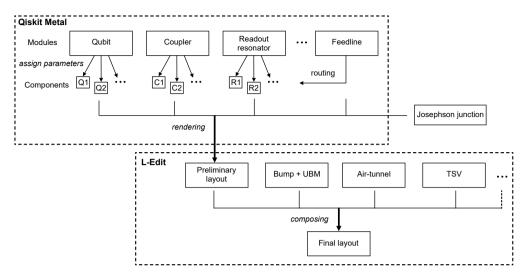

|              | 4.4   | Layout design                                                       | 35  |

|              | 1.1   | 4.4.1 Layout drawing workflow of an SQP                             | 38  |

|              | 4 5   | ·                                                                   |     |

|              | 4.5   | Design verification                                                 | 39  |

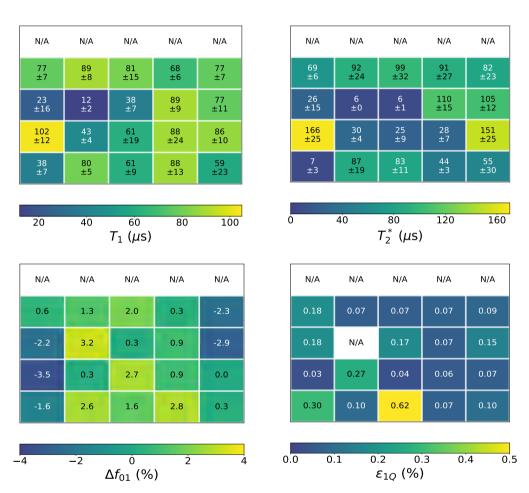

|              | 4.6   | Performance characterization after fabrication                      | 40  |

|              | 4.7   | Discussion on scaling up SQPs                                       | 42  |

| 5            | Fast  | t design of coplanar-waveguide (CPW) resonators in flip-chip archi  | i-  |

|              | tect  | ture                                                                | 45  |

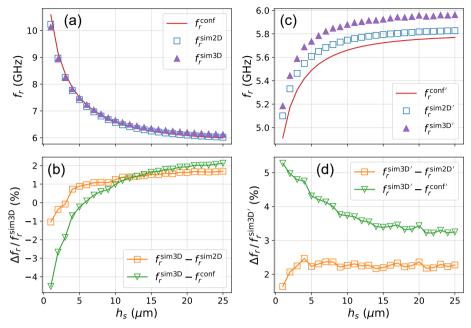

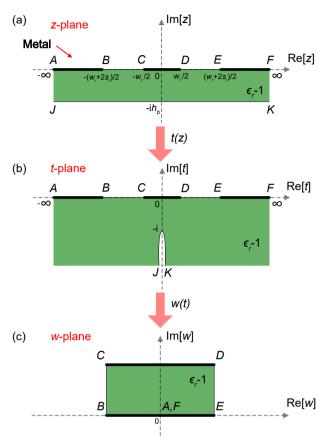

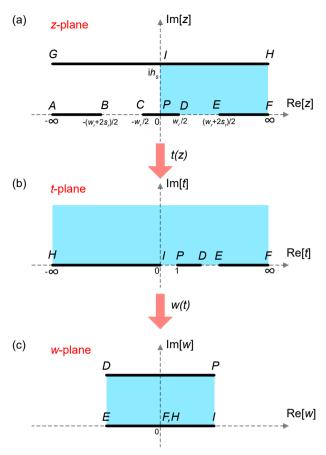

|              | 5.1   | Analytical calculation                                              | 45  |

|              | 5.2   | Comparison to 3D simulations                                        | 49  |

|              |       | 5.2.1 Resonant frequency $f_r$                                      | 49  |

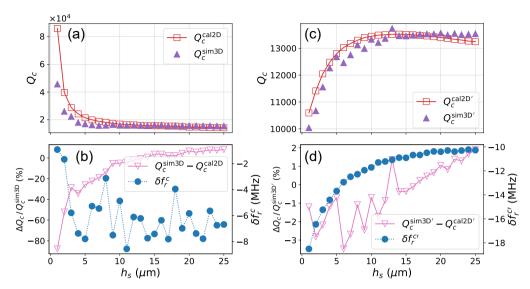

|              |       | 5.2.2 Coupling quality factor $Q_c$                                 | 49  |

|              | 5.3   | Discussion on computational resources consumption                   | 50  |

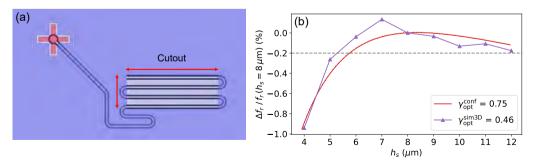

|              | 5.4   | Making $f_r$ insensitive to interchip spacing                       | 52  |

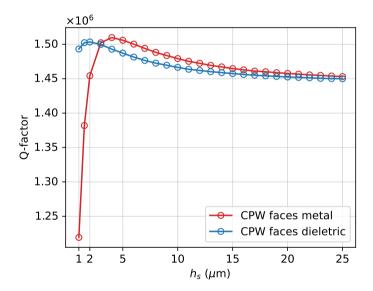

|              | 5.5   | Q-factor of the resonator's cross-section in flip-chip architecture | 53  |

|              | ~     |                                                                     |     |

| 6            |       | nmary and contributions                                             | 55  |

|              | 6.1   | Summary                                                             | 55  |

|              | 6.2   | Contributions                                                       | 56  |

| $\mathbf{A}$ | Pac   | kaging of an SQP                                                    | 57  |

| В            | Der   | ivation of $L_l^g$ , $C_l$ of a CPW line                            | 61  |

|              |       | Planar CPW line                                                     | 62  |

|              |       | Flip-chip CPW line                                                  | 63  |

|              |       | B.2.1 Top chip with the ground plane                                | 65  |

|              |       | B.2.2 Top chip without the ground plane                             | 67  |

| ъ.           | . c   |                                                                     | co  |

| Re           | efere | nces                                                                | 69  |

| II           | ٨     | ppended Papers                                                      | 75  |

| 11           | А     | ppended 1 apers                                                     | 10  |

| Pa           | per   | A                                                                   | 77  |

| Pa           | per   | В                                                                   | 107 |

| Pa           | per   | C                                                                   | 119 |

| Pa           | per   | D                                                                   | 133 |

| Pa           | per   | $\mathbf{E}$                                                        | 147 |

To Ke Zou, my lovely wife.

#### ACKNOWLEDGEMENTS

When I look back at the journey I have walked through as a PhD student, I would say, 'incredible'. There are many moments that are so fulfilling, and also moments that are so stressed. Most importantly, I have met so many people that I genuinely want to give my thanks for helping me along the way.

First, I would like to thank my supervisor, Jonas Bylander, for your kind support during my time at Chalmers. I could not have come to this point without your guidance on my work and help with arranging experimental resources. I greatly appreciate your detailed remarks on my writings, which always force me to think deeper about the meaning that I have written down.

I would also give my sincere thanks to Daryoush Shiri, who is not only my co-supervisor, but also my best friend in Sweden. You gave me a lot of advice, both in research and in life. It was a delightful experience to work with you, chat with you, and share my thoughts with you. I am also very grateful for your critical comments on my writings and talks, after which they always result in a much better quality.

I would also like to thank my examiner, Per Delsing, for your valuable input on my research and your kind help throughout my PhD study, and our current head of the division, Witlef Wieczorek, for your management of QTL's research activities and support of healthy working environment.

To Anita Fadavi Roudsari and Daniel Perez Lozano, I am still very thankful for your patience in teaching me lots of design and measurement techniques at the beginning of my PhD. And Sandoko Kosen, working closely with you is a pleasant and rewarding experience. I would not have accomplished so much work without our collaboration. You are my role model for being hard-working.

My weak point is always at fabrication. Thank you a lot, Marcus Rommel, for your patient explanation and for showing me how to fabricate the chips out, one step by another. Moreover, without your effort, our flip-chip devices would not have been so good and could not have been fabricated so successfully.

I am also very thankful to the people in QTL that I always have discussions with: Giovanna Tancredi, Robert Rehammar and Andreas Nylander, as senior people in the group, the discussions with you had enriched my knowledge; and my fellow PhDs, Liangyu Chen, Christopher Warren, Janka Biznárová, Christian Križan, Amr Osman, Hampus Renberg Nilsson, Martí Gutierrez Latorre, Yong Lu, Jiaying Yang, Anuj Aggarwal, Emil Rehnman, and Achintya Paradkar, the discussions with you were always fruitful. Especially Liangyu, it was a great time when we had intense discussions during our collaboration on the qubit readout experiments. Moreover, I had a good time working with Lert Chayanun, Miroslav Dobsicek, Mamta Mamta, Irshad Ahmad, and all the current and previous members of QTL.

I should also thank many other people who have helped me along the way: Linda Brånell, for your kindness in helping me deal with administration paperwork and Swedish migration system; Lars Jönsson, for your magical making of our sample boxes; Tuure Rantanen, Kestutis Grigoras, Leif Grönberg, Marco Caputo, Joonas Govenius and other people in VTT, for completing the fabrication of flip-chip devices; Henrik Frederiksen, for your help on fabrication recipes; Graham Norris, for your early help on chip design;

Alexey Zadorozhko, for your maintenance of cryogenic fridges; Basudha Srivastava, for your teaching of quantum error correction; and Jorge Fernández-Pendás, Tahereh Abad, Anton Frisk Kockum, Göran Johansson and many people in AQP for your theoretical input at various aspects. There are definitely more people who I have discussed with and learned from, thank you very much.

To my parents, Xu-Xun Li and Yi-Qing Xie, thank you for understanding me not being able to visit you often during the past five years and for always supporting my pursuit of being a scientist.

And finally, to my love, Ke Zou, this year is our 10-year anniversary since we were together. Throughout my life, I can say my happiest moment was our wedding ceremony three years ago. Without you, I cannot imagine what my life in Sweden would look like. It is you who are always beside me, sharing my happiness, comforting my frustration, and giving me the energy to move on. Thank you so much for being here with me. This thesis is dedicated to you.

Hang-Xi Li, Göteborg, January 2025

## Abbreviations

Here we list the abbreviations in the order that they first occur in the thesis.

| RSA        | Rivest-Shamir-Adleman scheme                |

|------------|---------------------------------------------|

| SQP        | superconducting quantum processor           |

| L-C        | inductor-capacitor                          |

| 3D/2.5D/2D | 3/2.5/2-dimensional                         |

| CPW        | coplanar-waveguide                          |

| SoC        | system-on-chip                              |

| I/O        | input/output                                |

| PCB        | printed circuit board                       |

| IC         | integrated circuit                          |

| TSV        | through-silicon via                         |

| CMOS       | complementary metal-oxide-semiconductor     |

| C-chip     | control chip                                |

| Q-chip     | qubit chip                                  |

| SiP        | system-in-a-package                         |

| EM         | electromagnetic                             |

| SEM        | scanning electron microscope                |

| UBM        | under-bump metalization                     |

| Al         | aluminum                                    |

| NbN        | niobium nitride                             |

| In         | indium                                      |

| TiN        | titanium nitride                            |

| TLS        | two-level system                            |

| E-field    | electric field                              |

| SQUID      | superconducting quantum interference device |

| RB         | randomized benchmarking                     |

| iRB        | interleaved randomized benchmarking         |

| RDL        | redistribution layer                        |

| MCM        | multi-chip module                           |

| SNR        | signal-to-noise ratio                       |

| EDA        | electronic design automation                |

| DRC        | design rule checking                        |

| CPU        | central processing unit                     |

# Part I

# Thesis

## CHAPTER I

#### Introduction

When Richard Feynman in his 1982 landmark speech [1] said that 'you can simulate this (quantum mechanics) with a quantum system, with quantum computer elements,' he may not have thought that after only 40 years, quantum computers would have become so real in the world and evolve so fast. Just before the publication of this thesis, Google announced having used a 105-qubit superconducting quantum processor to demonstrate an exponential suppression of the logical qubit error rate with quantum error-correcting codes [2]. At the same time, IBM has announced having built a 1000-qubit superconducting quantum processor [3]. Both companies have used flip-chip integration technology to scale up their processors [4, 5], which will be the main topic of this thesis.

#### 1.1 Why quantum computation?

Why do we want to have a quantum computer, a machine to realize quantum computation? The basic building block of quantum computers, which gives them their unique 'quantum' nature, is the 'quantum bit' of information, or qubit. Unlike the state of a classical bit, which can only be in a digital 0 or 1, the state of a qubit,  $|\psi\rangle$ , can be in a quantum superposition of the two [6]:

$$|\psi\rangle = \alpha|0\rangle + \beta|1\rangle. \tag{1.1}$$

The coefficients  $\alpha$ ,  $\beta$  are complex numbers that must satisfy the constraint  $|\alpha|^2 + |\beta|^2 = 1$ . What's more, two qubits can be 'entangled' together as a joint state  $|\Phi\rangle$  that cannot be separated into two single-qubit states:

$$|\Phi\rangle = c_1|00\rangle + c_2|01\rangle + c_3|10\rangle + c_4|11\rangle \neq (\alpha_1|0\rangle + \beta_1|1\rangle) (\alpha_2|0\rangle + \beta_2|1\rangle), \qquad (1.2)$$

where the coefficients of this joint state satisfy  $|c_1|^2 + |c_2|^2 + |c_3|^2 + |c_4|^2 = 1$ .

A quantum algorithm is realized by a sequence of quantum gates operating on such joint states. Different from two-bit Boolean logic gates in 'classical' algorithms, which operate on one two-bit state at a time [7], a two-qubit quantum gate operates on the coefficients of all computational basis states ( $|00\rangle$ ,  $|01\rangle$ , etc.) of the joint state *simultaneously* and creates entanglement between qubits. This is the *quantum parallelism*, which can give a cleverly devised quantum algorithm an exponential advantage over a classical algorithm when applied to some computational problems. Here 'exponential advantage' means that the number of operations (and hence time to solution) grows as an exponential in the size of the problem (number of bits needed) in the classical algorithm, whereas it can grow much more slowly, as a polynomial, in a quantum algorithm [6].

The most prominent example of this is the quantum algorithm that Peter Shor had developed for factoring of integer numbers [8], with important applications in decryption of widely used public-key cryptography schemes such as the Rivest–Shamir–Adleman scheme (RSA) [9], which is based on the belief that factoring of integers is 'hard,' i.e., it cannot be done in polynomial time.

After the publication of Shor's algorithm, more and more efforts have been put into searching for quantum algorithms that may have an advantage over classical algorithms. Grover's algorithm [10] was shown to have quadratic speedup for unstructured database search. Simulation methods for quantum systems, just as Feynman envisioned, were proposed to try to utilize the same quantum power that Shor had discovered [11].

### 1.2 Superconducting quantum processor (SQP)

Among the many physical platforms that have been suggested for the realization of quantum computers [12], the superconducting quantum processor (SQP), based on circuit quantum electrodynamics [13], represents one of the most developed and promising technologies [14]. Its design flexibility and fabrication compatibility with mainstream semiconductor fabrication equipment have resulted in its rapid growth of scale [3, 15] after its first prototype was realized [16].

The qubits within an SQP are based on the non-linear behavior of the Josephson tunnel junctions [17]. Following years of evolution, a rich design landscape of superconducting qubits has emerged [7, 13], and researchers are developing SQPs based on various kinds of qubit designs [4, 18–20].

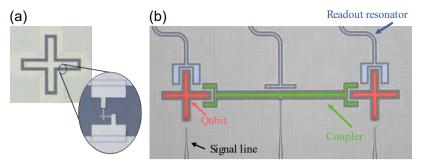

The superconducting qubit modality used in this thesis is called transmon, essentially an inductor–capacitor (L–C) oscillator whose spectrum has been rendered slightly anharmonic by the Josephson nonlinear inductance. Its name comes from its original realization using a transmission line [21]. The transmon has a large shunt capacitor, compared to its Josephson junction's own capacitance. Figure 1.1(a) shows a typical design of the transmon within the SQP. Additional control and readout components are used to manipulate the transmons and interrogate their states. A dedicated coupler (in our case, another qubit) mediates the interaction between qubits within the SQP, bringing about quantum entanglement.

Figure 1.1(b) shows a simple 2-qubit SQP design that contains all the elements just mentioned. Such a design is generally patterned on a superconducting thin film (here aluminum) on top of a dielectric substrate (silicon).

Figure 1.1: (a) Standalone transmon qubit in which the Josephson junction (zoom-in photo) connects the qubit island and the ground plane. (b) A small SQP made at Chalmers, containing two qubits connected by a coupler, along with their control and readout components. Picture adapted from Reference [22].

### 1.3 Scaling up is necessary

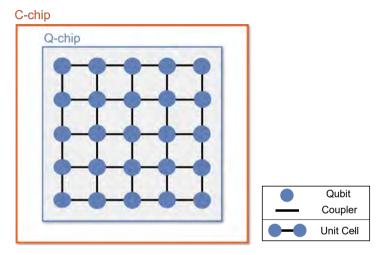

Why do we first design a small SQP like in Figure 1.1(b)? It is quite easy to see that such a 2-qubit pair design can be viewed as the unit cell of a larger SQP with a square qubit lattice. An SQP with only 2 qubits can be used to do some interesting scientific experiments [22, 23], but to demonstrate that a quantum computer is superior to its classical counterpart, thousands or even millions of qubits need to be linked together [24].

Specifically, there are two factors that result in the need for a large number of qubits. The first one comes from the necessity of using a quantum computer. For example, as Feynman discussed in his paper [1], when a quantum system is small, we can still simulate it using classical computers. Only when the system has too many variables can the benefit of using the quantum computer surpass the cost of building it. What's more, we believe that the larger the quantum system we can simulate, the more interesting phenomena we can observe, as P. W. Anderson has claimed [25]. A similar argument can also be used for all other quantum algorithms including Shor's algorithm. We always pursue those quantum algorithms that can be run exponentially faster than their classical counterparts for a fixed size of the problem. Conversely, you can say that when the problem is small, it may not be cost-efficient to solve it using a quantum computer.

Another factor comes from the imperfection of qubits. Perturbation from their surrounding environment is unavoidable since the qubits are not completely isolated. We describe different kinds of perturbation as different noise channels of the qubit. To overcome these noises, such that the qubit can stay at a target state for as long as we want, we can either make efforts to suppress these noise channels by better fabrication [26] and engineering [27], or to correct the errors incurred by the noise by implementing a quantum error-correcting code [6]. Similarly to classical error-correcting codes [28], a quantum error-correcting code requires redundancy, meaning that one uses more than one qubit to represent a single logical qubit in an abstract way. For example, with the

quantum repetition code, we can represent a logical qubit by N physical qubits with

$$|\psi\rangle_L = \alpha_L |0\rangle_L + \beta_L |1\rangle_L = \alpha_L |\underbrace{0...0}_{N}\rangle + \beta_L |\underbrace{1...1}_{N}\rangle.$$

(1.3)

Notice that  $|\psi\rangle_L$  is an entangled state if  $\alpha_L$  or  $\beta_L$  is not equal to zero. The more physical qubits you link together for one logical qubit, the longer the state of this logical qubit can last against errors [2, 29]. As the size of the target problem keeps increasing, better qubits are always needed. For quantum error-correcting codes, a better logical qubit means more qubits, i.e., the SQP needs to scale up.

#### 1.4 Challenges ahead

However, scaling up an SQP is not easy. At every step of producing a working SQP, i.e., its design, fabrication, and operation, there are limits on the number of qubits that can be involved.

Typically, the finite amount of resources imposes most of such limits on the possible scale of the final produced SQP. A relatively fixed resource is needed to design a single qubit, including its control and readout components, and linked couplers. For example, each qubit's parameters need to be optimized along with surrounding qubits and then realized with the help of simulations. Therefore, trying to reduce the design cost per qubit is a must to scale up the SQP. When the qubit number is large, a small reduction in design cost per qubit can significantly affect the SQP's total resource expense.

The fabrication of an SQP not only constitutes a fixed resource cost per qubit, but also has a large overhead that increases with the scale of the SQP. Usually, the footprint of a qubit on the SQP is a fixed quantity: as the number of qubits increases, so does the overall size of the SQP. Considering the cost of fabrication, such an increase in the SQP's size likely reduces the yield of each fabrication run due to fabrication variations and defects [15], which necessitates costly process development and upgrades to the tool set.

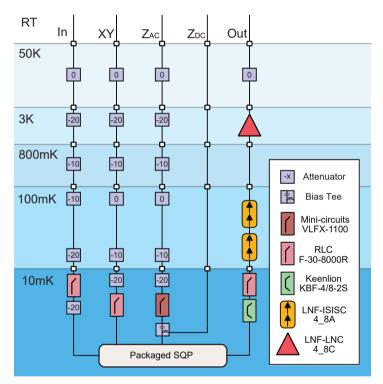

The effort to ensure the constant operation of an SQP also should not be underestimated. As the size of the computational problem increases, so does the number of qubits involved and the complexity of the qubit control system. Continuous calibration of every qubit is needed to achieve stable high-fidelity qubit control [4]. To correctly and continuously execute quantum algorithms on the SQP, a complex software stack with layers of abstraction is built upon the physical device and needs to be maintained [30, 31]. Although similar concepts apply in classical computing, the particularities of the quantum hardware and ways of operating a quantum computer bring a whole new set of challenges to hardware and software engineering. From the hardware perspective, to enable the control and readout of every qubit within the SQP, the number of electronic control devices should align with the scale of the SQP, which results in a correspondingly increasing heat dissipation, putting high demands on the cooling system at both ambient and cryogenic environment [32].

Apart from finite resources, another challenge that scales together with the SQP is qubit interference. With an increase in size, the total crosstalk induced by other qubits

for each qubit within the SQP will also increase. The level of crosstalk must decrease rapidly with the qubit-qubit distance at a threshold rate in order to ensure each qubit's functionality, as we discuss in Paper E. This requirement brings additional architecture, design, and fabrication improvement as the SQP scales up.

Finally, as the physical size of the SQP increases with the qubit number, those noise channels that scale with chip size will transition from being negligible to significant. For example, the impact of high-energy radiation only becomes noticeable when the SQP is large enough, and the frequency of occurrence of such an impact can reach once per 10 seconds [33], which is detrimental to logical qubit state computation using quantum error-correcting codes. Eventually, much more work needs to be done to mitigate such an impact [27].

#### 1.5 Thesis outline

As there are so many challenges ahead, scaling up a superconducting quantum processor is a complex and difficult task. This thesis covers the works that I have contributed to this project, focusing on tackling the design and simulation challenges.

Chapter 2 briefly introduces the background of 3-dimensional (3D) integration technology. First, it reviews the advanced packaging technologies used by the semiconductor industry. And then it discusses the reasons why we would like to adopt these technologies into the SQP to scale it up further, and the differences in the implementation compared to the semiconductor industry. It also discusses the requirements for implementing 3D integration technologies in SQPs.

Within the new architecture, modification of the SQP design and fabrication process is necessary. **Chapter 3** shows the architecture of the flip-chip integrated SQPs, and the modified design of every component within the SQP. In particular, we demonstrate the similar performance of these components to that of single-chip designs. It also discusses the variation effect of interchip spacing on the SQP design, an additional variable imposed by the flip-chip architecture. This chapter covers the works in Paper A, B and C.

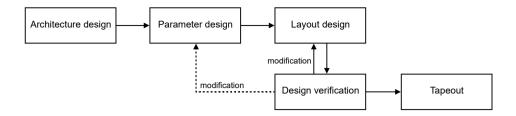

With successful designs of SQP components in the flip-chip architecture, **Chapter 4** then discusses how to design a scaled-up flip-chip integrated SQP in detail. It goes through a design workflow that includes architecture, parameter, and layout design, and then discusses the design verification step that will become more and more necessary when the size of the SQP becomes larger. This chapter summarizes our design experiences of the SQPs used in Paper D and E.

Chapter 5 focuses on how to speed up the design and simulation of the readout resonators, a necessary component to read out the state of qubits. It shows that we can use only the 2-dimensional (2D) cross-section of the resonator to predict its resonant frequency and coupling quality factor to its readout line. Such work is important because each qubit needs one readout resonator, and when the scale of SQP is large, saving the computational resources spent on these resonators, e.g., reducing the simulation time by three orders of magnitude, can greatly accelerate the design workflow. It also shows a modified resonator design that can overcome the effect of variations of the interchip spacing discussed in Chapter 3. This chapter is based on the work of Paper D.

This thesis ends with a summary in **Chapter 6** and appended papers that have been mentioned above. Though a single PhD thesis definitely cannot contain all the aspects of scaling up an SQP, I hope this thesis can give the reader a clear overview and some understanding of the challenges we face and the solutions we propose, so as to finally build a quantum computer that can benefit society.

## CHAPTER II

## 3-dimensional (3D) integration technology

In the history of the semiconductor industry, the chip packaging technology generally evolves together with the scaling of the chip [34]. Recently, rather than making a monolithic system-on-chip (SoC), building up a SoC by so-called chiplets [35] has become a trend to satisfy end users' growing needs of system performance while at the same time keeping the cost down, since not every functionality within the SoC needs the most advanced fabrication process. As a result, advanced packaging technologies [36] that serve to integrate these chiplets into one SoC are becoming a hot topic within the semiconductor industry. Coincidentally, in the field of superconducting quantum computing, the scale of SQPs has reached a level where adopting 3D integration technologies from advanced packaging technologies has become a necessity.

This chapter starts with a brief review of the advanced packaging technologies currently used by the semiconductor industry. We then shift our attention to quantum chips, discussing the reason why people introduce 3D integration technologies into SQPs, and the differences between classical chips and SQPs regarding these technologies. We then talk about the challenges of implementing 3D integration technologies into SQPs and these technologies' future trends.

## 2.1 Advanced packaging in semiconductor industry

Following the exponential increase of the transistor number that Moore's law [37] had successfully predicted, the packaging technology has also evolved to keep up with the pace of the increase of the chips' input/output (I/O) density and data speed [34]. Following years of development, more and more complex packaging technologies have been developed to integrate the most advanced chips of each generation.

In the early times, packaging was a step after the chip was made, during which the chip is encapsulated by the epoxy molding compound and placed on top of an organic or ceramic printed-circuit board (PCB), like surface-mount technology [38]. However,

as the chip becomes denser and smaller, the first packaging step that a silicon chip experiences is more and more likely to be another silicon chip for signal routing, before being encapsulated and placed on the PCB. Such advanced packaging step often occurs in 2.5-dimensional integrated circuits (2.5D-IC) or 3D-IC [36].

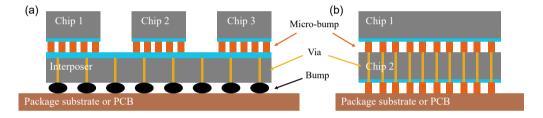

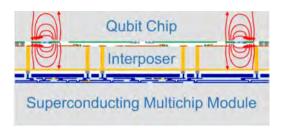

A 2.5D-IC architecture typically includes an interposer made of silicon to host the connections between chiplets that have different functionalities. As shown in Figure 2.1(a), the chiplets are attached to the interposer through micro-bumps using flip-chip bonding technology. After that, the interposer is again attached to the package substrate or PCB using a different bonding technology. To reach the transistors on the top chips, signal and power go through bumps between the layers and vias within the interposer. For 3D-IC, the difference is that the connection between chips is not through an interposer, but by stacking one chip on top of another chip through flip-chip bonding, with bumps between the two chips and vias within the bottom chip to deliver signal and power to the top chip, as shown in Figure 2.1(b).

Figure 2.1: (a) 2.5D-IC architecture. (b) 3D-IC architecture.

As we can see, both 2.5D and 3D-IC have used the flip-chip bonding technology to integrate the chips together. Actually, flip-chip bonding technology was invented quite early. Historically, in order to increase the I/O port number between the chip and the PCB, people transitioned from putting the I/O ports on the four edges of the chip to the front side of the chip, such that the port number can increase with the square of the chip's size, rather than just linearly [39]. As a result, the chip then needs to be flipped and bonded using bumps to facilitate its connection to the PCB. Following the increase of the chip's transistor count and density, both the pitch between bumps and the size of the bump shrink considerably to match the increase of I/O number, but such a packaging method is always called flip-chip bonding technology.

Via connections is another technology that is always required by 2.5D and 3D-IC architecture. If the interposer or the bottom chip is made of silicon, through-silicon vias (TSVs) that are filled with conductive metal are used to realize the signal and power connection between the top side and the bottom side of the interposer or the bottom chip. When the chip's transistor density increases, the pitch of the TSVs will decrease accordingly.

#### 2.2 3D integration in SQP

Typically, qubits within an SQP are fabricated on the surface of a silicon chip, the same substrate used for complementary metal-oxide-semiconductor (CMOS) transistors [40]. In the CMOS process, the transistor's source, drain, and gate are made within several layers on the chip surface. However, unlike the semiconductor chip with transistors that are able to proceed to build additional layers of interconnects on top of the transistors to link them together on the same chip, the general practice in SQPs is to keep qubits facing the air, so as to avoid additional losses [41] that are detrimental to the qubit coherence. As a result, the control and readout lines to address these qubits have to route on the same plane as the qubits from the edge of the SQP, and then connect to the PCB via wirebonds, as illustrated by Figure 2.2.

Figure 2.2: A single-chip 5-qubit SQP at our lab. There are wirebonds connecting SQP's control and readout lines from SQP's launch pads on the edges to the CPW lines on the PCB (gold). Within the SQP, the control lines on the top part of the SQP are using airbridges [42] to jump across the readout lines of the qubits (red circles with a zoom-in image of the airbridges at the crossing point.). Photo of the SQP is taken by Dr. Christopher Warren.

#### 2.2.1 Separating the qubits from their control lines

When the SQP is scaling up, meaning the qubits are linked by couplers to form a square lattice, routing lines on the same layer as that of qubits cause problems. Since each qubit needs at least one control line, to address the center qubit of a  $3 \times 3$  square lattice, crossover is unavoidable between the control line and the couplers along the way. When the qubit number is small, the crossover can be resolved by using airbridges to make the control lines jump over the coupler [43], as shown in Figure 2.2. However, as the number

of qubits increases, so do the number and the density of these crossovers. Continuing using airbridges can result in a low yield of the SQP fabrication and considerable crosstalk between couplers.

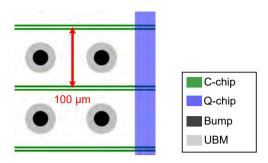

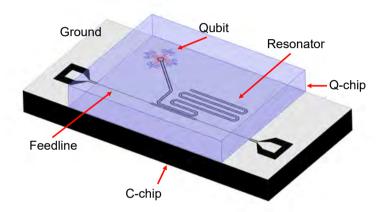

To avoid using airbridges, and at the same time satisfy the constraint that qubits should face the air first, putting all the lines on another chip's surface and making this chip's surface hover above the qubits and couplers with a distance, is a natural solution. We call the chip that hosts lines the control chip (C-chip), while the chip that hosts qubits and couplers, the qubit chip (Q-chip). The separation between the C-chip and the Q-chip can be realized by the flip-chip bonding technology similar to the technology in advanced packaging [44], with bumps located around the qubits and couplers on the Q-chip side, and the lines on the C-chip side passing through the rows of bumps, as illustrated by Figure 2.3.

Figure 2.3: 3D model of a flip-chip 2-qubit SQP, where C-chip and Q-chip are separated by bumps sitting between the two under-bump metalization layers (gold color dots). A detailed description of this flip-chip architecture is in Chapter 3.

#### 2.2.2 Controlling the qubits vertically

As the number of lines to control the qubits increases with the scale of the SQP, we will face the same problem as the classical semiconductor chip, in which the chip size is mostly determined by the number of I/O ports on the edge. A mere separation of the SQP into two chips cannot solve this problem. However, if the control lines can vertically approach the qubit, not only can we eliminate the crossovers, but we can also vastly reduce the required chip size, since now the allowable number of I/O ports is proportionally increased with the chip area, rather than the chip's edge length.

For single-chip SQPs, the lines can be realized by vertical pins directly penetrating from the sample holder's lid [45, 46]. If the SQP has been separated by C-chip and Q-chip using flip-chip bonding technology, the lines can then be vertically routed through the C-chip by vias, and fanned out on the back side of the C-chip, as illustrated by Figure 2.4.

**Figure 2.4:** Cross-section of a flip-chip integrated SQP implemented with TSVs, in which the C-chip is called interposer, and there is a third chip under the C-chip to redistribute the lines to the outside. Figure adapted from Reference [47].

#### 2.2.3 Differences from classical advanced packaging technologies

It is easy to see the similarity of SQP architectures, as described above, to 2.5D-IC, where we can view the C-chip as the interposer and the Q-chip as an active classical chip. Or, if we put some qubits on the C-chip, the architecture more closely resembles 3D-IC. Therefore, people may think that we can directly adopt the advanced packaging technologies used in the semiconductor industry during the scaling up of the SQP. However, since the working principles of a superconducting qubit and a transistor are not the same, there will be differences between the implementations of 3D integration technologies on these two kinds of chips.

The first difference is the usage of underfill [38]. The step after the flip-chip bonding for 2.5D-IC and 3D-IC generally includes injecting underfill between the chip and the interposer (or another chip) to strengthen the package's mechanical robustness and isolate the bumps from the environment. However, for SQPs, to fulfill the requirement that qubits should face air to avoid additional losses has blocked the potential usage of underfill. As a consequence, the mechanical robustness of the flip-chip integrated SQP may be lower than the classical semiconductor chips.

The second difference is the role of bumps and vias. For a transistor to work, it needs a stable current supply to be able to go through its source and drain. But for a superconducting qubit, it ideally only needs pulsed microwave signals through capacitively-coupled control lines as an energy supply to change its state. (A different case is frequency-tunable qubits [7] and couplers; they need constant current to generate fixed-amount magnetic flux to maintain their frequencies, but the current doesn't need to go through the qubits/couplers directly.) Therefore, the bumps in an SQP are not necessary to facilitate the delivery of energy. They can work only as mechanical support and galvanic connections between the Q- and C-chip. On the other hand, in addition to delivering microwave signals to the qubits, the vias also connect the chip's two sides galvanically and suppress the low-frequency chip mode that may act as the mediator of qubit crosstalk.

The third difference is in the property of components. From the eyes of an electrical engineer, there is no active component inside an SQP. A superconducting qubit/coupler is no more than a parallel combination of a capacitor and an inductor (with some non-linearity), which can still be categorized as passive elements [48]. Therefore, there is

no strict rule to forbid us from moving qubits, resonators, etc. between the Q-chip and the C-chip with adjusted designs. From this aspect, a flip-chip integrated SQP has an architecture that sits in the middle between 2.5D and 3D-IC architectures.

#### 2.2.4 Implementation requirements

When we make an effort to introduce a new architecture to our SQPs, we always want such a change to improve some aspects of the SQP while not causing a severe hit on its other properties. 3D integration technologies are known to improve the scalability of an SQP, but to clear their way to becoming well-accepted technologies used, there are two obstacles that we have to overcome.

The first one is the maintenance of the SQP's performance. Since a qubit's surrounding electromagnetic environment will be altered under the new architecture, and will go through additional fabrication processes, it is then reasonable to ask whether the coherence of the qubits in the new SQP can be at least the same as that of the old, single-chip SQPs. The same question can also be asked for single-qubit and two-qubit gate fidelities. If the resulting performance of the SQP with the new architecture is worse than the old one, it means that either the introduced additional loss on the qubit is significant, or there are some unknown effects. Both cases will create more uncertainties regarding the relationship between the performance and the complexity level of the design, and in the face of large uncertainties, people usually hesitate to move forward.

The second obstacle is the reduced yield of the fabrication. In general, there is a cumulative decay of the yield of the final device if each fabrication step has a yield less than 100% [49]. To obtain an acceptable yield of the SQP in the end, adding one more fabrication step means that the yield of each previous step needs to improve accordingly. Since moving SQPs to the 3D architecture will certainly add multiple steps to the whole fabrication process, maintaining the original yield, or even trying to improve it, at the same time will be a very hard task, but it is necessary for keeping the overall fabrication cost down.

#### 2.3 Discussion of the future trend

Similar to the development of semiconductor chips, the required density of bumps and vias on SQPs will increase dramatically in the future. Current superconducting qubits typically have a size at the order of hundreds of micrometers [50–52]. Taking its size as 500  $\mu$ m, with 1000 qubits we will need at least 256 mm<sup>2</sup> of the chip area, which is already comparable to the size of modern processors, but later has billions of transistors [53]. If such a qubit size is kept constant, the chip area will be too large for hosting millions of qubits [24]. Therefore, reducing the qubit size is necessary, along with the pitch and the size of bumps and vias if 3D integration technologies are implemented. We can expect that the most advanced packaging technologies in 2.5D and 3D-IC will be adapted to SQPs to meet such needs accordingly.

On the other hand, as the number of qubits increases, so does the number of control lines for qubits and couplers within the SQP. However, when the SQP has millions of qubits, it is economically unrealistic to connect all these lines to the room temperature

microwave sources and measurement tools as we do in our current setups [32]. Efforts are already under way to reduce the number of I/O lines between ambient and cryogenic temperature by replacing room-temperature arbitrary waveform generators with digital logic units at cryogenic temperature close to the SQP [54, 55]. Following the trend, such a logic unit can be integrated together with the SQP within one package, similar to the system-in-a-package (SiP) technology in the semiconductor industry.

## CHAPTER III

## Flip-chip integrated SQPs

As a widely used packaging method in the semiconductor industry [36], flip-chip bonding of one chip onto another is a mature technology. However, unlike transistors in classical semiconductor processors, qubits inside the superconducting quantum processor (SQP) are much more sensitive to defects surrounding them, hence the performance of SQPs may suffer from the additional fabrication processes for flip-chip integration. In addition, one may ask whether a qubit's coherence can still be maintained when there is an another chip hovering a few micrometers above the qubit.

This chapter shows the performance of the essential components of a flip-chip integrated SQP. It will show that the performance of these components is similar to that of the single-chip architecture, demonstrating that the change in the electromagnetic (EM) environment and additional fabrication processes do not necessarily degrade the performance of an SQP, while transitioning to the flip-chip architecture can significantly improve its scalability.

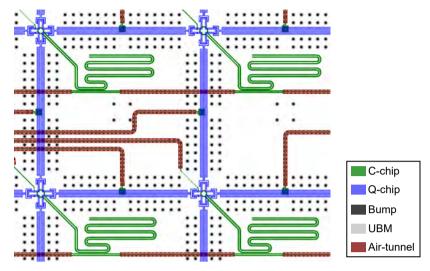

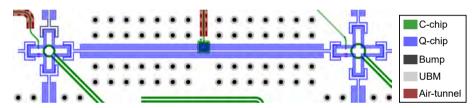

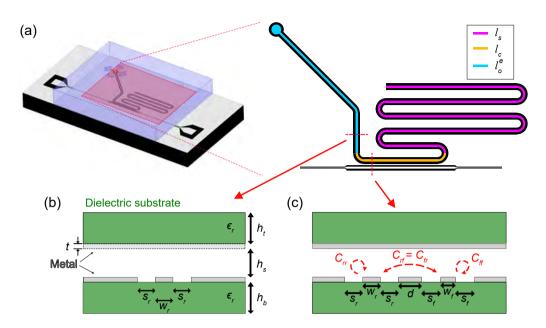

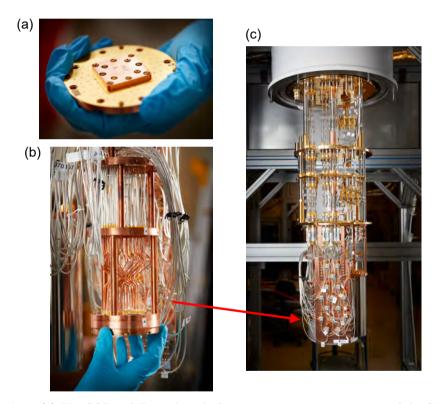

## 3.1 3D structures in flip-chip integrated SQPs

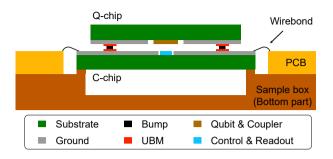

Our flip-chip integrated SQPs consist of two chips. The top chip is called the qubit chip (Q-chip), which contains qubits and couplers that are the basis of SQPs. The bottom chip is called the control chip (C-chip), containing all the components and feedlines to control and read out the qubits. By separating these components into two chips, SQP's scalability can be improved by simplifying the signal routing and suppressing crosstalks among qubits and couplers. In our flip-chip architecture, the components on the surface of each chip face each other after flip-chip bonding the Q-chip onto the top of the C-chip. See Figure 3.1, which shows the cross-sectional schematic of a flip-chip integrated SQP.

**Figure 3.1:** Cross-section of a flip-chip integrated SQP (not to scaled). Our flip-chip integrated SQP is connected to the outside world through a PCB via wirebonds and is encased in a sample box.

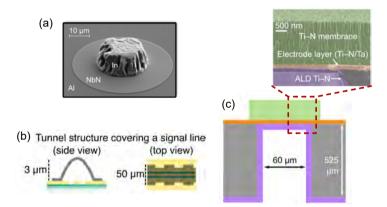

**Figure 3.2:** 3D structures for flip-chip integrated SQPs. (a) The scanning electron microscope (SEM) image of a bump sitting on top of UBM and the ground metal plane on the surface of the C-chip or Q-chip before the flip-chip bonding process. (b) Air-tunnel that covers the feedlines on C-chip. (c) a TSV that goes through the chip's substrate, with a zoom-in SEM image of each layer's material, fabricated by VTT (Paper B).

Figure 3.2 shows additional 3D structures that are implemented in our flip-chip integrated SQPs. Most of these structures are not new, as they have been widely used in semiconductor industries. The challenge lies in the choice of materials and fabrication processes that can maintain the performance of the SQP that has been achieved in the single-ship architecture [22].

Following is a brief description of 3D structures in flip-chip integrated SQPs:

- Air-tunnel: The air-tunnel is a 3D structure that is similar to airbridges used in single-chip SQPs [42]. Its usage is to suppress the feedlines' slotline mode and to stitch the separated ground plane of the chip to minimize the parasitic modes due to feedlines or other components on the chip, and shorten the return current path to minimize the flux crosstalk.

- Bump: Bumps act as the main supporting structure in the flip-chip integrated SQP to separate the top and the bottom chips. The interchip spacing is the most important parameter introduced by the flip-chip architecture since it can influence all components within the SQP. The height of a bump after bonding determines the interchip spacing. The bumps are generally chosen to be superconducting at cryogenic temperature, so they are also used as a conducting path between the ground planes of the two chips. A well-designed bump pattern across the SQP can reduce or even eliminate the need for air-tunnels in flip-chip integrated SQPs, as in Paper E. Bumps can also be used for signal routing from one chip to another chip [56].

- Under-bump metalization (UBM): UBMs consist of one or several layers of thin films between the bump and the wiring layer. Their main purpose is as a diffusion barrier to avoid the direct contact between the bump material and the top metal layer of the chip, which may otherwise form intermetallic compounds [44, 56]. In addition, UBM can help with bump formation and ensure a galvanic connection between bumps and the chip's ground plane.

- Through-silicon via (TSV): TSV is a vertical structure etched through the silicon substrate of the chip. By depositing a thin metal layer within the via, it can provide galvanic connectivity between the two sides of the substrate, such that signals can be routed between the two. By connecting both sides' ground planes, the fundamental frequency of the device's chip mode can be shifted well above the working frequencies of the SQP [56, 57]. It also can directly work as part of a qubit or a readout resonator of the SQP [58].

#### 3.2 Fabrication process

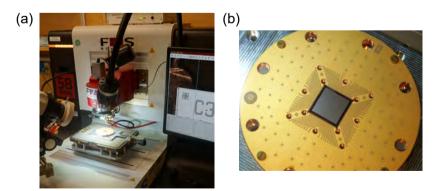

In this section, we will briefly describe how flip-chip integrated SQPs have been made in our laboratory. A more detailed description of the fabrication process can be found in Paper A.

We use high-resistivity intrinsic silicon wafers as the substrate for both the Q-chip and the C-chip. We do the wafer cleaning process by going through Standard Cleaning 1, a generally used cleaning procedure for removing organic residue from silicon wafers, and HF dip for removing native oxide on the surface of the silicon wafers [59], and then immediately load the wafer into the evaporator. We deposit an aluminum (Al) thin film on top of the substrate, then sputter a niobium nitride (NbN) thin film on a patterned lift-off resist to form UBMs. The wiring layer of the chip is defined by etching out of the Al film.

We fabricate Josephson junctions using the patch-integrated cross-type technique [60] on the wafer containing the Q-chips. Next, indium (In) is evaporated on a patterned thick resist, and 7  $\mu$ m-high In bumps are formed after resist lift-off. The Q-chip and C-chip are diced from the wafers, and the Q-chip is flip-chip bonded to the C-chip by mechanical compression by approximately 50% at room temperature.

The fabrication of TSVs was developed independently for a single-chip device and has not yet been integrated into the fabrication process of flip-chip integrated SQPs. The via holes of the TSVs are etched through the back side of the wafer and stopped by the thick titanium nitride (TiN) membranes patterned on the front side. The inner walls of the vias and the back side of the wafer are coated with TiN to enable conductivity between the front and the back side of the chip. A detailed fabrication process of TSVs can be found in Paper B.

### 3.3 Individual qubit performance

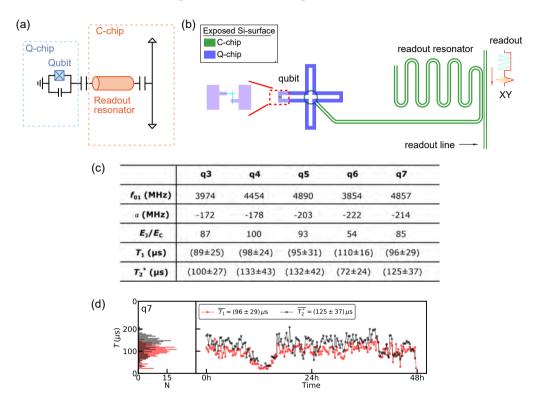

It is necessary to show that the additional fabrication processes of flip-chip integrated SQPs do not degrade qubit coherence compared to those of a single-chip architecture. The coherence of individual qubits in a flip-chip architecture, i.e. qubits not connected by couplers, is a good benchmark. Figure 3.3(a)-(b) shows the circuit diagram and the layout of such an individual qubit, together with its readout resonator.

Figure 3.3(c)-(b) shows qubits' relaxation time  $T_1$  and decoherence time  $T_2^*$  that are comparable to what we usually achieve in the single-chip architecture [22].

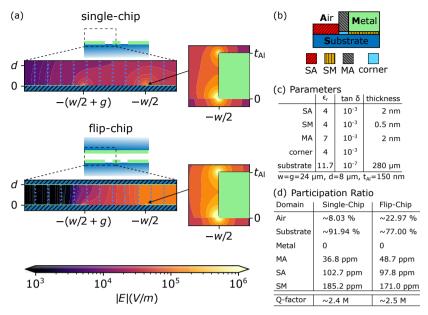

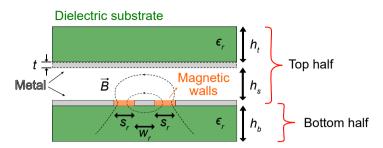

To illustrate the reason why the flip-chip fabrication process has not degraded the qubit coherence, we conduct 2D EM simulations on the cross-section of a CPW line in both single-chip and flip-chip architecture. Since the majority of coherence loss of the qubit at cryogenic temperature comes from the two-level systems (TLS) [41] within the interfaces between metal thin film, substrate, and the vacuum (air), we can obtain a Q-factor of the cross-section by simulating the energy participation ratio of each interface and calculate it using the following equation [26]:

$$1/Q = \sum_{i} p_i \tan \delta_i, \tag{3.1}$$

where  $p_i$  is the simulated participation ratio for each domain i and  $\tan \delta_i$  is the domain's loss tangent. The participation ratio  $p_i$  of a domain  $\Omega_i$  is calculated by

$$p_i = \frac{w_i}{w}, \qquad w_i = \int_{\Omega_i} \epsilon_{\rm r}(\Omega_i) \left| \vec{E}(\vec{r}) \right|^2 d\vec{r}, \qquad w = \sum_i w_i,$$

(3.2)

where  $\epsilon_{\rm r}(\Omega_i)$  is the relative permittivity of domain  $\Omega_i$ , and  $\vec{E}(\vec{r})$  is the simulated electric field (E-field).

Figure 3.4(a) shows the E-field distribution of both architectures. We found similar Q-factors of CPW lines in single- and flip-chip architectures, as shown in Figure 3.4(d), indicating that the total loss that a qubit experiences is similar within both architectures. The detailed simulation setup can be found in Paper A.

Figure 3.3: (a) Circuit diagram of an individual qubit, separating Q-chip and C-chip. (b) The physical layout of the qubit, with a zoom-in illustration of the Josephson junction design. The qubit's control (XY) pulse and readout pulse are sent from its readout line. (c) Table of parameters of five measured individual qubits.  $f_{01}$  is qubit's frequency and  $\alpha$  is the anharmonicity of the qubit.  $E_J$  is the Josephson energy and  $E_C$  is the charging energy [13]. (d) Example of qubit's coherence times  $T_1$  and  $T_2^*$  fluctuations over time of one of the qubits, with accumulated histograms.

Figure 3.4: 2D simulation of the E-field within the single-chip and flip-chip architecture. (a) Contour plots of the E-field magnitude for the same CPW geometry in both single-chip and flip-chip environments. The arrow indicates the direction of the E-field. (b) Designation of the various domains for the participation ratio simulation. (c) Parameters used in the simulation. (d) Calculated total Q-factor and participation ratios of the different domains for both single-chip and flip-chip architectures.

#### 3.4 Two-qubit pair as a unit cell

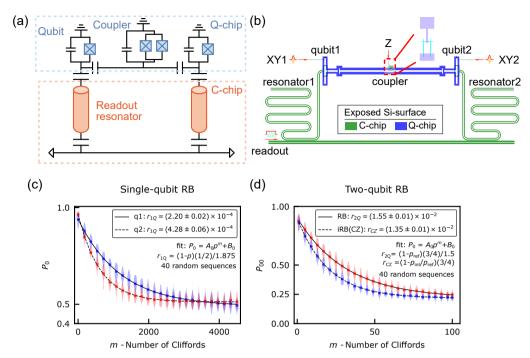

An SQP contains not only qubits but also couplers between the two adjacent qubits, which enable two-qubit interaction. A proper design of a two-qubit pair containing two qubits and one coupler, together with their control and readout components on the C-chip, can work as a basic unit cell to construct SQPs with arbitrarily large numbers of interconnected qubits. Figure 3.5(a) and (b) show the circuit diagram and the physical layout for a two-qubit pair in flip-chip architecture.

As illustrated by Figure 3.5(b), for such a coupled two-qubit design, the single-qubit gate is performed via the drive line beneath the qubit. Since we use the parametric controlled-phase gate [61, 62] as our native two-qubit gate, a flux-tunable qubit is used as a coupler, and we control the coupler through the current loop at the end of the flux line. The qubit's states are read out through their corresponding readout resonators. Figure 3.5(c)-(d) show the fidelities of both single- and two-qubit gates using randomized benchmarking experiments [63], and their values are comparable to what we can achieve in the single-chip architecture [22].

Figure 3.5: (a) Circuit diagram of the two-qubit pair design, separating Q-chip and C-chip. (b) The physical layout of a two-qubit pair, with a zoom-in illustration of the SQUID (superconducting quantum interference device that made of a loop of two parallel Josephson junctions such that the coupler's frequency is tunable by the magnetic flux.) of the coupler. The control (XY) pulse and readout pulse are sent to the qubit through the drive line and the readout line separately. The coupler is controlled through a flux (Z) line. (c) Measured single-qubit gate fidelity ( $\approx 99.95\%$ ) and (d) two-qubit gate fidelity ( $\approx 98.65\%$ ) using randomized benchmarking (RB) and interleaved randomized benchmarking (iRB).

### 3.5 Purcell filter for qubit readout

To read out the state of a qubit, the qubit must couple to a readout line. However, such coupling creates an energy leakage channel for the qubit. The stronger the coupling for faster measurement, the worse the leakage will be. Generally, to suppress such leakage, and at the same time still realize fast measurement of the qubit, a readout resonator is dispersively coupled to the qubit [13]. The measurement of the qubit state is then realized by monitoring the resonator's qubit-state-dependent resonant frequency through the readout line that is coupled to the resonator only. However, though suppressed, the energy leakage of the qubit cannot be completely eliminated. The decaying mechanism of qubit excitation through its readout resonator is called Purcell decay [64], which is in essence the excited qubit's spontaneous emission of a photon into the readout resonator.

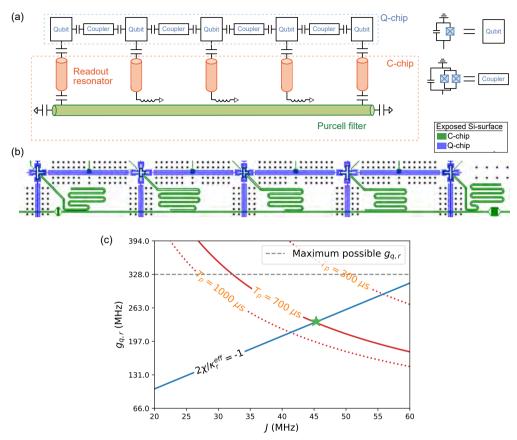

To further suppress the qubit energy leakage, a second resonator is introduced between the first resonator and its readout line. We call the second resonator the Purcell filter [65]. When multiple qubits and their readout resonators exist, each qubit's readout resonator can couple to one Purcell filter that has the same resonant frequency and bandwidth as the readout resonator [66]. Alternatively, the Purcell filter can be a long single-pole resonator that simultaneously couples to multiple readout resonators, hence multiple qubits at the same time, with its central resonant frequency near the readout resonators' frequencies and a large bandwidth to include all the coupled resonators [67], while the qubit frequencies lie at the high attenuation part of the Purcell filter transmission spectrum. Such a Purcell filter can be called a common Purcell filter. Detailed theory describing how Purcell filter works can be found in Paper C.

Both types of Purcell filters can be implemented in flip-chip integrated SQPs. We choose to use the common Purcell filter because of its simplicity in layout and less sensitivity to the variations in the fabrication process. Figure 3.6 shows the circuit diagram and the layout design of such a Purcell filter, together with a parameter optimization diagram for one qubit coupled to this Purcell filter.

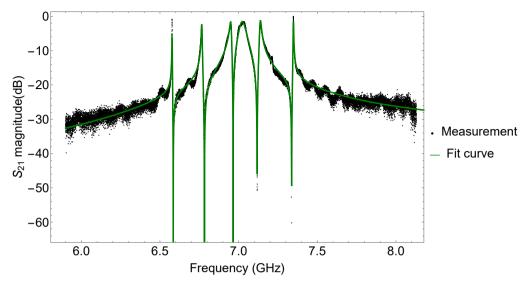

Benefiting from the further suppression of the qubit's Purcell decay, we can now design the qubit to be much more strongly coupled to its readout resonator, such that the readout speed can be significantly increased while at the same time retaining the qubit's high coherence. The transmission spectrum of the Purcell filter together with five strongly coupled readout resonators is shown in Figure 3.7. Table 3.1 shows the measurement time  $(\tau_m)$  of the Purcell filter-protected qubits (Q16-Q20) when their two-state readout assignment fidelity reaches maximum  $(\mathcal{F}_a^{max})$ , compared to those qubits without Purcell filter (Q21-Q25). In general, qubits protected by the Purcell filter exhibit higher readout fidelity with shorter measurement time.

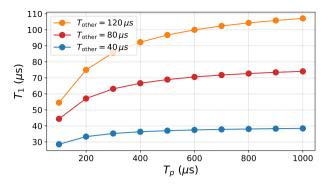

It is noticeable that both kinds of qubits have similar coherence times  $(T_1, T_2^*)$  that are much smaller than Purcell limit  $T_p$ , the relaxation time limit of the qubit due to Purcell decay, meaning their coherence times are limited by loss channels other than the Purcell decay. To illustrate, Figure 3.8 shows that the  $T_1$  of the qubit is capped by losses from other channels if  $T_p$  is much higher than  $T_{\text{other}}$ , where  $T_{\text{other}}$  is qubit's relaxation time limit if it has no Purcell decay. It is worth emphasizing that the goal of Purcell filters in SQPs is to retain the qubit coherence while improving the qubit's readout fidelity and shortening the measurement time by increasing the coupling rate  $g_{q,r}$  between the qubit and the readout resonator. To this end, our implementation of the Purcell filter in the flip-chip integrated SQP has fulfilled this goal.

Figure 3.6: (a) Circuit diagram and (b) physical layout example of five qubits and readout resonators coupled to a common Purcell filter. The Purcell filter is a half-wave  $(\lambda/2)$  resonator defined by two capacitors which impose open boundary conditions at the input and output ports of the readout line. (c) Parameter optimization diagram of one of qubits coupled to the Purcell filter to determine the qubit-resonator coupling rate  $g_{\mathbf{q},\mathbf{r}}$  and resonator-filter coupling rate J that satisfy the optimal readout condition  $2\chi/\kappa_r^{\mathrm{eff}} = -1$  [13], and the resulting Purcell limit  $T_p$ . Here  $\chi$  is the dispersive shift of the readout resonator, and  $\kappa_r^{\mathrm{eff}}$  is the effective leakage rate of the readout resonator in the presence of the Purcell filter. The dashed line indicates the maximum possible  $g_{\mathbf{q},\mathbf{r}}$  our layout design can achieve.

Figure 3.7: The transmission,  $S_{21}$ , spectrum of the readout line with a common Purcell filer, coupled to five readout resonators and qubits. The fit function of the curve is theoretically derived in Paper C. Note that the qubit frequencies are below 6 GHz.

| Qubit | $f_{01}$ | $g_{\mathrm{q,r}}/2\pi$ | $T_p$     | $T_1$     | $T_2^*$   | $\mathcal{F}_a^{max}$ | $	au_m$   |

|-------|----------|-------------------------|-----------|-----------|-----------|-----------------------|-----------|

| Nr.   | (MHz)    | (MHz)                   | $(\mu s)$ | $(\mu s)$ | $(\mu s)$ | (%)                   | $(\mu s)$ |

| Q16   | 4208     | 126                     | 1535      | 36        | 46        | 99.44                 | 0.84      |

| Q17   | 5079     | 109                     | 1937      | 36        | 47        | 99.05                 | 1.04      |

| Q18   | 4398     | 278                     | 1369      | 44        | 72        | 99.07                 | 0.68      |

| Q19   | 4656     | 220                     | 2175      | 50        | 40        | 96.83                 | 0.66      |

| Q20   | 4033     | 255                     | 681       | 35        | 41        | 99.34                 | 0.78      |

| Q21   | 4964     | 53                      | 513       | 26        | 51        | 96.04                 | 2.08      |

| Q22   | 4420     | 55                      | 617       | 57        | 65        | 98.19                 | 1.75      |

| Q23   | 4855     | 46                      | 587       | 31        | 56        | 97.17                 | 2.1       |

| Q24   | 4167     | 66                      | 506       | 47        | 60        | 98.58                 | 1.97      |

| Q25   | 4766     | 58                      | 583       | 27        | 26        | 78.59                 | 1.07      |

**Table 3.1:** Qubit characterization results of two readout lines, in which one line is replaced by a common Purcell filter shown in Figure 3.6(b) and qubits on this line (Q16-Q20) are strongly coupled to the readout resonator, while another line has no the Purcell filter and qubits (Q21-Q25) are weakly coupled.

Figure 3.8: Expected qubit relaxation time  $T_1$  at different values of the Purcell limit  $T_p$ , considering losses from other channels that also limit the qubit's relaxation time to  $T_{\text{other}}$ . The resulting qubit relaxation time is calculated by  $1/T_1 = 1/T_p + 1/T_{\text{other}}$  [26].

### 3.6 Interchip spacing variation effect

In the flip-chip architecture, one of the most important parameters is the interchip spacing between the C-chip and the Q-chip. Since most of the components have a relatively large footprint on the chip, the variation of the interchip spacing can significantly affect the performance of the SQP components through the change of their self and mutual capacitances and inductances. This section shows how the interchip spacing affects these components under global and local variations of the interchip spacing across the processor. Since in our current multi-qubit, flip-chip integrated SQP design, which will be discussed in Chapter 4, all components on one chip face the ground metal plane of another chip, we only discuss such a scenario in this section. Discussions on the scenario in which the readout resonators face the silicon substrate of the opposite chip will be discussed in Chapter 5.

#### 3.6.1 Global variation

When there is a variation in the calibration of the flip-chip bonding force, or other factors resulting in a global variation of the height of the formed bumps prior to the bonding step, the fabricated flip-chip integrated SQP may have a homogeneous deviation of interchip spacing from the target value across the whole processor. This global shift will cause all components of the SQP to have certain deviations from their designed parameters.

A deviation of the interchip spacing changes a component's capacitances and geometric inductances to its surrounding ground plane and to other nearby components, which then change the component's other related design parameters, resulting in a deviation from its intended performance.

For CPW lines that make up the feedlines (qubit's drive line and readout line, coupler's flux line), readout resonators, and Purcell filters, the variation of interchip spacing propagates to the variation of the characteristic impedance of the CPW lines. Typically, the characteristic impedance of the feedlines is designed to be the same as lines outside

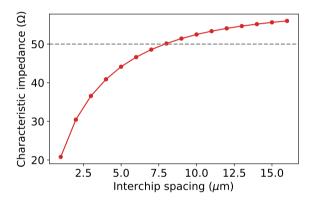

the SQP. The mismatch of the impedance at the boundary of the SQP, if the deviation of interchip spacing is too large, can cause significant input and output signal reflections [68], reducing the effectiveness of qubit control and readout. Figure 3.9 shows the change of the readout lines' characteristic impedance as the interchip spacing changes. For readout resonators and Purcell filters, a change in characteristic impedance results in a change in their resonant frequencies and, thus, their coupling rates to other components. A detailed derivation of the effect of interchip spacing on CPW lines and thus resonators will be discussed in Chapter 5.

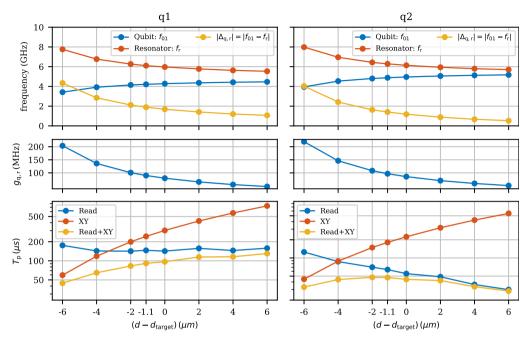

The interchip spacing that a qubit sees affects the qubit's frequency  $f_{01}$  and its coupling strength to its readout resonator  $g_{q,r}$  and drive line, as the capacitance between the qubit island and the C-chip's metal film on the surface is directly correlated with the interchip spacing. Figure 3.10 shows the effect of the interchip spacing deviation on qubits' parameters, in particular to its Purcell limit time  $(T_P)$  that sets the upper limit to the qubit's lifetime  $T_1$  in the absence of other loss channels.

Figure 3.9: Feedlines realized by CPW lines have characteristic impedance changing with the interchip spacing in the flip-chip architecture. The CPW line here has a center width of 9  $\mu$ m and a gap of 10  $\mu$ m. The gray dashed line indicates the characteristic impedance when the interchip spacing is at its target value of 8  $\mu$ m.

Figure 3.10: Qubit parameters change with the interchip spacing (d) when it deviates from the target value  $(d_{\text{target}})$ . The two qubits are from Figure 3.5(b) and the low Purcell limit time  $(T_P)$  of qubit 2 at  $d_{\text{target}}$  is due to higher-than-expected qubit frequency  $(f_{01})$  resulted from deviated Josephson junction size.  $f_r$  is the resonant frequency of readout resonator. Qubit's  $T_1$  limit due to decay through the drive (XY) line is also calculated and combined with qubit's Purcell decay within the figure.

#### 3.6.2 Local variation

The non-uniformity of the bump height across the chip (chip tilt) and the chip's own non-flatness (chip warp) can cause local variation over the flip-chip integrated SQP, meaning that depending on each component's location, a different interchip spacing is seen by the component, causing a mismatch of design parameters between two adjacent components. In addition, for components with large footprints, such as the common Purcell filter, the prediction of its parameters becomes much harder.

For example, under certain conditions, the chip tilt is detrimental to the multiplexing readout of qubits. As the number of qubits increases with the scale of the SQP, more and more qubits must be read out through their readout resonators that are coupled to a single readout line. Due to the limited bandwidth of arbitrary waveform generators, the resonant frequencies of these readout resonators need to be arranged within a small bandwidth. Currently, a 200 MHz frequency separation is used between different resonators. A 1  $\mu m$  change of the interchip spacing roughly corresponds to a 100 MHz shift of the resonator frequency (details will be shown in Chapter 5 and can be found in Paper D). This means that if the chip tilt causes two resonators that are close in frequency to have a 2  $\mu m$  interchip spacing difference, a frequency collision is expected to happen.

### 3.7 Further developments in flip-chip architecture

The full integration of TSVs is expected to be the next step in the development of the flip-chip architecture to improve ground plane stitching for the suppression of chip mode and parasitic modes. In addition, TSVs can be used for signal routing with the utilization of a redistribution layer (RDL) as a third layer below the C-chip [56] to simplify the wiring layer on the C-chip. The connection between TSVs and RDL can be realized by an additional sets of bumps between the C-chip and RDL.

Another promising development is to flip-chip bond multiple Q-chips (chiplets) to a single C-chip in a multi-chip module (MCM) [69], similar to 2.5D-IC architecture in the semiconductor industry. The major advantage of such a packaging method is to reduce the variation of Josephson junction resistance and the number of defects within the SQP. As the number of qubits an SQP is expected to host keeps increasing, so does the size of the Q-chip. Unfortunately, fabrication variation and the number of defects also increase with the size of the Q-chip. This results in a lower yield per fabrication round and translates to a too-high cost for making large SQPs. Treating each Q-chip as a chiplet with a small number of qubits can then enable us to scale up the SQP while keeping or even shrinking the size of the Q-chip. Supported by pre-bonding verification steps (Josephson junction resistance probe and defect inspection), we can discard those Q-chips with defects or those that are out of the parameter tolerance range. In this way, building a large SQP by flip-chip bonding of multiple 'good' small Q-chips on a large C-chip is feasible.

# CHAPTER ${ m IV}$

## Design of a multi-qubit, flip-chip integrated SQP