# Advancing GaN HEMT Technology for Microwave Applications: Investigations of Ohmic Contacts, Passivation, and Buffer-Free Concepts

Ding Yuan Chen

## **CHALMERS**

Microwave Electronics Laboratory

Department of Microtechnology and Nanoscience

Chalmers University of Technology

Göteborg, Sweden, 2025

Advancing GaN HEMT Technology for Microwave Applications: Investigations of Ohmic Contacts, Passivation, and Buffer-Free Concepts

DING YUAN CHEN

© Ding Yuan Chen, 2025.

Chalmers University of Technology Department of Microtechnology and Nanoscience - MC2 Microwave Electronics Laboratory SE-412 96 Göteborg, Sweden Phone: +46 (0) 31 772 1000

ISBN: 978-91-8103-159-1 Technical Report MC2 - 5617

Printed by Chalmers Reproservice Göteborg, Sweden 2025

# Abstract

High electron mobility transistors (HEMTs) based on gallium nitride (GaN) exhibit significant performance in high-frequency and high-power applications due to unique properties. For instance, high electron mobility, substantial saturation velocity, and elevated breakdown voltage. However, challenges including forming low resistivity ohmic contacts, trapping effects, and Two-Dimensional Electron Gas (2DEG) confinement impede further improvement.

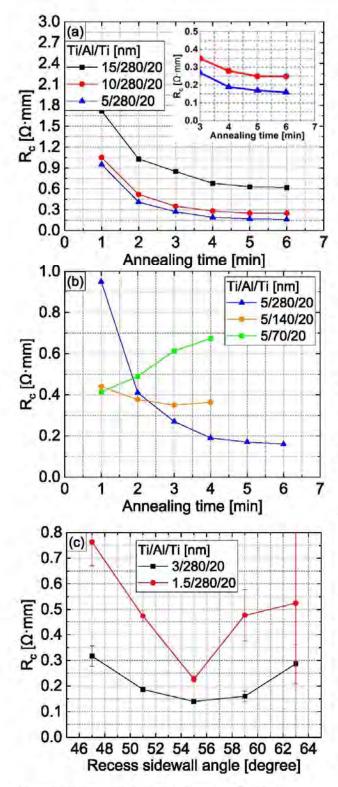

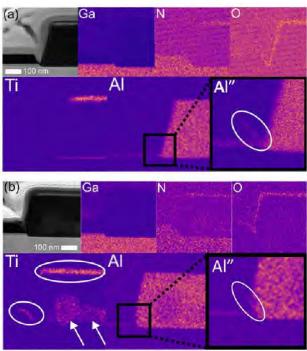

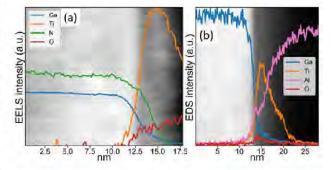

The formation of deeply recessed Ti/Al/Ti and Ta/Al/Ta sidewall ohmic contacts, using a low annealing temperature and achieving minimal contact resistance of 0.14 and 0.24  $\Omega$ ·mm, respectively, were explored. The reduced annealing temperature mitigates Al metal melting risk, enabling sharper edges and improved surface morphology. Deep recessing beyond the barrier layers makes the process less susceptible to variations in etching depth since ohmic contacts are formed on the recessed sidewall. The bottom Ti and Ta layer, Al thicknesses, and recessed sidewall angle, were optimized, successfully demonstrating on epitaxial structures with varied barrier designs.

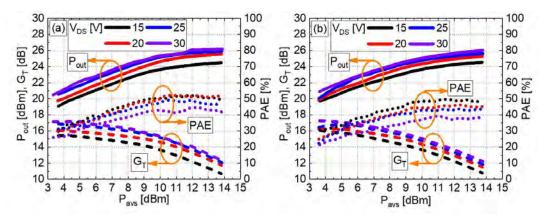

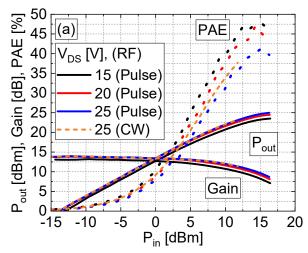

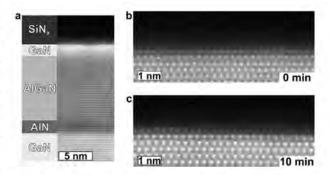

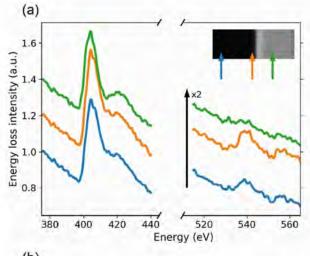

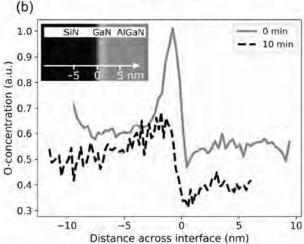

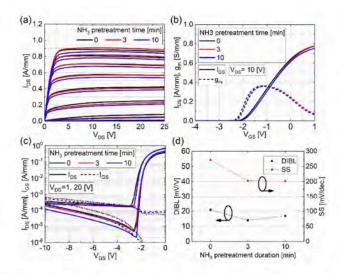

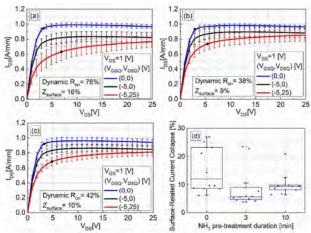

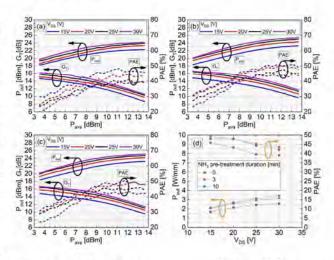

Passivation utilizing low pressure chemical vapor deposition (LPCVD) silicon nitride (SiN) has emerged as an effective method for mitigating surface-related trapping effects. However, surface traps could not be entirely eliminated with passivation, owing to the persistence of defects, dangling bonds and a native oxide layer at the interface between the passivation and epi-structure. Consequently, an in-situ NH<sub>3</sub> pretreatment method preceding LPCVD SiN deposition was investigated. The pretreated sample exhibited a 38% reduction in surface-related current collapse compared to the un-pretreated sample, culminating in a 30% augmentation in output power (3.4 vs. 2.6 W/mm) and an enhanced power-added efficiency (44% vs. 39%) at 3 GHz. Additionally, the pretreated samples demonstrated improved uniformity in device performance.

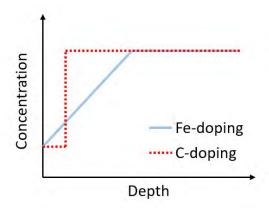

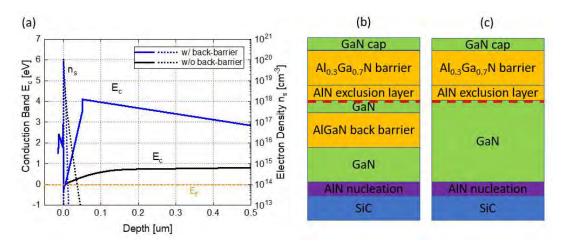

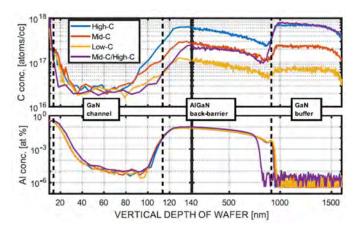

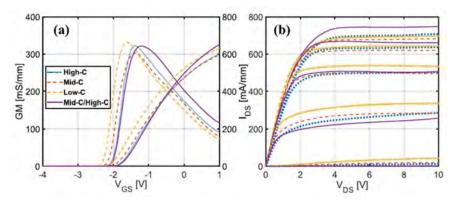

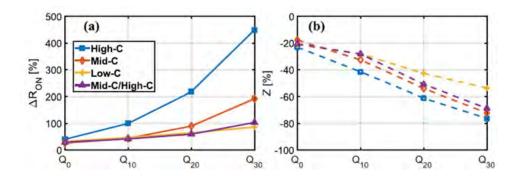

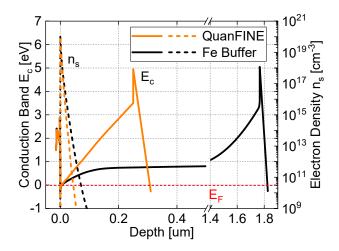

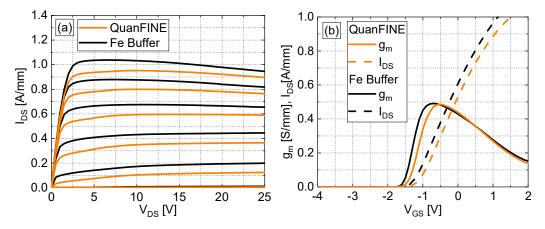

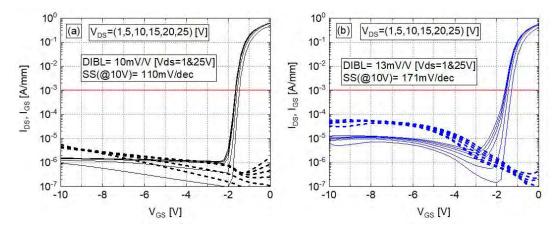

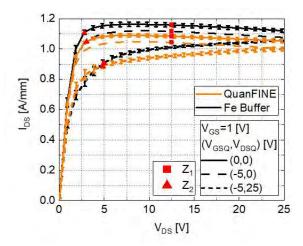

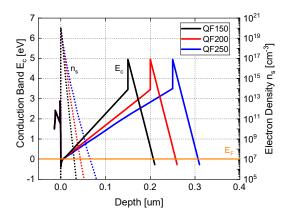

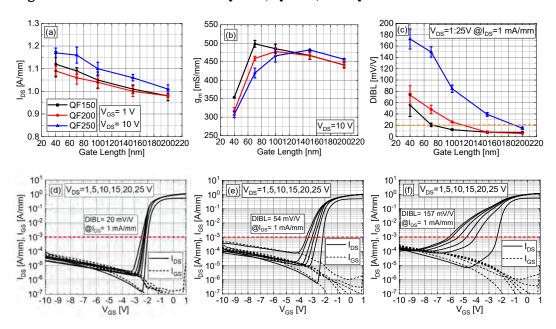

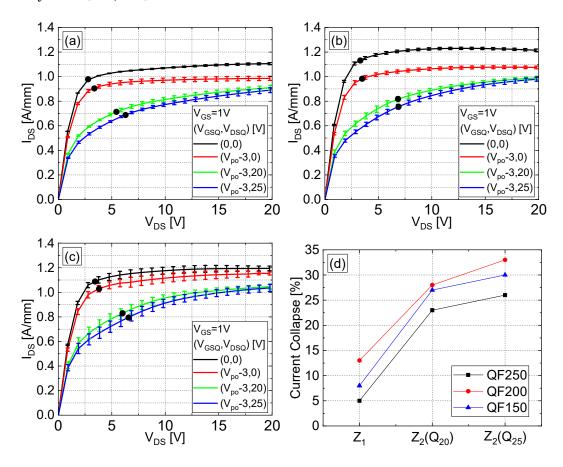

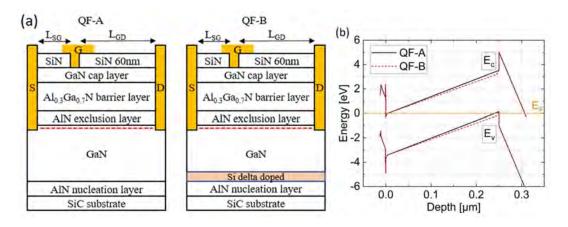

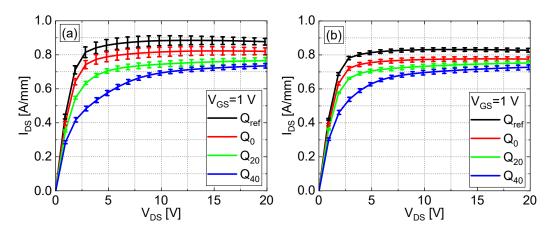

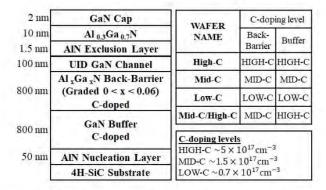

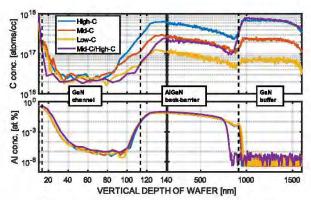

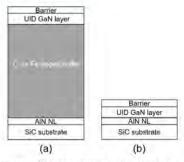

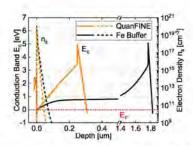

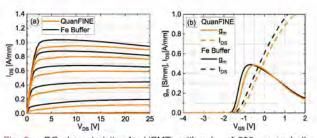

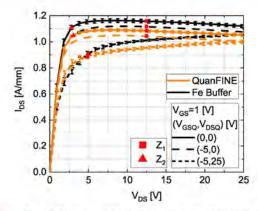

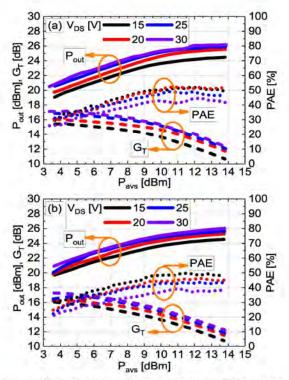

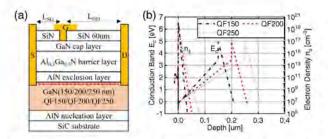

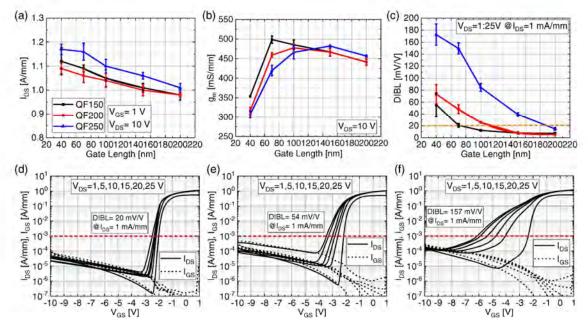

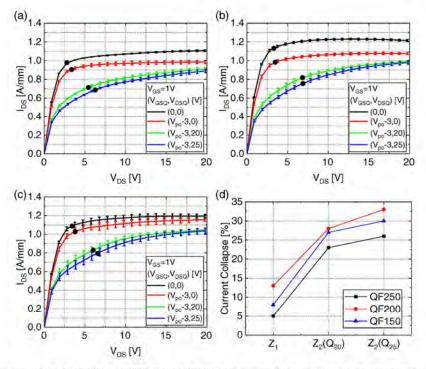

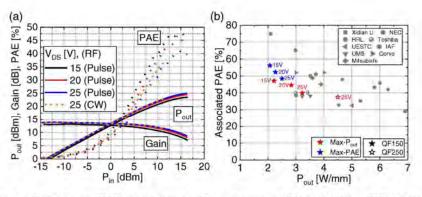

Traditionally, adequate buffer insulation and 2DEG confinement have been achieved through the intentional acceptor-like dopants (iron (Fe) and carbon (C)) or the AlGaN back-barrier in the GaN buffer. In this thesis, the impact of different carbon concentrations in AlGaN back-barrier and GaN buffer is studied. The results highlight that the back-barrier effectively screens the trapping effects underneath the backbarrier and the importance of optimization C-doping level in GaN channel, back-barrier and GaN buffer. However, solutions involving acceptor dopants, and a back-barrier have been reported to increase trapping effects and thermal resistivity, respectively. Therefore, a novel buffer-free epitaxial scheme, QuanFINE, was proposed. It removes thick Fe-/C-doped GaN buffer, enabling a GaN channel thickness of 250 nm to be directly grown on an AlN nucleation layer. Consequently, the AlN nucleation layer serves as a back-barrier. This approach results in a lower buffer-related current collapse (15% vs. 18%) compared to a conventional epi-structure with a thick Fe-doped GaN buffer. Furthermore, the reduction of GaN channel thickness from 250 nm to 150 nm is explored to facilitate the development of highly scaled devices. No degradation of 2DEG properties was observed in the epitaxial structure with the GaN channel thickness reduced to 150 nm. An exemplary drain-induced barrier lowering (DIBL) of 20 mV/V was measured on a device with a L<sub>g</sub> of 70 nm. While the sought-after 2DEG confinement and buffer insulation can be achieved, QuanFINE is not devoid of traps. This thesis also investigates an epitaxial structure with a band structure engineering at the interface of GaN channel and AlN nucleation layer using Si delta doping, which exhibited a lower buffer-related current collapse (19.8% vs. 26.8%), a more rapid current recovery speed, and a mitigation of long time constant as compared to the standard QuanFINE structure.

Keywords: GaN HEMT, Ohmic contact, Pretreatment, Passivation, QuanFINE.

# List of Publications

# Appended publications

This thesis is based on the following publications:

- [A] <u>D.Y. Chen</u>, A.R. Persson, V. Darakchieva, P.O.Å. Persson, J.T. Chen, and N. Rorsman, "Structural investigation of ultra-low resistance deeply recessed sidewall ohmic contacts for AlGaN/GaN HEMTs based on Ti/Al/Timetallization", Semiconductor Science and Technology, Vol. 38, Issue 10, Sep. 2023.

- [B] Y.K. Lin, J. Bergsten, H. Leong, A. Malmros, J.T. Chen, <u>D.Y. Chen</u>, O. Kordina, H. Zirath, E.Y. Chang, and N. Rorsman, "A versatile low low-resistance ohmic contact process with ohmic recess and low-temperature annealing for GaN HEMTs", Semiconductor Science and Technology, Vol. 33, Num. 9, Aug. 2018.

- [C] <u>D.Y. Chen</u>, A.R. Persson, K.H. Wen, D. Sommer, J. Grünenpütt, H. Blanck, M. Thorsell, O. Kordina, V. Darakchieva, P.O.Å. Persson, J.T. Chen, and N. Rorsman, "Impact of *In Situ* NH<sub>3</sub> Pre-treatment of LPCVD SiN Passivation on GaN HEMT Performance", Semiconductor Science and Technology, Vol. 37, Issue 3, Jan. 2022.

- [D] R. Ferrand-Drake Del Castillo, <u>D.Y. Chen</u>, J.T. Chen, M. Thorsell, V. Darakchieva, and N. Rorsman "Characterization of Trapping Effects Related to Carbon Doping Level in AlGaN Back-Barriers for AlGaN/GaN HEMTs", IEEE Transactions on Electron Devices, Vol. 71, Issue 6, Page 3596 3602, May. 2024.

- [E] D.Y. Chen, A. Malmros, M. Thorsell, H. Hjelmgren, O. Kordina, J.T. Chen, and N. Rorsman, "Microwave Performance of 'Buffer-Free' GaN-on-SiC High Electron Mobility Transistors" IEEE Electron Device Letters, Vol. 41, Issue 6, Apr. 2020.

- [F] <u>D.Y. Chen</u>, K.H. Wen, M. Thorsell, M. Lorenzini, H. Hjelmgren, J.T. Chen, and N. Rorsman, "Impact of the Channel Thickness on Electron Confinement in MOCVD-Grown High Breakdown Buffer-Free AlGaN/GaN Heterostructures" Physica Status Solidi (a), Sep. 2022.

- [G] <u>D.Y. Chen</u>, K.H. Wen, M. Thorsell, J.T. Chen, and N. Rorsman, "Investigation and Mitigation of Trapping Mechanisms in Buffer-Free AlGaN/GaN HEMTs" Manuscript with major revision submitted again to IEEE Transactions on Electron Devices, Jan. 2025.

# Other publication

[h] J. Bremer, <u>D.Y. Chen</u>, A. Malko, M. Madel, N. Rorsman, S. E Gunnarsson, K. Andersson, T. MJ Nilsson, P. E Raad, P. L Komarov, T. L Sandy, and M. Thorsell, "Electric-Based Thermal Characterization of GaN Technologies Affected by Trapping Effects", IEEE Transactions on Electron Devices, Vol. 67, Issue 5, Page 1952-1958, Apr. 2020.

# Patent

[i] <u>D.Y. Chen</u>, N. Rorsman, and J.T. Chen, "SEMICONDUCTOR DEVICE STRUCTURE WITH RECESSED OHMIC CONTACTS AND METHOD FOR PRODUCING THE SAME", [US20240363746A1, EP4123721A1, TW202315117A, JP2024526363A, KR20240056492A, CN117652032A, WO2023001762A1]

## Conference

- [j] <u>D.Y. Chen</u>, J. Bergsten, A. Malmros, M. Thorsell, H. Hjelmgren, J.T. Chen, O. Kordina, and N. Rorsman, "QuanFINE High RF Performance AlGaN/AlN/GaN HEMTs with a Thin Buffer Layer", Oral presentation, 13th International Conference on Nitride Semiconductors (ICNS-13), July 2019.

- [k] D.Y. Chen, K.H. Wen, M. Thorsell, O. Kordina, J.T. Chen, and N. Rorsman, "Thin Al<sub>0.5</sub>Ga<sub>0.5</sub>N/GaN HEMTs on QuanFINE® Structure", Oral presentation, 2021 International Conference on Compound Semiconductor Manufacturing Technology (CS-MANTECH 2021), May 2021.

- D.Y. Chen, K.H. Wen, M. Thorsell, M. Lorenzini, H. Hjelmgren, J.T. Chen, and N. Rorsman, "Improve 2DEG Confinement in 70 nm AlGaN/GaN HEMTs by Reducing the GaN Channel Thickness in Buffer-Free Heterostructures", Oral presentation, International Workshop on Nitride Semiconductors (IWN 2022), Oct 2022.

# Thesis

[m] <u>D.Y. Chen</u> "Optimization of Ohmic Contacts and Surface Passivation for 'Buffer-Free' GaN HEMT Technologies" Tekn. Lic. Thesis, Department of Microtechnology and Nanoscience - MC2, Chalmers University of Technology, Gothenburg, Dec 2020.

As part of the author's doctoral studies, some of the work presented in this thesis has previously been published in [m]. Figures, tables, and text from [m] may therefore be fully or partially reproduced in this thesis.

# List of Contents

## Abstract

| T :  | _C | 1  | -1: - | ۔ ئد۔ |      |

|------|----|----|-------|-------|------|

| List | OΤ | pu | шс    | ашс   | פדדי |

| 1. Introduction                                                           | 7  |

|---------------------------------------------------------------------------|----|

| 2. GaN HEMTs technology                                                   | 11 |

| 3. Ohmic contacts for GaN HEMTs                                           | 25 |

| 3.1. Introduction of ohmic contacts                                       | 25 |

| 3.2. Ohmic process and design                                             | 27 |

| 3.3. Deeply recessed Ti based ohmic contacts                              | 31 |

| 4. Passivation and surface pretreatment for GaN HEMTs                     | 38 |

| 4.1. Introduction of passivation layer                                    | 38 |

| 4.2. Pretreatment prior to deposition of passivation layer                | 43 |

| 4.3. In-situ NH <sub>3</sub> pretreatment for LPCVD SiN passivation layer | 45 |

| 5. QuanFINE – a 'buffer-free' GaN HEMT heterostructure                    | 49 |

| 5.1. Conventional GaN HEMT heterostructure                                | 49 |

| 5.2. QuanFINE - a 'buffer-free' concept                                   | 55 |

| 5.3. Benchmark QuanFINE to conventional Fe-doped heterostructure          | 56 |

| 5.4. Impact of GaN channel thickness in QuanFINE                          | 59 |

| 5.5. Investigation and mitigation of trapping mechanisms in QuanFINE      | 64 |

| 6. Conclusions and future work                                            | 70 |

| 7. Summary of appended papers                                             | 73 |

| Acknowledgment                                                            |    |

References

Appended paper

# Chapter 1

# Introduction

GaN HEMTs have showcased exemplary performance in high-frequency applications, especially those operated under substantial power density, with contributions related to the large bandgap. In comparison to conventional semiconductors utilized for high-frequency applications - such as Si (1.1 eV), SiGe (1.12 eV), InP (1.34 eV), and GaAs (1.42 eV) - GaN boasts a notably larger bandgap of 3.4 eV. This substantial bandgap enables GaN to function at elevated voltages while maintaining robustness under high ambient temperature and radiation environments. This is partly due to the mitigation of carrier excitation to the conduction band (E<sub>c</sub>) induced by thermal and radiation effects [1]. Initially, GaN HEMTs were fabricated on AlGaN/GaN heterostructures, where a two-dimensional electron gas (2DEG) forms within the quantum well due to the epitaxial growth of a larger-bandgap III-nitride material on GaN, while the pronounced 2DEG concentration is further enhanced by polarization and piezoelectric fields. More recently, InAl(Ga)N/GaN, AlScN/GaN, and AlN/GaN heterostructures emerge as alternative considerations owing to their higher polarization fields, thereby resulting in an enhanced 2DEG concentration [1]. Within the energy well, highconcentration electrons can travel with less scattering effects, leading to high electron mobility and saturation velocity. An augmented saturation velocity in GaN HEMTs can facilitate a higher cut-off frequency (f<sub>T</sub>) and maximum oscillation frequency (f<sub>max</sub>), thus bolstering high-frequency operating performance [1]. The combination of a higher 2DEG concentration with elevated mobility and saturation velocity results in a reduced 2DEG sheet resistance (R<sub>sh</sub>) and an increased saturation source-drain current (I<sub>DS</sub>), potentially improving high-power performance.

When combined with a high thermal conductivity SiC substrate, these advantages enable GaN HEMTs to operate at an escalated power density, maintaining high robustness. Compared to alternative transistors founded on Si,

SiGe, InP, and GaAs, utilized for high-frequency power amplifier (PA) applications up to 200 GHz, GaN HEMTs yield a higher output power (Pout) density [2]. These merits pave the way for GaN HEMTs to be used for compact PA designs, proving ideal for sensing technology, satellite, and wireless communication.

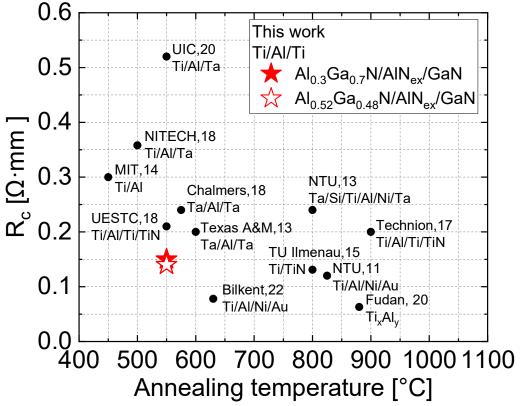

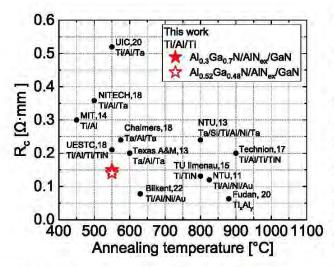

Despite the advantages of GaN HEMTs, several persisting issues limit their performance. The formation of low contact resistance (R<sub>c</sub>) ohmic contacts on GaN HEMTs always presents a notable first challenge while processing GaN HEMTs. Establishing ohmic contacts with minimized  $R_c$  is important as it reduces resistance at the transistor's source and drain terminals, thereby enhancing device performance. One approach to form ohmic contacts involves regrowing n-GaN contact using metal-organic chemical vapor deposition (MOCVD) or molecular-beam epitaxy (MBE). Employing heavily Si-doped regrown GaN can achieve a low Ro ( $<0.15 \Omega \cdot mm$ ) [3]. However, this methodology can be complex and is not typically compatible with industrial high-throughput requirements. An alternate approach encompasses alloyed Ti- and Ta-based ohmic contacts, which have been reported to have a  $R_c$  ranging from 0.06 to 0.40  $\Omega$ ·mm [4-8]. In this work [Paper A], the formation mechanism of deeply recessed Ti-based ohmic contacts, utilizing a low annealing temperature, was explored. A R<sub>c</sub> of 0.14 Ω·mm was achieved with Tibased ohmic contact, employing an annealing temperature of 550 °C on AlGaN barrier epi-structures with various Al contents, building upon previous publication [Paper B], using Ta-based deeply-recessed sidewall ohmic contacts with a R<sub>c</sub> of 0.24  $\Omega$ ·mm.

Another performance-limiting factor for GaN HEMTs is the DC-RF dispersion effects, which result from surface- and buffer-related trapping effects, as well as thermal dissipation capability [9, 10] [Paper h]. Surface trap states exist due to the surface defects, native oxides, and polarization-induced energy states. The accumulation of negative charges on the epi-structure's surface, acting as a virtual gate, occurs when the surface trap states, filled by electrons due to the electric field, are not instantaneously released, depleting 2DEG and resulting in knee-walkout and current collapse [9]. Although surface passivation with dielectric material is commonly employed to mitigate undesirable surface trap states, it does not fully eliminate surface traps. Various pre-treatments, including ex-/in-situ chemical- and plasma-based processes, have been studied. A non-plasma-based in-situ process is preferred to minimize contamination, re-oxidation, and plasma damage risks. Yet, no non-plasma-based in-situ pre-treatments have been reported for LPCVD SiN passivation [11]. Commonly used gases in LPCVD systems include Dichlorosilane (DCS), silane, ammonia (NH<sub>3</sub>), and nitrogen, with NH<sub>3</sub> being effective in removing native oxide and recovering the dangling bond on the GaN surface [12]. Thus, [Paper C] proposes an in-situ NH<sub>3</sub> surface pre-treatment process before LPCVD SiN passivation layer deposition to mitigate surface-related trapping effects. Samples subjected to NH<sub>3</sub> pre-treatment exhibited a reduced surface-related current collapse (9% compared to 16% for untreated samples) and, consequently, a higher maximum P<sub>out</sub> (3.4 W/mm vs. 2.6 W/mm) at 3 GHz as well as better on wafer uniformity.

In contrast to surface-related traps, which can be mitigated through passivation layers and surface pre-treatment, addressing buffer-related traps necessitates optimization in epi-structure design and epitaxial growth to diminish trap states and undesirable impurities. Commonly, Fe and C are employed as acceptor-like dopants to facilitate buffer insulation and 2DEG confinement [10, 13]. Nonetheless, these dopants lead to trapping effects, limiting large-signal performance. In [Paper E], a novel "buffer-free" epi-structure, trademarked QuanFINE by SweGaN AB, is proposed, removing the conventional Fe- or C-doped thick GaN buffer. This structure comprises merely a 250 nm thin GaN channel, directly grown on an AlN nucleation layer (a stark contrast to the ~2 µm thick GaN buffer in conventional epi-structures), enabling the AlN nucleation layer to function as a back-barrier, confining the 2DEG. Furthermore, buffer-related trapping effects in QuanFINE are reduced compared to conventional Fe-doped epi-structures (15% vs. 18%) due to the elimination of the Fe-doped buffer.

To realize the desired 2DEG confinement for highly scaled GaN HEMTs, particularly those with a gate length (L<sub>g</sub>) under 100 nm, an additional AlGaN backbarrier is commonly deployed in conventional thick buffer epi-structures. Nonetheless, this can inadvertently form an unwanted 2DEG channel at the interface of the back-barrier and GaN buffer, necessitating compensation through Fe- or C-dopants, and thereby introducing trapping effects. Therefore, [Paper D] investigates the impact of different carbon concentrations in AlGaN back-barrier and GaN buffer. The results highlight that the buffer-related trapping effects can be mitigated by the AlGaN back-barrier and the optimized carbon doping profile in AlGaN back-barrier and GaN buffer.

However, the creation of extra interfaces by the back-barrier could foreseeably impair thermal dissipation properties [14, 15]. An alternative strategy to enhance 2DEG confinement involves diminishing the GaN channel thickness atop the AlGaN back-barrier [16]. However, reducing GaN channel thickness without sacrificing 2DEG properties and structural quality in a buffer-free epi-structure presents a challenge [17]. Based on [paper E], a reduction of GaN channel thickness from 250 nm to 150 nm—achieved without compromising 2DEG and structural integrity—is demonstrated and further studied in [Paper F]. Moreover, this work investigates the tradeoff among 2DEG confinement, trapping effects, and large-signal performance.

Despite the elimination of the Fe- and C-doped thick buffer, QuanFINE is not entirely free from trapping effects [Paper E]. A noticeable increase in current collapse was characterized as the thickness of the GaN channel was reduced [Paper F]. Consequently, the dominant trap states are hypothesized to be situated at the bottom of GaN channel, or AlN nucleation layer, or within the semi-insulating SiC substrate or the interface between different epi-structure layers. Furthermore, a potential two-dimensional hole gas (2DHG) has been reported at the interface between GaN and the AlN nucleation layer [18] with the possibility of temporary traps the injected electron during device operation. [Paper G] explores trapping effects within QuanFINE with a band-structure engineering interface using Si delta doping between GaN channel and AlN nucleation layer and compares them to the standard QuanFINE. The QuanFINE with band structure engineered interface demonstrated a lower current collapse and a more rapid current recovery speed compared to the conventional QuanFINE structure. Additionally, the properties of the traps were analysed through temperature-dependent and filling time-dependent

drain current transient measurements.

The discussions and analyses within this thesis are structured as follows: Chapter 2 presents an introduction to GaN HEMTs, exploring its operation, fabrication process, and characterization methods. Chapter 3 delves into the fundamental aspects of ohmic contacts, including alloyed-based and regrowth ohmic contacts, and further discusses the formation mechanism of low-temperature, deeply recessed Ti- and Ta-based ohmic contacts [Paper A and Paper B]. Chapter 4 consolidates and compares different passivation materials and pre-treatments, placing particular emphasis on the proposed in-situ NH<sub>3</sub> pre-treatment for LPCVD SiN passivation [Paper C]. Chapter 5, which embodies the key of this thesis, introduces the buffer-free QuanFINE epi-structure [Paper E], benchmarks it against conventional materials, and examines different buffer designs aimed at enhancing 2DEG confinement and mitigating trapping effects [Paper D, F, and G]. Lastly, Chapter 6 encapsulates the conclusions drawn and delineates potential avenues for future research.

# Chapter 2

# GaN HEMTs technology

# 2.1 AlGaN/GaN heterostructure

Ever since the invention of the AlGaN/GaN heterostructure, recognized as a third-generation semiconductor, the development of GaN HEMTs has thrived over the past decades, thanks to the unique properties of GaN (Table 2.1) [2]. GaN exhibits a larger bandgap ( $E_g$ ) than that of Si, GaAs, and InP. A larger  $E_g$  leads to a higher critical breakdown field ( $E_{crit}$ ), resulting in a higher operation drain-source voltage ( $V_{DS}$ ) for the transistor. Although 4H-SiC also possesses a bandgap similar to that of GaN, it displays lower mobility and saturation velocity. Consequently, SiC is more suited for power switching devices rather than high-frequency applications.

**Table 2.1.** Summary of semiconductors properties [2].

|                                                 | Si      | 4H-SiC  | GaAs HEMT   | InP HEMT      | GaN HEMT  |

|-------------------------------------------------|---------|---------|-------------|---------------|-----------|

|                                                 | 51      | 411-510 | AlGaAs/GaAs | InAlAs/InGaAs | AlGaN/GaN |

| Bandgap [eV]                                    | 1.12    | 3.26    | 1.43        | 1.34          | 3.4       |

| Critical breakdown field [10 <sup>6</sup> V/cm] | 0.3-0.4 | 2.5-4   | 0.4-0.5     | 0.5 - 0.7     | 3.5-5     |

| Electron mobility @300 K [cm²/V·s]              | 1.5k    | 0.9k    | 5k-15k      | 10k-20k       | 2k        |

| Electron modifity @500 IX [cm / v 5]            | 1.0K    | 0.510   | (2DEG)      | (2DEG)        | (2DEG)    |

| Thermal conductivity [W/m·K]                    | 150-180 | 490     | 50          | 68            | 130       |

| Lattice mismatch to GaN [%]                     | -17.0   | +3.5    |             |               |           |

For THz applications, GaAs and InP offer higher electron mobility than GaN. Nevertheless, the output power of GaN can surpass that of GaAs and InP devices when the operation frequency is below 150 GHz, due to its higher breakdown voltage ( $V_{BR}$ ). Furthermore, the high thermal conductivity of GaN allows for enhanced heat dissipation and improved device robustness.

## 2.1.1 Substrate for GaN epitaxy

In the early stages of III-nitride development, GaN grew on sapphire and used in light-emitting diodes (LEDs) due to its cost-effectiveness and reliability. However, sapphire's poor thermal conductivity (0.23 W/K·cm) and significant lattice mismatch with GaN (-16%) make it less ideal for high-frequency applications [19]. Nonetheless, with the right process optimization and thermal management, GaN-on-sapphire can be suitable for high-power switching applications that operate at lower frequencies (< 10 MHz) [20].

The Si substrate presents an alternative for GaN epitaxy, primarily due to its cost-effectiveness and the capability to support larger wafer sizes. These attributes render GaN on Si suitable for high-volume, low-voltage power devices with ratings below 1200 V [21]. However, the pronounced lattice mismatch with GaN necessitates a thick strain-relief buffer to maintain the desired structural quality and inhibit crystal relaxation. Similar to sapphire, the challenges of inadequate heat dissipation and significant trapping effects make Si a less optimal choice for high-power microwave devices.

Alternative substrates for GaN epitaxy are also free-standing GaN and diamond. GaN-on-GaN offers an ideal lattice match, eliminating the need for an AlN nucleation layer [22]. However, the current limitations in GaN substrate quality consistency and smaller wafer size make it more expensive and less viable for commercial production. In contrast, while diamond has a significant lattice mismatch of 12% with GaN, GaN-on-diamond holds considerable promise for highend RF applications, such as satellite communication, thanks to its exceptional thermal conductivity (22.9 W/K·cm) [23].

Among the several substrate options for GaN epitaxy, the SiC substrate stands out with its high thermal conductivity and a relatively minor lattice mismatch (+3.5%). Furthermore, semi-insulating (SI)-SiC substrates can be realized either through a high-purity process using point defects or via vanadium doping, ensuring the desired resistivity. Also, SI-SiC made by high-purity process provides better thermal conductivity as compared to that by vanadium doping. These characteristics make the SiC substrate suitable for both high-power and high-frequency GaN HEMTs applications. For the research presented in this thesis, all GaN HEMTs heterostructures were grown on SI-SiC. To address the lattice mismatch between GaN and SiC, both an AlN nucleation layer and a thick strain-release GaN buffer are commonly employed in conventional epi-structures. Further details will be explored in Chapter 5.

#### 2.1.2 Formation of 2DEG

A GaN HEMTs heterostructure is realized by epitaxially growing a III-nitride barrier, which has a larger bandgap than GaN, on a GaN channel layer. In the conventional AlGaN/GaN heterostructure, an increased Al content results in a more pronounced lattice mismatch with GaN. This mismatch raises the potential for crystal structure relaxation, dislocation, and defects, all of which can adversely affect device performance and surface properties including morphology. Consequently, barriers with higher Al content necessitate a reduction in barrier

thickness. This approach effectively mitigates short channel effects as well as maintains high 2DEG concentration for highly scaled GaN HEMT.

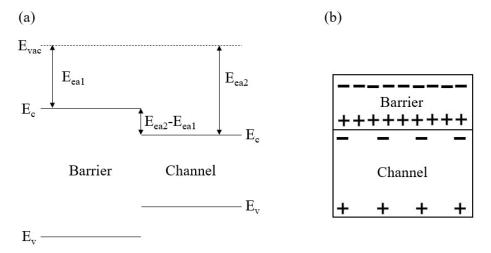

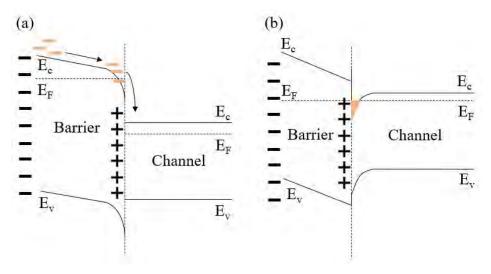

Electron affinity (E<sub>ea</sub>) and E<sub>g</sub> play crucial roles in the formation of an energy well and 2DEG. Electron affinity is defined as the energy required to detach an electron from the conduction band (E<sub>c</sub>) to the vacuum state (E<sub>vac</sub>). The barrier typically has a larger E<sub>g</sub> and a smaller E<sub>ea</sub> compared to the GaN channel. This difference leads to an energy offset at the interface, as illustrated in Fig. 2.1a. To equate the Fermi level (E<sub>F</sub>) of the two semiconductor materials, both the E<sub>c</sub> and valence band (E<sub>v</sub>) bend. This bending facilitates the migration of electrons from the barrier to the GaN channel side because of the channel's lower energy state, depicted in Fig. 2.2a. Consequently, an energy well containing 2DEG forms at the interface between the barrier and the GaN channel.

**Fig. 2.1.** Schematic of (a) band structure and (b) polarization charges in III-nitride heterostructure.

**Fig. 2.2.** Illustration of (a) electron migration due to band structure offset and polarization field, and (b) the formation of 2DEG in energy well.

In addition to the  $E_c$  offset between the barrier and the GaN channel, polarization fields within the III-nitride also play an important role in 2DEG formation. III-nitride materials possess a wurtzite crystal structure, inherently asymmetric in its lattice. This asymmetry gives rise to variations in electronegativity between distinct atoms. As a result, asymmetrical, dipole-like electron clouds emerge, known as the spontaneous polarization field  $(P_{sp})$ . Another type of polarization field in the III-nitride heterostructure is the piezoelectric polarization  $(P_{pz})$ , which arises due to the strain built within the barrier. The total polarization field  $(P_{tot})$  is then defined as the sum of  $P_{sp}$  and  $P_{pz}$  [24].

The crystal orientation of GaN can be either Ga-faced or N-faced. For this thesis, all epi-structures grown using MOCVD were Ga-faced. The direction of P<sub>sp</sub> in both AlGaN and GaN are from the Ga-face to the N-face, and is considered negative [24].  $P_{pz}$ , for tensile strained barriers, has been verified to be negative [25]. Since the lattice constant of AlGaN is smaller than that of GaN, AlGaN grown on GaN is a tensile-strained barrier exhibiting a negative Ppz. The Ptot of the AlGaN barrier on GaN induces positive polarization charges on the AlGaN side at the AlGaN/GaN interface, and negative charges on the AlGaN barrier surface. This gives rise to an internal electric field (as shown in Fig. 2.1b). This internal field alters the band structure, prompting electrons to move to the GaN that has a lower energy state. These electrons then accumulate at the AlGaN/GaN interface, culminating in the formation of a 2DEG in the energy well (Fig. 2.2). Generally, a higher Al content and increased thickness of the AlGaN barrier lead to a more pronounced polarization-induced 2DEG concentration [26]. However, an AlGaN barrier with a higher Al content displays a larger lattice mismatch to GaN, constraining the maximum usable thickness before a barrier relaxation occurs. Since P<sub>pz</sub> arises from strain, both the GaN cap layer and any added passivation layer on the barrier layer significantly influence the 2DEG formation and its properties [27].

Electron mobility (μ), electron density (n<sub>s</sub>), and sheet resistance (R<sub>sh</sub>) are standard metrics to gauge the performance of 2DEG. These characteristics can be measured using contactless Hall measurements (Leighton), eddy current measurements, and van der Pauw structure with Hall effects measurement. The effective μ encompasses various scattering effects, such as phonon scattering, interface scattering, carrier-carrier scattering, and impurities scattering [28-30]. Phonon scattering is triggered by lattice vibrations and is notably influenced by device operation and ambient temperature. The quality (particularly roughness) at the interface between the barrier and channel also imposes a limit on μ. High n<sub>s</sub> values increase the likelihood of electron collisions, resulting in carrier-carrier scattering. Sometimes, higher n<sub>s</sub> tends to extend into the barrier, which will lead to more pronounced alloy scattering. Impurity scattering originates from unintentional contaminants introduced during epi-structure growth. Thus, a GaN channel of high structural quality and minimal unintentional impurities is crucial to alleviate the scattering mechanisms. The sheet resistance can be derived from equation 2.1:

$$R_{sh} = \frac{1}{q \cdot n_s \cdot \mu} \tag{2.1}$$

where q represents the elementary charge (approximately 1.6·10<sup>-19</sup> C).

## 2.2 GaN HEMTs fabrication

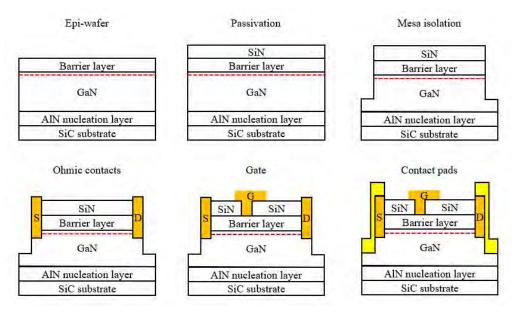

The processes for fabricating GaN HEMTs on an epi-structure encompass the following steps in this thesis: deposition of the passivation layer, device isolation, formation of ohmic contacts, gate definition, and the creation of contact pads. It should be noted that this thesis does not cover the air bridge process for multi-finger devices or backside processes, which include substrate thinning and via-hole creation.

The passivation layer can be fabricated using either a "passivation-first" or "post-gate passivation" process scheme. Compared to the post-gate passivation scheme, the passivation-first approach offers better protection to the epi-structure against potential damage and contamination during processing [31]. Additionally, the deposition temperature of the passivation layer constrains the methods available for the post-passivation scheme, as elevated temperatures might degrade the ohmic and gate contacts.

Device isolation in GaN HEMTs can be achieved through either ion implantation or mesa recessed isolation methods. Ion implantation achieves isolation by bombarding the epi-structure outside the device's active area with high-energy ions, such as H+, He+, F+, Mg+, Ar+, N+, or O+. This process introduces defects and damages the structure, leading to material insulation [32]. By contrast, mesa recessed isolation is implemented using a dry etching process, which removes the 2DEG, a portion of the GaN channel, and some of the buffer. While ion implantation offers the advantage of a smooth surface morphology, mesa isolation can encounter some troubles such as gate leakage currents at the mesa sidewall and potential issues with the robustness of gate structure formation.

Ohmic contacts for HEMTs can be fabricated using either alloyed-based metal contacts or regrowth n-GaN contacts as source and drain terminals. Alloy-based contacts require annealing at high temperatures. These characteristics dictate that the formation of ohmic contacts must precede the gate process or ion implantation isolation to avoid potential gate degradation and inadvertent recovery of intentionally damaged crystal structures during annealing. On the other hand, regrowth n-GaN contacts involve Si doping during the GaN regrowth process, achieved either through molecular beam epitaxy (MBE) [33] or Metal organic chemical vapor deposition (MOCVD) [34, 35]. Though this method provides better precision, reduced resistance, improved reliability, and thermal stability, its complexity including soft mask, hard mask, dry etching, extra cleaning, pretreatment, and n-GaN growth makes it less attractive for commercial production of cost-driven large gate length devices compared to alloyed-based contacts.

In high-frequency GaN HEMTs, an Schottky field plate gate is a common choice. The nickel/gold (Ni/Au) metal stack is frequently utilized as the Schottky gate. Nickel offers excellent adhesion and a substantial work function, which produces a high Schottky barrier height. Meanwhile, gold provides excellent conductivity, leading to reduced gate resistance. To further enhance device reliability, other high work function metals such as palladium (Pd), iridium (Ir), and platinum (Pt) are often interposed between the Ni and Au layers. Another critical consideration for device performance is the parasitic capacitance induced by the gate. An advanced

mushroom gate structure, in comparison to the field-plate gate, can effectively decrease this capacitance. When considering power switching applications, a normally-off device is preferred. This can be realized with a gate deposited on a partially removed barrier or on a p-GaN cap layer.

Fig. 2.3. Process steps of GaN HEMTs in this thesis.

In this thesis, a passivation-first process scheme was selected to fabricate GaN HEMTs, as depicted in Fig. 2.3. Initially, the epi-structure underwent standard cleaning processes (SC1 and SC2) and diluted NH3 dipping. This was followed by an in-situ NH<sub>3</sub> pre-treatment and SiN deposition in LPCVD, the details of which will be covered in Chapter 4. Using mask-free laser writer photolithography, the device's active area was delineated, and then mesa recessed isolation was achieved through inductively coupled plasma-reactive ion etching (ICP-RIE). Two different plasma chemistries were used in this step: a fluorine-based one for the SiN and a chlorinebased one to etch the epi-structure, targeting a mesa depth of approximately 120 nm below the 2DEG. For the source and drain terminals, a Ta-based deeply recessed sidewall ohmic contact was used that required low annealing temperature. After defining the terminals using photolithography, the SiN and the epi-structure's barrier layer were opened up with ICP-RIE. Following a wet chemical oxide etching procedure using diluted buffer oxide etchant (BOE) and HCl, metal stacks of Ta/Al/Ta were deposited using an electron beam thermal evaporator. The annealing process was executed in a rapid thermal processing (RTP) system under N<sub>2</sub> ambient conditions. Further details on this topic will be explored in Chapter 3. The gate's design involved a two-step e-beam lithography process, first determining the gate length and then the gate's field-plate. A fluorine-based plasma etched the SiN, effectively defining the gate length. Subsequently, another round of e-beam lithography enabled the metallization of the Ni/Pt/Au Schottky gate metal stacks, resulting in a field-plate gate structure (Fig 2.3). The fabrication was finalized with an in-situ Ar+ plasma cleaning to remove native surface oxide followed by the sputtering deposition of Ti/Au contact pads for device characterization.

# 2.3 GaN HEMTs characterizations

#### 2.3.1 DC characterization

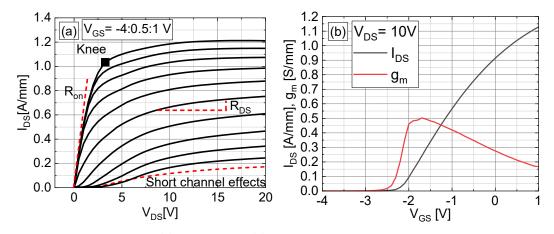

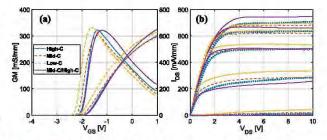

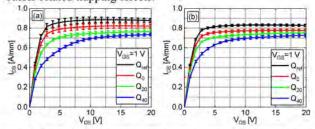

The DC-IV characteristics are the most basic method for evaluating the electrical performance of a transistor. As depicted in Fig. 2.4a, these characteristics provide insights into drain-source current ( $I_{DS}$ ), on resistance ( $R_{on}$ ), and drain-source resistance ( $R_{DS}$ ). The  $I_{DS}$  is recorded over a range of gate-source voltages ( $V_{GS}$ ) and drain-source voltages ( $V_{DS}$ ). The saturated  $I_{DS}$  primarily depends on the properties of the 2DEG. In scenarios where  $V_{GS}$  and  $V_{DS}$  are both high and in the saturation region, any reduction in  $I_{DS}$  can often be attributed to inefficient thermal dissipation. Conversely, in the saturation region with a low  $V_{GS}$  and high  $V_{DS}$ ,  $R_{DS}$  can be derived using equation 2.2:

$$R_{DS} = \frac{\delta V_{DS}}{\delta I_{DS}} \tag{2.2}$$

In the analysis of transistor characteristics, the drain-source resistance ( $R_{DS}$ ) is instrumental in examining the short channel effects. These effects can be a limiting factor for the range of the high frequency load-line swing. A significantly lower  $R_{DS}$  value is indicative of pronounced short channel effects. Meanwhile, in the linear operational region of the transistor, the on resistance ( $R_{On}$ ) provides valuable insights. Specifically, it helps identify the position of the knee voltage ( $V_{DS-knee}$ ) and the knee current ( $I_{DS-knee}$ ), both of which are crucial parameters for the load-line swing in microwave power amplifier (PA) applications. The transconductance ( $g_m$ ), a measure of the capability of the transistor to control the current flow between the drain and source for given change in gate-source voltage, is given by equation 2.3. The higher the transconductance, the more effective the transistor is at modulating the current flow, making it a critical parameter in microwave HEMT evaluations.

$$g_m = \frac{\delta I_{DS}}{\delta V_{GS}} \tag{2.3}$$

A higher  $g_m$  translates to a potentially higher cut-off frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{max}$ ), which can be calculated as:

$$f_T = \frac{g_m}{2\pi (c_{gs} + c_{gd})} \tag{2.4}$$

$$f_{max} = \frac{f_T}{2\sqrt{\frac{R_{in} + R_S + R_g}{R_{dS}}} + 2\pi f_T R_g C_{gd}}}$$

(2.5)

where  $C_{\rm gs}$  and  $C_{\rm gd}$  are intrinsic gate-source and gate-drain capacitance, respectively.  $R_{\rm s}$  and  $R_{\rm g}$  are extrinsic source and gate resistance, respectively.  $R_{\rm in}$  and  $R_{\rm ds}$  are intrinsic input and drain-source resistance, respectively.  $f_{\rm T}$  represents the frequency at which the current gain of the transistor drops to unity, and is a commonly used figure of merit to characterize the potential speed of a transistor. Meanwhile,  $f_{\rm max}$  gives the frequency at which the power gain drops to unity, indicating the upper limit where the transistor can effectively operate as an amplifier. Both parameters are crucial for high-frequency applications, such as RF amplifiers and oscillators.

In addition to the aforementioned characteristics, the off-state breakdown voltage  $(V_{BR})$  is another pivotal parameter when assessing GaN HEMTs. The  $V_{BR}$  refers to

the  $V_{DS}$  at which a sudden rise in the  $I_{DS}$  occurs when the device is in its off state, i.e., when the  $V_{GS}$  pinches off the channel. During this characterization, the device remains in the pinch-off state, and  $V_{DS}$  gradually increases until the  $I_{DS}$  meets or surpasses a compliance level, typically set at 1 mA/mm for microwave transistor. A higher  $V_{BR}$  suggests that the device can handle larger voltages without undergoing catastrophic failure, indicating its robustness and reliability. The  $V_{BR}$  plays a critical role in defining the maximum load-line swing for a microwave transistor, representing the boundary at which the device transitions from its normal operational state to a breakdown regime. The ability to achieve a high  $V_{BR}$  directly correlates to the device's capacity to operate at higher power density levels and maintain its integrity. In power applications, transistors often face high-voltage scenarios, and a strong  $V_{BR}$  ensures that the device can handle these stresses without undergoing catastrophic failure. Hence,  $V_{BR}$  is a good indicator of the device's robustness and reliability in demanding conditions typical of power electronics.

**Fig. 2.4.** Illustration of (a) DC-IV and (b)  $g_m$  characteristics.

#### Short channel effect

Decreasing the gate length ( $L_g$ ) and increasing  $V_{DS}$  can result in the short channel effect. This effect occurs when electrons, propelled by the potent electric field produced by  $V_{DS}$ , traverse beneath the depletion region created by the reverse  $V_{GS}$ . As the  $L_g$  becomes shorter, the capability to deplete the channel diminishes. This situation limits the range of load-line movement, thereby reducing both the  $P_{out}$  and efficiency of HEMTs when used as power amplifiers (PA). Although reducing the barrier thickness can mitigate the short channel effect, it can also introduce tunneling leakage between the gate and channel as a downside. Hence, better 2DEG confinement requires the development of enhanced buffer designs, which will be discussed in the CH5.

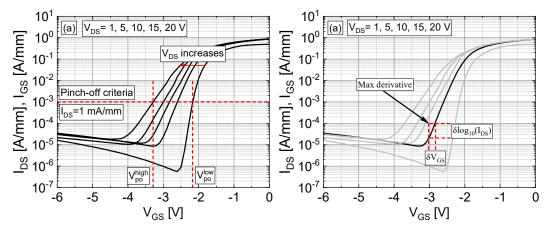

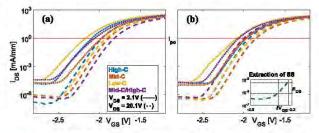

During DC-IV measurements, the short channel effects can often be found in regions with high  $V_{DS}$  and low  $I_{DS}$  (as depicted in Fig. 2.4a). However, quantifying these effects directly using only the DC-IV characteristics can be challenging. Instead, the transfer characteristic offers a more insightful approach to assessing these short channel effects (illustrated in Fig. 2.5). In this method  $I_{DS}$  is measured against  $V_{GS}$ , with the  $I_{DS}$  values presented on a logarithmic scale on the Y-axis. As

$V_{DS}$  increases, a more negative  $V_{GS}$  is required to achieve device pinch-off. The phenomenon of drain induced barrier lowering (DIBL) can be quantified using equation 2.6:

$$DIBL = \begin{vmatrix} v_{po}^{high} - v_{po}^{low} \\ v_{DS}^{high} - v_{DS}^{low} \end{vmatrix}$$

(2.6)

which uses the pinch-off voltage  $(V_{po})$  at  $V_{DS}^{low}$  and  $V_{DS}^{high}$  with the pinch-off criteria, typically  $I_{DS}$ = 1 mA/mm. The DIBL effect refers to the reduction in the pinch-off voltage  $(V_{po})$  of a transistor due to an increase in the  $V_{DS}$ . As devices scale down (smaller  $L_g$ ), short channel effects become more pronounced, impacting the device's performance. A larger DIBL value indicates a more pronounced short channel effect, which might pose constraints on the load-line swing in PA applications.

Fig. 2.5. Illustration of (a) DIBL and (b) SS extraction.

Another metric for assessing short channel effects is the subthreshold swing (SS), calculated using equation 2.7:

$$SS = \frac{\delta V_{GS}}{\delta \log_{10} I_{DS}} \tag{2.7}$$

SS quantifies the change in V<sub>GS</sub> relative to the logarithmic change in I<sub>DS</sub> below the V<sub>po</sub>. This value is determined at the point of maximum derivative within the transfer characteristics, expressed in units of mV/decade. A lower SS value signifies enhanced pinch-off capabilities for the device, whereas a higher value suggests the opposite.

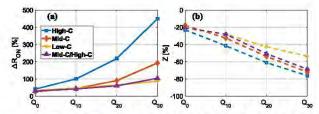

# 2.3.2 Trapping effects characterization

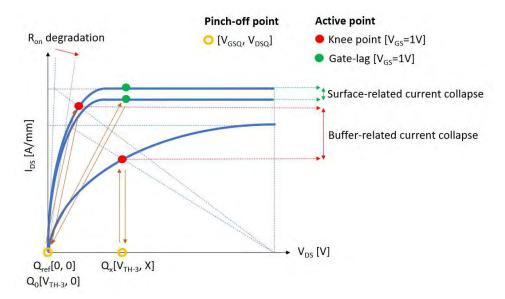

Trapping effects lead to phenomena such as current collapse, knee walk-out, and dynamic  $R_{on}$  degradation, all of which limit the high-frequency performance of HEMTs as illustrated in Fig 2.6 [36]. These effects can be characterized using a pulsed-IV system (AMCAD AM3200), which provides gate and drain voltage pulses at a quiescent point (pinch-off condition,  $V_{GS} < V_{po}$ ) and an active point (on-condition,  $V_{GS} > V_{po}$ ), while measuring the  $I_{DS}$ . Under the pinch-off condition for the quiescent point, the traps are filled due to the electric field induced by the quiescent bias points ( $V_{GSQ}$ ,  $V_{DSQ}$ ). This condition also facilitates nearly thermal-free

characterization. When the device is switched on at an active point, the pulse duration is sufficiently short to prevent heat generation. The typical duty cycle (equation 2.8) between the quiescent point and active point is kept below 1% to ensure the device is adequately cooled down.

$$duty\ cycle\ [\%] = \frac{pulse\ width\ at\ active\ point}{pulse\ width\ at\ quiescent\ point} \times 100 \tag{2.8}$$

**Fig. 2.6.** Illustration of the characteristics of trapping effects of GaN HEMTs in pulsed IV measurements.

To assess the traps mainly related to the surface, two specific quiescent points are used on HEMTs:  $(V_{GSQ}, V_{DSQ})$  of (0, 0), known as  $Q_{ref}$ , and  $(V_{TH}-3, 0)$ , referred to as  $Q_0$ . The  $V_{DSQ}$  is maintained at 0 V to avoid activating the buffer-related traps. The current collapse associated with surface-related phenomena, denoted as  $Z_1$  (represented by green dots in Fig 2.6) and also termed gate-lag, is defined as follows:

$$Z_1 [\%] = \left| \frac{I_{DS}(Q_0) - I_{DS}(Q_{ref})}{I_{DS}(Q_{ref})} \right| \cdot 100 \tag{2.9}$$

When a drain voltage is applied under pinch-off conditions with quiescent biases, specifically ( $V_{GSQ}$ ,  $V_{DSQ}$ ) of ( $V_{TH}$ -3, X), termed as  $Q_X$ , the trap states within the buffer become occupied. This leads to the buffer-related current collapse, denoted as  $Z_2$ . Also referred to as drain-lag, it is defined as:

$$Z_2 \left[\%\right] = \left| \frac{I_{DS-knee}(Q_{\rm X}) - I_{DS-knee}(Q_{ref})}{I_{DS-knee}(Q_{ref})} \right| \cdot 100 \tag{2.10}$$

where I<sub>DS-knee</sub> is the current at knee point (red dots in Fig 2.6). Moreover, buffer-related trapping effects also lead to knee walk-out and degradation of dynamic R<sub>on</sub>, which are commonly defined as:

$$Knee - walkout [V] = V_{DS,knee}(Q_X) - V_{DS,knee}(Q_{ref})$$

(2.11)

$$dynamic R_{on} \text{ degradation } [\%] = \left| \frac{R_{on}(Q_{X}) - R_{on}(Q_{ref})}{R_{on}(Q_{ref})} \right| \cdot 100$$

(2.12)

where knee points (VDS-knee) are defined as red dots in Fig. 2.6.

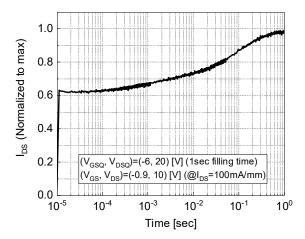

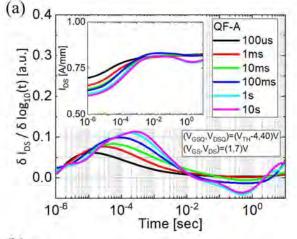

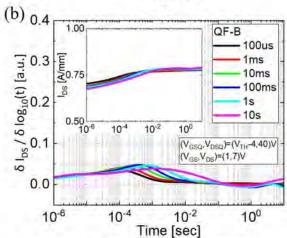

#### 2.3.3 Drain current transient measurement

A technique to pinpoint the time constant and the energy state of traps has been developed as drain current transient (DCT) measurements, which use varying filling time durations and ambient temperatures [37]. Conducted using the AMCAD AM3200 in a temperature-controlled chamber, this method stresses the device under pinch-off conditions with a high V<sub>DSQ</sub> for varying time spans. Given the pinch-off state of the device, thermal effects are negligible. Following the stress period, the device is transitioned to an active bias point (corresponding to PA operation biases, such as the knee point, the class-AB operation point, or linear region). Throughout this phase, the I<sub>DS</sub> is tracked over a time span that is pertinent to modulated PA operation frequency. Typically, a lower stress bias is indicative of surface region traps, while a higher stress bias includes traps at both surface and buffer regions. As the stress is alleviated, electrons are de-trapped, causing a rise in the I<sub>DS</sub> (as depicted in Fig. 2.7).

Fig. 2.7. Illustration of DCT measurement.

From the measured IDS, the time constant of traps can be obtained by the following stretch model [37]:

$$I_{DS}(t) = I_{DS,final} - \sum_{i=1}^{N} A_i \cdot e^{-\left(\frac{t}{\tau_i}\right)^{\beta_i}}$$

(2.13)

where  $I_{DS}(t)$  represents the  $I_{DS}$  observed after stress release, and  $I_{DS}$ , final denotes the final monitored  $I_{DS}$  following a set time period. The amplitude of the trapping effects is symbolized by  $A_i$ , while  $\tau_i$  is the time constant associated with the traps.  $\beta_i$  is the nonexponential stretching factor, which falls between 0 and 1, corresponding to the N identified processes in which electrons are either trapped (when  $A_i$  is positive) or released (when  $A_i$  is negative).

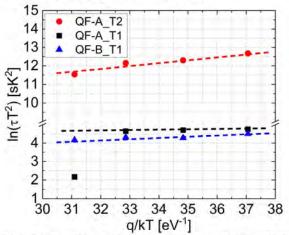

With the obtained time constant  $(\tau_i)$  and applied different ambient temperature correction [38], the activation energy  $(E_a)$  and the capture cross section  $\sigma_n$  can be extracted by the Arrhenius' equation [38]:

$$\ln(\tau_i T^2) = \ln\left(\frac{h^3}{2(2\pi)^{\frac{3}{2}}\sqrt{3}m_e k_B \sigma_p}\right) + \frac{E_a}{k_B T}$$

(2.14)

where T is temperature, h is the Planck's constant,  $m_e$  is the effective mass of carriers (0.22m<sub>0</sub>), and  $k_B$  is the Boltzmann constant. All data points measured at different T can be plot as Arrhenius plot with the X-axis of  $q/k_BT$  and Y-axis of  $\ln(\tau_i T^2)$ . The slope of the data points is the E<sub>a</sub>, while the  $\sigma_n$  can be extrapolated from the interception on Y-axis. The extracted E<sub>a</sub> and  $\sigma_n$  can be compared to literatures to analyze the possible location and the formation mechanism of the traps [37].

### 2.3.4 Small-signal characterization

Small signal measurements on HEMTs are conducted using a high-frequency signal with power typically ranging from -10 to -20 dBm to ensure minimal non-linear behavior. These measurements aim to extract parameters such as  $f_T$  and  $f_{max}$ , and an equivalent small-signal circuit model by measuring the HEMTs' scattering parameters (s-parameters). The  $f_T$  is determined at the point where the current gain  $(h_{21})$  reaches 0 dB. The  $h_{21}$  value is derived from the s-parameters as expressed in equation 2.15:

$$h_{21} = \frac{-2S_{21}}{(1 - S_{11})(1 + S_{22}) + S_{12}S_{21}} \tag{2.15}$$

The definition of  $f_{max}$  requires the consideration of device stability factor (K) and  $\Delta$ , which are defined as:

$$K = \frac{1 + |S_{11}S_{22} - S_{12}S_{21}|^2 - |S_{11}|^2 - |S_{22}|^2}{2|S_{12}||S_{21}|} \tag{2.16}$$

$$\Delta = |S_{11}S_{22} - S_{12}S_{21}| \tag{2.17}$$

If K > 1 and  $\Delta < 1$ , the device is stable, and vice versa. If the device is stable over the measured frequency of s-parameters, the  $f_{max}$  can be extrapolated when maximum available gain (MAG) becomes 0 dB. The MAG is defined as:

$$MAG = \frac{|S_{21}|}{|S_{12}|} \left( K - \sqrt{K^2 - 1} \right) \tag{2.18}$$

If the device is unstable, the  $f_{max}$  can be extrapolated when unilateral power gain (U) or so-called Mason's gain becomes 0 dB. The U is defined as:

$$U = \frac{|S_{21}|^2}{(1-|S_{11}|)^2(1-|S_{22}|)^2} = \frac{\left|\frac{S_{21}}{S_{12}}-1\right|^2}{2K\left|\frac{S_{21}}{S_{12}}\right|-2Re\left(\frac{S_{21}}{S_{12}}\right)}$$

(2.19)

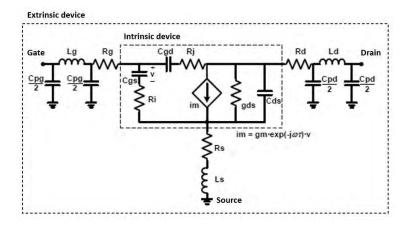

To extract the small signal equivalent circuit model (Fig. 2.8) through s-

parameters measurements, the bias independent extrinsic part of circuit is deembedded through two additional cold-FET measurements including pinch-off condition and forward condition as defined:

#### #1. Pinch-off condition:

$V_{GS} = (V_{po}-6) V$

$V_{DS}=0 V$

#### #2. Forward condition:

$V_{GS}$ = from 0 to 2 V ( $V_{GS}$  sweeps until  $I_{GS}$ = 1 mA/mm)

$V_{DS}=0 V$

Upon removing the extrinsic components, the bias-dependent intrinsic portion is ascertained through the direct extraction method outlined in [39]. Given that the intrinsic component is only applicable for a single bias point, this thesis employs the bias point that results in the  $f_{max}$  for comparing devices. The influences of varying intrinsic parameters will be elaborated upon in Chapters 4 and 5. By employing diverse bias points, small signal equivalent circuits serve as the preliminary method for simulating the large signal non-linear circuit model.

Fig. 2.8. Equivalent small signal circuit model for GaN HEMTs [39].

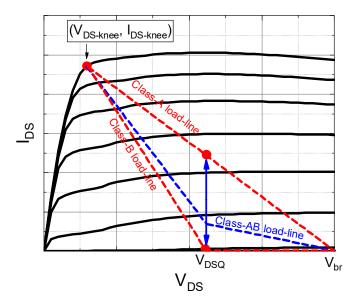

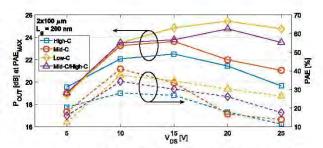

# 2.3.5 Large-signal characterization

The non-linear large signal measurements offer insights into the high-frequency capabilities of GaN HEMTs when functioning as a microwave power amplifier. In this thesis, parameters such as RF output power (Pout), gain, and power added efficiency (PAE) are characterized by load-pull measurements. The operational class of the device is determined by the IDSQ, which is regulated by VGS. When the HEMT operates in Class-A (conducting throughout the full cycle), it delivers the highest gain and Pout but has the lowest efficiency. On the other hand, Class-B operation, where the HEMT conducts for half a cycle, exhibits the opposite performance. This

thesis primarily focuses on Class-AB operation, which maintains a balance between the performances mentioned earlier. For an ideal Class-A operation (max 50% efficiency), the maximum  $P_{out}$  can be estimated as:

$$P_{out,class-A} = \frac{V_Q}{\sqrt{2}} \times \frac{I_Q}{\sqrt{2}} = \frac{1}{2} \times \frac{V_{max}}{2} \times \frac{I_{max}}{2} \cong \frac{(V_{BR} - V_{DS,knee}) \cdot (I_{DS,knee} - I_{po})}{8}$$

(2.20)

where  $V_{BR}$  is the breakdown voltage and  $I_{po}$  is the pinch-off current.

Under this condition, the operation voltage  $(V_{DSQ})$  is set as:

$$V_{DSQ} = \frac{V_{br} + V_{DS,knee}}{2} \tag{2.21}$$

So, the RF signal is able to swing the entire load line (Fig. 2.9). The PAE is defined as:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{2.22}$$

where  $P_{in}$  is the RF power added to the input of HEMT, while the  $P_{DC}$  is the DC power consumption defined as:

$$P_{DC} = I_{DSO} \cdot V_{DSO} \tag{2.23}$$

Also, the drain efficiency  $(\eta_{eff})$  is defined as:

$$\eta_{eff} = \frac{P_{out}}{P_{DC}} \tag{2.24}$$

**Fig. 2.9.** Illustration of large signal operations in HEMTs under different operation classes.

# Chapter 3

# Ohmic contacts for GaN HEMTs

## 3.1 Introduction of ohmic contacts

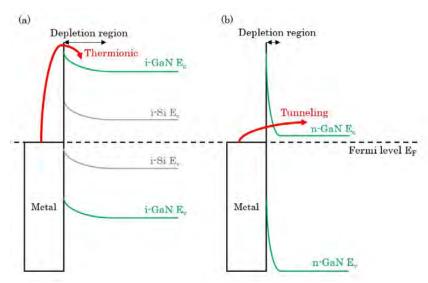

Good ohmic contacts, characterized by a low contact resistance ( $R_c$ ), are crucial for transistors that operate at high frequencies with high power density. A reduced  $R_c$  in ohmic contacts enhances the device's output power, efficiency, and reduces noise and heat generation. However, forming ohmic contacts on wide bandgap III-nitride semiconductors is challenging due to the substantial Schottky barrier height ( $\Phi_B$ ) present at the metal-semiconductor interface [40]. In contrast to intrinsic Si (i-Si), which has a smaller bandgap energy of 1.1 eV and a minor energy offset between the conduction band and the Fermi level, intrinsic GaN (i-GaN) possesses a large bandgap of 3.4 eV. This results in a significantly higher  $\Phi_B$  and a reduced thermionic electron transport probability. Additionally, the broader width of the depletion region ( $W_d$ ) caused by band bending beneath the metal-GaN junction further diminishes the electron tunneling probability (see Fig. 3.1).

Lowering the Schottky barrier height is one method to achieve low  $R_c$  ohmic contacts. This can be accomplished by choosing metals with a smaller work function  $(\Phi_M)$ , such as Ti (4.33 eV) and Ta (approximately 4.0-4.8 eV) [40, 41]. Another alternative is to adjust the Fermi level in GaN through intentional Si doping methods. These methods include regrown contacts [3], Si ion-implantation [6], and epitaxially grown Si-doped GaN [42]. This leads to n-GaN having a reduced depletion region width (shorter tunneling distance), which is inversely proportional to the n-type doping concentration (N<sub>d</sub>) in the semiconductor:

$$W_d \propto \frac{1}{\sqrt{N_d}} \tag{3.1}$$

Nitrogen vacancies, which serve as n-type doping agents [7, 43], can also form during the annealing process of metal ohmic contacts. Metals used in ohmic contacts, such as Ti and Ta, extract nitrogen from GaN to produce TiN and TaN, thereby generating nitrogen vacancies. The work functions of Ti-N and Ta-N have been reported to be 3.74 eV and 4.75 eV, respectively, which contribute to a decreased  $\Phi_B$  [44, 45]. However, an excessive amount of Ti in the bottom layer can result in the creation of voids beneath the TiN [43]. In the formation of ohmic contacts on AlGaN/GaN heterostructures, the Al layer plays multiple roles when combined with Ti and Ta. Al is frequently used in ohmic metal stacks, where it aids in a smooth transition of the work function and further promotes the extraction of nitrogen from GaN in the form of the Al-N phase. Yet, when Al is present in the metal stacks, it alloys with the Ti layer, causing Ti to lose its reactivity with GaN [43]. Conversely, the presence of Al in the AlGaN barrier hinders the extraction of N, given that the Al-N bond is stronger than the Ti-N bond. This protects the 2DEG from degradation during high-temperature processing. As a result, the thickness ratio between Ti or Ta and Al needs optimization. A limitation of using Al is that annealing temperatures exceeding its melting point (660 °C) often lead to inferior surface morphology and edge precision, posing challenges to the downscaling of the source-drain distance in HEMTs.

**Fig. 3.1.** Schottky barriers and band structures of (a) i-GaN and i-Si with thermionic transport dominated, and (b) n-GaN with Tunneling transport dominated.

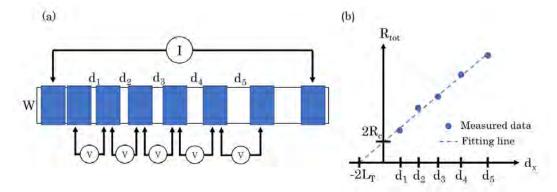

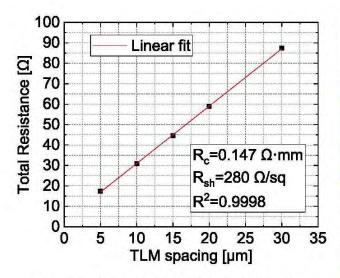

The transmission line measurement (TLM) is a widely used method for characterizing the electrical properties of ohmic contacts. Through this technique, parameters such as  $R_c$ ,  $R_{sh}$ , specific contact resistance, and transfer length can be accurately extracted [46]. A TLM characterization structure, illustrated in Fig 3.2a, comprises multiple ohmic contacts spaced at increasing distances (for instance, ranging from 5 to 30  $\mu$ m, labelled as  $d_1$  to  $d_5$ ). The method employs a four-probe measurement, where two probes conduct the current and the remaining two measure the voltage. This configuration directly mitigates the influence of resistance of the probes.

Fig. 3.2. (a) Schematic of TLM structure and (b) extrapolate method of R<sub>c</sub>.

The total resistance ( $R_{tot}$ ) for each spacing is determined from the voltage and current measurements.  $R_{tot}$  encompasses the  $R_c$ , the resistance of the ohmic metal electrodes ( $R_m$ ), and the semiconductor ( $R_{semi}$ ):

$$R_{tot} = 2R_m + 2R_c + R_{semi} \tag{3.3}$$

Given that  $R_m$  is typically much smaller than  $R_c$ , it can be disregarded.  $R_{\text{semi}}$  is derived from the  $R_{\text{sh}}$  of the 2DEG:

$$R_{semi} = \frac{R_{sh}}{W} \times d_x \tag{3.4}$$

By assessing R<sub>tot</sub> across all spacings in the TLM structure, both R<sub>c</sub> and R<sub>sh</sub> can be extracted, as depicted in Fig. 3.2b and as per equation 3.3.

While the current flow through the semiconductor is uniform, it diminishes exponentially towards the contact edges. At the furthest edge, the current flow ceases, resulting in the current crowding effect. The transfer length (L<sub>T</sub>), obtainable via TLM measurements as shown in Fig 3.2b, represents the average distance that carriers traverse from the semiconductor to the contact. An effective area can be deduced as L<sub>T</sub> multiplied by W. Subsequently, the contact resistivity ( $\rho_c$ ) is computed as:

$$\rho_c = R_c \times L_T W \tag{3.5}$$

# 3.2 Ohmic process and design

#### 3.2.1 Planar contacts

The fabrication of planar contacts involves lithography, metal deposition, and annealing. During the lithography phase, the region designated for the ohmic is exposed, and after metal deposition, a lift-off process is conducted. Various pretreatments are employed within the exposed area, including both wet chemical and plasma methods. Wet chemical treatments such as HF, buffered HF, HCl, HNO<sub>3</sub>, H<sub>2</sub>SO<sub>4</sub>, KOH, NaOH, NH<sub>4</sub>OH, and (NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> aim to reduce surface contamination linked to carbon or oxygen [12, 47-51]. Plasma pretreatments,

encompassing H<sub>2</sub>, N<sub>2</sub>, O<sub>2</sub> (descum), Cl-based, SF<sub>6</sub>, and Ar, have been designed to eliminate the surface's native oxide layer, any lithography residue, and to restore surface dangling bonds, enhancing surface termination and Ga-N stoichiometry [4]. Beyond surface pretreatment, Si ion-implantation has been introduced for both planar and recessed contacts prior to metal deposition. This process transforms the surface i-GaN into n-GaN, resulting in a more concise tunneling path [6]. Yet, activating the implanted Si demands high-temperature annealing (exceeding 1000°C). This is problematic as it can degrade the epitaxial properties since the epitaxial growth temperature is typically within a similar range. Ohmic metal stacks can be deposited via evaporation or sputtering, with further details on the metal stack design provided in section 3.2.3. Subsequently, the annealing of the ohmic metal stacks is executed in a rapid thermal processing (RTP) system in an oxygen-free environment. Commonly, either Ar or N<sub>2</sub> serve as ambient gases during this high-temperature procedure.

The creation of planar ohmic contacts with a low  $R_c$  can face issues in reproducibility and uniformity due to variations in barrier design and thickness. Broadly, a thicker barrier extends the tunneling distance between the metal and 2DEG. An increased Al content in the AlGaN barrier heightens the barrier height, leading to a diminished thermionic transport probability. In certain cases, an AlN exclusion (spacer) layer is introduced between the barrier layer and the 2DEG to further confine the 2DEG and provide a sharp interface. This additional layer can exacerbate the challenge of crafting ohmic contacts with a low  $R_c$ . Such complexities underscore the necessity for alternative strategies, such as deeply recessed sidewall contacts, as discussed in [Paper A and B].

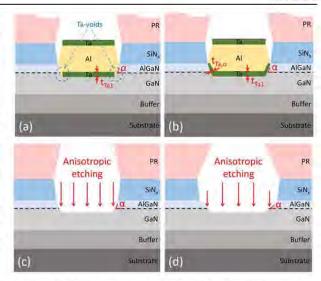

#### 3.2.2 Recessed contacts

While annealing in planar contacts can transform the barrier into an n-type semiconductor by producing nitrogen vacancies in the AlGaN/GaN barrier, the distance remains substantial, hindering efficient electron tunneling to the 2DEG. To address this, shallow recessed contacts have been introduced. These contacts minimize the tunneling distance by etching the barrier of the epi-structure using Clbased dry etching through inductively coupled plasma reactive ion etching (ICP-RIE). A reduced barrier thickness shortens the tunneling distance between the metal and the 2DEG, as illustrated in Fig. 3.3a. However, this thinning also diminishes the 2DEG concentration, which can compromise the carrier density required for optimal tunneling transportation. As a result, a delicate balance must be considered between barrier thickness and 2DEG density, necessitating innovative approaches to achieve contacts with a lower R<sub>c</sub>. Some studies suggest that the ideal etching depth is about  $1\sim5$ nm above the 2DEG [5, 8, 52]. However, commercially available ICP-RIE systems often fail to ensure consistent and reproducible etching depths across an entire wafer. To overcome this challenge, deeply recessed contacts—which etch through the barrier to the GaN region housing the 2DEG—were explored in [Paper A and B], as depicted in Fig. 3.3b (see section 3.3). Such deeply recessed contacts are less affected by variations in etching depth since the contact area is established on the recessed sidewall.

**Fig. 3.3.** (a) shallow recessed contacts and a trade-off between etching depth and 2DEG density, (b) deeply recessed contacts, and (c) patterned recessed contacts [5].

A viable solution to counteract the reduction in 2DEG density due to a thinner barrier is the use of patterned recessed contacts. The dimensions of the via hole pattern are tailored to be large enough for metal deposition to reach the base, yet sufficiently compact to mitigate the effect on 2DEG density. This results in a notably low  $R_c$  of 0.12  $\Omega$  mm when utilizing Ti-based metal stacks, however, with a drawback of process complexity [5].

Regrown contacts present another innovation, merging the techniques of recess etching and Si n-type doping. This approach achieves an exceptionally low  $R_c$  (less than 0.1  $\Omega$ ·mm), in contrast to traditional alloyed ohmic contacts which typically have a  $R_c$  exceeding 0.1  $\Omega$ ·mm. This is achieved by lattice-matching the regrowth of n-GaN with a high concentration of Si-dopants using either molecular beam epitaxy (MBE) or metal-organic chemical vapor deposition (MOCVD) within the recessed region. This process furnishes an abundant electron supply while simultaneously minimizing the tunnelling distance between the semiconductor and the contact metal situated atop the regrown n-GaN [3, 53].

## 3.2.3 Contact metal designs

Metal stacks need to fulfill the two requirements to form good ohmic contacts with low R<sub>c</sub>, including a low work function of the first (bottom) metal layer and a capability of extracting nitrogen from GaN. Several reported contacts are summarized in Table 3.1.

|   | Table 3.1. Offwire Contacts Examinees iter outed in Literature. |                                                             |                             |                            |                      |                                      |      |      |

|---|-----------------------------------------------------------------|-------------------------------------------------------------|-----------------------------|----------------------------|----------------------|--------------------------------------|------|------|

|   | Metal<br>stacks                                                 | Al <sub>x</sub> Ga <sub>l-x</sub> N<br>barrier [x],<br>[nm] | AlN exclusion<br>layer [nm] | Anneal<br>temperature [°C] | $R_c$ $[\Omega  mm]$ | Contact categories                   | Ref  | Year |

| A | Ti/Al/Ni/A<br>u                                                 | 26%, 18                                                     | 0                           | 825                        | 0.18                 | Planar contact                       | [54] | 2013 |

| В | Ti/Al/Ni/A<br>u                                                 | 30%, 25                                                     | 0                           | 830                        | 0.1                  | Planar contact with plasma treatment | [4]  | 2018 |

| С | Ti/Al/Ni/A<br>u                                                 | 30%, 24                                                     | 1                           | 850                        | 0.12                 | Patterned shallow recessed contact   | [5]  | 2018 |

| D | Ti/Al/Ni/A<br>u                                                 | 30%, 27                                                     | 0                           | Without anneal             | 0.4                  | Recessed, Si ion implantation        | [6]  | 2006 |

| E | Si/Ge/Ti/A<br>l/Ni/Au                                           | 23%, 18                                                     | 0                           | 820                        | 0.3                  | Planar contact                       | [55] | 2017 |

| F | Ta/Si/Ti/Al<br>/Ni/Ta                                           | 26%, 18                                                     | 0                           | 850                        | 0.22                 | Planar contact                       | [54] | 2013 |

| G | Ti/TiN                                                          | 20%, 20                                                     | 2                           | 850                        | 0.13                 | Planar contact                       | [56] | 2014 |

| Н | Ti/TiN                                                          | 35%, 20                                                     | 0                           | 850                        | 0.6                  | Planar contact                       | [56] | 2014 |

Table 3.1. OHMIC CONTACTS EXAMPLES REPORTED IN LITERATURE.

| I | Ti/Al/Ti/Ti<br>N                     | 25%, 20   | 1   | 550            | 0.21      | Shallow recessed contact | [52]      | 2018 |

|---|--------------------------------------|-----------|-----|----------------|-----------|--------------------------|-----------|------|

| J | Ti/Al/W                              | 26.4%, 23 | 0   | 500            | 0.35      | Planar contact           | [57]      | 2018 |

| K | Ti/Al/Ni/Ti<br>N                     | 23%, 19   | 1   | 830            | 1.1       | Planar contact           | [58]      | 2020 |

| L | Ti <sub>5</sub> Al <sub>1</sub> /TiN | 25%, 20   | 0   | 880            | 0.06      | Planar contact           | [59]      | 2020 |

| M | TiAl₃/Au                             | 20%, 22   | 0   | 850-900        | 0.23      | Planar contact           | [60]      | 2024 |

| N | Ta/Al/Ta                             | 25%, 25   | 0   | 575            | 0.28      | Planar contact           | [7]       | 2011 |

| О | Ta/Al/Ta                             | 14%, 22   | 0   | 550            | 0.06      | Planar contact           | [7]       | 2011 |

| P | Ta/Al/Ta                             | 30%, 15   | 0   | 550-600        | 0.21/0.27 | Shallow recessed contact | [61]      | 2015 |

| Q | Ta/Al/Ta                             | 25%, 20   | 0   | 575            | 0.24      | Deeply recessed contact  | [Paper B] | 2018 |

| R | Ta/Al/Ta                             | 25%, 19   | 1   | 575            | 0.21      | Deeply recessed contact  | [Paper B] | 2018 |

| s | Ta/Al/Ta                             | 30%, 11   | 1   | 575            | 0.25      | Deeply recessed contact  | [Paper B] | 2018 |

| Т | Ti/Al/Ti                             | 30%, 11   | 1   | 550            | 0.14      | Deeply recessed contact  | [Paper A] | 2023 |

| U | Ti/Al/Ti                             | 52%, 3.5  | 1.5 | 550            | 0.15      | Deeply recessed contact  | [Paper A] | 2023 |

| V | Ti/Al/Ni/A<br>u                      | 25%, 20   | 1   | 810            | 0.16      | Shallow recessed contact | [62]      | 2024 |

| W |                                      | 25%, 22   | 0   | Without anneal | 0.2       | MBE regrown contact      | [63]      | 2011 |

| X | Ti/Au                                | InAlN/GaN | 0   | Without anneal | 0.05      | MBE regrown contact      | [3]       | 2020 |

| Y |                                      |           | 0   | Without anneal | 0.1       | MOCVD regrown<br>contact | [53]      | 2020 |

Conventional Ti/Al/Ni/Au contacts are showcased in examples A-C. Typically, it's simpler to achieve ohmic contacts with a low  $R_{\rm c}$  on epi-structures that lack an AlN exclusion layer. Example B serves as a testament to this, contrasting with Example A, and underscores the importance of thorough surface pretreatments prior to metal deposition. This involves eliminating surface oxides and contaminants. Example C depicts a resilient low  $R_{\rm c}$  achieved by patterning the recessed ohmic contact. By not fully removing the barrier layer, the 2DEG remains intact. Additionally, the tunneling distance is curtailed due to the presence of the recessed pit-hole.

Examples D-F illustrate the conventional Ti/Al-based metal arrangements paired with Si, an n-type dopant for GaN. However, Si, possessing a high work function of 4.85 eV, results in a significant  $\Phi_B$  [64]. This translates to a reduced probability of thermionic transport at the metal-semiconductor junction. In Example F, Si is deposited atop the Ta layer, which has a smaller work function, culminating in a R<sub>c</sub> lower than that in Examples D and E.

Al plays a pivotal role in ohmic contacts. It facilitates the extraction of nitrogen from GaN, resulting in the formation of Ti-Al-N or Al-N phase alloys. Yet, it tends to compromise surface morphology and edge precision. To circumvent this, there have been suggestions to either eliminate Al or employ TiN, TaN, and Tungsten (W) as cap layers. This alteration improves edge sharpness, especially vital for miniaturized devices, as depicted in Examples G-K. A recent study, as referenced in Example L and M, demonstrates that co-depositing Ti and Al as an alloy, rather than discrete layers, yields superior ohmic contact. This approach achieves a lower  $R_{\rm c}$  than traditional multilayer configurations.

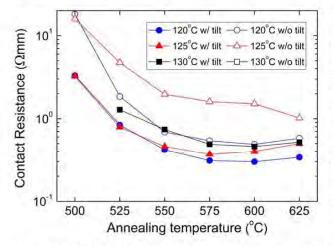

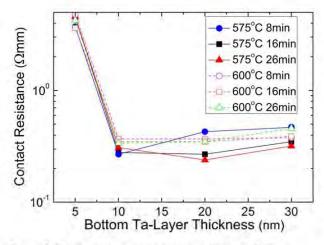

In our study [Paper B, Example Q·S], deeply recessed Ta/Al/Ta sidewall ohmic contacts were developed with a low  $R_c$  of  $\sim 0.24~\Omega$  mm. The results highlight the importance of process optimization including the metal coverage, sidewall angle, metal stack thickness ratio, and annealing temperature. These works lead to the innovation of the Ti/Al/Ti ohmic contacts [Paper A, Example T and U], which will be introduced in the following section. Moreover, Example V also showed that the Ti/Al metal stacks can provide very low  $R_c$  at high annealing temperature.

Diverging from the standard metal stack ohmic contacts, regrown contacts (Examples W-Y) forgo the annealing process. This is because the barrier is entirely eradicated through dry etching. Subsequently, a heavily Si-doped n-type GaN, which is lattice-matched, is regrown using MBE or MOCVD within the recessed area. This leads to a diminished  $\Phi_B$  and a concise tunneling distance.  $R_c$  values below 0.1  $\Omega$  mm have been reported across various epi-structures. Especially noteworthy are the regrown contacts on the InAlN barrier, which boasts a 2DEG concentration surpassing the conventional AlGaN barrier, recording an impressively low  $R_c$  of 0.05  $\Omega$  mm [3].

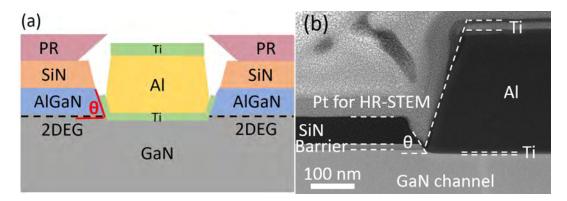

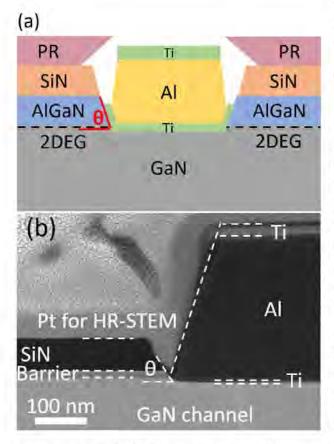

# 3.3 Deeply recessed Ti based ohmic contacts

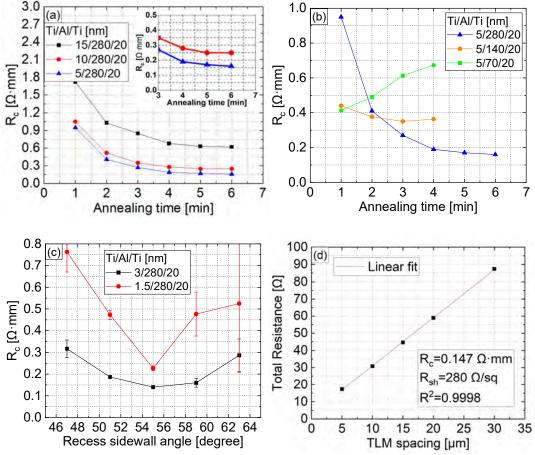

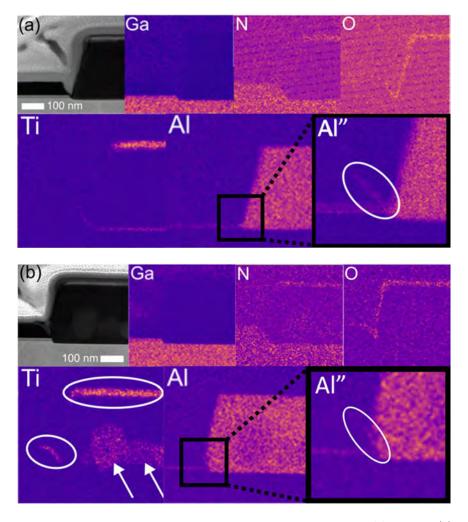

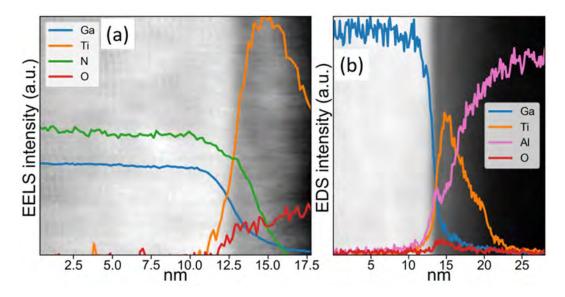

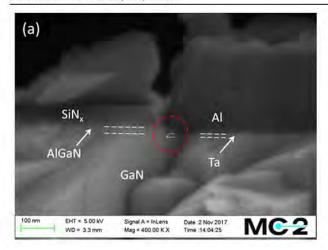

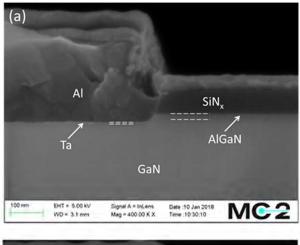

This study exhibits an innovative strategy for fabricating Ti/Al/Ti low-resistance ohmic contacts within AlGaN/GaN HEMTs, as outlined in [Paper A]. A contact resistance of approximately 0.15  $\Omega$  mm has been achieved and characterized using TLM structure (Fig. 3.2a and Fig 3.4). This is achieved by initially etching the barrier of the heterostructure beyond the depth of the channel, and subsequently applying Ti/Al/Ti ohmic metallization to the recessed sidewalls. Annealing of this metallization is conducted at a low temperature of 550 °C. The investigation encompasses a thorough examination of the influences exerted by the recessed sidewall angle, the respective thicknesses of the Ti and Al layers, and the specifics of the annealing process. The utility of this ohmic contact method has been verified on HEMT structures (Epi I and Epi II) as indicated in Table 3.2.

**Fig. 3.4.** (a) Schematic of TLM structure, (b) HR-STEM cross-section of annealed TLM with 10° tilted t<sub>Ti</sub> of 3 nm on Epi II.

Table 3.2. EPI-STRUCTURE USED IN THIS WORK

|                                                        | Epi I                                           | Epi II                                        |

|--------------------------------------------------------|-------------------------------------------------|-----------------------------------------------|

| Cap layer                                              | GaN, 1.4 nm                                     | GaN, 2 nm                                     |

| Barrier layer                                          | Al <sub>0.52</sub> Ga <sub>0.48</sub> N, 3.3 nm | Al <sub>0.3</sub> Ga <sub>0.7</sub> N, 9.7 nm |

| Spacer layer                                           | AlN, 1.5 nm                                     | AlN, 1.2 nm                                   |

| Channel layer                                          | GaN, 260 nm                                     | GaN, 255 nm                                   |

| Nucleation layer                                       | AlN, 60 nm                                      | AlN, 60 nm                                    |

| GaN RC <0 0 2>                                         | 94 arcsec                                       | 216 arcsec                                    |

| GaN RC <1 0 2>                                         | 353 arcsec                                      | 443 arcsec                                    |

| $n_{\rm s} [10^{13}/{\rm cm}^2]$                       | 1.16                                            | 1.07                                          |

| $\mu \left[ \text{cm}^2/\text{V}\cdot\text{s} \right]$ | 1746                                            | 1966                                          |

| $R_{sh} \left[ \Omega/sq. \right]$                     | 316                                             | 298                                           |

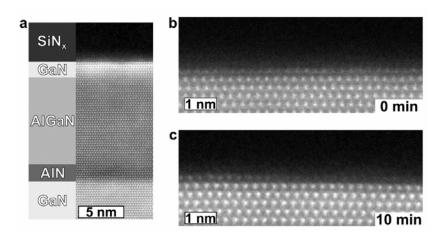

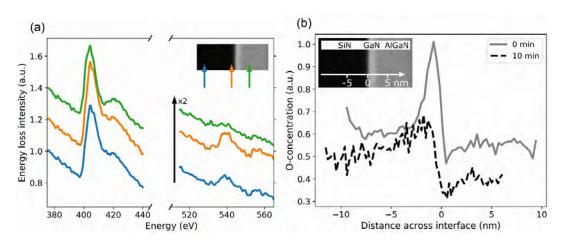

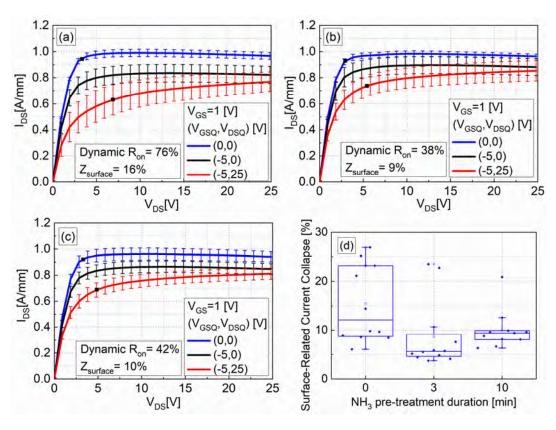

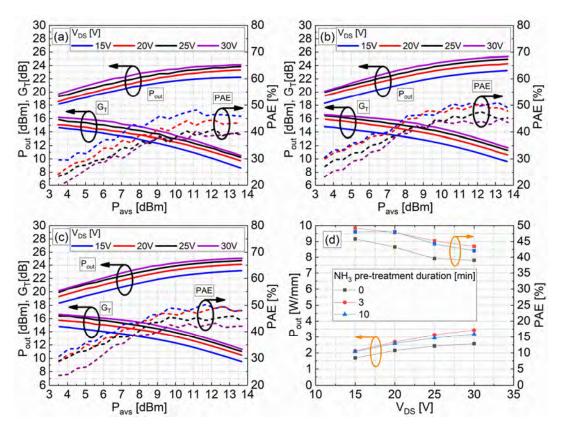

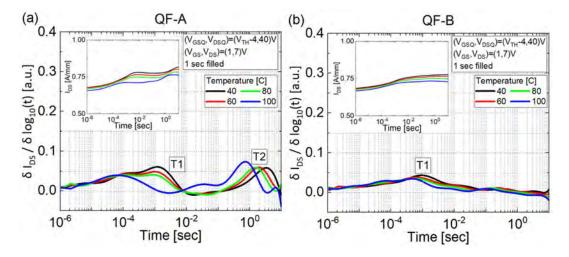

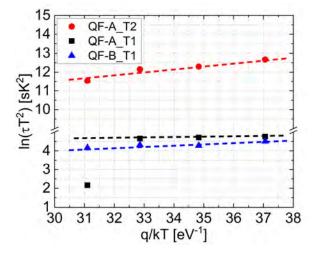

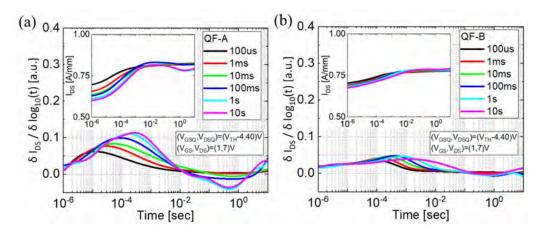

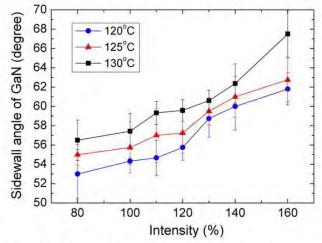

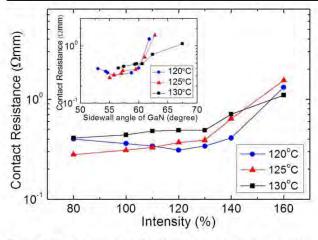

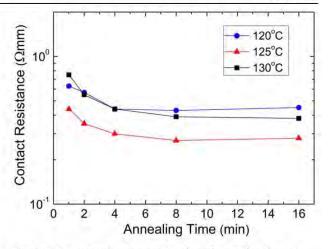

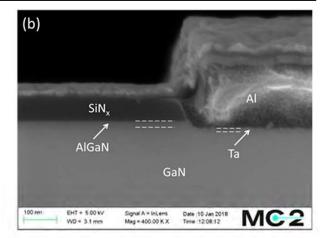

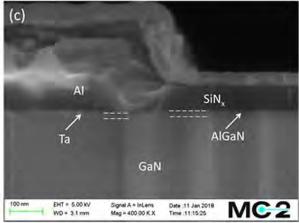

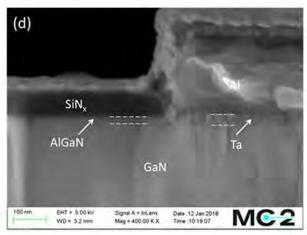

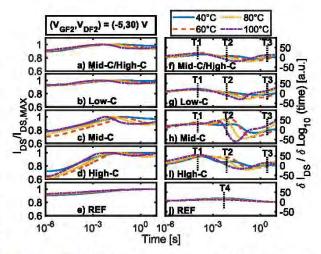

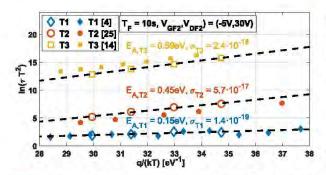

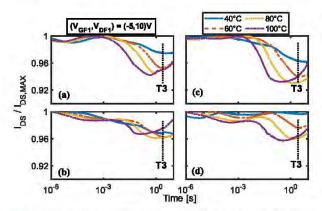

#### 3.3.1 TLM results