THESIS FOR THE DEGREE OF LICENTIATE OF ENGINEERING

# Accelerating CNN inference via co-design of convolutional algorithms and long vector processors

Sonia Rani Gupta

Division of Computer and Network Systems

Department of Computer Science & Engineering

Chalmers University of Technology

Gothenburg, Sweden, 2025

Accelerating CNN inference via co-design of convolutional algorithms and long vector processors

Sonia Rani Gupta

Copyright c2025 Sonia Rani Gupta except where otherwise stated. All rights reserved.

Department of Computer Science & Engineering Division of Computer and Network Systems Chalmers University of Technology and Gothenburg University Gothenburg, Sweden

This thesis has been prepared using LATEX. Printed by Chalmers Reproservice, Gothenburg, Sweden 2025.

### Abstract

Model serving has become crucial for AI applications, with convolutional neural networks (CNNs) driving various applications from object detection to speech recognition. While specialized accelerators and GPUs offer high performance for CNN inference, CPU-based solutions provide better availability and portability for server-side and mobile computing. Vector architectures such as RISC-V Vector extension and ARM Scalable Vector Extension have emerged as a promising solution, offering GPU-like parallel processing capabilities with low latency, high availability, and lower energy consumption.

This thesis investigates co-design opportunities in vector architectures for CNN inference, focusing on the interplay between convolutional algorithmic optimizations and hardware design choices. First, it conducts a co-design study that explores both convolutional algorithm optimizations and hardware parameter tuning such as vector lengths, cache sizes, and vector lanes for CNN inference on ARM-SVE and RISC-VV architectures. Second, it explores the co-design of CNN layers by studying three distinct algorithmic implementations: Direct, im2col+GEMM, and Winograd, in conjunction with hardware parameters for RISC-VV.

While optimizing the im2col+GEMM algorithm, various optimizations have been applied to the GEMM kernel; however, our study shows that not all optimizations benefit different vector architectures equally. Our co-design study using the gem5 simulator demonstrates an  $\sim$ 5× performance improvement with 16384-bit vector lengths and 256MB of L2 cache, compared to 512-bit vectors and 1MB of L2 cache. Since larger tile sizes cannot be used for the Winograd algorithm due to numerical inaccuracies, this thesis proposes intertile parallelism across the input/output channels using 8×8 tiles per channel to utilize longer vector lengths. This approach improves data reuse and achieves an additional performance improvement of 2.4× (compared to im2col+GEMM) on the A64FX processor. Our co-design study also shows that the Winograd algorithm has lower cache size requirements compared to im2col+GEMM.

The performance of convolutional algorithms depends on layer dimensions (input/output/kernel dimensions, stride, and input/output channels), while computational demands influence SIMD requirements, and cache sharing impacts runtime algorithm selection in model serving. Our study shows that Winograd performs better with smaller vector lengths, whereas the Direct algorithm excels with longer vectors. While im2col+GEMM benefits from larger caches, Direct and Winograd exhibit varying cache sensitivity across VGG16 layers. In contrast, all YOLOv3 layers benefit from the largest simulated L2 cache across all algorithms. To address these complexities, this thesis proposes a random forest classifier that selects the optimal algorithm per layer with 92.8% accuracy and per-layer algorithm selection improves performance by  $\sim\!\!2\times$  compared to using a single algorithm. Finally, our Pareto analysis of area-performance trade-offs for a 7nm RISC-V multicore model shows that algorithm selection leads to increased throughput per area, highlighting the need for co-design in the context of model serving.

**Keywords:** CNNs, co-design, GEMM, Winograd, Direct, optimizations, long vector architectures, vector length agnostic ISAs, model serving

## Acknowledgment

First and foremost, I would like to express my deep and sincere gratitude to my advisor, Professor Miquel Pericàs, for giving me the opportunity to pursue my studies and providing contiguous guidance and support during my studies. His vast knowledge, vision, motivation, and confidence in my work have profoundly encouraged me and taught me the methodology to effectively conduct my research and present my findings with clarity.

I would also like to thank my co-advisor Dr. Nikela Papadopoulou for her insightful feedback and enthusiasm. Her extensive research experience has inspired and taught me to conduct my research work with greater clarity and confidence.

I am grateful to Professor Pedro Petersen Moura Trancoso, who has been my examiner. I would like to say thanks to my, past and present, colleagues and friends at Chalmers, Pirah, Jing, Bhavishya, Hari, Minyu, Nufail, Mahmoud, Fareed, Mateo, Neethu, Per, Monica, Arne, and many others who created a nice and friendly work environment.

Lastly, I would like to express my deepest gratitude to my family for their unwavering support. I am especially thankful to my husband, Amit, and my daughters, Aamia and Aanvi, for always being there for me. I would not have been able to accomplish this without them.

This research was supported by multiple funding sources: The Swedish Research Council (grant no. 2020-04892), and the European High-Performance Computing Joint Undertaking (JU) through several grant agreements: No. 956702 (eProcessor), No. 101036168 (EPI SGA2, under Framework Partnership Agreement No. 800928), and No. 101034126 (The European PILOT). The JU receives support from the European Union's Horizon 2020 research and innovation programme and multiple member states (Spain, Sweden, Greece, Italy, France, and Germany). Additional funding was provided by the Swedish Foundation for Strategic Research through the PRIDE project (CHI19-0048). The simulations were enabled by resources provided by the Swedish National Infrastructure for Computing (SNIC) at NSC (grant no. 2018-05973) and the National Academic Infrastructure for Supercomputing in Sweden (NAISS, grant no. 2022-06725), both partially funded by the Swedish Research Council. We thank the Barcelona Supercomputing Center for providing access to an A64FX machine.

## List of Publications

### Appended publications

This thesis is based on the following publications:

- [I] Sonia Rani Gupta, Nikela Papadopoulou, and Miquel Pericàs "Accelerating CNN inference on long vector architectures via co-design" 2023 IEEE International Parallel and Distributed Processing Symposium (IPDPS), St. Petersburg, FL, USA, 2023, pp. 145-155, doi: 10.1109/IPDPS54959.2023.00024.

- [II] Sonia Rani Gupta, Nikela Papadopoulou, Jing Chen, and Miquel Pericàs "Co-Design of Convolutional Algorithms and Long Vector RISC-V Processors for Efficient CNN Model Serving" In Proceedings of the 53rd International Conference on Parallel Processing (ICPP '24). Association for Computing Machinery, New York, NY, USA, 73-83. https://doi.org/10.1145/3673038.3673121.

### Other publications

The following publications are not included in the thesis.

[a] Sonia Rani Gupta, Nikela Papadopoulou, and Miquel Pericàs "Challenges and Opportunities in the Co-design of Convolutions and RISC-V Vector Processors"

In Proceedings of the SC '23 Workshops of The International Conference on High Performance Computing, Network, Storage, and Analysis (SC-W '23). Association for Computing Machinery, New York, NY, USA, 1550–1556. https://doi.org/10.1145/3624062.3624232.

## Contents

| A            | Abstract |                           |                                                                                                                                                                  |  |  |

|--------------|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| $\mathbf{A}$ | ckno     | wledgement                | <ul> <li>iii</li> <li>v</li> <li>viii</li> <li>1</li> <li>3</li> <li>3</li> <li>4</li> <li>5</li> <li>7</li> <li>7</li> <li>9</li> <li>13</li> <li>21</li> </ul> |  |  |

| Li           | st of    | Publications              | vii                                                                                                                                                              |  |  |

| 1            | Inti     | roduction                 | 1                                                                                                                                                                |  |  |

|              | 1.1      | Background                | 3                                                                                                                                                                |  |  |

|              | 1.2      | Related Work              | 3                                                                                                                                                                |  |  |

|              | 1.3      | Problem Statements        | 4                                                                                                                                                                |  |  |

|              | 1.4      | Contributions             | 5                                                                                                                                                                |  |  |

| <b>2</b>     | Sun      | nmary of the Papers       | 7                                                                                                                                                                |  |  |

|              | 2.1      | Paper I - Summary         | 7                                                                                                                                                                |  |  |

|              | 2.2      |                           | 9                                                                                                                                                                |  |  |

| 3            | Cor      | nclusions and Future Work | 13                                                                                                                                                               |  |  |

| 4            | Pap      | oer I                     | 21                                                                                                                                                               |  |  |

| 5            | Pap      | oer II                    | 35                                                                                                                                                               |  |  |

X CONTENTS

## Chapter 1

## Introduction

Convolutional Neural Networks (CNNs) play a key role in Artificial Intelligence (AI) inference, powering a wide range of applications such as object detection [1], natural language processing [2], and speech recognition [3]. These models require high throughput and power efficiency due to power constraints (e.g., battery-powered embedded devices or the power caps in data centers). Offloading compute-intensive operations to neural accelerators and GPUs has become a common approach to accelerate CNN inference [4–6]. However, integrating specialized accelerators [7,8] into general-purpose computing systems remains challenging. Various frameworks [9–11] are optimized for GPUs, but server-side inference requires availability and low latency [12], while mobile and embedded devices benefit from CPU availability and portability [13,14]. Consequently, optimizing CNNs has become popular on CPUs [14–16], while CPU vendors are increasingly adding deep neural networks (DNN) capabilities to processors [17].

Vector-enabled processors have seen renewed interest as they bring GPU-like parallel processing capabilities to CPUs while maintaining lower energy consumption. In this context, tightly coupled modern long vector processors with low latency, high performance, and power efficiency such as RISC-V Vector Extension (RISC-VV) [18] and ARM Scalable Extension (ARM-SVE) [19] are considered a promising option for efficient CNN inference serving [20,21]. These vector architectures are based on vector length agnostic (VLA) instruction set architecture (ISA), which ensures code portability across hardware platforms with distinct vector lengths.

Maximizing performance in vector architectures requires efficient algorithmic optimizations and a deeper exploration of the design space, such as leveraging new levels of parallelism introduced by vector units and understanding the relationships between micro-architectural parameters, performance characteristics, and area efficiency for applications of interest. Manual code transformation and optimization are necessary to achieve an efficient algorithmic implementation by exposing the maximum available SIMD parallelism to the vector unit. Additionally, modern architectures are integrating longer vector lengths to support scientific applications and AI workloads. Longer vector lengths increase the high data demand, necessitating larger caches. Furthermore, additional vector lanes become necessary to maintain computational throughput. The relationship between cache capacity, vector lanes, and vector length creates

complex performance trade-offs that must be carefully analyzed. Since these components occupy a significant die area and greatly impact performance, tuning them to the requirements of optimized kernels is essential for designing efficient, high-performing vector architectures for CNN inference.

CNNs consist of consecutive layers, with convolutional layers being the most time-consuming. These convolutional layers can be implemented using various algorithms [22], such as im2col+GEMM, Direct, Winograd, and FFT. The Direct algorithm slides convolutional weights over the input tensor, performing dot products [23]. The im2col+GEMM algorithm transforms the image into a column matrix, turning the convolutional operation into a matrix multiplication by convolving the transformed input matrix with the weight matrix. Winograd and FFT reduce computational complexity, but require transforming the image and weights, performing block-wise multiplications, and applying output transformations. Winograd is effective with small kernel sizes, such as  $3\times3$  or  $5\times5$  [24], while FFT is better suited for larger kernel sizes [25].

Convolutional layers in CNNs vary in their dimensions, including input, output, kernel height and width, input and output channels, and stride. Different convolutional algorithms exhibit varying performance based on each layer's dimensions, due to differences in computational complexity and memory footprints [13]. Additionally, cache size and vector length can impact performance, as some algorithms, like im2col+GEMM, increase the memory footprint. Algorithmic optimizations that exploit longer vector lengths can help achieve higher performance from the vector unit. Moreover, model serving is rapidly becoming the standard approach for deploying AI applications, with cloud providers reporting hundreds of trillions of AI model executions daily [26]. Model serving frameworks [27, 28] enable concurrent model replicas for better resource utilization, although cache contention from co-running inferences affects algorithmic decisions.

Despite extensive research on CNNs and hardware microarchitectural parameters tuning [20, 29–38], the interplay between the optimization space of convolution algorithms and the design space of hardware parameters remains unexplored. The lack of a co-design approach can hamper the design of future vector architectures based on CPUs for CNN inference and model serving.

This thesis fills this gap by providing a co-design study that jointly explores the optimization of convolutional algorithms and the tuning of hardware parameters on long vector architectures, aiming to provide guidance to programmers, hardware designers, and compiler developers. Additionally, it proposes intertile parallelism across input/output channels to utilize longer vector lengths for the Winograd algorithm. Furthermore, this thesis conducts a co-design exploration, focusing on the software parameters of convolutional layers and algorithmic implementations alongside hardware parameters for vector architectures, demonstrating that selecting the best algorithm per layer leads to better performance compared to using a single algorithm for all layers. To select the best algorithm at runtime, this thesis proposes a Random Forest classifier that selects the best algorithm for 92.8% of the cases. Furthermore, analyzing the performance-area trade-offs reveals that combining per-layer algorithm selection with model co-location enhances throughput per unit area, emphasizing the importance of co-design in model serving.

1.1. BACKGROUND 3

### 1.1 Background

Vector architectures: Vector supercomputers with long vector lengths [39] were first developed in the 1970s to solve scientific problems. A new era of SIMD architectures began in the 1990s with short vectors, initially built for media streaming applications, which later became popular in Digital Signal Processing (DSP) and general-purpose computing [40,41]. SIMD ISAs with fixed short vector length are now commonly used for general-purpose computing. However, these ISAs provide limited portability, as a new instruction set extension is required if a longer vector length is needed. To overcome this limitation, modern long vector architectures such as RISC-VV [18] and ARM-SVE [19] offer vector length agnostic ISAs, where there is no need to specify a specific vector length. RISC-VV supports MVL up to 16384-bits in powers of 2 whereas ARM-SVE implementations range from 128-bit to 2048-bits with 128-bit increments, as implemented in Fujitsu's A64FX processor with its 512-bit vector length.

Convolutional neural network models The core building block of CNNs is the convolutional layer, which performs the convolution operation between the input data and a set of learnable filters. These layers are followed by other types of layers, including pooling layers, fully connected layers, and normalization layers, depending on the network architecture. YOLOv3, CNN based object detection model, which contains 107 layers of five different types, 75 of these layers are convolutional, making them the most computationally intensive part of the network. Similarly, in VGG16, a model for image classification, 13 of the 25 layers are convolutional, with an additional 3 fully connected layers. the convolutional layers in YOLOv3 and VGG16 consume  $\sim 96\%$  and  $\sim 64\%$  of the total inference time, respectively, when profiled on A64FX using Linux perf.

Algorithms for Convolutions: To optimize the performance of CNN-based models, various convolutional algorithms can be employed. In this thesis, I use three convolutional algorithms: im2col+GEMM, Direct, and Winograd to implement the convolutional layers as most CNN-based network models use convolutional layers with small kernel sizes of 1×1, 3×3 or 5×5. I developed an optimized version of the im2col+GEMM algorithm in the Darknet [42] framework, where the convolutional layer is implemented using the im2col+GEMM algorithm. Additionally, I developed an optimized version of the Winograd algorithm from the NNPACK [43] package for implementing these convolutional layers. I then developed and optimized the Direct algorithm for implementing these convolutional layers inside the Darknet framework.

### 1.2 Related Work

Several works have focused on optimizing convolutions for vector architectures. Specifically, Kelefouras et al. [44] vectorize and optimize the 2D direct convolutions on Intel AVX. Wang et al. [35] optimize the Direct algorithm on ARM NEON. Wang et al. [37] optimize the Winograd algorithm on RISC-V architectures with a custom instruction extension. Louis et al. [29] port and

optimize convolutional and matrix multiplication kernels of CNNs from Tensor-Flow lite and study the reduced number of instructions on RISC-VV. Alaejos et al. [45]optimize GEMM for deep learning on the ARM-NEON, ARM-SVE, and Intel AVX512 vector extensions. Arm [46] has developed an ARM Compute Library to optimize convolutional kernels for ARM-SVE. Dolz et al. [47] optimize the im2col transformation and Winograd algorithms for ARM-SVE. In another work, Dolz et al. [38] optimize the Winograd algorithm for Intel AVX, ARM NEON, and ARM-SVE architectures. Santana et al. [36] optimize the Direct algorithm for long vector architectures, focusing on the NEC SX Aurora architecture

In the context of microarchitectural parameter tuning of modern long vector architectures, Kodama et al. [33] evaluate the "triad", "gemm" and "nbody" application kernels with multiple vector lengths and number of physical registers using ARM-SVE and evaluated the impact of vector length. Ramirez et al. [32] study the impact of microarchitectural parameters, such as vector lane and vector length, using different vectorized kernels presented in the RISC-V Vectorized Benchmark Suite.

Concerning performance comparisons of different algorithmic implementations of convolutions, Jordà et al. [48] and Xu et al. [49] perform such an analysis on GPUs. Jordà er al. [48] focus on cuDNN and propose that different algorithms should be used depending on the kernel size. Xu et al. [48] also look at cuDNN implementations and propose a scheme for algorithm selection based on the convolution dimensions. Dolz et al. [50] focus on performance-energy tradeoffs of the different algorithms for convolutions on ARM processors. Zlatenski et al. [51] perform a comparative analysis of Winograd and FFT for convolutions using different CNNs on modern CPUs, for full network models.

This thesis focuses on optimizing the im2col+GEMM, Winograd, and Direct convolutional algorithms for long vector architectures using vector length agnostic ISAs. It also presents a co-design study that explores the interaction between microarchitectural parameters and algorithmic optimizations to fully assess the performance potential of vector architectures for CNN inference, providing valuable insights for programmers, hardware designers, and compiler developers. Furthermore, this thesis conducts a co-design study to select the optimal algorithm for each convolutional layer and analyzes its impact on the achievable throughput per area for model serving.

### 1.3 Problem Statements

**Problem 1:** Prior work on CNN inference on vector architectures focuses either on applying algorithmic optimizations [20,29–31,38] or on studying the hardware micro-architectural parameters design points [32–34]. These studies miss an opportunity to explore the trade-offs in algorithmic and architectural co-design for CNN kernels running on long vector architectures. To address this gap, this thesis investigates the following problem statement.

How to study the design space exploration to co-design an effective vector architecture for high performing CNN inference?

**Research questions:** To provide a solution to the problem, we need to answer four research questions.

1.4. CONTRIBUTIONS 5

Q1 Are all algorithmic optimizations beneficial for different vector architectures?

- Q2 How is the performance of the im2col+GEMM algorithmic implementation affected by very long vector lengths, larger caches, and more vector lanes within a vector unit?

- Q3 Can the Winograd algorithm improve the performance of convolutional layers on long vector architectures?

- Q4 Can the performance of the Winograd implementation benefit from longer vectors and larger caches?

**Problem 2:** Previous studies [35–37,47,50,52,53] have focused on optimizing the performance of specific algorithms on vector architectures, presenting comparative analysis with state-of-the-art libraries for different layers of network models on vector processors, and providing a comparative analysis of different algorithmic implementations of convolutional layers on SIMD ARM-based architectures. Despite the extensive research on convolutional neural networks and various algorithmic implementations, the mutual impact of convolution algorithms and hardware parameters remains unexplored. This limits resource utilization and hampers the task of effectively designing future CPUs for CNN model serving. This thesis performs a co-design study of three convolutional algorithms: Direct, im2col+GEMM, and Winograd and addresses the following problem statement:

How can model serving for CNNs achieve higher performance by co-designing vector architectures?

**Research questions:** To provide a solution to the problem, four research questions need to be addressed in this context:

- Q5 What is the performance of different convolutional algorithms for different layers on vector architectures?

- Q6 Is there any single algorithm that benefits all the convolutional layers?

- Q7 How to predict the optimal algorithm for each convolutional layer?

- Q8 What are the throughput-area tradeoffs to efficiently serve CNNs with vector architectures?

### 1.4 Contributions

This thesis is based on two papers.  $Paper\ I$  addresses the first problem statement and answers the research questions 1, 2, 3 and 4.  $Paper\ I$  is the first work that shows the impact of different algorithmic optimizations on different vector architectures (decoupled and integrated) with CNN kernels.  $Paper\ I$  also proposes a novel vectorized implementation of Winograd implementation with ARM-SVE that uses inter-tile parallelism across the input/output channels for utilizing the longer vector lengths. The main contributions of this paper are:

- We compare different algorithmic optimizations of the GEMM kernel across two vector architectures: ARM-SVE (tightly integrated vector architecture) and RISC-VV (decoupled vector architecture). Our analysis demonstrates that not all optimizations benefit different vector architectures equally. Further, our co-design study shows that longer vector lengths and bigger caches help to improve the performance by  $\sim 5\times$ , however, scalability becomes limited with very long vector lengths (16384-bit).

- We vectorize the Winograd kernels using inter-tile parallelism, which helps to achieve 1.35× and 1.5× for YOLOv3 and VGG16 network models, respectively, compared to im2col+GEMM on ARM-SVE. Our co-design study shows that our Winograd algorithm is less sensitive to L2 caches compared to im2col+GEMM.

In Paper II, we perform a comparative analysis of Direct, Winograd, and two variants of im2col+GEMM algorithms on each convolutional layer of the YOLOv3 and VGG16 network models. Our co-design analysis shows that the performance of the algorithms for a convolutional layer depends on each layer's dimensions and hardware parameters. To predict the best algorithm for each convolutional layer, in Paper II, we train an algorithm selection model using a random forest that takes each layer's dimensions and the hardware's microarchitectural parameters as inputs and outputs algorithm with the lowest execution time for each layer. Paper II addresses the second problem statement and addresses the research questions 5, 6, 7, and 8. The main contributions of this paper are:

- Our performance comparison with 512-bit vector length and 1MB L2 cache shows that Winograd is the best choice for layers with 3×3 kernel size, whereas im2col+GEMM works best for layers with skinnier matrices. On the other hand, Direct works best for layers with high input dimensions but low input/output channels.

- Our co-design study shows that Winograd works best with smaller vector lengths while Direct excels with longer vector lengths. im2col+GEMM takes benefit from larger caches except for layers with extremely skinny matrices. Direct takes maximum benefit out of larger caches with longer vector lengths.

- We train a Random Forest classifier using 5-fold validation with shuffling, achieving a prediction accuracy of 92.8%. Selecting the optimal algorithm for each layer can boost performance by more than 2× compared to using a single algorithm. Our performance-to-area trade-offs for both single and multiple model instances demonstrate that carefully selecting the algorithm for each layer enables higher performance in a reduced area.

The rest of the thesis is organized as follows. In Chapter 2, a summary of each paper is presented. Finally, Chapter 3 concludes the thesis, and discusses some possible future research directions.

## Chapter 2

## Summary of the Papers

### 2.1 Paper I - Summary

As an alternative to off-chip accelerators, long vector length agnostic architectures such as RISC-VV and ARM-SVE can offer high performance for machine learning workloads and higher energy efficiency, making CPUs suitable for CNN inference. However, manual transformations and optimizations are key to achieving efficient algorithmic implementations and maximizing performance from these long vector architectures. Furthermore, tuning hardware parameters such as vector lengths and L2 cache size to the requirement of algorithmic optimizations can significantly impact performance. Therefore, it is important to have a joint exploration of the design space of vector architectures and optimization space of CNNs to have design points for a high performing vector architecture for CNNs. While existing works focus either on optimizing convolutional algorithms [20, 29–31] or tuning hardware parameters [32–34], they miss the trade-offs between both. In Paper I, we bridge this gap and perform a co-design study between algorithmic optimizations and micro-architectural parameter choices, aiming to give guidance to programmers, compiler developers, and hardware designers.

Convolutional layers are the most time-consuming of CNNs. In Darknet, this layer is implemented using the im2col+GEMM algorithm with GEMM consuming 93.4% of the computation time when compiled with clang on the A64FX system. For experiments, we use the YOLOv3 (object detection) and VGG16(image classification) network models, from the Darknet framework on a 768×576 pixels input image. We use the gem5 simulator [32,54] to assess the impact of integrating vector units tightly to the core in the case of ARM-SVE and as a decoupled vector architecture attached to the L2 cache in the case of RISC-VV.

To optimize the convolutional layer, we optimize all kernels in the Darknet framework using intrinsic instructions of the respective ISAs, mainly focusing on the GEMM kernel. We optimize the GEMM kernel using two approaches: 3 loops and 6 loops. We apply the following optimizations to the 3-loop implementation: i) vectorization with intrinsic instructions ii) contiguous memory loads/stores to/from vector registers, iii) loop reorder, and iv) loop unrolling. We apply the following BLIS-like optimizations to the 6-loop implementation:

i) loop reorder, ii) matrix packing, iii) block size tuning, iv) loop unrolling, v) prefetching, and vi) vectorization using intrinsic instructions. We simulate the first 4 convolutional layers of the YOLOv3 network on RISC-VV@gem5 with a 512-bit vector length, 1MB of L2 cache and 8 vector lanes, on a single core with different block sizes. We observed that the optimal block size for the 6-loop implementation is  $16 \times 512 \times 128$ , which differs  $\sim 2\%$  with 3-loop implementation, a difference that is not significant in the simulated environment. This is because VPU is directly attached to the L2 cache, not taking any benefit from bringing packed matrices in the L1 cache beforehand. Additionally, RISC-VV@gem5 does not support software prefetching, which is a desired feature in the 6-loops implementation. On ARM-SVE@gem5, the 6-loop implementation achieves a 15% performance gain over the 3-loop approach, leveraging cache usage despite the lack of software prefetching. On the other hand, we observe a 2× performance improvement with ARM-SVE@A64FX using 6-loop implementation, where the 6-loop implementation is able to take advantage of the caches and prefetching.

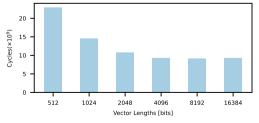

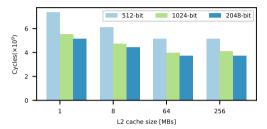

Further, we tune the hardware parameters using the optimized 3-loop implementation in the case of RISC-VV@gem5 with the first 20 layers of the YOLOv3 model. Increasing the vector lengths from 512-bit to 16384-bit showcases the performance saturates beyond the 8192-bit vector length. Increasing the L2 cache size from 1MB to 256MB shows a  $1.5\times$  -  $1.9\times$  performance gain for different vector lengths Our study reveals that larger L2 caches are beneficial with longer vector lengths, but the performance gains of very long vector lengths are limited, as with 256MB L2 cache performance improves by  $\sim\!\!5\%$  from 8192-bit to 16384-bit vector lengths. Additionally, we tune the hardware parameters using 6-loops optimization on ARM-SVE@gem5 which validates the observations made by RISC-VV@gem5 that our optimized kernels can benefit from longer vectors and larger cache sizes.

As an alternative to im2col+GEMM, we have optimized the Winograd implementation of the convolutional layer with  $3\times3$  kernel size from the NNPACK package. For vectorizing the Winograd algorithm to utilize long vector lengths in a VLA way, Paper I proposes an inter-tile parallelism across the input/output channels by using an  $8\times8$  tile from each channel on ARM-SVE. Using 4 input/output channels with one row of  $8\times8$  tiles from each channel as shown in Figure 2.1, we can utilize two 512-bit vector registers. To utilize longer vector lengths, we increase the number of input/output channels accordingly, e.g. 16 channels for 2048-bit vector registers. For vectorizing the tuple multiplications in a VLA way on ARM-SVE, we increase the block size from 3 to 16 with 4 elements in each block i.e., utilizing a maximum of 2048-bit vector lengths. For 512-bit vector lengths, an additional performance of  $1.5\times$  is achieved on top of im2col+GEMM.

Figure 2.1: Inter-tile parallelism in Winograd

2.2. PAPER II - SUMMARY 9

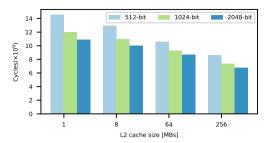

Increasing the vector length from 512 to 2048 bits while keeping the L2 cache at 1MB, we observe a  $1.4\times$  performance improvement for both network models. Increasing the L2 cache size from 1MB to 256MB improves performance by  $1.75\times$  and  $1.4\times$  for all vector lengths in YOLOv3 and VGG16 respectively. All layers in VGG16 use Winograd, which has smaller cache requirements compared to im2col+GEMM, whereas several layers in YOLOv3 invoke im2col+GEMM. This emphasizes that our Winograd implementation does not have high cache requirements.

### 2.2 Paper II - Summary

CNN models are built upon a series of consecutive layers, where each layer is distinct based on dimensions such as input, output, kernel's height and width, input and output channels, and stride. Multiple algorithms such as im2col+GEMM, Winograd, Direct, and FFT can be used to implement the convolutional layer. These algorithms can demonstrate varying performances for each layer as they have different computational complexities and memory footprints. Moreover, cache memory can impact the performance of these convolutional algorithms, as certain algorithms such as im2col+GEMM increase the memory footprint of a convolutional layer. Additionally, these convolutional algorithms need several optimizations to utilize the SIMD unit efficiently.

Model serving frameworks create replicas of a single model and distribute incoming requests across these replicas by maintaining load balancing. However, concurrent execution competes for cache resources, making the convolutional algorithms dependent on co-running inference tasks. Therefore, it is important to have a mutual impact of convolutional algorithms and hardware parameters to have efficient design points for future vector CPUs for CNN model serving. Previous studies [35–38] have focused on optimizing the performance of specific algorithms on vector architectures and presenting comparative analyses with state-of-the-art libraries for different layers of network models on vector processors. We identify the absence of a joint study of convolutional algorithms and hardware parameters as a missed opportunity. In paper II, we perform a co-design study of three distinct convolutional algorithms, Direct, im2col+GEMM, and Winograd for implementing convolutions on RISC-V based vector architecture. Since large kernel sizes are not common in modern CNNs, we do not consider the FFT algorithm in this work.

We use two variants of the optimized im2col+GEMM algorithm from Paper I. Additionally, we use the optimized Winograd algorithm from our workshop paper [55] on RISC-VV. For the Direct algorithm, we manually vectorize and optimize it with NHWC memory layout (where N refers to batch size, H refers to input height, W refers to input width and C refers to input channels) on RISC-VV using intrinsic instructions of the respective ISA. We evaluate each convolutional layer of the YOLOv3 and VGG16 network model on RISC-VV on a  $768 \times 576$  pixels input image using the gem5 simulator [56].

We evaluate each convolutional layer of both network models with a 512-bit vector length and 1MB of L2 cache size. Our study showcases that the Direct algorithm is better when input/output dimensions are high, but input/output channels are low. On the other hand, im2col+GEMM with 6 loops prevails

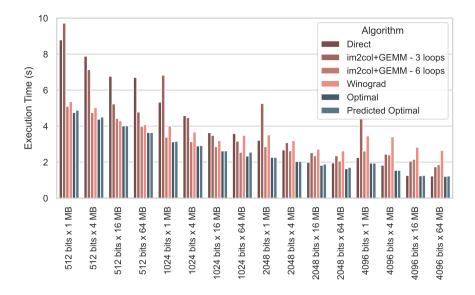

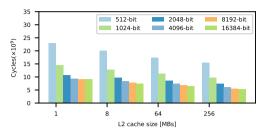

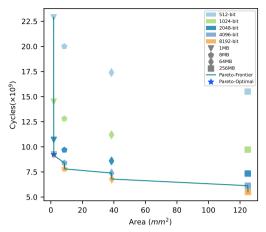

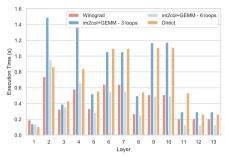

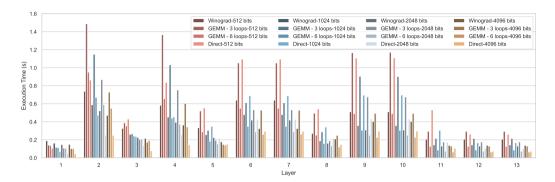

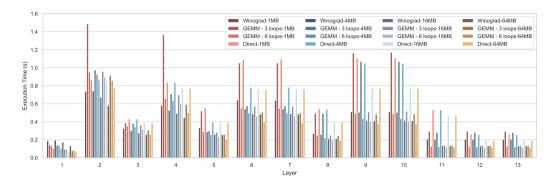

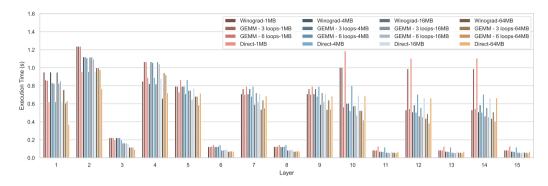

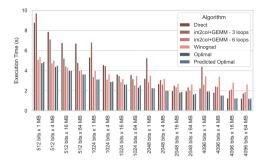

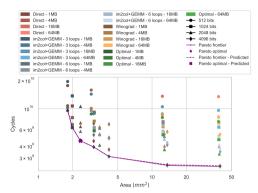

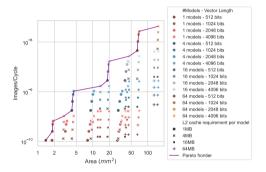

Figure 2.2: Execution time of VGG16 for different vector lengths and L2 cache sizes, when a single algorithm is used for all layers (*Direct*, *im2col+GEMM - 3 loops*, *im2col+GEMM - 6 loops*, *Winograd*), compared against using the *Optimal* algorithm per layer, and using our algorithm selection model to predict the optimal algorithm per layer (*Predicted Optimal*).

and performs better in the case of skinny matrices, i.e., when input/output dimensions are low, but input/output channels are high. Winograd shows better or comparable performance for most layers, except for layers with high input channels. Further, increasing vector lengths from 512-bit to 4096-bit demonstrates that the Direct algorithm shows the maximum scalability of  $2.4\times-5.8\times$  with longer vector lengths and outperforms the other algorithms. The im2col+GEMM algorithm offers better performance for vector lengths higher than 1024-bit for the skinny matrices. Additionally, increasing the L2 cache from 1MB to 64MB showcases the limited scalability of the Winograd algorithm due to its fixed tile size, which does not utilize the larger caches. Both variants of im2col+GEMM show limited scalability beyond 16MB of L2 cache for extremely skinny matrices. On the other hand, the Direct algorithm benefits the most from larger caches.

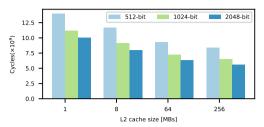

Our evaluation shows that the selection of the convolutional algorithms depends upon the layer's dimensions and hardware microarchitectural parameters. Consequently, it is important to select an optimal algorithm for each convolutional layer based upon the co-design study. In Paper II, we propose a random forest classifier that achieves 92.8% prediction accuracy by considering both convolutional layer dimensions and hardware configuration parameters. Selecting the optimal algorithm improves the execution time by up to  $1.85\times$  compared to always using the Direct algorithm and up to  $1.73\times$  over using the 6-loop implementation of im2col+GEMM in the case of VGG16 as shown in Figure 2.2. For YOLOv3, selecting the optimal algorithm improves the execution time by  $1.33\times$  and  $2.11\times$  over always using the Direct and 6-loop im-

2.2. PAPER II - SUMMARY 11

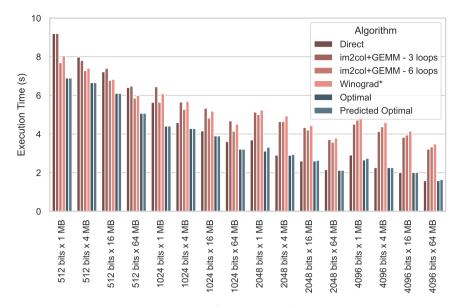

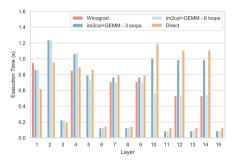

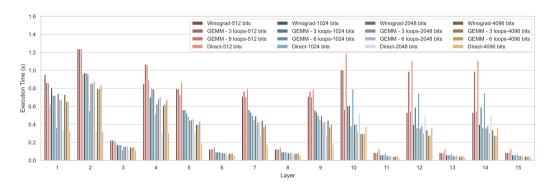

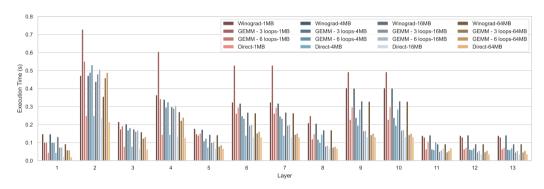

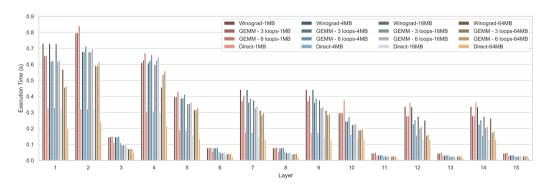

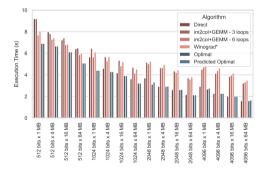

Figure 2.3: Execution time of YOLOv3 (first 15 layers) for different vector lengths and L2 cache sizes, when a single algorithm is used for all layers (*Direct*, *im2col+GEMM* - 3 loops, *im2col+GEMM* - 6 loops, *Winograd\**-uses im2col+GEMM for some layers), compared against using the *Optimal* algorithm per layer, and using our algorithm selection model to predict the optimal algorithm per layer (*Predicted Optimal*).

plementation of im2col+GEMM algorithms, respectively as shown in Figure 2.3. Moreover, our performance-area tradeoffs show that algorithm selection allows for better performance in less area, compared to using a single algorithm for each layer.

### Chapter 3

# Conclusions and Future Work

In this thesis, we present a hardware and software co-design study of CNNs inference with three distinct algorithms, Direct, im2col+GEMM, and Winograd, on modern long vector architectures by considering the architecture's hardware parameters tuning.

This thesis makes the following contributions: Paper 1 concludes that optimizing the algorithms according to the underlying vector architecture is important because not all types of vector architectures benefit from all the optimizations. Manual optimizations on the vector architecture are crucial, as a performance improvement of  $3\times -6\times$  has been observed compared to autovectorization. Paper 1 additionally concludes that tuning the microarchitectural parameters with longer vector lengths, bigger caches, and more vector lanes can improve the performance by  $\sim 5 \times$ . However, the performance gain from very long vectors is limited and additional vector lanes only benefit long vector lengths by hiding the startup overhead and pipeline latency. Moreover, our optimized Winograd algorithm with inter-tile parallelism further improves the performance by  $1.35\times$  and  $1.5\times$  for YOLOv3 and VGG16 network models respectively, while having a lower cache requirement. Paper 2 concludes that the selection of an algorithm per convolutional layer highly depends on the convolutional layer parameters and hardware microarchitectural parameters such as vector lengths and L2 cache sizes. All the algorithms benefit  $\sim 2 \times$ with longer vector lengths (2048-bit) compared to 512-bits. Both algorithms im2col+GEMM and Direct benefit about 1.5× from a larger L2 cache (64MB compared to 1MB), but the Direct can have higher speedups if the vector length is large (4096 bits). Moreover, our study shows that there is no single algorithm that fits all the convolutional layers. Therefore, to select the best algorithm, Paper 2 presents our Random Forest classifier, resulting in an average of 92.8% prediction accuracy, with inference time predictions showing at most 10% relative errors. Furthermore, algorithm selection can boost performance more than 2× compared to using a single algorithm and results in more efficient chips for CNN model serving.

So far, we have focused on the optimization space of algorithms for convolutions and the design space of vector architectures. There are various

opportunities to extend this work. One promising direction is toward vision transformers (ViTs), a deep learning architecture that applies to transformer models, designed for natural level processing, object detection, image classifications, etc. These network models are built with self-attention and feedforward layers, where matrix multiplication is the main kernel, contributing a substantial part of total inference time. However, optimizing ViTs on vector architectures presents several challenges. First, many matrices are skinny and irregular, making it challenging to utilize long vector lengths and optimize them effectively. Second, data movement is substantial as each self-attention layer involves two matrix-matrix multiplications along with one softmax kernel. Therefore, mechanisms like data reuse and fusion are proposed [57] to reduce memory accesses and improve performance.

## **Bibliography**

- [1] K. Li, W. Ma, U. Sajid, Y. Wu, and G. Wang, "Object detection with convolutional neural networks," *CoRR*, vol. abs/1912.01844, 2019. [Online]. Available: http://arxiv.org/abs/1912.01844

- [2] M. M. Lopez and J. Kalita, "Deep learning applied to NLP," CoRR, vol. abs/1703.03091, 2017. [Online]. Available: http://arxiv.org/abs/1703.03091

- [3] D. Palaz, M. Magimai.-Doss, and R. Collobert, "Convolutional neural networks-based continuous speech recognition using raw speech signal," in 2015 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2015, pp. 4295–4299.

- [4] Y. Hu, Y. Liu, and Z. Liu, "A survey on convolutional neural network accelerators: GPU, FPGA and ASIC," in 2022 14th International Conference on Computer Research and Development (ICCRD), 2022, pp. 100–107.

- [5] "Whitepaper GPU-based deep learning inference: A performance and power analysis," 2015.

- [6] L. Wang, Z. Chen, Y. Liu, Y. Wang, L. Zheng, M. Li, and Y. Wang, "A unified optimization approach for cnn model inference on integrated GPUs," 2019.

- [7] K. Abdelouahab, M. Pelcat, J. Serot, and F. Berry, "Accelerating CNN inference on FPGAs: A survey," arXiv preprint arXiv:1806.01683, 2018.

- [8] D. Moolchandani, A. Kumar, and S. R. Sarangi, "Accelerating cnn inference on asics: A survey," *Journal of Systems Architecture*, vol. 113, p. 101887, 2021.

- [9] M. Abadi, "TensorFlow: Large-Scale Machine Learning on Heterogeneous Distributed Systems," 2016.

- [10] Pytorch. Pytorch GPU. [Online]. Available: https://www.run.ai/guides/gpu-deep-learning/pytorch-gpu/

- [11] J. Redmon and A. Farhadi, "YOLOv3: An incremental improvement," arXiv, 2018.

- [12] J. Park, "Deep learning inference in facebook data centers: Characterization, performance optimizations and hardware implications," 2018.

[13] S. Mittal, P. Rajput, and S. Subramoney, "A survey of deep learning on cpus: Opportunities and co-optimizations," *IEEE Transactions on Neural Networks and Learning Systems*, pp. 1–21, 2021.

- [14] Y. Liu, Y. Wang, R. Yu, M. Li, V. Sharma, and Y. Wang, "Optimizing {CNN} model inference on {CPUs}," in 2019 USENIX Annual Technical Conference (USENIX ATC 19), 2019, pp. 1025–1040.

- [15] E. Georganas and Kalamkar, "Tensor processing primitives: a programming abstraction for efficiency and portability in deep learning workloads," in *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*, 2021, pp. 1–14.

- [16] R. Li and Xu, "Analytical characterization and design space exploration for optimization of cnns," in *Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems*, 2021, pp. 928–942.

- [17] T. P. Morgan, "IBM BETS BIG ON NATIVE INFERENCE WITH BIG IRON," *The Next Platform*, August 23, 2021. [Online]. Available: "https://www.nextplatform.com/2021/08/23/ibm-bets-big-on-native-inference-with-big-iron/"

- [18] (2020) V for vector: software exploration of the vector extension of RISC-V. [Online]. Available: https://www.european-processor-initiative.eu/v-for-vector-software-exploration-of-the-vector-extension-of-risc-v/

- [19] N. Stephens, "The arm scalable vector extension," *IEEE Micro*, vol. 37, no. 2, pp. 26–39, 2017.

- [20] Dan Andrei Iliescu, Francesco Petrogalli. Arm scalable vector extension and application to machine learning. [Online]. Available: https://developer.arm.com/solutions/hpc/resources/hpc-white-papers/arm-scalable-vector-extensions-and-application-to-machine-learning

- [21] European Processor Initiative. (2019)V for vector: softexploration of RISC-V. ware vector extension of the https://www.european-processor-initiative.eu/ Available: v-for-vector-software-exploration-of-the-vector-extension-of-risc-v/

- [22] T. Ben-Nun and T. Hoefler, "Demystifying parallel and distributed deep learning: An in-depth concurrency analysis," ACM Comput. Surv., vol. 52, no. 4, aug 2019.

- [23] S. Mittal and S. Vaishay, "A survey of techniques for optimizing deep learning on GPUs," *Journal of Systems Architecture*, vol. 99, p. 101635, 2019. [Online]. Available: https://www.sciencedirect.com/science/article/ pii/S1383762119302656

- [24] S. A. Alam, A. Anderson, B. Barabasz, and D. Gregg, "Winograd convolution for deep neural networks: Efficient point selection," ACM Trans. Embed. Comput. Syst., vol. 21, no. 6, Dec. 2022. [Online]. Available: https://doi.org/10.1145/3524069

[25] M. Mathieu, M. Henaff, and Y. LeCun, "Fast training of convolutional networks through FFTs," 2014.

- [26] Meta Platforms, Inc. Building meta's genai infrastructure. [Online]. Available: https://engineering.fb.com/2024/03/12/data-center-engineering/building-metas-genai-infrastructure/

- [27] Nvidia Corporation. Triton inference server: Architecture: Concurrent model execution. [Online]. Available: https://docs.nvidia.com/deeplearning/triton-inference-server/archives/triton\_inference\_server\_1150/user-guide/docs/architecture.html#concurrent-model-execution

- [28] BentoML. Bentoml docs: Concurrency. [Online]. Available: https://docs.bentoml.com/en/latest/guides/concurrency.html

- [29] M. Sahaya Loui, Z. Azad, L. Delshadtehrani, S. Gupta, P. Warden, V. Reddi, and A. Joshi, "Towards deep learning using tensorflow lite on RISC-V," 06 2019.

- [30] M. Cococcioni, F. Rossi, and E. Ruffaldi, "Fast deep neural networks for image processing using posits and ARM scalable vector extension," *Journal of Real-Time Image Processing*, vol. 17, 06 2020.

- [31] ARM. ARM Compute Library. [Online]. Available: https://github.com/ARM-software/ComputeLibrary

- [32] C. Ramírez, C. A. Hernández, O. Palomar, O. Unsal, M. A. Ramírez, and A. Cristal, "A risc-v simulator and benchmark suite for designing and evaluating vector architectures," *ACM Trans. Archit. Code Optim.*, vol. 17, no. 4, nov 2020. [Online]. Available: https://doi.org/10.1145/3422667

- [33] Y. Kodama, T. Odajima, M. Matsuda, M. Tsuji, J. Lee, and M. Sato, "Preliminary performance evaluation of application kernels using arm sve with multiple vector lengths," in 2017 IEEE International Conference on Cluster Computing (CLUSTER), 2017, pp. 677–684.

- [34] A. Poenaru and S. McIntosh-Smith, "The effects of wide vector operations on processor caches," in 2020 IEEE International Conference on Cluster Computing (CLUSTER), 2020, pp. 531–539.

- [35] P. Wang, W. Yang, J. Fang, D. Dong, C. Huang, P. Zhang, T. Tang, and Z. Wang, "Optimizing direct convolutions on ARM multi-cores," in Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis, ser. SC '23. New York, NY, USA: Association for Computing Machinery, 2023.

- [36] A. d. L. Santana, A. Armejach, and M. Casas, "Efficient direct convolution using long simd instructions," in *Proceedings of the 28th ACM SIGPLAN* Annual Symposium on Principles and Practice of Parallel Programming, ser. PPoPP '23. New York, NY, USA: Association for Computing Machinery, 2023, p. 342–353.

[37] S. Wang, J. Zhu, Q. Wang, C. He, and T. T. Ye, "Customized instruction on risc-v for winograd-based convolution acceleration," in 2021 IEEE 32nd International Conference on Application-specific Systems, Architectures and Processors (ASAP), 2021, pp. 65–68.

- [38] M. F. Dolz, H. Martínez, A. Castelló, P. Alonso-Jordá, and E. S. Quintana-Ortí, "Efficient and portable winograd convolutions for multi-core processors," *The Journal of Supercomputing*, pp. 1–22, 2023.

- [39] R. Espasa, M. Valero, and J. E. Smith, "Vector architectures: Past, present and future," in *Proceedings of the 12th International Conference on Supercomputing*, ser. ICS '98. NY, USA: ACM, 1998, p. 425–432.

- [40] Intel. (2020) Instruction set extensions and future features programming reference. [Online]. Available: https://software.intel.com/content/www/us/en/develop/download/intel-architecture-instruction-set-extensions-programming-reference. html

- [41] ARM, "ARM Neon Programmer's Guide," 2013. [Online]. Available: https://documentation-service.arm.com/static/5f731b591b758617cd95559c?token=

- [42] J. Redmon, "Darknet: Open source neural networks in c," http://pjreddie.com/darknet/, 2013–2016.

- [43] M. Dukhan. (2016) NNPACK. https://github.com/Maratyszcza/ NNPACK.

- [44] V. Kelefouras and G. Keramidas, "Design and implementation of 2d convolution on x86/x64 processors," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 12, pp. 3800–3815, 2022.

- [45] G. Alaejos, A. Castelló, H. Martínez, P. Alonso-Jordá, F. D. Igual, and E. S. Quintana-Ortí, "Micro-kernels for portable and efficient matrix multiplication in deep learning," *The Journal of Supercomputing*, vol. 79, no. 7, pp. 8124–8147, 2023.

- [46] D. Li, D. Huang, Z. Chen, and Y. Lu, "Optimizing massively parallel winograd convolution on arm processor," in *Proceedings of the 50th International Conference on Parallel Processing*, ser. ICPP '21. New York, NY, USA: Association for Computing Machinery, 2021. [Online]. Available: https://doi.org/10.1145/3472456.3472496

- [47] M. F. Dolz, H. Martínez, P. Alonso, and E. S. Quintana-Ortí, "Convolution operators for deep learning inference on the fujitsu a64fx processor," in 2022 IEEE 34th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD), 2022, pp. 1–10.

- [48] M. Jordà, P. Valero-Lara, and A. J. Peña, "Performance evaluation of cudnn convolution algorithms on nvidia volta gpus," *IEEE Access*, vol. 7, pp. 70461–70473, 2019.

[49] R. Xu, S. Ma, and Y. Guo, "Performance analysis of different convolution algorithms in GPU environment," in 2018 IEEE International Conference on Networking, Architecture and Storage (NAS), 2018, pp. 1–10.

- [50] M. F. Dolz, S. Barrachina Mir, H. Martinez, A. Castelló, A. Maciá, G. Fabregat, and A. Tomás, "Performance-energy trade-offs of deep learning convolution algorithms on ARM processors," The Journal of Supercomputing, vol. 79, 01 2023.

- [51] A. Zlateski, Z. Jia, K. Li, and F. Durand, "FFT convolutions are faster than winograd on modern CPUs, here is why," ArXiv, vol. abs/1809.07851, 2018. [Online]. Available: https://api.semanticscholar.org/CorpusID:52339177

- [52] M. F. Dolz, H. Martinez, P. Alonso-Jordá, A. Castelló, and E. S. Quintana-Orti, "Parallel and vectorised winograd convolutions for multi-core processors."

- [53] M. F. Dolz, A. Castelló, and E. S. Quintana-Ortí, "Towards portable realizations of winograd-based convolution with vector intrinsics and openmp," in 2022 30th Euromicro International Conference on Parallel, Distributed and Network-based Processing (PDP), 2022, pp. 39–46.

- [54] Gem5, "Gem5." [Online]. Available: https://gem5.googlesource.com/public/gem5

- [55] S. R. Gupta, N. Papadopoulou, and M. Pericàs, "Challenges and opportunities in the co-design of convolutions and RISC-V Vector Processors," in Proceedings of the SC '23 Workshops of The International Conference on High Performance Computing, Network, Storage, and Analysis, ser. SC-W '23. New York, NY, USA: Association for Computing Machinery, 2023, p. 1550–1556.

- [56] RISC-V Vector. [Online]. Available: https://github.com/riscv/riscv-v-spec/releases

- [57] X. Fu, W. Yang, D. Dong, and X. Su, "Optimizing attention by exploiting data reuse on ARM multi-core CPUs," in *Proceedings of the 38th ACM International Conference on Supercomputing*, ser. ICS '24. New York, NY, USA: Association for Computing Machinery, 2024, p. 137–149. [Online]. Available: https://doi.org/10.1145/3650200.3656620

## Chapter 4

## Paper I

## Accelerating CNN inference on long vector architectures via co-design

Sonia Rani Gupta, Nikela Papadopoulou, and Miquel Pericàs

$Preprint\ from$

$\begin{array}{c} International \ Symposium \ on \ Parallel \ and \ Distributed \ Processing \ (IPDPS), \\ 2023 \end{array}$

22 Chapter 4. Paper 1

### Accelerating CNN inference on long vector architectures via co-design

Sonia Rani Gupta Computer Science and Engineering Chalmers University of Technology Gothenburg, Sweden

Email: soniar@chalmers.se

Nikela Papadopoulou Computer Science and Engineering Chalmers University of Technology Gothenburg, Sweden Email: nikela@chalmers.se

Miquel Pericàs Computer Science and Engineering Chalmers University of Technology Gothenburg, Sweden Email: miquelp@chalmers.se

Abstract-CPU-based inference can be deployed as an alternative to off-chip accelerators. In this context, emerging vector architectures are a promising option, owing to their high efficiency. Yet the large design space of convolutional algorithms and hardware implementations makes the selection of design options challenging. In this paper, we present our ongoing research into co-designing future vector architectures for CPU-based Convolutional Neural Networks (CNN) inference focusing on the im2col+GEMM and Winograd kernels. Using the Gem5 simulator we explore the impact of several hardware microarchitectural features including (i) vector lanes, (ii) vector lengths, (iii) cache sizes, and (iv) options for integrating the vector unit into the CPU pipeline. In the context of im2col+GEMM, we study the impact of several BLIS-like algorithmic optimizations such as (1) utilization of vector registers, (2) loop unrolling, (3) loop reorder, (4) manual vectorization, (5) prefetching, and (6) packing of matrices, on the RISC-V Vector Extension and ARM-SVE ISAs. We use the YOLOv3 and VGG16 network models for our evaluation. Our co-design study shows that BLIS-like optimizations are not beneficial to all types of vector microarchitectures. We additionally demonstrate that longer vector lengths (of at least 8192 bits) and larger caches (of 256MB) can boost performance by 5×, with our optimized CNN kernels, compared to a vector length of 512-bit and 1MB of L2 cache. In the context of Winograd, we present our novel approach of inter-tile parallelization across the input/output channels by using  $8 \times 8$  tiles per channel to vectorize the algorithm on vector length agnostic (VLA) architectures. Our method exploits longer vector lengths and offers high memory reuse, resulting in performance improvement of up to 2.4× for non-strided convolutional layers with 3×3 kernel size, compared to our optimized im2col+GEMM approach on the Fujitsu A64FX processor. Our co-design study furthermore reveals that Winograd requires smaller cache sizes (up to 64MB) compared to im2col+GEMM.

Index Terms—CNNs, GEMM, Winograd, long vector architectures, vector-length agnostic ISAs, co-design, optimizations

### I. INTRODUCTION

Inference via Convolutional Neural Networks (CNNs) is used in many Artificial Intelligence applications such as object detection [1], natural language processing [2] and speech recognition [3]. Most CNN-based object detection network models work with a tight response-time limit and have high and increasing computation costs [4]-[6]. Additionally, these models often operate under tight power constraints, e.g. battery power in embedded systems [7], or power caps in datacenters [8]. Therefore, highly accurate real-time CNNs require highly optimized kernels, running on energy-efficient architectures with large computational capacity.

The popular approach for CNN inference, adopted by many frameworks [6], [9], [10] is to offload the compute-intensive kernels to GPUs [11]-[13]. Specialized neural accelerators also exist [14], [15], but their integration in the generalpurpose computing stack is challenging. Nevertheless, many use cases require availability, low-latency, or portability [16]-[18], and therefore benefit from executing deep neural networks (DNNs) on tightly integrated systems. Consequently, many works target software optimization of CNN inference on CPUs [18]-[20], while CPU vendors increasingly add DNN capabilities to processors [21].

In this aspect, vector processors play a leading role [22]. Contemporary vector architectures, such as ARM-SVE [23] and the RISC-V Vector extension (RISC-VV) [24] specify a maximum length of vector registers and allow the usage of different vector lengths. These vector-length agnostic (VLA) Instruction Set Architecture (ISAs) facilitate code portability across iterations of the same machine with different vector lengths.

The effectiveness of vector processors depends on algorithmic optimizations and the hardware design. First, given the limited compiler's ability to perform transformations during auto-vectorization [25], manual transformations and optimizations to expose the available SIMD parallelism to the vector processing units are key to achieving high performance on vector architectures. Second, modern architectures can combine very long vector units, more on-chip vector parallelism and large caches. Tuning the micro-architectural parameters to the requirements of the vectorized and optimized kernels is integral to the design of high-performing, efficient vector architectures.

Existing work on CNN inference on vector architectures focuses either on applying algorithmic optimizations [26]–[29] or on tuning the hardware micro-architectural parameters [30]-[32]. We identify the absence of a combined study as a missed opportunity to uncover algorithmic and architectural tradeoffs in the performance of CNN kernels running on vector architectures. In this work, we bridge this gap with a codesign study that performs a joint exploration of the design space of vector architectures and the optimization space of CNNs, aiming to provide guidance to programmers, hardware designers, and compiler developers.

This paper studies the interplay between algorithmic optimizations and micro-architectural parameter choices, demonstrating the trade-offs in co-designing CNNs and vector architectures. For our co-design study, we vectorize all the kernels of the convolutional layer from the Darknet framework [6] on the RISC-VV and ARM-SVE architectures, using highlevel intrinsics of the respective ISAs. We then optimize GEMM, the most time-consuming kernel, using various BLISlike [33] techniques to reduce the pressure on the memorysubsystem, enforce contiguous memory accesses, and maximize the utilization of vector registers. We additionally optimize the Winograd algorithm from NNPACK [34], with VLA vectorization on ARM-SVE, proposing a novel, inter-tile parallelism scheme. We then use the gem5 [35] simulator to assess the impact of tuning hardware parameters such as vector lengths, vector lanes and L2 cache sizes, on the optimized kernels. We consequently also assess the impact of integrating vector units tightly to the core, in the case of ARM-SVE, or as a decoupled vector architecture, in the case of RISC-VV. Finally, we evaluate the performance of Winograd as an algorithmic replacement for im2col+GEMM.

In summary, we make the following contributions:

- We demonstrate that not all algorithmic optimizations are beneficial to all different vector architectures, due to traits of their micro-architectural design. To the best of our knowledge, this is the first work that shows the impact of different algorithmic optimizations with CNN kernels on the ARM-SVE and RISC-VV ISAs.

- 2) We characterize the impact of hardware parameters on convolutional layers with im2col+GEMM, showing that longer vectors can improve the performance by up to 2.5×, and larger caches can further improve performance by up to 1.9× (i.e., a total of almost 5×), when compared to a 512-bit long vector architecture with 1MB of L2 cache.

- 3) We present a novel, vectorized implementation of Winograd with ARM-SVE in a VLA manner, offering up to 1.35× and 1.5× higher performance with the YOLOv3 and VGG16 network models respectively, compared to im2col+GEMM, on a single core of A64FX. To the best of our knowledge, this is the first implementation of Winograd utilizing long vectors (up to 2048 bits). Moreover, our co-design study on ARM-SVE shows that Winograd is less sensitive to the L2 cache size compared to im2col+GEMM.

The rest of this paper is organized as follows. Section II offers background on vector architectures and CNNs. Section III presents our experimental platforms and setup. Section IV describes the algorithmic transformations and optimizations on the most-time consuming kernels of the convolutional layer, namely im2col+gemm and Winograd. Section V details the hardware parameters we consider in our co-design study. Section VI presents our co-design study on the RISC-VV and ARM-SVE architectures. Section VII evaluates the Winograd kernel and Section IX concludes the paper.

### II. BACKGROUND

### A. Vector Architectures

Although long vector lengths were used in supercomputers in the past [36], and short vectors later became popular

in general-purpose architectures [37], [38], the high energy efficiency and scalable vector length of vector architectures have led to renewed interest in High-Performance Computing. While SIMD instruction set architectures with a fixed short vector length are available and commonly used for general purpose computing, introducing longer vector lengths requires a new ISA extension, limiting portability. To overcome this limitation, modern architectures such as RISC-VV [39] and ARM-SVE [23] offer vector length agnostic (VLA) ISAs that are portable across different hardware vector lengths.

a) RISC-V Vector Extension (RISC-VV): This is the vector extension of the RISC-V Architecture, with 32 vector registers and a maximum supported vector length (MVL) of 16384 bits. Different vector lengths (vlen) in powers of two, not exceeding the MVL (maximum vector length), can be used. A vector instruction vsetvl determines the granted vector length (gvl) at runtime, using the requested vector length (rvl) in elements and the element width in bits (sew) as input. RISC-VV also supports strided-access, gather-load and scatter-store vector operations.

b) ARM Scalable Vector Extension (ARM-SVE): This is the vector extension of the ARMv8 architecture. The ARM-SVE ISA operates on 32 vector registers and 16 predicate registers. The supported MVL is 2048 bits, allowing to use different vector lengths at runtime, from 128-bit to 2048-bit in increments of 128-bits. Predicate registers are used for per-lane predication, where elements with active lanes get processed and inactive lanes either update the destination or leave the destination unchanged. For the scalar loop tail, ARM-SVE uses loop predication by masking out vector elements and by processing partial vectors. ARM-SVE also provides gatherload and scatter-store vector instructions.

### B. Convolutional network models

Convolutional neural networks are implemented in multiple deep learning frameworks. In this work, we focus on Darknet [40], an open-source neural network framework written in C and CUDA. It supports many pre-trained convolutional network models for inference in various applications, such as object detection and image classification. These network models consist of different types of layers, but the computationally dominant layer is the convolutional layer. In Darknet, a convolutional layer is built from the functions GEMM, im2col, fill\_cpu, copy\_cpu, normalize\_cpu, add\_bias, scale\_bias and activate\_array.

- a) CNNs for object detection and image classification: A popular CNN for object detection is YOLOv3, which features 107 layers of five different types, out of which 75 layers are convolutional. A variant for the same task is YOLOv3-tiny, which features 23 layers, out of which 13 are convolutional. VGG16 is an image classification CNN. VGG16 includes 25 layers, out of which 13 are convolutional and 3 are fully-connected layers. The fully connected layers also use compute intensive kernels similar to convolutional layers.

- b) Execution time breakdown for CNN inference: We profile the execution time of different kernels in the YOLOv3

TABLE I: Hardware Platforms

|                 | RISC-VV        | ARM-SVE          | A64FX            |

|-----------------|----------------|------------------|------------------|

|                 | @gem5          | @gem5            |                  |

| ISA             | RISC-VV v0.8   | ARM v8.2+sve     | ARM v8.2+sve     |

| Processor       | in-order       | in-order         | out-of-order     |

| Clock Rate      | 2GHz           | 2GHz             | 2GHz             |

| L1 Cache size   | 64kB, 4-way    | 64kB,4-way       | 64kB,4-way       |

| L2 Cache size   | 1MB, 8-way     | 1MB, 8way        | 8-MB, 16-way     |

| Cache line size | 64B            | 64B              | 256B             |

| Prefetching     | No             | No               | Yes              |

| Vector Length   | upto 16384-bit | up to 2048-bit   | 512-bit          |

| Vector Lanes    | upto 8         | proportional     | not configurable |

|                 |                | to vector length |                  |

network model, compiled with clang on the A64FX system (see Section III for details) and collect measurements using Linux perf. Approximately 92% of the total execution time is spent on computation for inference, while the remaining 8% is used for setting up the network model. We exclude the time for setup, as it occurs only once, and calculate the percentage of time spent on each kernel with respect to the total computation time. The convolutional layer dominates execution, with GEMM consuming 93.4% of the computation time.

c) Convolutional layer implementations: Our profiling results show that the convolutional layer is the main building block of CNN network models. In Darknet, this layer is implemented using the im2col+GEMM algorithm, which is also the dominant kernel. We focus on the optimization of the generic im2col+GEMM algorithm, however, a convolutional layer can be implemented with multiple algorithms, as no "one-size-fits-all" strategy exists [41]: Winograd [42] works best with convolutional layers with 3×3 or 5×5 kernel sizes [43], FFT works best for layers with large kernel sizes, while the Direct algorithm is better for 1×1 kernels. We therefore also optimize the Winograd algorithm of the NNPACK [34] package implementation, as in CNN-based network models most of the network models have convolutional layers with kernel sizes of 1×1, 3×3 or 5×5 [44].

### III. METHODOLOGY

### A. Hardware platforms

Our experimental analysis focuses on the RISC-VV and ARM-SVE architectures. For the exploration of hardware parameters, we simulate both architectures with gem5 [35], a cycle-accurate simulator that models the core pipeline, providing accurate timing predictions. For ARM-SVE, we use the Fujitsu A64FX processor that implements the ARMv8-SVE architecture, to evaluate our algorithmic optimizations.

The specifics of the hardware platforms used for our experiments are described in Table I. We note that A64FX has 2 SIMD units, and the vector lengths are not reconfigurable, as this is an actual processor. We use a RISC-V fork of gem5 [30] and the public version of the gem5 simulator [45] with support for modeling vector architectures, for RISC-VV and ARM-SVE, respectively, in system call emulation (SE) mode. We configure gem5 with the in-order "MinorCPU" CPU model, with a frequency of 2GHz for the CPU and vector processor unit (VPU). The memory subsystem is configured with two

levels of the data cache. We note that in RISC-VV@gem5, the VPU is connected to the L2 cache. A small VectorCache buffer of 2KB is used, through which the VPU reads and writes data from/to the L2 cache. However, on ARM-SVE@gem5, data for vector registers is accessed through the L1 cache itself.

### B. Experimental setup

We evaluate the YOLOv3 network models from the Darknet framework on a 768  $\times$  576 pixels input image. To compile the models, we use the EPI fork of the LLVM clang [46] cross-compiler v12.0.0 for RISC-VV, LLVM armclang v20.3 [47] for ARM-SVE@A64FX, and GCC cross-compiler version 10.2 for ARM-SVE@gem5. For both RISC-VV and ARM-SVE, we use the -03 optimization flag. To collect baseline results, we use the -fno-vectorize compiler flag in both compilers. Note that the baseline implementation of the network models in Darknet does not include any manual vectorization. The versions of Darknet with our vectorized and optimized kernel implementations for ARM-SVE and RISC-VV are open-source and publicly available  $^{1}$   $^{2}$ .

To analyze the impact of the vector lengths, we vary the vector lengths in both simulated architectures from 512 bits up to 2048 bits on ARM-SVE and up to 16384 bits on RISC-VV, in powers of 2. To analyze the impact of on-chip parallelism on RISC-VV, we vary the number of vector lanes from 2 up to 8. To analyze the impact of cache parameters, we increase the L2 cache size on both simulated architectures from 1MB up to 256MB. We calculate the L2 cache latency using the latency of AMD Zen2 L2 [48] (12 cycles @ 7nm tech) and extrapolating it to a cache size of 1MB, using the CACTI tool [49], resulting in a latency of 12 cycles.

To collect time measurements, we perform 100 repetitions for all experiments on A64FX, ensuring that the 95% confidence interval of the mean falls within 5% of the mean.

### IV. ALGORITHMIC OPTIMIZATIONS

In this section, we focus on the algorithmic optimizations for im2col+GEMM for the convolutional layer. We additionally describe the optimization of the Winograd implementation of convolutional layers.

### A. im2col+GEMM optimizations

To maximize the attainable performance, we begin by vectorizing all kernels of the convolutional layer in Darknet with low-level intrinsic instructions of the respective ISAs on each of our experimental platforms. However, as discussed in Section II, GEMM is the most time consuming kernel, and aside from vectorization, manual optimizations are necessary to extract the maximum parallelism out of im2col+GEMM.

Assuming a convolutional layer with a  $k \times k$  kernel size, on an input image of dimensions  $h \times w \times c$ , where h, w, c are the height, width, and number of channels respectively, for n number of filters, GEMM takes as input a weight matrix  $M \times K$ , and an input matrix  $K \times N$ , where M = n,  $K = k \times k \times c$ , and  $N = h \times w$ .

<sup>1</sup>https://github.com/chalmers-hart/Darknet-ARM-SVE.git

<sup>&</sup>lt;sup>2</sup>https://github.com/chalmers-hart/Darknet-RISCVV.git

```

2: for i \leftarrow 0, i < M, i + + do

3.

4.

tmp = alpha * A[i, k]

5:

for i \leftarrow 0, i < N, i+=1 do

6:

C[i,j] += tmp * B[k,j]

7.

end for

8:

end for

9: end for

Fig. 1: Naive implementation of GEMM

1: i \leftarrow 0 , j \leftarrow 0, k \leftarrow 0

2: long int gvl;

3: for j \leftarrow 0, j < N do

gvl \leftarrow vsetvl(N-j) //compute 'granted vector length' for i \leftarrow 0, \ i < M, \ i+=U do //U is unrollfactor

4.

5:

VC[i:i+U] \leftarrow C[i:i+U,j:j+gvl]

6.

7:

for k \leftarrow 0, k < K, k++ do

8:

VB \leftarrow B[k, j: j + gvl]

Q.

for it \leftarrow 0, it < U, it + + do

10:

tmp = alpha \times A[it, k]

11.

Vtmp \leftarrow tmp //broadcast

VC[it] \leftarrow vfmacc (VC[it],Vtmp, VB, qvl)

12:

13.

end for

14:

end for

C[i:i+U,j:j+gvl] \leftarrow VC[i:i+U]

15:

16.

end for

17:

j+=gvl

18: end for

Fig. 2: Optimized 3-loop implementation of GEMM

```

1:  $i \leftarrow 0$  ,  $j \leftarrow 0$ ,  $k \leftarrow 0$

Fig. 1 shows the pseudocode for the naive implementation of GEMM ( $C = alpha \cdot A \cdot B + beta \cdot C$ ), as implemented in Darknet. In the pseudo code,  $A \ (M \times K)$  represents the weight matrix,  $B \ (K \times N)$  represents the input matrix and  $C \ (M \times N)$  represents the output matrix.

To optimize GEMM, we follow two approaches. The first approach optimizes the *3-loop implementation*, depicted in Fig. 2. The second approach tiles the matrices, resulting in a *6-loop implementation* depicted in Fig. 3, where we apply optimizations.

We apply the following optimization to the 3-loop implementation: i) vectorization with intrinsic instructions ii) contiguous memory loads/stores to/from vector registers, iii) loop reorder, and iv) loop unrolling. Loop reordering reduces the pressure on the memory subsystem by maximizing the reuse of the vector registers. Loop unrolling hides the pipeline latency by maximizing the vector register utilization and increasing the parallelism in the algorithm.

Figure 2 shows the pseudocode for the optimized 3-loop implementation of the GEMM kernel. In this algorithm, we use the jik loop order, and we unroll the intermediate loop j to reuse the vector data of matrix B by performing U (unrollfactor) times dot products with different A matrix elements. The loop in line 3 is incremented by the vector length gvl to take advantage of VLA and the loop in line 5 is incremented by U to take advantage of loop unrolling. Loops are reordered to reuse the loaded vector data as much as possible. Low level intrinsics are used to manually vectorize the algorithm. For RISC-VV, the vector length is calculated

```

1: i \leftarrow 0, j \leftarrow 0, k \leftarrow 0

2: long int qvl;

3: for j1 \leftarrow 0, j1 < N, j1+=blockN do

4.

for k1 \leftarrow 0, k1 < K, k1+=blockK do

5:

Pack MatrixB

for i1 \leftarrow 0, i1 < M, i1+=blockM do

7:

Pack MatrixA

8:

for j \leftarrow 0, j < blockN, do

gvl \leftarrow vsetvl(blockN - j)

10.

for i \leftarrow 0, i < blockM, i + = U do

Prefetch block of C matrix into L1 cache

11.

Prefetch packedA matrix into L2 cache

12.

Prefetch packedB matrix into L2 cache

13.

VC[i:i+U] \leftarrow C[i:i+U,j:j+gvl]

14.

15:

for k \leftarrow 0, k < blockK, k + + do

Prefetch packed B matrix into L1 cache

16.

17:

Prefetch packed A matrix into L1 cache

VB \leftarrow packedB[k, j: j + gvl]

18.

for it \leftarrow 0, it < U, it + + \mathbf{do}

19.

tmp = alpha \times packedA[it, k]

20:

21.

Vtmp \leftarrow tmp //broadcast

22:

VC[it] \leftarrow vfmacc (VC[it], Vtmp, VB, qvl)

23.

end for

24:

25:

C[i:i+U,j:j+gvl] \leftarrow VC[i:i+U]

26.

end for

27:

j+=gvl

28.

end for

29:

end for

30:

end for

31: end for