THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Novel Approaches for Thermal and Electrical Characterization of GaN HEMTs

JOHAN BREMER

Microwave Electronics Laboratory Department of Microtechnology and Nanoscience – MC2 Chalmers University of Technology Göteborg, Sweden, 2025 Novel Approaches for Thermal and Electrical Characterization of GaN HEMTs

JOHAN BREMER

$\ensuremath{\textcircled{O}}$  Johan Bremer, 2025

Chalmers University of Technology Department of Microtechnology and Nanoscience – MC2 Microwave Electronics Laboratory SE-412 96 Göteborg, Sweden + 46 (0) 31-772 1000

ISBN 978-91-8103-182-9 Doktorsavhandlingar vid Chalmers tekniska högskola, Ny serie nr 5640 ISSN 0346-718X

Printed by Chalmers digitaltryck Göteborg, Sweden 2025

## Abstract

The evaluation of microwave components requires detailed knowledge of different performance aspects, and component models must be extracted from highly accurate characteristics. However, heating and trapping effects in active components create multifaceted characteristics with complex behavior. This creates major measurement challenges and can cause established measurement methods to yield inaccurate and inadequate information. This thesis outlines solutions to problems faced in the characterization of GaN-based devices and circuits by introducing new measurement techniques capable of capturing complex characteristics and mitigating distortion due to trapping effects.

A new method to perform the  $I_{ds}$ - $V_{ds}$  characterization is shown, which minimizes trap-related memory effects by controlling the ordering of the bias points in the sweep. This allows extracting rudimentary IV properties, and facilitates studying the effects of trapping and heating separately. In addition, a method for electric-based thermal evaluation of GaN semiconductor technologies is outlined, where trap-related distortion in the thermal resistance is suppressed, which facilitates the comparison of thermal properties of different devices. A method to electrically characterize the lateral heat spread is also introduced, by utilizing the HEMT temperature characteristics to design a thermal sensor suitable for integration into GaN MMICs. This enables the use of standard electrical test equipment to measure lateral thermal coupling in packaged circuits. Thermal compensation is explored using a new biasing technique to compensate for thermal performance degradation in an LNA, in which the gate- and drain-voltage dependencies of the RF performance are utilized to maintain a constant gain as the temperature increases. Lastly, GaN HEMT breakdown measurements and characteristics are examined, and a method for RF breakdown characterization is introduced. This allows studying the breakdown at different signal conditions, and comparisons show that the breakdown voltage increases with frequency, which demonstrates the need to evaluate devices under application-relevant conditions. Overall, the proposed methods in this thesis enable more comprehensive and accurate assessments of thermal and electrical device properties, which is crucial in the development of new devices and circuits.

**Keywords:** AlGaN/GaN, breakdown, characterization, HEMT, measurement, thermal coupling, thermal effects, thermal resistance, trapping effects

## List of Publications

### **Appended Publications**

This thesis is based on the content in the following papers:

- [A] J. Bremer, N. Rorsman, and M. Thorsell, "Method for Suppressing Trap-Related Memory Effects in IV Characterizations of GaN HEMTs," *IEEE 36th International Conference on Microelectronic Test Structures*, Edinburgh, United Kingdom, April, 2024.

- [B] J. Bremer, D. Chen, A. Malko, M. Madel, N. Rorsman, S. Gunnarsson, K. Andersson, T. Nilsson, P. Raad, P. Komarov, T. Sandy, and M. Thorsell, "Electric-Based Thermal Characterization of GaN Technologies Affected by Trapping Effects," *IEEE Transactions on Electron Devices*, vol. 67, no. 5, pp. 1952-1958, May, 2020.

- [C] J. Bremer, J. Bergsten, L. Hanning, T. Nilsson, N. Rorsman, S. Gustafsson A. M. Eriksson, and M. Thorsell, "Analysis of Lateral Thermal Coupling for GaN MMIC Technologies," *IEEE Transactions on Microwave Theory* and Techniques, vol. 66, no. 10, pp. 4430-4438, October, 2018.

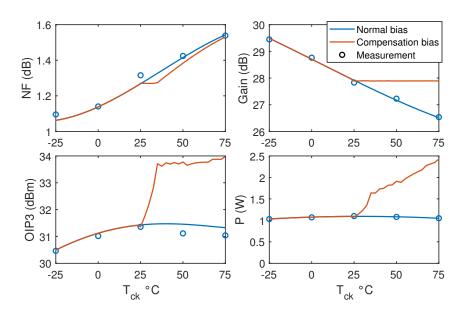

- [D] J. Bremer, L. Hanning, N. Rorsman, and M. Thorsell, "Compensation of Performance Degradation Due to Thermal Effects in GaN LNA Using Dynamic Bias," 48th European Microwave Conference, Madrid, Spain, Sept., 2018.

- [E] J. Bremer, B. Hult, N. Rorsman, and M. Thorsell, "Static and Dynamic Breakdown Characteristics of Microwave GaN HEMTs," to be submitted to IEEE Transactions on Electron Devices, 2025.

### Other Publications

The content of the following papers partially overlaps with the appended papers or is out of the scope of this thesis.

- [a] L. Hanning, J. Bremer, M. Ström, N. Billström, T. Eriksson, and M. Thorsell, "Optimizing the Signal-to-Noise and Distortion Ratio of a GaN LNA using Dynamic Bias," 91st ARFTG Microwave Measurement Conference, Philadelphia, PA, USA, June, 2018.

- [b] T. Kristensen, T. M. J. Nilsson, A. Divinyi, J. Bremer, and M. Thorsell, "Numerical Modeling of Dynamic Thermal Coupling in GaN HEMTs Calibrated by Transient Measurements," *IEEE Transactions on Electron Devices*, vol. 71, no. 12, pp. 7343-7349, Dec. 2024.

- [c] T. Kristensen, T. M. J. Nilsson, A. Divinyi, J. Bremer and M. Thorsell, "Dynamic Thermal Coupling in GaN MMIC Power Amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 73, no. 1, pp. 38-44, Jan. 2025.

# Abbreviations & Notations

| ALC: NI                          | A.1. · · · 11· · · · 1                           |

|----------------------------------|--------------------------------------------------|

| AlGaN                            | Aluminium gallium nitride                        |

| AlN                              | Aluminium nitride                                |

| BV                               | Breakdown voltage                                |

| CTE                              | Coefficient of thermal expansion                 |

| DUT                              | Device under test                                |

| FET                              | Field-effect transistor                          |

| $\operatorname{GaN}$             | Gallium nitride                                  |

| GaAs                             | Gallium arsenide                                 |

| GRT                              | Gate resistance thermometry                      |

| HEMT                             | High electron mobility transistor                |

| LNA                              | Low noise amplifier                              |

| MTTF                             | Mean time-to-failure                             |

| MMIC                             | Monolithic microwave integrated circuit          |

| NF                               | Noise figure                                     |

| OIP3                             | Output third order intercept point               |

| P1dB                             | 1 dB compression point                           |

| $\operatorname{RF}$              | Radio frequency                                  |

| $\operatorname{SiC}$             | Silicon Carbide                                  |

| SMU                              | Source measurement unit                          |

| TIM                              | Thermal interface material                       |

| TBR                              | Thermal boundary resistance                      |

| $\mathrm{TR}$                    | Thermoreflectance                                |

| TCAD                             | Technology computer-aided design                 |

| ТВ                               | Thin buffer                                      |

| 2DEG                             | Two-dimensional electron gas                     |

| $BV_{ds}$                        | Drain-source breakdown voltage                   |

| $\alpha$                         | Thermal coefficient                              |

| L                                | Contact separation                               |

| $\overline{W}$                   | Device width                                     |

| $\mu$                            | Electron mobility                                |

| $\widetilde{C}_{	ext{th}}$       | Thermal capacitance                              |

| E                                | Electric field                                   |

| $G_{ m ii}$                      | Carrier generation rate due to impact ionization |

| I                                | Current                                          |

| I<br>I <sub>d</sub>              | Drain current                                    |

| I <sub>d</sub><br>I <sub>g</sub> | Gate current                                     |

| Ig<br>Is                         | Source current                                   |

| 1 <sub>S</sub>                   |                                                  |

| $I_{\rm ds}$                                                     | Drain-source current          |

|------------------------------------------------------------------|-------------------------------|

| $I_{ m ds,max}$                                                  | Maximum drain-source current  |

| $n_{\rm s}$                                                      | Electron density              |

| $\tilde{P}$                                                      | Power dissipation             |

| $R_{ m on}$                                                      | On-resistance                 |

| $R_{ m th}$                                                      | Thermal resistance            |

| R                                                                | Differential resistance       |

| $R_{ m in}$                                                      | Differential input resistance |

| $R_{ m pd}$                                                      | Drain protection resistor     |

| $T_{\rm ck}$                                                     | Thermal chuck temperature     |

| $T_{\rm c}$                                                      | Average channel temperature   |

| $t_{ m d}$                                                       | Propagation delay             |

| $t_{ m dm}$                                                      | Measurement delay time        |

| V                                                                | Voltage                       |

| $V_{\rm gs}$                                                     | Gate-source voltage           |

| $V_{ m ds}$                                                      | Drain-source voltage          |

| $V_{ m ds,max}$                                                  | Maximum drain-source voltage  |

| $V_{ m gs,max}$                                                  | Maximum gate-source voltage   |

| $V_{\rm gs,min}$                                                 | Minimum gate-source voltage   |

| $V_{ m d}$                                                       | Drain voltage                 |

| $V_{ m po}$                                                      | Pinch-off voltage             |

| $V_{ m dg}$                                                      | Drain-gate voltage            |

| $V_{ m knee}$                                                    | Knee voltage                  |

| $Y_{\rm in}^{\rm e}$                                             | Extrinsic input admittance    |

| $egin{array}{l} Y^{ m e}_{ m in} \ Y^{ m i}_{ m in} \end{array}$ | Intrinsic input admittance    |

| $Z_{ m th}$                                                      | Thermal impedance             |

| $Z_{ m in}$                                                      | Input impedance               |

## Contents

| Ał | bstract                                                                                                                                                                      | iii                               |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Li | st of Publications                                                                                                                                                           | $\mathbf{v}$                      |

| Ał | bbreviations & Notations                                                                                                                                                     | vii                               |

| 1  | I Introduction                                                                                                                                                               |                                   |

| 2  | Key Aspects of GaN HEMT Technology2.1Device Structure and Functionality2.2Dispersive Effects                                                                                 | <b>7</b><br>7<br>12               |

| 3  | Measurement-Based Mitigation of Trap-Effects3.1Trapping Effects in IV Characteristics3.2Trap-Effects Suppression in IV Measurements3.3Reliable Thermal Resistance Extraction | <b>15</b><br>16<br>18<br>20       |

| 4  | Thermal Characterization and Management4.1Temperature Measurement Methods                                                                                                    | <b>25</b><br>26<br>32<br>33<br>36 |

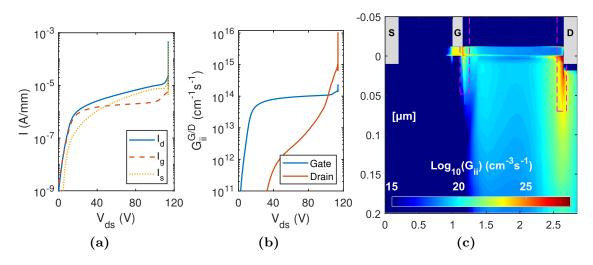

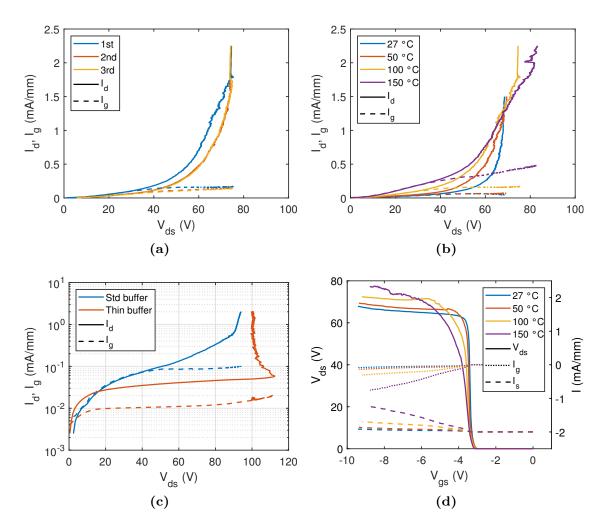

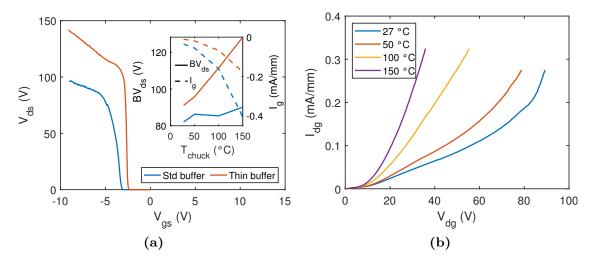

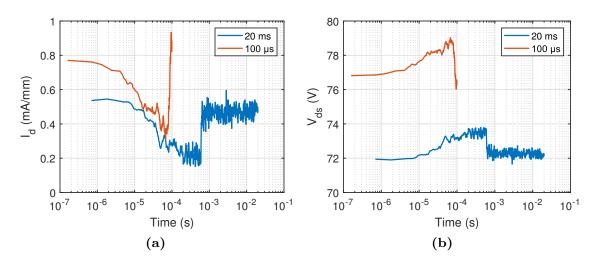

| 5  | Breakdown Characterizations5.1DC Breakdown Measurements5.2Dynamic Breakdown Measurements                                                                                     | <b>41</b><br>43<br>47             |

| 6  | 6 Conclusions and Future Work                                                                                                                                                |                                   |

| Ac | cknowledgments                                                                                                                                                               | <b>53</b>                         |

| Bi | Bibliography                                                                                                                                                                 |                                   |

# Chapter 1 Introduction

Gallium nitride (GaN)-based high electron mobility transistors (HEMTs) is a transistor technology that possesses many of the intrinsic properties necessary to fabricate high-performance electronic circuits at a broad range of frequencies. As a result, GaN technology is today increasingly used in industry sectors such as defense, aerospace, telecom infrastructure, and power electronics, to meet the increasing performance demands on the applications in these sectors.

Power electronic applications such as switching converters need to be efficient, have high power handling capability, and must be manufacturable at a low cost. Applications such as power supplies also need to be able to operate safely over a long period of time. A high switching frequency enables the use of smaller transformers and filter components, which reduces the size, weight, and cost of converters. However, a higher switching frequency increases the switching losses and transistors with high switching speeds are therefore attractive. In addition, the transistor needs a high breakdown voltage and low on-resistance to meet the requirements on efficiency and voltage conversion.

In wireless communication systems, the demands on capacity, data rate, latency, and reduced power consumption are constantly increasing. To achieve multi-gigabit per second speeds and ultra-low latency, mobile operators must improve the performance of the systems through investments in spectrum acquisitioning, network infrastructure, and transmission technologies. The system performance is largely determined by the equivalent isotropic radiated power (EIRP) of base stations. A higher EIRP needs to be achieved without increasing the non-radiated power, which put high demands on the semiconductor technologies used for the power amplifiers in the transmitters. In 5G systems, multiple-input multiple-output (MIMO) technology is used to increase performance and capacity, and the size of the MIMO antenna arrays strongly influences the cost for base stations. To further increase the system capacity, a higher bandwidth is needed, which makes it necessary to design the systems at higher mm-wave frequencies. Advanced 5G systems are designed to operate at frequencies up to 86 GHz and future systems, including backhaul infrastructure, will possibly operate in the sub-THz region [1, 2].

In the defense sector, systems often require highly reliable and rugged components with RF output power levels in the order of kilowatts. The complex communication environment requires complex modulation schemes and

transmissions occur over multiple channels over a wide spectrum, creating a need for wideband components. Several applications migrate away from traveling wave tube amplifiers to solid-state power amplifiers due to the advantages in voltage power supply requirements, noise figures, energy costs, availability, and instant-on capability. In radars, actively electronically scanned array (AESA) architectures are increasingly used as an alternative to more traditional mechanical-based systems. AESA systems require high power, small form factors, and need to be able to operate reliably at high temperatures. The requirements on size, weight, power, and cost are high in air and space-based systems, where the space and load capacity is limited. Receivers need high sensitivity, to detect weak signals but must also be robust to withstand large input signals without losing any sense/detection capabilities. The RF output power needs to be maximized to increase the range as well as to improve the capability to detect objects with small electric signatures. The requirements are similar for electronic warfare systems such as radar warners and jammer systems, which must be functional in harsh electromagnetic environments, as well as be small and light to be portable and integrable. Satellite communication systems share many of the requirements of defense applications. In these systems, demands for smaller satellites, portables, and mobile satcom devices drives the need for more compact, lightweight components with lower power consumption. Furthermore, high output power and wide bandwidth is needed to transmit large amounts of data over the long distances associated with satellite communication.

For any industry application, high reliability is desirable since it translates to a long application lifetime and the ability of the application to function at elevated temperatures for shorter times. All applications therefore strive for semiconductors with higher reliability, better heat removal, and higher efficiency, which reduces the temperature as well as the cost for operating the application. To meet the challenges in the different industry sectors, microwave and power electronics continuously need to be developed. In this context, the beneficial intrinsic properties of GaN HEMTs can be utilized.

#### Implications of Intrinsic GaN HEMT Properties

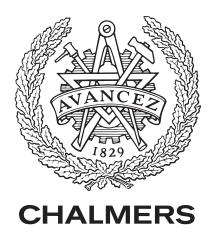

The advantages of GaN HEMTs stem from the large bandgap of GaN (3.4 eV) as well as the ability of GaN to form heterostructures with high electron mobility (> 2000 cm<sup>2</sup>/Vs), large electron sheet density (> 1 × 10<sup>13</sup> cm<sup>2</sup>), and high electron velocity (2 × 10<sup>7</sup> cm/s). A comparison of transistor material properties is shown in Fig. 1.1a, where the area of the polygon is a measure of the performance of the technology. The area of GaN is significantly larger than e.g. Si, meaning GaN can be used to fabricate circuits with higher performance.

The large bandgap enables a high breakdown voltage, which makes it possible to fabricate devices that can operate at high voltages. This increases the device robustness, enables large voltage handling, and increases circuit efficiency since the current in conductors can be reduced. In addition, the high electron mobility and large sheet density enable a high current density and a low on-resistance. As a result, GaN devices are attractive for power electronics since the devices can achieve low on-resistance (<  $4.5 \,\mathrm{m\Omega cm^2}$ ) for breakdown voltages up to 2 kV [3].

Figure 1.1: (a): comparison of device material properties. (b): typical MTTF versus channel temperature for GaN and GaAs-based devices.

The high current density and primarily the large bandgap make it possible for GaN devices to output high power densities. As a result, the devices and circuits can be made smaller. The array-size in wireless base stations as well as the form factor in defense and other commercial applications can therefore be reduced to save cost and weight. A higher power density also enables smaller losses in power combining circuits since more compact networks can be used due to the need of fewer and smaller devices. Furthermore, the power density enables more flexibility to control the port impedances of the device, which enables the design of matching networks with lower loss. Reduced losses lead to a higher efficiency, reliability, gain, and power for GaN-based circuits.

An additional benefit of high power density is the possibility to reduce the parasitic capacitances of the HEMTs since the capacitances scale with the size of the device. The parasitic capacitances degrade the high-frequency performance of the device and GaN-based HEMTs therefore exhibit less degradation at higher frequencies. Furthermore, the high electron velocity of GaN HEMTs is a key factor that enables high frequency performance, and  $f_{\rm T}$  and  $f_{\rm max}$  values over 400 GHz have been demonstrated [4]. As a result, GaN HEMT can output high power density (3 W/mm) at operating frequencies up to 100 GHz [5]. This enables the design of microwave circuits with larger bandwidth that can be used to design wideband radars and communication systems with higher capacity. The high frequency also translates to fast switching speeds, which can be utilized for power electronic applications.

The reliability of GaN transistors rank among the highest of all semiconductors, and the mean time-to-failure (MTTF) is several orders of magnitude higher than e.g. GaAs, as shown in Fig. 1.1b. As a result, GaN HEMTs are able to operate at higher device temperatures, which means that several times higher voltages and currents are supported. Since the higher power density of GaN HEMTs naturally leads to higher device temperatures, the higher temperature tolerance is a key feature that enables the performance of GaN HEMTs.

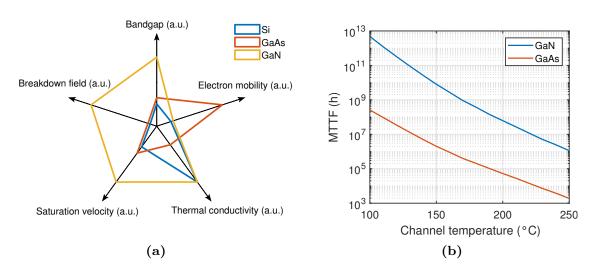

Figure 1.2: RF output power versus thermal resistance for a fixed channel temperature. The rectangle indicates the output power and thermal resistance of currently available devices.

#### Thermal Limitations

To be able to continue to meet the increasing industry demands, efforts are made to further improve the performance of GaN HEMTs, whose full potential is still far from realized. GaN technology therefore remains an active research area, where the focus is on increasing power density, efficiency, and linearity through progress in both material science and device design. The power density is a key enabling factor for many applications, and the current power density of GaN HEMTs is significantly lower than predicted theoretical limits as well as power levels that have been demonstrated with short pulses on small devices  $(40 \,\mathrm{W/mm})$  [6]. In practice, such power levels cannot be realized in sustained operation today due to the excessive waste heat that would be generated in the device. The waste heat is a result of the DC-to-RF conversion efficiency which is less than unity. The dissipated power elevates the channel temperature, resulting in rapid transistor performance and lifetime degradation, as shown in Fig. 1.1b. The channel temperature increases with increasing power density, and a typical requirement for commercial devices is a lifetime of at least  $10^6$ hours, meaning the channel temperature cannot exceed approximately 225 °C. As a result, commercial monolithic microwave integrated circuit (MMIC) technologies are limited to power densities between 5 and  $10 \,\mathrm{W/mm}$  [7]. Attempting to operate the devices at 40 W/mm under real-world waveforms conditions, would result in unacceptably high channel temperature, which would lead to a lifetime reduction of five orders of magnitude [8]. The power density of GaN HEMTs today is therefore thermally limited to levels approximately ten times lower than what is known to be attainable. To increase the output power while maintaining a sustainable channel temperature, the thermal resistance must be reduced. Fig. 1.2 shows the power density as a function of thermal resistance at 225 °C. The approximate power levels and thermal resistance of current GaN devices is indicated by the rectangle. The arrow shows that in order to increase the power density ten times with a temperature below 225 °C, the thermal resistance must be reduced by approximately a factor eight. Efforts are therefore made to reduce the thermal resistance by the implementation and improvement of remote and integrated cooling techniques.

#### Thesis Motivation and Outline

In the development of new semiconductor devices, measurement methodology is crucial since measurement results is the basis on which conclusions about material and device designs are drawn. The work to increase e.g. the power density involves efforts to increase the current density and breakdown voltage coupled with efforts to lower the thermal resistance and increase the efficiency. In the work to achieve this, modifications to the device design are made and key measurements are used to assess the alterations in regard to the thermal and electrical properties of the device. It is thus imperative that the measurement methods are capable of providing accurate and extensive characteristics. However, new semiconductor technologies create new measurement-challenges, and methods must therefore continuously be developed and adapted. The characterization of GaN-based devices is associated with a number of challenges that can make performance evaluations complicated. Key challenges and needs related to measurements can be summarized as follows. (i) Electron trapping create electrical memory effects that can distort rudimentary IV characteristics and electric-based thermal characteristics. Trapping effects and thermal effects are coupled and their interdependencies make it difficult to separately observe properties such as self-heating effects. (ii) Due to the limitations of optical-based thermal measurements, there are few techniques to reliably measure the lateral thermal coupling in GaN circuits. Furthermore, electric-based techniques are needed to evaluate solutions to disperse the heat in fully enclosed circuits, and the need to assess thermal coupling increases as the size of circuits decreases at higher frequencies. (iii) The power density is limited by the breakdown voltage, which is normally determined using DC measurements. However, the DC breakdown voltage does not necessarily represent the actual voltage limitation of the device during large-signal operation, where the maximum voltage is only applied for a short time. Furthermore, GaN devices inherently lacks the ability to be driven in the breakdown region [9], which makes it challenging to compare different breakdown results.

This thesis presents techniques for improved thermal and electrical characterization of GaN HEMTs. The methods have been developed to capture complex characteristics and to mitigate distortion due to trapping effects, which facilitates the evaluation of new GaN devices. Chapter 2 covers fundamentals aspects of GaN devices and briefly describes the device structure, functionality, and its inherent dispersive properties. Chapter 3 is dedicated to electrical characterization under trap-dispersive conditions, and methods are introduced to obtain distortion-free IV and thermal characteristics in the presence of trapping effects. In chapter 4, a method to characterize the lateral thermal coupling is presented as well as a biasing technique for GaN MMICs, which compensates for the RF performance loss due to thermal effects. In chapter 5, the static breakdown characteristics of GaN HEMTs are studied and methods to perform dynamic breakdown measurements are outlined. The different breakdown characteristics are subsequently compared and the influence of the buffer thickness on the breakdown measurement is examined.

## Chapter 2

# Key Aspects of GaN HEMT Technology

The purpose of this chapter is to briefly describe key aspects of GaN HEMT technology for RF applications, to make the research discussed in subsequent chapters more comprehensible. A more detailed description of GaN-based devices and their functionality can be found in e.g. [10,11]. The GaN HEMT is a compound semiconductor technology, which is based on a heterojunction that is formed by the growth of a GaN layer and a III-nitride barrier layer. The first HEMT based on an AlGaN/GaN heterojunction was reported in the 90s [12], and it showed the potential of heterostructures designed with wide bandgap materials. Since then, efforts have been made to fully realize the potential of GaN-based devices.

### 2.1 Device Structure and Functionality

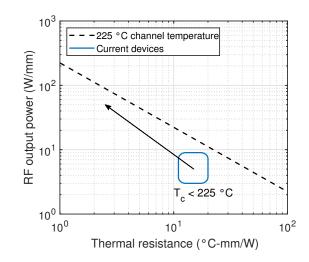

A schematic cross section of a basic microwave GaN HEMT is shown in Fig. 2.1a (not to scale). The HEMT is created by growing semiconductor materials in a layer structure, and by incorporating metal contacts and dielectrics in a device processing step. The different layers materials and their typical thickness are depicted in Fig. 2.1a. Although all GaN-based devices share a common core structure, the layer arrangement and dimensions are designed differently to enhance different device properties. In this case, the shown dimensions are indicative of the typical size of each layer, and the device features a generic design, which resembles the design of the evaluated devices in this thesis. The different parts of the device serve different purposes to create the desired device functionality. In the following sections, the purpose and challenges for each part are described briefly.

#### AlGaN Barrier and 2DEG

The GaN buffer and AlGaN barrier form the heterojunction where the channel is created, which enables the core functionality of HEMTs. All III-N materials are polarized due to the difference in electronegativity between the elements in the compounds. The polarization fields point downwards in the structure, and

Figure 2.1: (a): schematic cross section of a basic microwave GaN HEMT. (b): top view of a basic microwave GaN HEMT with coplanar layout.

the fields bend the energy bands, which are formed into a quantum well at the junction. The field strength is higher in the AlGaN compared to GaN, resulting in a net positive polarization charge at the AlGaN/GaN interface. This attracts electrons from donor-like surface states on the the AlGaN surface, which form a two-dimensional electron gas (2DEG) in the well at the AlGaN/GaN junction. To form the 2DEG, a minimal barrier thickness is required and the barrier bandgap needs to be wider than the bandgap of the GaN layer [13]. The electron density  $(n_s)$  in the 2DEG depends on the polarization charge and therefore on the barrier Al content. Increasing the thickness and/or the Al concentration in the AlGaN barrier increases  $n_{\rm s}$ . However, the lattice constant of the AlGaN barrier is generally not matched to GaN, and the barrier is therefore subjected to strain, which increases with the Al mole fraction. The strain increases the probability of dislocations and partial relaxation, which reduces the reliability of the device. This limits the maximum Al content in the AlGaN layer to values ranging from 15 to 30 %, and the thickness is normally around 10 nm.

In HEMTs, the carrier electrons are spatially separated from the donor atoms. This reduces the electron scattering due to collisions between particles, which translates to a higher carrier mobility for HEMTs compared to other types of FETs. Furthermore, in contrast to HEMTs based on GaAs, GaN HEMTs do not require n-doping in the barrier for the 2DEG to be created.

#### Surface Layers and GaN Buffer

A thin GaN cap layer around 2 nm is normally included on top of the barrier layer to protect the surface of the barrier from oxidization during fabrication. Since the electrons in the 2DEG originates from the barrier surface, it is sensitive to changes in the surface potential. The GaN cap layer can therefore slightly impact the maximum drain current as well as the gate leakage. To reduce channel modulations via the surface potential, a surface passivation layer is deposited to passivate the trap states. The most used and studied passivation layer for GaN HEMTs is silicon nitride,  $SiN_x$  [14, 15].

The main purpose of the GaN buffer layer is to decrease the number of defects in the channel region and provide a flat surface where the barrier layer can be grown. Therefore, the GaN buffer normally needs to be more than 1 µm. To mitigate short channel effects, the buffer should be designed to have high electric isolation as well as to confine the electrons to the channel. Several buffer design topologies can be used for this purpose, including transition layers with different doping profiles and materials. For microwave devices, the buffer is normally iron doped to increase the isolation whereas carbon is normally used for power devices. The main challenge is to introduce design changes without inadvertently impact other performance aspect of the device. Both the carbon and iron reduce current leakage but these elements also introduce acceptor-like trap states, which cause dispersion in the device.

#### Substrate and Nucleation Layer

The largest part of the device is the substrate underneath the buffer and nucleation layer. The substrate strongly influences the device reliability since it is the main medium through which heat flows away from the channel. The substrate should have high thermal conductivity to cool the device as much as possible, and it should ideally have a matched lattice constant to minimize the induced strain on the buffer. While SiC is the most common substrate for GaN MMIC technologies, GaN, AlN, and diamond are attractive alternatives since e.g. GaN would enable growing buffers with lower dislocation densities. Diamond has superior thermal conductivity but it would introduce a large mismatch in terms of lattice constant and coefficient of thermal expansion. The effective permittivity is largely set by the substrate properties, which are crucial for the performance at microwave frequencies.

To reduce the lattice mismatch and to promote two-dimensional growth of the GaN buffer, a nucleation layer is generally grown on the substrate, which is lattice matched to the buffer. For SiC substrates, AlN is mostly used, and due to the SiC-AlN lattice mismatch, the crystal quality is inherently low in the nucleation layer. This contributes to that the nucleation layer acts as a thermal barrier [16], which therefore reduces the heat flow from the channel to the substrate.

#### **Ohmic and Schottky Contacts**

The source, drain and gate contacts are indicated in Fig. 2.1a. The HEMT uses ohmic and Schottky type contacts to get access to and control the current in the channel. The source and drain should enable efficient injection and extraction of current, and minimal contact resistance to the channel is thus desirable. Ohmic contacts are therefore used, which have low contact resistance and promote a linear current flow between the contact and channel. The purpose of the gate is to control the flow of current between the two ohmic contacts while minimizing current flow through the gate. A Schottky contact is therefore used, which exhibits a non-linear IV characteristic, that allows current to flow predominantly in one direction. This allows for high reverse voltages on the gate, which is necessary to influence the flow of current in the channel. Control of the current in the 2DEG is done with the field effect where a voltage is applied to the gate terminal, which results in band bending underneath the gate contact. A sufficiently negative voltage raises the the quantum well above the fermi level, which depletes the 2DEG of charge carriers, effectively closing the channel.

#### **Device** layout

The layout of the device includes the dimensions and arrangement of the contacts, field plates, and access conductors to the HEMT. The layout strongly influences the device properties and performance, including thermal, frequency, and breakdown characteristics. Scaling down the device is generally necessary to improve the high frequency performance. However, a more compact device often leads to a higher operating temperature, lower breakdown voltage, and larger performance-deteriorating short-channel effects. The parasitics are also affected when the separation between electrodes, as well as geometry of contacts and conductors, are changed. Additionally, a reduction of e.g.  $L_{\rm gd}$  lowers the breakdown voltage due to the ensuing higher electric field between the drain and gate. A field plate is normally connected to the source and extended towards the drain to reduce the electric field and therefore increase the breakdown voltage. The device in Fig. 2.1a features a gate field plate, which is a simpler form of field plate that is connected to the gate.

GaN HEMTs normally feature several gate contacts connected in parallel (known as gate fingers), to increase the current and utilize chip area more efficiently. Furthermore, the devices often feature a co-planar design, where the signal and ground conductors are in the same plane, which enhances the RF performance due to reduced parasitics and better characteristic impedance control. Fig. 2.1b shows a coplanar  $2x50 \,\mu\text{m}$  device intended for tests and development, and the same kind of device was used for the studies in paper [A,E].

To enable the design of complete circuits, and to design test structures used to evaluate HEMT technologies, devices without the gate contact are often required. This type of device is essentially a HEMT with a constantly open channel, and it is refereed to as gateless device/ungated HEMT, GaN resistor or mesa resistor, depending on the method to electrically isolate the device. In paper [B,C], the properties of gateless devices are exploited to investigate lateral heat coupling in GaN MMIC technology and to suppress trap-related distortion in thermal resistance extractions.

#### **Basic Functionality**

The basic functionality of HEMTs can be understood by the their basic IV characteristics. Considering only the drift current, which is much larger than the diffusion current in GaN devices, the drain current can be expressed as [10]

$$I_{\rm ds} = qn_{\rm s}(x)Wv_{\rm d}(x), \tag{2.1}$$

where q is the electron charge,  $n_s$  is the charge carrier density in the channel, W is the width of transistor, and  $v_d(x)$  is the electron drift velocity at the horizontal position x in the channel. To derive accurate expressions of (2.1) in terms of physical parameters of the device as well as the gate-source voltage

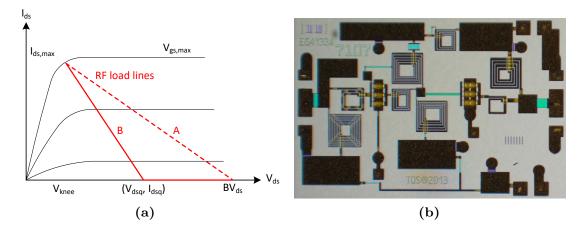

Figure 2.2: (a): GaN HEMT  $I_{ds}$ - $V_{ds}$  characteristics. The red lines show RF load lines associated with a class A (dashed) and B (solid) bias. (b): LNA MMIC featuring two GaN HEMTs connected in cascade.

$(V_{\rm gs})$  and drain-source voltage  $(V_{\rm ds})$  can become complex due to the inclusion of detailed physics of the device. Accurate expressions of  $v_{\rm d}(x)$  and  $n_{\rm s}(x)$  for GaN-based HEMTs are needed, and several publications have been made on this topic [17]. However, by using simplified expressions for  $v_{\rm d}(x)$  and  $n_{\rm s}(x)$ , basic functionality can be studied. First, Si-like velocity-field characteristics can be assumed, meaning  $v(x) = \mu E(x)/(1 + \mu E(x)/v_{\rm sat})$ , where  $v_{\rm sat}$  is the saturation velocity,  $\mu$  is the electron mobility, and E(x) is the electric field. It can be further assumed that  $n_{\rm s}(x) = \varepsilon_2/(qd) [V_{\rm gs} - V_{\rm off} - V(x)]$ , where  $\varepsilon_2$  is the dielectric constant in the AlGaN barrier, d is the barrier thickness, and  $V_{\rm off}$ is the threshold voltage under ideal conditions. Inserting these expressions in (2.1), and integrating over the gate length yields the following expression for the drain current:

$$I_{\rm ds} = \frac{1}{1 + \mu V_{\rm ds}/v_{\rm sat}L_{\rm g}} \left\{ \frac{\mu W}{L_{\rm g}} \frac{\varepsilon_2}{d} \left[ (V_{\rm gs} - V_{\rm off})V_{\rm ds} - \frac{V_{\rm ds}^2}{2} \right] \right\}.$$

(2.2)

The  $I_{\rm ds}$ - $V_{\rm ds}$  characteristics obtained by evaluating (2.2) for different  $V_{\rm gs}$  are shown in Fig. 2.2a (solid lines). At low  $V_{\rm ds}$  the slope at the maximum gatesource voltage ( $V_{\rm gs,max}$ ) is high meaning the on-resistance ( $R_{\rm on}$ ) of the HEMT is small. Conversely, at sufficiently low  $V_{\rm gs}$  the output resistance approaches infinity. The red line in Fig. 2.2a shows the current when the HEMT is biased at ( $V_{\rm dsq}$ ,  $I_{\rm dsq}$ ), and a large AC signal is applied to the gate. The small gate voltage causes a large current and voltage modulation on the HEMT output, and this signal gain can be used to fabricate amplifier circuits at high frequencies, including MMIC amplifiers. An example of such a circuit is shown in Fig. 2.2b, which shows the MMIC amplifier used for the study in paper [D]. In the circuit, two HEMTs are connected in cascade, and additional circuitry for e.g. biasing surround the HEMTs, which enable the functionality of the amplifier.

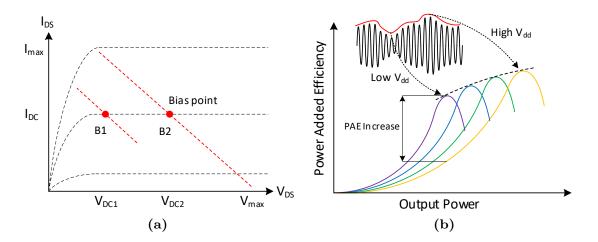

In amplifier applications, the current and voltage follow the RF load line (A or B in Fig. 2.2a), and the slope of the line is determined by the impedance of the load connected to the HEMT output. For power amplifiers, the load should be selected to maximize the swing in the characteristics to maximize the output power. Amplifiers are classified by their conduction angle, which indicates the fraction of the signal period during which the transistor conducts.

For a class A amplifier, the HEMT is always on (360 °conduction angle), and this is achieved by biasing the device so the channel conducts throughout the entire cycle. For this class of operation, the maximum output power of the HEMT is given by

$$P_{\rm max} = \frac{I_{\rm ds,max}(BV_{\rm ds} - V_{\rm knee})}{8},\tag{2.3}$$

where  $I_{ds,max}$  is the maximum drain current,  $BV_{ds}$  is the drain-source breakdown voltage, and  $V_{knee}$  is the knee voltage, as indicated in Fig. 2.2a. Although the breakdown can occur at on- or off-state  $V_{gs}$ , the off-state breakdown voltage has the most direct effect on the power limits of a device since the maximum voltage for the most commonly used amplifier classes is reached while the HEMT is in a pinch-off condition. The output power can be increased by increasing either  $I_{ds,max}$  or  $BV_{ds}$ . Increased  $I_{ds,max}$  decreases the optimal output impedance, and a higher current can be achieved by simply increasing the gate periphery. On the other hand, a high  $BV_{ds}$  increases the optimal output impedance, which can be utilized to design for a maximum output power at an output impedance closer to  $50 \Omega$ . This enables to design a simpler and more efficient matching network with large bandwidth, which facilitates the design of wide band amplifiers. Thus, increasing  $P_{max}$  by increasing  $BV_{ds}$  is advantageous and it is possible due to the large bandgap of GaN.

### 2.2 Dispersive Effects

There are several physical mechanisms in GaN HEMTs that can cause dispersion, which is broadly defined as undesired variations in electrical characteristics as a function of bias conditions, operating timescales, or signal properties such as frequency. Self-heating and electron trapping are prevalent and create major challenges in the development of GaN HEMTs. In the following sections, self-heating, electron trapping, and the effects of these dispersion sources are briefly discussed.

#### Self-heating Effects

Self-heating is caused by the conversion of electric power in the device into heat. The dissipated power increases the device temperature, which causes thermal effects such as a reduction of the current.  $n_{\rm s}$  in (2.1) is relatively stable versus temperature although a small decrease at higher temperatures has been observed [18]. The primary reason for a reduced current is the reduction in  $v_{\rm d}$  due to decreased electron mobility at higher channel temperatures  $(T_{\rm c})$ since generally  $v_{\rm d} = v_{\rm d}(\mu(E,T_{\rm c}),E)$ . The mobility is determined by different scattering mechanisms, and there are numerous scattering mechanisms occurring in different types of semiconductors. The scattering mechanisms in 2DEG systems are optical and acoustic phonon scattering (lattice vibrations), alloy scattering, remote ionized impurity scattering, residual screened impurity scattering (background or intentionally doped channel impurities), and interface roughness scattering. At temperatures higher than room temperature, polar optical phonon scattering is the dominant mechanism [19, 20], which causes the mobility to decrease significantly with increasing temperature. The temperature increase due to self-heating can be expressed in the frequency

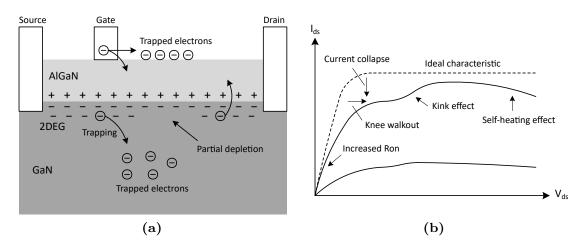

Figure 2.3: (a): illustration of the trapping and build-up of trap charge in a GaN HEMT. (b): illustration of trapping and self-heating effects in the  $I_{ds}$ - $V_{ds}$  characteristics of a GaN HEMT.

domain as a function of the power dissipation and the thermal properties of the device according to

$$T_{\rm c}(\omega) = P(\omega)Z_{\rm th}(\omega) + T_{\rm a}, \qquad (2.4)$$

where P is the power dissipation and  $T_{\rm a}$  is the ambient temperature.  $Z_{\rm th}(\omega)$  is the thermal impedance, which represents the thermal properties of the device.  $Z_{\rm th}(\omega)$  is comprised of a thermal resistance  $(R_{\rm th})$ , which quantifies the ability of the device to conduct heat from the channel region to the surrounding environment, and a thermal capacitance  $(C_{\rm th})$ , which represents the ability of the device to store heat. The thermal impedance is often modeled as a parallel RC, Foster or Cauer RC network [21]. The latter is used to better approximate the distributed nature of heat transfer through several materials. An implication of these models is that the self-heating is frequency-dependent, and can be constant above a certain frequency and vary according to e.g. the envelope of modulated signals. At low frequency,  $T_{\rm c}$  increases with P, causing  $\mu$  to decrease with P, and the current in the  $I_{ds}$ - $V_{ds}$  characteristic therefore decreases at higher power dissipation levels, as shown in Fig. 2.3b. The effects of self-heating generally involve a deterioration of the electric characteristics of the transistor and circuit where the device is used. The noise power increases at higher temperatures, and the reduced current reduces the RF power and the gain. Furthermore, the S-parameters depend on temperature, and the temperature variations can degrade the functionality and effectiveness of circuitry connected to the device.

#### **Electron Trapping Effects**

The effects of trapping range from localized charge accumulation to degradation of electrical performance. Trap-states are created by crystal defects in semiconductors, which can be divided into point defects and extended defects. Point defects are places where an atom is missing or is irregularly placed in the lattice and the following types of point defects exist: Foreign substitutional (e.g. dopant atom), foreign interstitial (e.g. oxygen in silicon), self-interstitial, and vacancy defects. Extended defects include line defects (groups of atoms in irregular position), planar defects (two-dimensional interface defects such as grain boundaries), and volume defects (e.g. regions with several missing atoms). The different crystal defects and associated trap-states are found at various locations in GaN HEMTs. At the surface, trap states are formed due to the termination of the bulk crystal structure. Furthermore, more trap states are present at/around interfaces because of the lattice mismatching, which leads to a higher strain and therefore larger amount of defects at such regions. The effects of trapping are typically caused by the following traps: surface traps, bulk traps in the AlGaN barrier, interface traps at the AlGaN/GaN interface, bulk traps in the GaN buffer, interface traps at the transition from the GaN buffer to the AlN nucleation layer, and traps in the substrate.

The different trap states are characterized by their energy level, capture cross section (probability to capture an electron) as well as their emission and capture and time constants. Deep-level traps have energies far down in the band-gap and therefore exhibit long emission time constants. Most trap time constants are temperature-dependent and can create severe memory effects in GaN HEMTs. In general, the trapping leads to deterioration of the electric characteristics, which reduces and limits the performance of the device in terms of e.g. output power, noise, and efficiency. This can be understood by the illustration of trapping effects in Fig. 2.3. In Fig. 2.3a, it can be observed that electrons from the gate are captured by surface traps, which is equivalent to negatively charging up an imaginary gate (referred to as virtual gate). This partially depletes the channel underneath of electrons and creates a second barrier along the channel, leading to reduced current. When a high  $V_{\rm ds}$  is applied, the electrons in the conducting channel are rapidly accelerated, and can gain enough kinetic energy to be injected into an adjacent regions such as the buffer. The electrons can subsequently become trapped in the buffer, as shown in Fig. 2.3a, and the build-up of negative charge in the buffer depletes the channel region, which reduces the current further. The effects of trapping on the  $I_{\rm ds}$ - $V_{\rm ds}$  characteristics are shown in Fig. 2.3b. Compared to the ideal IV curve, the non-ideal curve has a higher on-resistance and a collapse of the current in the knee region can be observed. Furthermore,  $V_{\rm knee}$  is seen to increase, which directly reduces the power in eq. (2.3). The kink in the curve above the knee is a hysteretic instability of the drain current in FETs, which is caused by trapping effects, although several trap-based explanations for this effect can be found in the literature [11].

## Chapter 3

# Measurement-Based Mitigation of Trap-Effects

IV measurements are the most fundamental measurements used to evaluate the performance of transistor technologies. The measurements provide basic information of the device including  $R_{\rm on}$ ,  $I_{\rm ds,max}$ , and pinch-off voltage ( $V_{\rm po}$ ), as well as figures of merits for short-channel effects such as DIBL (draininduced barrier lowering) and SS (subthreshold swing). Furthermore, the IV characteristics can be used to analyze the thermal properties of the device due to the coupling between the electric power and the device heating. The IV data is also essential for the extraction of a HEMT model, which enables simulations in MMIC design, where the properties predicted by the model are used to design circuitry surrounding the transistor.

To ensure that the IV data can be used for the different purposes as intended, the IV measurements should ideally meet certain requirements. The characterization process and setup fixture should not affect the measurement result. Furthermore, it is desirable to be able to fully control all types of current-affecting factors (such as voltage, temperature, and trapping) in IV measurements since this would enable to evaluate e.g. the effects of selfheating and trapping separately. An example of a temperature-controlled characterization is pulsed IV, where the influence of self-heating on the resulting characteristic is controlled by the pulse timing.

However, trapping effects in GaN devices make it difficult to carry out the ideal characterizations. In general, the IV characteristics are always sensitive to parameters influencing the trapping and de-trapping, including the bias voltage, stimulus timing, and the temperature. Furthermore, the self-heating and trapping effects are interdependent, which further complicates isolating the influence of self-heating in an IV characteristic, making it difficult to perform a thermal analysis. Additionally, the wide range of trap time constants cause IV characteristics to be affected by short- and long-term memory effects. As a result, IV characteristics may vary over time, and all parts of a characteristic depend on measurement settings such as the maximum voltage and the stimulus timing in measurement sweeps. It can therefore be difficult to repeat measurement results, and obtained characteristics may be strongly dependent on specific settings. In this chapter, the impact of trap-related effects on IV characteristics is demonstrated, and measurement methods to mitigate distortion of IV and electric-based thermal characteristics are introduced. A new method to perform the  $I_{ds}$ - $V_{ds}$  characterization is shown, which minimizes the influence of trap-related memory effects on the measurement result. The method yields a rudimentary IV characteristic suitable for the extraction of basic device properties. Additionally, a methodology to extract the thermal resistance of GaN devices using electric measurements is introduced, where trap-related effects are circumvented to prevent distortion of the results. This is useful when the thermal properties of different GaN samples are compared since the distortion due to trapping effects can vary significantly between different technologies.

### **3.1** Trapping Effects in IV Characteristics

Trapping effects in IV characteristics are commonly studied using pulsed IV measurements, where e.g. deep buffer trapping and surface trapping can be induced by controlling the quiescent bias and the pulse timing. Another method is presented in [22], where dynamic load-lines measured in the MHz range are used to reconstruct the equivalent of pulsed IV curves. In this case, the trapping is controlled by the frequency and the maximum  $V_{\rm ds}$  reached in the dynamic voltage swing. The main advantage is that the characterization (and subsequent model extraction) is performed under conditions better resembling the intended transistor operation.

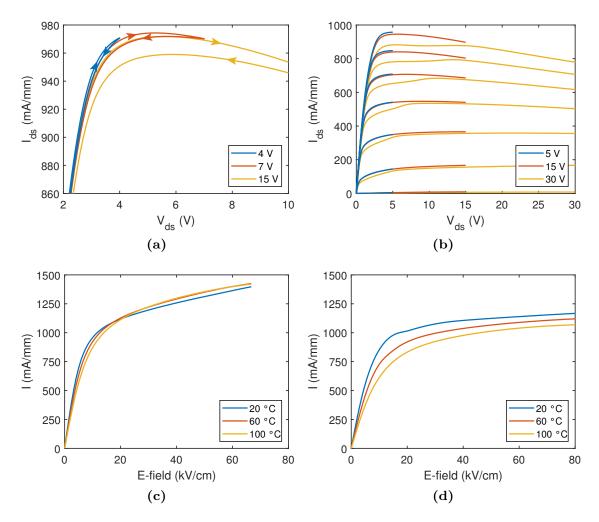

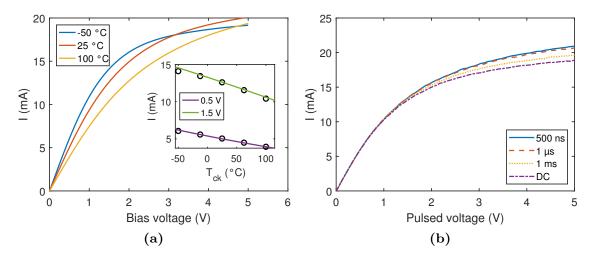

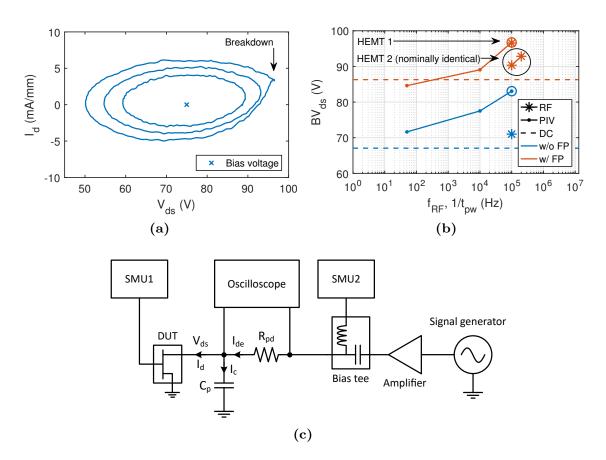

However, even when trapping effects are not deliberately induced, GaN HEMTs are affected by trapping so that the transistor performance depends on signal frequency and recently applied maximum voltages [22]. Trap-related memory effects in IV characteristics can be observed using bi-directional  $I_{\rm ds}$  versus  $V_{\rm ds}$  sweeps, as demonstrated in paper [A]. The results of three consecutive sweeps with increasing maximum drain-source voltage ( $V_{\rm ds,max}$ ) are shown in Fig. 3.1a, and the visible hysteresis is a distinct manifestation of a memory effect. Although hysteresis can be observed for all three voltage settings, it increases significantly when the maximum voltage in the sweep is increased. It can be further noted that the forward sweep for  $V_{\rm ds,max} = 15$  V overlaps with the reverse sweep of  $V_{\rm ds,max} = 7$  V, showing that the 15 V measurement starts with the memory state left by the previous sweep. Thus, each measurement starts with a different initial memory state in the device, which makes comparisons of the results of different IV measurements on GaN HEMTs complicated.

For sweeps to higher voltages, the trap-related kink effect (chapter 2.2) can often be observed in the  $I_{ds}$ - $V_{ds}$  characteristics [23] in addition to other memory effects. The kink anomaly is most visible in characteristics measured with a slow  $V_{ds}$  sweep, and it can be seen between 5 and 15 V in Fig. 3.1b, where several  $I_{ds}$ - $V_{ds}$  characteristics of a GaN HEMT are shown. From these cases, it can be concluded that the kink effect becomes apparent when  $V_{ds,max}$  is increased beyond 15 V. Furthermore, it can be noted that the entire IV characteristic deteriorates with increasing  $V_{ds,max}$  predominantly due to the kink effect. For example,  $I_{ds,max}$  is seen to be notably lower and  $V_{knee}$  is seen to be slightly higher at 30 V compared to  $V_{ds,max} = 15$  V. It can be further concluded that the shape of the obtained characteristics are bound to the selected  $V_{ds,max}$ , which

Figure 3.1: (a): consecutive bi-directional IV sweeps, with increasing  $V_{ds,max}$  (4 to 15 V). (b):  $I_{ds}$ - $V_{ds}$  characteristics with increasing  $V_{ds,max}$  (5 to 30 V). (c)-(d): current versus approximate E-field for two different GaN technologies.

makes it difficult to compare characteristics that have not been measured using the same settings. The extent to which basic properties of the characteristics are influenced by the specific voltage limits is also difficult to assess from a single measurement.

The electrical device properties are temperature dependent, and IV measurements at different ambient temperatures (chuck temperature in this work) is the obvious method to evaluate the thermal behavior of the device. However, the manner and way in which self-heating and trapping affect the current is different; self-heating affects the current due to the temperature dependence in  $v_d$ , whereas the charging and discharging of traps primarily modulate the current via  $n_s$ . The trapping and de-trapping of electrons strongly depends on the electric field [24], but the de-trapping is also heavily influenced by the temperature, which depends on the dissipated power. Hence, the self-heating and trapping effects are interdependent. Furthermore, these effects can affect the current in the opposite direction, which can be understood at e.g. higher temperatures, where  $v_d$  is decreased while increased de-trapping can cause  $n_s$ to increase. This is demonstrated in Fig. 3.1c & Fig. 3.1d, where the current (I) versus the approximated homogeneous electric field (E-field) of gateless devices is shown at three different chuck temperatures ( $T_{ck}$ ). The figures show IV characteristics of two different GaN HEMT technologies, and it can be seen in Fig. 3.1c that the current is first decreasing with temperature up to 15 kV/cm, after which the current temperature coefficient  $(dI/dT_{\rm ck})$  is inverted due to detrapping effects. In contrast, the characteristics of the other GaN technology in Fig. 3.1d exhibits a negative temperature coefficient up to 70 kV/cm, indicating less trapping and de-trapping effects. Clearly, the sole impact of self-heating cannot be observed, and device comparisons are complicated because the extent to which trapping effects hide self-heating effects varies between technologies.

## 3.2 Trap-Effects Suppression in IV Measurements

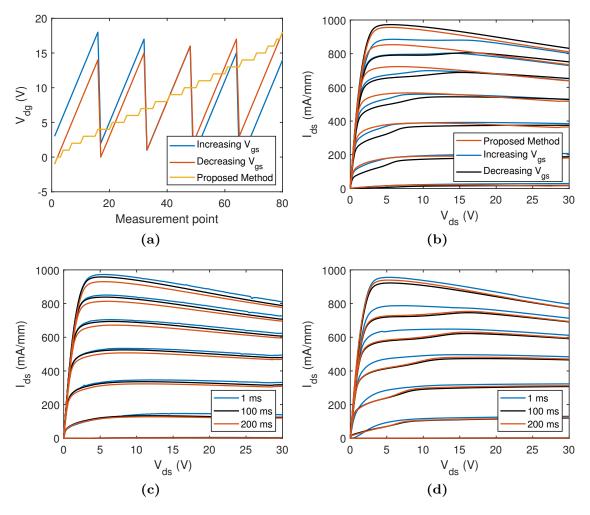

Normally, an IV characterization of field-effect transistors is performed by sweeping  $V_{\rm ds}$  and  $V_{\rm gs}$  according to the settings selected by the operator. For an  $I_{\rm ds}$ - $V_{\rm ds}$  characterization,  $V_{\rm ds}$  is usually swept from a low-to-high value while  $V_{\rm gs}$  is kept constant. The  $V_{\rm ds}$  sweep is then repeated at a different  $V_{\rm gs}$ , which is either increasing or decreasing. The characteristics obtained using this methodology (Fig. 3.1b, increasing  $V_{gs}$ ), are evidently heavily dependent on the maximum  $V_{\rm ds}$ , and deteriorate with increasing  $V_{\rm ds,max}$ . The deterioration is caused by the trapping effects, which are primarily induced and exacerbated by high electric fields. Thus, to avoid the deterioration of the characteristic, the bias points at high  $V_{\rm ds}$  should be measured at the end of the sweep, and the peak electric field at preceding measurement points should ideally be lower or equal. To achieve this, a method is needed to quantify the strength of electric field as a function of bias. For this purpose, the drain-gate voltage  $(V_{dg})$  can be used since the peak drain-gate electric field and extension of the field into the buffer increases when  $V_{\rm ds}$  increases and/or  $V_{\rm gs}$  decreases [25, 26]. This relationship is utilized in paper [A] to rearrange the gate and drain bias points so that the peak drain-gate E-field is predominantly increasing throughout the measurement. The ordering of the bias points is performed by first calculating  $V_{\rm dg}$  using the voltage sweep settings, and subsequently sorting the bias points so that  $V_{dg}$  strictly increases. An example for the  $I_{ds}$ - $V_{ds}$  characterization is presented in Fig. 3.2a, where  $V_{dg}$  for the standard methods (increasing and decreasing  $V_{\rm gs}$ ) as well as for the proposed method are shown. Clearly,  $V_{\rm dg}$ repeatably changes from a low to a high value in a sawtooth shape for the standard methods while it increases monotonically in the case of the proposed method.

In paper [A], the methodology was evaluated on two commercially available AlGaN/GaN-on-SiC HEMT technologies. Examples of the  $I_{ds}$ - $V_{ds}$  characteristics obtained using the proposed method and the standard methods are presented in Fig. 3.2b, where a lower knee current and the kink effect can be seen in the characteristics resulting from the standard methods. At  $V_{gs,max}$ , the increasing  $V_{gs}$  characteristic shows the largest deterioration due to the preceding sweeps starting at  $V_{gs,min}$ . On the contrary, the decreasing  $V_{gs}$  characteristic shows the smallest deterioration at  $V_{gs,max}$  since it is the first  $V_{gs}$  that is measured in this case. The IV characteristics of the proposed method show no obvious kink effect/trap-related deterioration.

The impact of trapping and de-trapping on the IV characteristics depends

Figure 3.2

Figure 3.3: (a): drain-gate voltages in different  $I_{ds}$ - $V_{ds}$  characterizations. (b):  $I_{ds}$ - $V_{ds}$  characteristics measured with the proposed method, increasing  $V_{gs}$  method, and decreasing  $V_{gs}$  method. (c)-(d):  $I_{ds}$ - $V_{ds}$  characteristics obtained using different measurement delay times. (c) shows characteristics obtained using the proposed method and (d) shows characteristics obtained using the decreasing  $V_{gs}$  method.

on the timing of the measurement due to the time constants associated with the trap states. Thus, trap-related effects in IV characteristics can be investigated by varying the time settings of the source measurement unit (SMU). In paper A, the sensitivity of the characteristics to the timing was investigated by varying the delay time  $(t_{\rm md})$  between the output of the bias and the measurement start at each bias point. The results for the proposed method and the standard method (decreasing  $V_{\rm gs}$ ) are shown in shown in Fig. 3.2c and Fig. 3.2d, respectively. Evidently, the characteristics obtained using the proposed method show a smaller dependence on  $t_{\rm md}$  compared to the standard method, indicating a smaller influence of traps. It can be further noted that a fast sweep with the standard method yields a characteristic seemingly devoid of trapping effects, partly because a possible kink is spread out over a larger voltage range.

Due to the self-heating, a current reduction, which increases with increasing  $t_{\rm md}$  and/or  $V_{\rm gs}$  is expected. This can be seen in the results of the proposed method (Fig. 3.2c) but not consistently in the case of the standard method. This suggests that the proposed method provides more accurate information

regarding the impact and time dependence of the self-heating in the HEMT. It can be further concluded that the proposed method yields an IV characteristic that is more independent of the time settings of the measurement.

### **3.3** Reliable Thermal Resistance Extraction

Thermal characterization techniques that rely on electric measurements exploit the self-heating in the device to determine key thermal properties such as the thermal resistance. These techniques (section 4.1) assume that the temperature behavior of the current is set by self-heating, which makes the validity of this assumption crucial to obtain accurate results. However, for many GaN-based devices, it is evident (section 3.1) that this assumption is not always true due to the charging and discharging of traps. As a result, the thermal analysis can yield inaccurate results that can be misleading. Furthermore, since technologies are affected by trapping to a varying extent, it is difficult to compare the results of the thermal analysis due to the variation of the accuracy.

The self-heating must be enhanced and trapping effects must be suppressed to enable an accurate thermal analysis. Thus,  $n_s$  should ideally be stable and independent of the lateral E-field and  $T_c$ . The trap-related current modulation increases when the peak E-field increases, and the obvious way to reduce the E-field is to reduce the applied voltage. However, a reduction of the voltage also decreases the dissipated power, leading to decreased self-heating. Another way to reduce the electric field is to increase the contact separation. To understand the relationship between the different parameters, the power dissipation in a gateless device (section 2.1) at low voltages can be examined, which is given by the following expression:

$$P = q n_{\rm s} \mu W \frac{V^2}{L},\tag{3.1}$$

where V is the voltage and L is the contact separation, and W is the device width. In this case the E-field can be approximated as V/L. Thus, (3.1) implies that to keep P as high as possible, it is better to reduce the E-field by increasing the contact separation  $(P \propto 1/L)$  instead of decreasing the voltage  $(P \propto V^2)$  [27]. Obviously, layout requirements such as a minimum L severely limits the kind of device that can be evaluated, which reduces the usefulness of the approach. Furthermore, the desired device type is likely not available on new wafers, and the necessary design can be difficult to determine since it depends on possibly unknown trap characteristics of the technology. A solution to this is to utilize gateless devices in TLM structures, which are ubiquitous in PCM areas and feature an array of devices with different L. Therefore, a device from the TLM structure that meets the thermal measurement requirements is likely available. It should be emphasized that the proposed approach limits the layout of the device to enable a more accurate thermal evaluation, which makes it suitable to use for comparisons of the thermal performance of e.g. different epitaxial designs. The suggested approach was therefore used in paper [B] to compare the thermal resistances of GaN devices featuring different substrate suppliers and buffers thicknesses.

To test the proposed idea, measurements of the power dissipation in gateless devices with different contact separation were performed in paper [B], and the

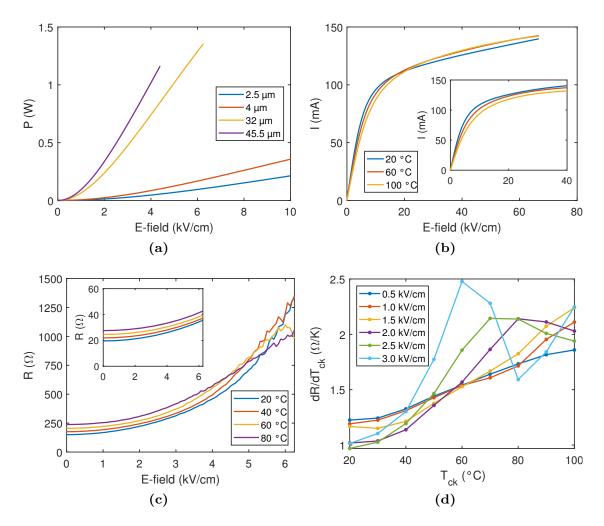

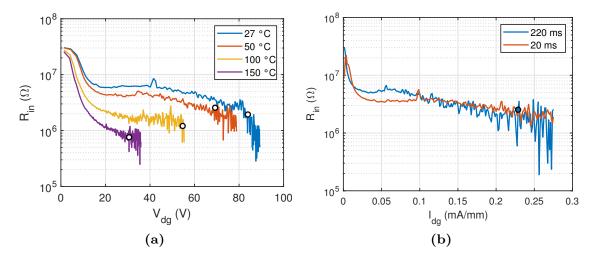

Figure 3.4: (a): power dissipation versus E-field for gateless devices with different contact separation. (b): current versus E-field at different chuck temperatures for a gateless device with  $3 \mu m$  (main figure) and  $5 \mu m$  (inset) contact separation. (c): differential resistance versus E-field for a gateless device with  $32 \mu m$  (main figure) and  $2.5 \mu m$  (inset) contact separation. (d): temperature derivative of the differential resistance versus chuck temperature at different bias voltages for a gateless device with  $32 \mu m$  contact separation.

results are shown versus the E-field in Fig. 3.4a. At a given E-field, it can be seen that the power dissipation increases with increasing contact separation, as implied by (3.1), and it can be further noted that the difference in power dissipation between the devices increases with increasing E-field. To examine the effects of a larger L on trap-related effects, the IV characteristics at different  $T_{\rm ck}$  can be inspected, which are shown in Fig. 3.4b for devices with  $L = 3 \,\mu{\rm m}$ (main figure) and  $5 \,\mu{\rm m}$  (inset). For this sample, it can be seen that the temperature coefficient at e.g.  $40 \,{\rm kV/cm}$  changes from positive (main figure) to negative (inset), which confirms that the trap-related effects are decreased when L is increased. In paper [B], devices with 30 to 32  $\mu{\rm m}$  contact separation were chosen based on the requirements of the thermal analysis and availability of similar devices on multiple engineering samples.

To further analyze the influence of trapping and self-heating in the devices, and to determine the range of bias voltages where the thermal analysis can be performed, the differential resistance (R = dV/dI) obtained from the IV measurements was utilized in paper [B]. Increased channel temperature is expected to increase R, which therefore can be used to quantify the self-heating in different devices. Fig 3.4c shows R for a device with  $L = 32 \,\mu\text{m}$  (main figure) and 2.5  $\mu\text{m}$  (inset), and it can be seen at e.g. 4 kV/cm that R has increased approximately a factor 3.1 for the 32  $\mu\text{m}$  device compared to a factor 1.3 for the 2.5  $\mu\text{m}$  device (inset). This strongly suggest the self-heating is significantly higher in the device with a longer contact separation.

Conversely, a decreasing or unchanged R at higher temperatures is an indication of electron trapping [28], which can be used to identify the maximum bias voltage suitable for thermal analysis. The 32 µm device exhibits a positive temperature coefficient up to approximately  $4.5 \,\mathrm{kV/cm}$  (Fig. 3.4c), suggesting self-heating is dominating up to this field level. However, trapping still affect Rbelow  $4.5 \,\mathrm{kV/cm}$ , which can be seen by examining the temperature derivative  $dR/dT_{\rm ck}$  in Fig. 3.4d. Although  $dR/dT_{\rm ck}$  remains positive up to 3 kV/cm, a decrease is seen at higher temperatures, which is attributed to de-trapping, and the decrease occurs at lower  $T_{\rm ck}$  for higher field levels. Thus, at e.g. 70 °C, the thermal analysis of this device should be performed up to approximately 8 V  $(2.5 \,\mathrm{kV/cm})$ , and a slightly higher voltage can be used at lower chuck temperatures. The subsequent step is to extract the thermal resistance at the selected bias voltages, and there are several electrical methods available for this purpose (section 4.1). In paper [B],  $R_{\rm th}$  was extracted using the electrical method presented in [29]. The main advantage with this method is that the extraction is made at a single independent bias condition, which can be used to inspect  $R_{th}$  versus bias voltage, gain insight of the of the extraction, and limit the extraction to the valid bias voltage range. A detailed description of the extraction of  $R_{th}$  for N-port devices is provided in [29]. In this section, a qualitative derivation is presented for the case of a gateless device (1-port). To obtain the thermal resistance, the coupled electrothermal system needs to be solved, which consists of the following equations.

$$0 = f(i(t), v(t), T_{c}(t))$$

(3.2)

$$p(t) = i(t)v(t) \tag{3.3}$$

$$T_{\rm c}(t) = p(t) * h_{\rm th}(t) + T_{\rm ck},$$

(3.4)

where f is the electric function of the device that describes the port voltage (v(t)) and current (i(t)). The function is dependent on the device temperature  $(T_c)$ , which can be determined with the linear thermal system model (3.4), where the temperature is set by the instantaneous power dissipation (p(t)), thermal impulse response  $(h_{\rm th}(t))$ , and chuck temperature  $(T_{\rm ck})$ . In [29], the electrothermal system is analyzed using a small signal approximation around an equilibrium state. This allows to derive expressions of the admittance parameters of the device as a function of the thermal transfer function and thermal (current) coefficient. In this case, the input admittance can be shown to be

$$Y_{\rm in}^{\rm e} = \frac{Y_{\rm in}^{\rm i} + Z_{\rm th}(\omega)I_{\rm q}\alpha}{1 - Z_{\rm th}(\omega)V_{\rm q}\alpha},\tag{3.5}$$

where  $Z_{\rm th}(\omega)$ , is the thermal impedance  $\alpha$  is the thermal coefficient,  $V_{\rm q}$  is the bias voltage, and  $I_{\rm q}$  is the bias current.  $Y_{\rm in}^{\rm e}$  and  $Y_{\rm in}^{\rm i}$  are the device input admittance with and without the influence of self-heating, respectively. For

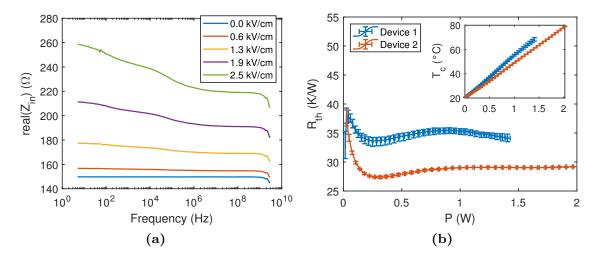

Figure 3.5: (a): real part of the input impedance versus frequency at 0 to 8 V for a gateless device with 32 µm contact separation. (b): thermal resistance versus power dissipation for two different GaN technologies. The inset shows the average channel temperature.

static voltages and currents, the thermal coefficient can be shown to be

$$\alpha = \frac{dI/dT_{\rm ck}}{R_{\rm th}V_{\rm q}dI/dT_{\rm ck}+1},\tag{3.6}$$

where  $dI/dT_{\rm ck}$  is the current derivative with respect to ambient temperature (chuck temperature). Equation (3.5) and (3.6) can be solved for  $R_{\rm th}$  at static signal conditions where  $Z_{\rm th}(0) = R_{\rm th}$ . The resulting expression for the thermal resistance is

$$R_{\rm th} = \frac{Y_{\rm in}^{\rm e} - Y_{\rm in}^{\rm i}}{dI/dT_{\rm ck}(I_{\rm q} + V_{\rm q}Y_{\rm in}^{\rm i})}.$$

(3.7)

As expected, the expression shows that the thermal resistance is zero when no self-heating occurs  $(Y_{in}^e = Y_{in}^i)$ . It can be further noted that a positive  $dI/dT_{ck}$  would lead to a negative  $R_{th}$  (since  $Y_{in}^e < Y_{in}^i$ ), showing how the effects of trapping can cause erroneous results.  $Y_{in}^e$  can be obtained from DC measurements since  $Y_{in}^e = dI(V_q)/dV$ , and the derivative  $dI/dT_{ck}$  is obtained from DC measurements at different chuck temperatures. To reduce the impact of measurement noise,  $Y_{in}^e$  can be estimated using a DC model extracted from the measurement data, as shown in paper [B].

It can be noted in (3.5) that  $Y_{in}^{e} = Y_{in}^{i}$  when  $Z_{th} = 0$  (no self-heating occurs). The thermal impedance generally exhibits a low-pass frequency characteristic, and  $Z_{th}$  therefore becomes zero at higher frequencies, usually above 100 MHz. Thus,  $Y_{in}^{i}$  can be determined using S-parameter measurements above the thermal response. Fig. 3.5a shows the real part of the input impedance  $(Z_{in})$  obtained from S-parameters measurements from 5 Hz to 3 GHz. The self-heating increases the input resistance significantly at low frequencies, and larger impact can be seen at higher bias voltages due to the higher power dissipation. From approximately 100 to 900 MHz,  $\text{Re}(Z_{in})$  is constant, suggesting  $Z_{th}(\omega) = 0$  in this region, which allows to extract  $Y_{in}^{i}$ . The parasitics of the device are small enough to have negligible influence on the measurement result at MHz frequencies. However, at higher frequencies, the parasitics cause  $Z_{in}$  to decrease, as seen at 1 to 3 GHz.

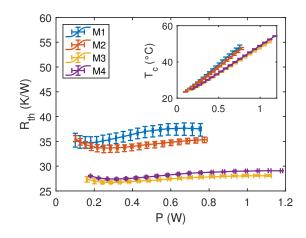

Two examples of the thermal resistance obtained by performing the outlined steps are shown in Fig. 3.5b, where  $R_{\rm th}$  is shown as a function of the dissipated power. At low P (0 to 0.15 W), the self-heating in the device is small, causing a large uncertainty (large error bars), which results in  $R_{\rm th}$  initially decreasing versus P. Above  $0.25 \,\mathrm{W}$ , sufficient self-heating occurs to enable a more accurate extraction, resulting in an approximately constant  $R_{\rm th}$  versus P. This is reasonable since the temperature rise (inset Fig. 3.5b) is not high enough to cause significant changes of the thermal properties of the device. It can be noted that the device corresponding to the blue curve exhibits a decreasing  $R_{\rm th}$  above 0.9 W, which is attributed to trapping since the corresponding bias points are in the voltage region where trapping effects could be observed in the DC characteristics. A comparison of the thermal resistance of the two devices can be made at e.g. 0.75 W, where trap-related effects on the extraction is negligible for both devices. A thermal evaluation of devices with different buffer and substrate thickness was performed in paper [B], which is discussed in section 4.2.

## Chapter 4

## Thermal Characterization and Management

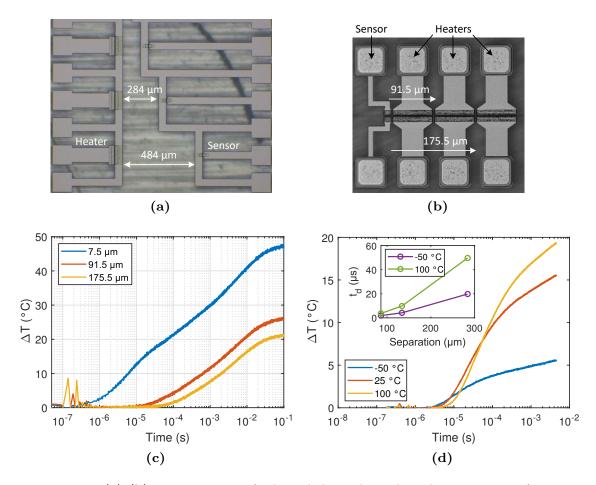

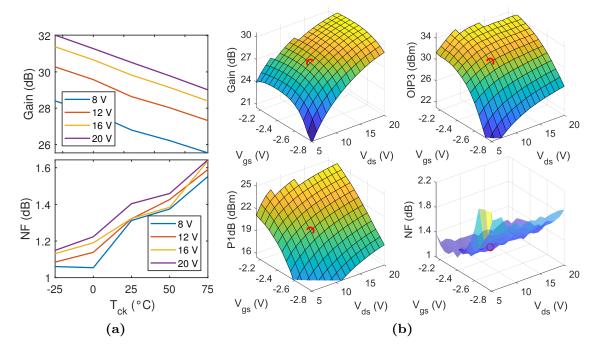

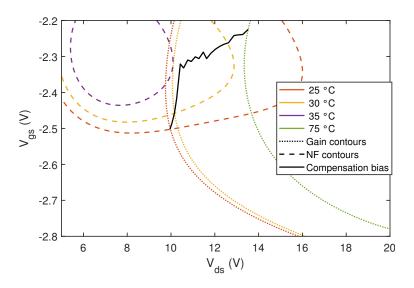

Thermal characterization is an integral part in the thermal optimization of GaN circuits and devices. At higher frequencies, the thermal challenges become more difficult due to the miniaturization of MMICs and the need to down-scale devices (to improve high frequency performance). The reduced distances increases the lateral heat coupling between circuits and components, and such thermal properties therefore needs to be accurately measured to enable improved thermal optimization and assessments. However, contemporary thermal evaluation methods are not always suitable for e.g. lateral heat spread characterizations. Optical methods suffer from transparency effects and subsurface reflections causing depth averaging and uncertainty of the measurement location. Furthermore, optical methods require optical access, and more reliable methods such as Raman spectroscopy are narrow view and not practical for measurements over large areas. Thus, there is a lack of methods to characterize heat spread properties under application-relevant conditions, such as when MMICs are packaged.