# AI-Assisted Deep-Learning-Based Design of High-Efficiency Class F Power Amplifiers

Downloaded from: https://research.chalmers.se, 2025-04-22 14:48 UTC

Citation for the original published paper (version of record):

Zhou, H., Chang, H., Widén, D. et al (2025). AI-Assisted Deep-Learning-Based Design of High-Efficiency Class F Power Amplifiers. IEEE Microwave and Wireless Technology Letters, in press. http://dx.doi.org/10.1109/LMWT.2025.3552495

N.B. When citing this work, cite the original published paper.

© 2025 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, or reuse of any copyrighted component of this work in other works.

# AI-Assisted Deep-Learning-Based Design of High-Efficiency Class F Power Amplifiers

Han Zhou<sup>®</sup>, *Member, IEEE*, Haojie Chang<sup>®</sup>, David Widén<sup>®</sup>, Ludvig Fornstedt, Gabriel Melin<sup>®</sup>, and Christian Fager<sup>®</sup>, *Fellow, IEEE*

Abstract—This article presents a deep-learning-based approach for designing Class F power amplifiers (PAs). We use convolutional neural networks (CNNs) to predict the scattering parameters of pixelated electromagnetic (EM) layouts. Using a CNN-based surrogate model and an evolutionary algorithm, we synthesize complex Class F output networks. As a proof of concept, we implement a gallium nitride (GaN) HEMT Class F PA, achieving a measured output power of 41.6 dBm and a drain efficiency of 74% at 2.9 GHz. The prototype also linearly reproduces a 20-MHz modulated signal with an 8.5-dB peak-to-average power ratio (PAPR), achieving an adjacent channel leakage ratio (ACLR) of -50.7 dBc with digital predistortion (DPD). To the best of our knowledge, this is the first deep-learning-based Class F PA design using pixelated layout structures.

Index Terms—Artificial intelligence (AI), Class F, deep learning, energy efficiency, gallium nitride (GaN), harmonic tuning, machine learning, power amplifier (PA), waveform engineering.

#### I. INTRODUCTION

THE increasing demand for higher data rates in wireless communication systems has posed significant challenges, particularly in energy efficiency. Among various components, the power amplifier (PA) is the most power-intensive element in base stations. Consequently, the development of highly efficient, waveform-engineered PAs has been a key research focus for decades [1].

The output network of a waveform-engineered PA typically consists of a matching network, a harmonic-tuning network, and a bias network. Traditional designs rely on predefined electromagnetic (EM) topologies based on prior physical insights, using lumped or distributed elements. However, these fixed topologies inherently constrain the design space, limiting the potential for globally optimal performance. Inspired by advances in integrated photonics [2], [3] and metalens antennas [4], a recent trend in microwave circuit design involves pixelating layout geometries into binary matrices [5], [6]. While previous works have explored this approach using traditional optimization and machine learning techniques, they

The authors are with the Department of Microtechnology and Nanoscience, Chalmers University of Technology, 412 96 Gothenburg, Sweden (e-mail: han.zhou@chalmers.se).

Digital Object Identifier 10.1109/LMWT.2025.3552495

often require manual feature engineering, restricting their adaptability and scalability.

Deep learning has recently emerged as a powerful framework for solving complex EM and circuit design problems, with applications spanning photonics [2], transistor modeling [7], scattering theory [8], and antenna design [9]. Unlike conventional machine learning methods, deep learning can automatically learn hierarchical representations directly from raw data, eliminating the need for manual feature extraction. In PA design, deep-learning-based surrogate models with pixelated layouts have been proposed for design of a wideband class B PA [10]. However, their application to the synthesis of output networks for highly efficient waveform-engineered PAs, such as Class F PAs, remains unexplored.

This letter presents a deep-learning-based approach using convolutional neural networks (CNNs) with pixelated layouts for synthesizing the output network of a Class F PA. The fabricated prototype circuit demonstrates a drain efficiency of 74% and an output power of 41.6 dBm at 2.9 GHz, validating the effectiveness of the proposed methodology.

# II. THEORY

Harmonic-tuned PAs maximize efficiency and output power by minimizing the overlap between drain current and voltage waveforms through precise harmonic impedance control. Among these, the Class F PA offers excellent performance with a relatively straightforward implementation. Its optimal loading conditions at the fundamental, second, and third harmonics are as follows:  $Z_{f_0} = R_{opt}$ ,  $Z_{2f_0} = 0$ , and  $Z_{3f_0} = \infty$ .

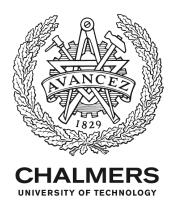

The proposed deep learning approach discretizes a planar circuit layout into a binary grid, where "1" represents metal and "0" represents nonmetal. A deep CNN model, trained on a large dataset of pixelated circuit structures and their scattering parameters (*S*-parameters), serves as a surrogate for time-consuming EM simulations. The trained model efficiently evaluates candidate solutions with an evolutionary algorithm, specifically a genetic algorithm (GA), generating pixelated circuit layouts to achieve the target *S*-parameters [10].

# A. Dataset Generation and Augmentation

Our dataset comprises 957728 two-port circuits with the *S*-parameters simulated at 21 discrete frequencies: seven evenly spaced points within 2.4–3 GHz, 4.8–6 GHz, and 7.2–9 GHz. To accelerate training, we generate eight two-port structures from a single four-port EM simulation. Using

© 2025 The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Received 28 February 2025; accepted 15 March 2025. This work was supported in part by EUREKA EURIPIDES2 InnoStar Project (Innovative Systems and Automated Design for 5G/6G Connectivity and Radar Applications), under Grant 2021-0405 and in part by Sweden's Innovation Agency (VINNOVA), Sivers Semiconductors, and Chalmers University of Technology under Grant 2022-00863. (*Corresponding author: Han Zhou.*)

Fig. 1. (a) Trained deep CNN architecture takes a binary matrix input representing the pixelated EM layout and outputs *S*-parameters across the designed frequencies. Once trained, the CNN-based surrogate model accurately predicts the *S*-parameters for any given pixelated EM structure. The forward emulator, derived from the deep CNN architecture, facilitates the inverse synthesis of arbitrary EM structures with desired *S*-parameters. (b) Equivalent output parasitic and package model of the CG2H40010F transistor used in the GA and the simulated results at the transistor's intrinsic plane.

ADS Momentum and Python automation, we simulate around 119716 pixelated four-port layouts, with ports centrally placed on each side of a  $15\times15$  grid. The circuit density follows a normal distribution with a mean of 50% and a standard deviation of 15%. Postprocessing in Python expands each four-port structure into eight two-port circuits by first converting one port into an open circuit, yielding four three-port variations, and then shorting the opposite port to represent the bias network. Finally, mirroring generates four additional circuits per configuration. To ensure reliable direct connections between pixels, we enforce a 10% overlap on each side of the metal pixels. In addition, during data generation, we ensure that 80% of the circuits include a direct connection between ports. This condition is verified using a depth-first search (DFS) algorithm implemented in Python.

# B. Deep CNN Model

As shown in Fig. 1(a), the input of the deep CNN architecture is a  $15\times15$  binary matrix and the output is the predicted *S*-parameters. Since we evaluate *S*-parameters at 21 discrete frequencies, each frequency point includes the real and imaginary components of  $S_{11}$ ,  $S_{21}$ , and  $S_{22}$ , resulting in a total of 126 values that fully characterize the *S*-parameters.

The deep CNN architecture comprises 14 convolutional layers and five fully connected (FC) layers. To address the vanishing gradient problem and enhance the model's stability and convergence speed, we incorporate a residual network structure [11]. Each convolutional layer uses 32 filters, with specific filter sizes and the corresponding residual connections detailed in Table I. The feature maps generated by the convolutional layer, enabling the FC layers to process the extracted information. Each of the five FC layers contains 2048 neurons and use the leaky rectified linear unit (ReLU) activation function to introduce nonlinearity [12]. To prevent overfitting, we apply a 30% dropout rate and *L2* regularization, followed by batch normalization [13].

We trained the deep CNN using Python's TensorFlow library on an Nvidia RTX 3090 GPU for eight hours. The final trained model is 375 MB. Once trained, the CNN-based surrogate model rapidly predicts various pixe-lated circuit topologies, significantly accelerating the design process.

TABLE I Details of the Deep CNN Architecture

| Conv. Layer                                                          | Filter Size    | Filter Number | Layer Input                  |  |  |  |  |  |

|----------------------------------------------------------------------|----------------|---------------|------------------------------|--|--|--|--|--|

| $L_1$                                                                | $12 \times 12$ | 32            | Matrix <sub>in</sub>         |  |  |  |  |  |

| $L_2$                                                                | $12 \times 12$ | 32            | $L_1$                        |  |  |  |  |  |

| $L_3$                                                                | $10 \times 10$ | 32            | $L_2$ + Matrix <sub>in</sub> |  |  |  |  |  |

| $L_4$                                                                | $10 \times 10$ | 32            | $L_3$                        |  |  |  |  |  |

| $L_5$                                                                | $8 \times 8$   | 32            | $L_4 + L_2$                  |  |  |  |  |  |

| $L_6$                                                                | $8 \times 8$   | 32            | $L_5$                        |  |  |  |  |  |

| $L_7$                                                                | $6 \times 6$   | 32            | $L_6 + L_4$                  |  |  |  |  |  |

| $L_8$                                                                | $6 \times 6$   | 32            | $L_7$                        |  |  |  |  |  |

| $L_9$                                                                | $5 \times 5$   | 32            | $L_8 + L_6$                  |  |  |  |  |  |

| $L_{10}$                                                             | $5 \times 5$   | 32            | $L_9$                        |  |  |  |  |  |

| $L_{11}$                                                             | $4 \times 4$   | 32            | $L_{10} + L_8$               |  |  |  |  |  |

| $L_{12}$                                                             | $4 \times 4$   | 32            | $L_{11}$                     |  |  |  |  |  |

| $L_{13}$                                                             | $3 \times 3$   | 32            | $L_{12} + L_{10}$            |  |  |  |  |  |

| $L_{14}$                                                             | $3 \times 3$   | 32            | $L_{13}$                     |  |  |  |  |  |

| RFin<br>50 2 pF<br>15 pF 1/12 2/10 100 2.37<br>15 rF spleide retwork |                |               |                              |  |  |  |  |  |

Fig. 2. Circuit schematic of the proposed deep-learning-aided class F PA.

Width/Length

#### C. Class F PA Output Network Synthesis

After training, the deep CNN-based surrogate model is integrated with a population-based GA [14], using the Python library pyGAD. To maintain population diversity, we use tournament selection and an injection-based mutation mechanism, introducing entirely new matrices to enhance variation. As shown in Fig. 1(b), the equivalent output parasitic and package model of the used CG2H40010F transistor is cascaded with the pixelated layout structure to form a new two-port network [15]. The optimization goal is to achieve Class F loading conditions at fundamental and harmonic frequencies at the transistor's intrinsic plane.

### **III. PROTOTYPE DESIGN**

The complete schematic of the proposed deep-learningaided Class F PA prototype circuit is shown in Fig. 2. The circuit is implemented on a 20-mil Rogers 4350B substrate,

Fig. 3. Photograph of the fabricated deep-learning-aided Class F PA prototype.

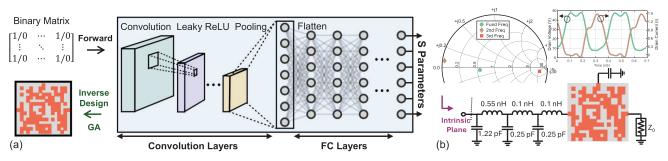

Fig. 4. (a) Measured and simulated small-signal performance, (b) measured large-signal performance at 2.9 GHz, and (c) measured and simulated large-signal performance across frequencies for the fabricated Class F PA prototype.

using a 10-W packaged gallium nitride (GaN) HEMT transistor from Macom as the active device. The output network, designed with the proposed method, features a compact  $15 \times 15$ pixelated structure, with each pixel having dimensions of  $1.2 \times 1.2$  mm to balance pixel coupling considerations and training resource constraints. Integrated with the transistor's parasitic and package network, this layout provides the necessary fundamental and higher order harmonic impedances for Class F operation. At the saturated power level, the prototype demonstrates a distinct Class F PA waveform at the intrinsic plane, as illustrated in Fig. 1(b).

# **IV. MEASUREMENT RESULTS**

Fig. 3 presents a photograph of the fabricated Class F PA. During the measurements, the drain bias voltage of the PA is

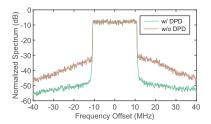

Fig. 5. Normalized spectrum of the prototype circuit with a 20-MHz, 8.5-dB PAPR OFDM signal at 2.9 GHz before and after applying DPD.

TABLE II Summary of State-of-the-Art High-Efficiency PAs

| Ref.                                                                | Arch.                 | f <sub>0</sub><br>(GHz) | $\eta_{\mathrm{SAT}}$ (%) | P <sub>SAT</sub><br>(dBm) | Gain<br>(dB) | ACLR<br>(dBc) |  |

|---------------------------------------------------------------------|-----------------------|-------------------------|---------------------------|---------------------------|--------------|---------------|--|

| [16] 2022                                                           | class E               | 2.5                     | 70                        | 40.8                      | 15.1         | N.A.          |  |

| [17] 2022                                                           | class F               | 1.7                     | $72^{*}$                  | 41.7                      | 9.2          | -49.0         |  |

| [18] 2023                                                           | class F <sup>-1</sup> | 3.0                     | $65^{*}$                  | 38.4                      | 10.3         | N.A.          |  |

| [19] 2023                                                           | class F <sup>-1</sup> | 2.3                     | 77                        | 40.8                      | 12.3         | -56.1         |  |

| [20] 2024                                                           | class F <sup>-1</sup> | 3.7                     | 71                        | 40.3                      | 10.6         | -46.4         |  |

| [21] 2024                                                           | class J <sup>HI</sup> | 1.7                     | 82                        | 40.5                      | 14.3         | N.A.          |  |

| This Work                                                           | class F               | 2.9                     | <b>74</b>                 | 41.6                      | 11.2         | -50.7         |  |

| $a^{\rm HI}$ stands for harmonic injection, $b^{*}$ PAE is reported |                       |                         |                           |                           |              |               |  |

$a^{111}$  stands for harmonic injection,  $b^*$  PAE is reported

set to  $V_{\rm DD} = 28$  V, and the gate bias voltage is fixed at  $V_{\rm GG} =$ -2.85 V. Fig. 4 illustrates the simulated and measured smallsignal and large-signal performance of the fabricated prototype circuit. The results show excellent agreement between the measured and simulated data across the design frequencies. At 2.9 GHz, the prototype achieves a measured drain efficiency of 74% and an output power of 41.6 dBm. The performance of the prototype is also assessed using a 20-MHz orthogonal frequency division multiplexing (OFDM) signal, with an 8.5-dB peak-to-average power ratio (PAPR). As shown in Fig. 5, the adjacent channel leakage ratio (ACLR) of the prototype improves from -32.6 to -50.7 dBc after applying digital predistortion (DPD) [22]. The performance of the prototype PA is benchmarked against state-of-the-art high-efficiency PAs in Table II, which exhibits its excellent efficiency compared with previously published designs.

# V. CONCLUSION

In this article, we present a deep-learning-based approach for designing high-efficiency Class F PAs. The design process combines a deep CNN architecture as a forward model to predict the behavior of pixelated EM structures with an evolutionary algorithm for inverse design. As a proof of concept, we design and fabricate a GaN HEMT Class F PA prototype using the proposed approach. When used in combination with a standard DPD, the prototype achieves excellent efficiency and linearity, satisfying the stringent requirements of modern wireless communication standards.

#### REFERENCES

S. Kim, J. Moon, Y. Park, D. Minn, and B. Kim, "Saturated PAs for high efficiency: Operation of saturated amplifiers having the optimum voltage waveform to achieve maximum efficiency," *IEEE Microw. Mag.*, vol. 19, no. 7, pp. 116–133, Nov. 2018.

- [2] M. H. Tahersima et al., "Deep neural network inverse design of integrated photonic power splitters," *Sci. Rep.*, vol. 9, no. 1, p. 1368, Feb. 2019.

- [3] W. Ma, Z. Liu, Z. A. Kudyshev, A. Boltasseva, W. Cai, and Y. Liu, "Deep learning for the design of photonic structures," *Nature Photon.*, vol. 15, no. 2, pp. 77–90, 2020.

- [4] P. Liu, L. Chen, and Z. N. Chen, "Prior-knowledge-guided deeplearning-enabled synthesis for broadband and large phase shift range metacells in metalens antenna," *IEEE Trans. Antennas Propag.*, vol. 70, no. 7, pp. 5024–5034, Jul. 2022.

- [5] Z. Ni, J. Xia, X. Y. Zhou, W. Kong, H. Zhang, and X.-W. Zhu, "Optimization design of ultra-wideband PA with fragment-type structure using load impedance overlap and geometrical constraint," *IEEE Trans. Microw. Theory Techn.*, early access, Jan. 10, 2025, doi: 10.1109/ TMTT.2024.3524417.

- [6] W. Kong et al., "Optimization design of broadband Doherty PA using fragment-type matching network based on dual-state impedance objective function," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 71, no. 4, pp. 1809–1813, Apr. 2024.

- [7] N. Calik, F. Güneş, S. Koziel, A. Pietrenko-Dabrowska, M. A. Belen, and P. Mahouti, "Deep-learning-based precise characterization of microwave transistors using fully-automated regression surrogates," *Sci. Rep.*, vol. 13, no. 1, p. 1445, Jan. 2023.

- [8] K. Xu, L. Wu, X. Ye, and X. Chen, "Deep learning-based inversion methods for solving inverse scattering problems with phaseless data," *IEEE Trans. Antennas Propag.*, vol. 68, no. 11, pp. 7457–7470, Nov. 2020.

- [9] L. Xiao, W. Shao, F. Jin, B. Wang, and Q. H. Liu, "Inverse artificial neural network for multiobjective antenna design," *IEEE Trans. Antennas Propag.*, vol. 69, no. 10, pp. 6651–6659, Oct. 2021.

- [10] E. A. Karahan, Z. Liu, and K. Sengupta, "Deep-learning-based inversedesigned millimeter-wave passives and power amplifiers," *IEEE J. Solid-State Circuits*, vol. 58, no. 11, pp. 3074–3088, Nov. 2023.

- [11] K. He, X. Zhang, S. Ren, and J. Sun, "Deep residual learning for image recognition," in *Proc. IEEE Conf. Comput. Vis. Pattern Recognit.* (CVPR), Jun. 2016, pp. 770–778.

- [12] V. Nair and G. E. Hinton, "Rectified linear units improve restricted Boltzmann machines," in *Proc. 27th Int. Conf. Mach. Learn.*, 2010, pp. 807–814.

- [13] N. Srivastava, G. Hinton, A. Krizhevsky, I. Sutskever, and R. Salakhutdinov, "Dropout: A simple way to prevent neural networks from overfitting," *J. Mach. Learn. Res.*, vol. 15, no. 1, pp. 1929–1958, 2014.

- [14] D. S. Weile and E. Michielssen, "Genetic algorithm optimization applied to electromagnetics: A review," *IEEE Trans. Antennas Propag.*, vol. 45, no. 3, pp. 343–353, Mar. 1997.

- [15] H. Zhou, J.-R. Perez-Cisneros, B. Langborn, T. Eriksson, and C. Fager, "Design of a compact GaN power amplifier with high efficiency and beyond decade bandwidth," *IEEE Microw. Wireless Compon. Lett.*, vol. 32, no. 12, pp. 1439–1442, Dec. 2022.

- [16] C. Yang, K. Jin, D. Mao, and X. Zhu, "Precise configuration of transmission line class-E power amplifier operating at GHz frequency," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 5, pp. 6396–6404, Oct. 2022.

- [17] K. Han and L. Geng, "Enhancing efficiency and linearity of continuous class-F<sub>3</sub> power amplifier with peak-clipped current waveform," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 2, pp. 1423–1431, Feb. 2022.

- [18] S. Yang et al., "A high-efficiency inverse class-F GaN MMIC power amplifier with compact output matching network," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 70, no. 10, pp. 3767–3771, Oct. 2023.

- [19] C. Chu, V. Tamrakar, S. K. Dhar, T. Sharma, J. Mukherjee, and A. Zhu, "High-efficiency class-iF<sup>-1</sup> power amplifier with enhanced linearity," *IEEE Trans. Microw. Theory Techn.*, vol. 71, no. 5, pp. 1977–1989, May 2023.

- [20] X. Ji et al., "High-efficiency and high-linearity class-F<sup>-1</sup> power amplifier with AM-AM and AM-PM improvement," *IEEE Microw. Wireless Technol. Lett.*, vol. 35, no. 1, pp. 91–94, Jan. 2025.

- [21] C. Liu, Q. Sun, H.-D. Wu, H. Zhang, and F. M. Ghannouchi, "Efficiency enhancement of class-J power amplifiers by injecting second harmonic into the gate and drain node simultaneously," *IEEE Microw. Wireless Technol. Lett.*, vol. 34, no. 12, pp. 1347–1350, Dec. 2024.

- [22] D. R. Morgan, Z. Ma, J. Kim, M. G. Zierdt, and J. Pastalan, "A generalized memory polynomial model for digital predistortion of RF power amplifiers," *IEEE Trans. Signal Process.*, vol. 54, no. 10, pp. 3852–3860, Oct. 2006.