# A Ka-Band Doherty-Like Non-Load Modulated Power Amplifier

Downloaded from: https://research.chalmers.se, 2025-05-09 15:19 UTC

Citation for the original published paper (version of record):

Liu, E., Zhou, H., Fager, C. et al (2025). A Ka-Band Doherty-Like Non-Load Modulated Power Amplifier. IEEE Journal of Solid-State Circuits, In Press. http://dx.doi.org/10.1109/JSSC.2025.3532578

N.B. When citing this work, cite the original published paper.

© 2025 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, or reuse of any copyrighted component of this work in other works.

# A Ka-Band Doherty-Like Non-Load Modulated Power Amplifier

Edward Liu, *Graduate Student Member, IEEE*, Han Zhou *Member, IEEE*, Christian Fager *Fellow, IEEE*, and Hua Wang, *Fellow, IEEE*

Abstract—This article describes a three-way power amplifier (PA) topology that achieves broadband power back-off (PBO) efficiency enhancement without using active load modulation on the Main PA or supply modulation. This allows the PA to avoid the classic trade-off between load modulation and bandwidth that is typical among Doherty PAs. Unlike Doherty PAs, the proposed PA has both its voltage and current drive profiles reach a maximum at PBO, which causes the impedance of the Main PA to be constant across the entire input drive. This is achieved with a novel parallel-series output matching network (OMN) that primarily utilizes coupled-line baluns. A prototype is fabricated in the GlobalFoundries 45nm RFSOI and achieves a  $P_{\rm avg}$  and  ${\rm PAE}_{\rm avg}$  of 6.45 - 12.61 dBm and 5.9 - 16.4% from 25 - 40 GHz, respectively. With a 200 MHz signal,  $P_{\rm avg}$  and  ${\rm PAE}_{\rm avg}$  are 5.58 - 11.1 dBm and 4.8 - 13.3%, respectively.

Index Terms—Load modulation, doherty, power amplifier (PA), broadband, CMOS, fifth generation (5G), frequency range 2 (FR2), power-added efficiency (PAE), power back-off (PBO), millimeter-wave (mm-wave).

#### I. Introduction

ILLIMETER-wave (mm-wave) 5G promises multi-Gbps data rates by harnessing the vast spectral resources in frequency bands such as n257 - n261 (24.25 -43.5 GHz) [1]. As seen in Fig. 1, different regions in the world are allocated different bands, highlighting the need for broadband RF front-ends. A broadband power amplifier (PA) that can cover multiple bands enables frequency-agile radio front-end deployment and reduces costs through increased re-usability [2], [3]. Furthermore, mm-wave communications rely on orthogonal frequency-division multiplexing (OFDM) to combat hostile environmental effects such as multipath fading [4]. However, OFDM drastically increases the peakto-average power ratio (PAPR) of the RF signal, placing an extra burden on the PA. Since the PA must operate in PBO, the average efficiency when transmitting a high PAPR signal suffers. Therefore, one research trend is to develop architectures that are simultaneously broadband and efficient at PBO [5].

Doherty PAs are a popular choice for achieving PBO efficiency enhancement, but they usually suffer from narrow bandwidths caused by the required active load modulation and impedance inverting networks [6], [7], [8], [9], [10], [11],

Fig. 1. 5G NR FR2 frequency allocation for different regions.

[12], [13], [14]. This problem is exacerbated with higher order Doherty PAs, as the required load modulation range and impedance transformation ratio is significantly larger [15], [16], [17], [18], [19]. Recently, main/auxiliary role-exchange has been explored as a bandwidth enhancement technique [20], [21], [22], [23]. However, one drawback in this technique is the large gain variation across frequency and the need for extra reconfiguration circuitry, which increases the complexity.

Another way of achieving broadband performance is to eliminate the need for load modulation entirely. One way of achieving this is with the sequential load modulated balanced amplifier [24], [25], [26], [27], [28], [29]. While most of the prior works are implemented at sub-6 GHz, recently this technique has also been demonstrated at Ka-band in CMOS [30]. However, the fractional bandwidth (FBW =  $\frac{f_2-f_1}{f_c}$ ) of this design (15%) is much lower compared to the designs at sub-6 GHz, where FBWs of >100% have been demonstrated. This is possibly due to the extra output baluns needed to interface with the single-ended quadrature coupler, which also increases the loss of the output matching network.

The distributed efficient power amplifier (DEPA) architecture removes the load modulation and does not need a quadrature coupler [31]. However, the prototype DEPA PA in [31] uses six auxiliary amplifiers, which is not conducive to on-chip implementations and leads to large output combiner loss. Furthermore, the Main PA is furthest from the load, which results in a high combiner loss and lower PBO efficiency. A design that reduces the number of auxiliary amplifiers to four is presented in [32], achieving higher efficiency and output power, but with a reduced FBW of 38%, compared to the 71% of [31]. A new, Doherty-like architecture with no load modulation is presented in [33] uses two auxiliary amplifiers, but achieves a smaller FBW of 33%. In this spirit, an alternative architecture is explored that minimizes the number of auxiliary paths required, but also achieving the desired non-load modulated behavior over a wider bandwidth.

This article proposes a parallel-series architecture with two auxiliary paths that can achieve a FBW of 48%. As an

E. Liu and H. Zhou are co-first authors on this work with equal contribution. (Corresponding author: Edward Liu and Han Zhou)

E. Liu and H. Wang are with the Department of Information Technology and Electrical Engineering at ETH Zürich. email: edwliu@iis.ee.ethz.ch, hua.wang@iis.ee.ethz.ch.

H. Zhou and C. Fager are with Chalmers University of Technology, Sweden.

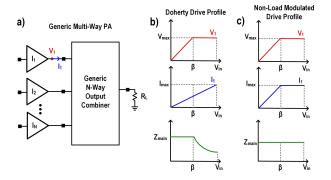

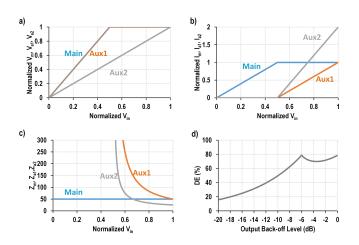

Fig. 2. (a) A generic schematic of a multi-way PA. (b) Voltage/Current drive profile of a Doherty PA. (c) Voltage/current drive profile of the proposed PA.

extension of [34], this article includes an expanded theoretical analysis of the proposed novel output combiner. The demonstrated PA, implemented in GlobalFoundries 45nm CMOS SOI technology, covers 25 - 40 GHz, which occupies the entire Kaband and addresses four 5G FR2 bands (n257, n258, n260, and n261) without any tuning elements or main/auxiliary PA role-exchange. Section II describes the difference between the traditional Doherty current/voltage drive profile, and that of the proposed network. Section III introduces the circuit details of the PA. Section IV describes the measurement results and compares the performance with state-of-the-art CMOS PAs. Lastly, the conclusion is given in section V.

## II. NON-LOAD MODULATED OUTPUT ARCHITECTURE

The current/voltage drive profiles of the proposed architecture and the traditional Doherty architecture is shown in Fig. 2. First, Fig. 2(a) describes a generic multi-way PA, and if this is designed as a Doherty PA then the current/voltage drive profile of the Main PA will look similar to Fig. 2(b). For a Doherty PA, the output voltage  $V_1$  rises as the input drive increases, and is maximized at some back-off point  $\beta$ , leading to a high efficiency in the region from  $\beta$  to peak output power. It is important to note here that the current  $I_1$  does not reach its maximum until the PA reaches its peak drive. Therefore, the

impedance seen by the Main PA,  $Z_{\rm main}$ , is modulated to a lower value in the high power region.

In contrast, the drive profile of the proposed PA is shown in Fig. 2(c). The key difference is that the current  $I_1$  maximizes at  $\beta$ , which allows  $Z_{main}$  to remain independent of the input drive. In this design,  $\beta = 0.5$ . At the same time, the voltage swing is maximized at back-off, which ensures a high efficiency, just as in the case of a Doherty PA.

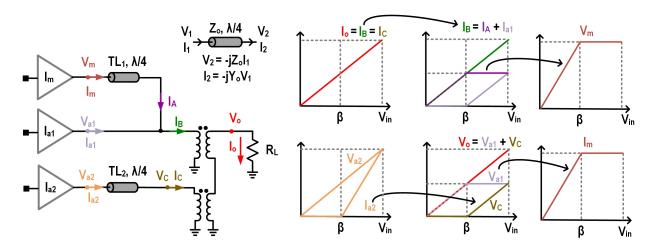

An example of a PA architecture that can achieve this drive profile is shown in Fig. 3. First, for a  $\lambda/4$  transmission line, the voltage and current relationships at its terminals is given by

$$\begin{bmatrix} V_2 \\ I_2 \end{bmatrix} = \begin{bmatrix} 0 & -jZ_o \\ -jY_o & 0 \end{bmatrix} \begin{bmatrix} V_1 \\ I_1 \end{bmatrix} \tag{1}$$

where  $Z_o$  is the characteristic impedance of the line. With this information, the correct drive profile of the Main PA can be determined. Since the output is series combined,  $I_o = I_B = I_C$ , and  $V_o = V_{a1} + V_C$ . Additionally, both  $I_o$  and  $V_o$  increase linearly with input drive up to the peak point, as the PAs are modeled as ideal current sources. Then, both  $I_{a1}$  and  $I_{a2}$  only turn on in the high power region. This means that  $V_C$ , which is on the other side of  $TL_2$ , must follow  $I_{a2}$ . Then,  $V_{a1}$  can be determined as  $V_o$  -  $V_C$ . Lastly,  $I_m$  must follow  $V_{a1}$ , which means it reaches its maximum at  $\beta$ . Furthermore,  $I_A$  can be determined as  $I_B$  -  $I_{a1}$ . Since  $V_m$  must follow  $I_A$ , this means that  $V_m$  must also reach its maximum at  $\beta$ . Therefore, the drive profile of the Main PA is shown to behave as that of Fig. 2(c).

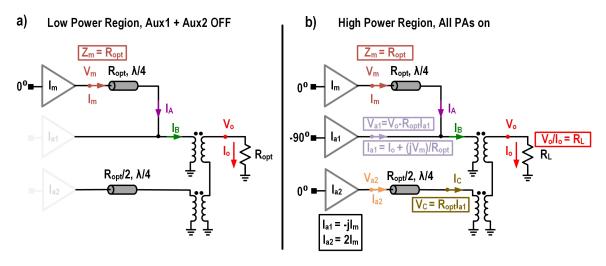

This output network can be further analyzed by dividing it into two operation regions, as shown in Fig. 4. The transmission lines  $TL_1$  and  $TL_2$  have values of  $R_{\rm opt}$  and  $\frac{R_{\rm opt}}{2}$ , respectively.

1) Low power region: In this region, only the Main PA is on. Since  $I_{\rm a1}$  and  $I_{\rm a2}$  are open circuited, the impedance presented to the Main PA  $Z_{\rm m}$  can simply be determined directly as

$$Z_m = \frac{V_m}{I_m} = R_{opt} \tag{2}$$

Fig. 3. Drive profile breakdown at different nodes in the output matching network.

Fig. 4. (a) Low power region. (b) High power region. All PA paths are on, and the impedance  $Z_{\rm m}$  is still  $R_{\rm opt}$ .

2) High power region: At this point, both auxiliary paths  $(I_{a1} \text{ and } I_{a2})$  turn on, and the currents are sized as

$$I_{a1} = -jI_m \tag{3}$$

$$I_{a2} = 2I_m \tag{4}$$

Note that this is a key difference compared to higher-order Doherty PAs, where the auxiliary paths are turned on sequentially. At the same time the auxiliary paths turn on, the Main PA reaches voltage saturation, leading to an efficiency peak. By applying (1), the voltage at  $V_{\rm C}$  and  $V_{\rm al}$  can be determined as

$$V_C = -j\frac{R_{opt}}{2}I_{a2} = R_{opt}I_{a1}$$

(5)

$$V_{a1} = V_o - R_{opt} I_{a1} \tag{6}$$

and the Main PA current  $I_{\rm m}$  is calculated as

$$I_{m} = \frac{V_{a1}}{-jR_{opt}} = j(\frac{V_{o}}{R_{opt}} - I_{a1})$$

(7)

Again by applying (1),  $I_{\rm a1}$  can be determined in terms of  $V_{\rm m}$  and  $I_{\rm o}$  as

$$I_{a1} = I_o + \frac{j}{R_{out}} V_m \tag{8}$$

Lastly, by combining (8) with (7) the impedance  $Z_{\rm m}$  is calculated as

$$Z_m = \frac{V_m}{I_m} = R_{opt} \tag{9}$$

which is exactly the same as (2), confirming that in either low or high power region, the load of the Main PA is constant. The impedance seen by the auxiliary PAs at peak power can be derived in a similar way (see Appendix), and provided below as

$$Z_{a1} = R_{opt} \tag{10}$$

$$Z_{a2} = \frac{R_{opt}}{2} \tag{11}$$

Therefore, at peak power all PA paths are matched to their optimum load impedance. To summarize, the drive profiles for

Fig. 5. (a) Voltage drive profile. (b) Current drive profile. (c) Non-load modulation behavior. (d) Ideal drain efficiency vs. power back-off level.

all three PA paths are shown in Fig. 5(a) - (b). The impedance seen by each PA is shown in Fig. 5(c), and the theoretical drain efficiency enhancement is shown in Fig. 5(d).

At this point, it is necessary to understand the bandwidth limitations imposed by the  $\lambda/4$  lines. It can be shown that at PBO, the impedance seen by the main PA can be written as

$$Z_m = \frac{1 - j(\frac{1}{2}\cot(\theta) - \tan(\theta))}{\frac{3}{2} + j\tan(\theta)}$$

(12)

and the real and imaginary components can be determined as

$$\operatorname{Re}[Z_m] = R_{opt} \frac{1 + \tan^2(\theta)}{\frac{9}{4} + \tan^2(\theta)}$$

(13)

Imag[

$$Z_m$$

] =  $R_{opt} \frac{-\frac{1}{2}(\frac{3}{2}\cot(\theta) - \tan(\theta))}{\frac{9}{4} + \tan^2(\theta)}$  (14)

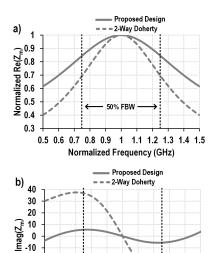

where  $\theta$  is a frequency dependent parameter. This can be compared with a standard two-way Doherty that achieves load modulation from  $2R_{\rm opt} \to R_{\rm opt}$ . The normalized real part of the impedance is shown in Fig. 6(a), and the imaginary part is shown in Fig. 6(b). The real part of the impedance is

Fig. 6. (a) Normalized real part and (b) imaginary part of the impedance vs. frequency seen by the main PA at back-off of the proposed design compared to a standard two-way parallel Doherty.

Normalized Frequency (GHz)

0.5 0.6 0.7 0.8 0.9

1 1.1 1.2 1.3 1.4 1.5

-20

-30

-40

normalized, since the Doherty PA performs load modulation whereas our design does not. Over a 50% FBW, our proposed network sees a decrease in the real part from the peak value to  $0.85\times$  of that. However, the standard two-way parallel Doherty sees a drop of  $0.7\times$ . This means that if  $R_{\rm opt}$  =  $50\Omega$ , our network only sees a reduction from  $50\Omega \to 42.5\Omega$  whereas the Doherty network sees a reduction from  $100\Omega \to 70\Omega$ . Furthermore, over the same 50% FBW, the imaginary component of the impedance is also improved drastically. As shown in Fig. 6(b), the variation is reduced by over  $6\times$ . This is important because a large reactive impedance component will degrade the PA performance severely, and may in fact be the overall limiting factor.

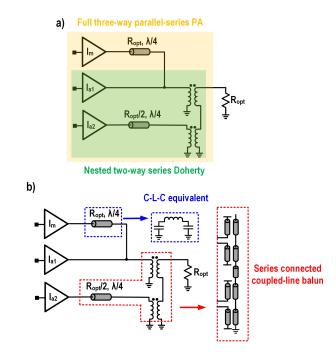

As mm-wave CMOS PAs are usually implemented differentially, a few modifications to the architecture of Fig. 3 are needed. As shown in Fig. 7(a), the Aux1 and Aux2 paths comprise of a nested two-way series Doherty within the overall three-way parallel-series PA. This topology has been well studied in [35], and the broadband coupler balun-based approach can be easily adopted for this PA. These baluns absorb the PA output capacitance over a broad bandwidth, and allow for easy large signal matching and DC biasing. The  $\lambda/4$  transmission line interfacing the Main PA can be realized as a lumped C-L-C network. This network can inherently absorb the PA output capacitance in its design, therefore only an extra inductor and capacitor is needed. The L and C values can be determined as

$$L = \frac{Z_o}{\omega} \tag{15}$$

$$C = \frac{1}{Z_o \omega} \tag{16}$$

Finally, one additional advantage of this output network is that despite needing three PA paths, only two baluns are required.

Fig. 7. (a) Full PA matching network, with sub series Doherty highlighted. (b) Converting ideal components to on chip equivalents.

The L-C network interfacing the main PA can be placed in the space between the two baluns. Therefore, the overall chip area can be minimized. It should be noted that the lumped element approximation of a  $\lambda/4$  line will also limit the bandwidth of the output network, along with the transistor parasitic capacitance. However, these are limitations due to implementation, and not limitations inherent to the topology such as those illustrated in Fig. 6.

#### III. CIRCUIT IMPLEMENTATION

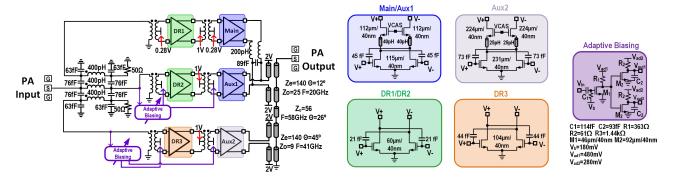

The full circuit of the PA is shown in Fig. 8. The input signal is first split into three paths with proper phase shift by the input coupler. Each of the three paths consists of a common-source (CS) driver and a cascode PA stage. The Main:Aux1:Aux2 sizing ratio is 1:1:2. An adaptive biasing circuit is used to control the turn-on point of the Aux1 and Aux2 paths [21]. Lastly, the signals in each path are recombined through the output combiner. The next two subsections will describe the output matching network, input splitter, and adaptive biasing.

# A. Output Network

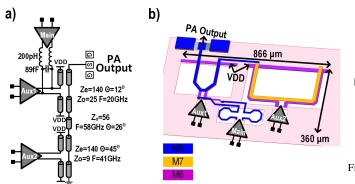

As shown in Fig. 9(a), coupled-line baluns are used to interface with both Aux1 and Aux2 PAs [2]. The Main path is connected through a CLC-based transmission line, which is also used to absorb the output capacitance of the Main PA. The balun interfacing the Aux2 PA uses adjacent metal layers (M6 and M7) for high coupling, which is necessary to achieve a low odd-mode impedance  $Z_{\rm o}$  (Fig. 9(b)). On the other hand, the balun interfacing the Aux1 PA requires a much larger  $Z_{\rm o}$ , so non-adjacent metal layers (M6 and M8) are used.

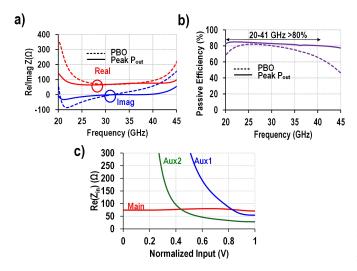

Figure 10(a) shows that over the 25 - 40 GHz frequency range,  $Z_{\rm m}$  is almost constant, confirming that this performance

Fig. 8. Full schematic of the PA.

Fig. 9. (a) Schematic of the output network. (b) 3-D EM model.

Fig. 10. (a) Impedance seen by the Main PA at back-off and peak power. (b) Passive efficiency. (c) Real part of the load impedance of the three PA paths over input drive at 33 GHz.

can be maintained over a large frequency range. The passive efficiency is  $>\!80\%$  from 20 - 41 GHz at peak  $P_{\rm out}$  and  $>\!60\%$  at back-off as shown in Fig. 10(b). Lastly, Fig. 10(c) confirms that the real part of the Main PA impedance stays constant over the input drive. Furthermore, both auxiliary paths see an impedance close to their optimal values. Ideally, the Aux1 impedance should be equal to that of the Main at peak drive,

Fig. 11. (a) Schematic of the input splitter. (b) 3-D EM model.

Fig. 12. (a) Simulated phase relationships between the different paths. (b) Simulated S21, S31 and S41. (c) Isolation between ports 2 and 3. (d) Input reflection parameters for all six ports.

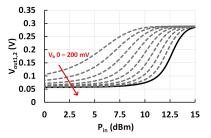

Fig. 13. Adaptive biasing ramp-up for different  $V_{\rm b}$  values.

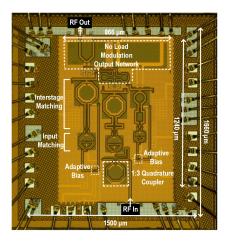

Fig. 14. Die photo of the PA.

but in practice it is somewhat lower due to the nonidealities introduced by the EM simulated matching network.

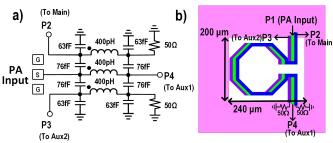

#### B. Input Splitter

It is generally more difficult to design input splitting networks for three-way PAs compared to two-way PAs, especially those requiring a phase difference between the different paths and over a wide frequency range. This results in bulky networks involving multiple components, which increases the chip area. For example, the design in [17] utilizes a combination of a two-way Wilkinson divider and a single-ended quadrature hybrid. Similarly, [15] uses a Wilkinson divider, a quadrature hybrid, and additional 90° and phase compensation lines.

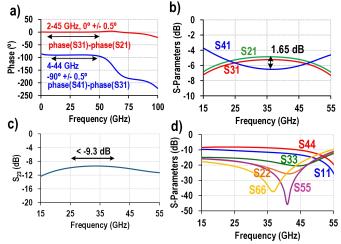

The transformer-based quadrature coupler design in [36] can be extended to support an extra coupled port, as shown in Fig. 11(a). This network uses three coupled inductors that can be overlayed, drastically reducing the total footprint (Fig. 11(b)) while simultaneously providing the correct phase relationships between the three PA paths as shown in Fig. 12(a). The total area required by the three coupled inductors is only 0.24mm  $\times$  0.2mm, which is about the same size as a single interstage matching transformer. The coupling between pairs of adjacent inductors is about k = 0.66. The phase difference between the Main and Aux2 is close to 0°, and the phase difference between the Aux1 and Aux2 (and Main) paths is -90°. This fulfills the phase requirement, as described in Fig. 4(b). Furthermore, the transmission parameters are shown in Fig. 12(b). Across the bandwidth, the power split between the three PA paths is relatively equal. Additionally, the isolation between the two coupled ports is shown in Fig. 12(c), and it is <-9.3 dB from 25 - 40 GHz. Lastly, Fig. 12(d) shows the input reflection parameters for all six ports, which are all <-10 dB in the bandwidth of interest, with the exception of  $S_{44}$ , which is <-8.1 dB.

# C. Adaptive Biasing

Adaptive biasing is normally used in Doherty PAs to control the load modulation through the auxiliary path ramp-up. In this PA, it serves a similar function by keeping the Aux1 and Aux2

Fig. 15. Modulation measurement setup.

paths off, until the high power region, at which point the PAs are ramped up to class-AB biasing. By controlling the voltage  $V_b$  as shown in Fig. 13, the turn-on point of the Aux1/2 paths can be controlled. The adaptive biasing is applied to both the driver and the PA stage to ensure that there is no accidental turn-on of any path in the low power region. From simulations, the bandwidth of the adaptive bias circuit is approximately 2.2 GHz, which limits the modulation bandwidth to about 700 MHz when considering the AM bandwidth [37]. To improve the bandwidth of the adaptive biasing, techniques such as inductive peaking can be used [38], but may result in larger chip area.

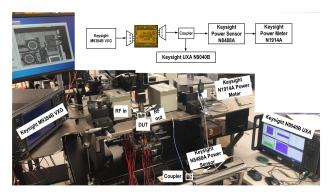

#### IV. MEASUREMENTS

The chip is fabricated in the GlobalFoundries 45RFSOI process, and the die photo is shown in Fig. 14. Measurements are conducted with RF probing and DC pads are wirebonded to a PCB. The modulation measurement setup is shown in Fig. 15. The modulated signal is generated by a M9384B VXG, and the amplified output is de-modulated by a N9040B UXA spectrum analyzer running 89600 Vector Signal Analysis (VSA) software. Output power is measured with a N1914A power meter and N8488A power sensor. The large signal continuous-wave (CW) setup is similar, with a Keysight E8267D replacing the VXG. The UXA is not used during CW tests.

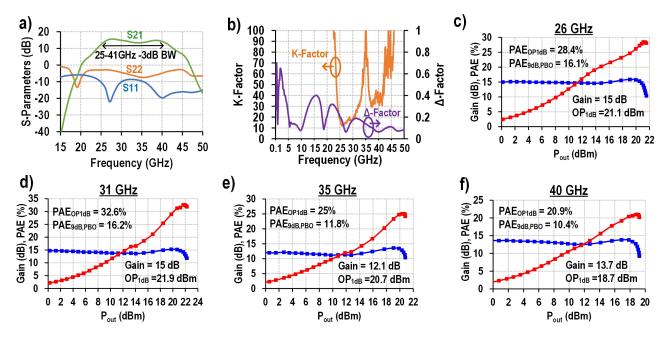

### A. Single Tone Measurements

Figure 16(a) and (b) shows the measured S-parameters and K- $\Delta$  stability factor, respectively. The  $S_{21}$  -3dB bandwidth is 25 - 41 GHz, demonstrating the broadband capabilities of this PA. The  $S_{11}$  is < -10 dB from 25 - 30 GHz and 35 - 50 GHz. From 30 - 35 GHz, the  $S_{11}$  is < -8.7 dB. The PA also demonstrates unconditional stability across the entire measurement frequency range, as shown in Fig. 16(b).

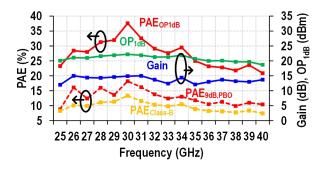

Figures 16(c) - (f) show the large signal CW measurements as a function of output power for different frequencies. Across the entire bandwidth, this PA demonstrates improved back-off efficiency, validating the broadband, PBO efficiency enhancement concept. A summary of the CW measurement results from 25 - 40 GHz is shown in Fig. 17. This PA achieves a power gain of 12 - 15 dB, an  $\mathrm{OP}_{1\mathrm{dB}}$  of 18.7 - 22.2 dBm and a PAE at the  $\mathrm{OP}_{1\mathrm{dB}}$  of 20.9 - 37.6%. The 9 dB PBO

Fig. 16. Small signal measurements of (a) S-parameters and (b) stability. Large signal CW measurements at (c) 26 GHz, (d) 31 GHz, (e) 35 GHz, and (f) 40 GHz.

Fig. 17. Summary of CW measurement results from 25 - 40 GHz.

PAE is 8.8 - 18.2%. The PAE at 9dB PBO of hypothetical class-B PA with the same  $PAE_{\mathrm{OP1dB}}$  is also plotted in yellow, demonstrating that the proposed design can achieve better PAE at PBO across frequency.

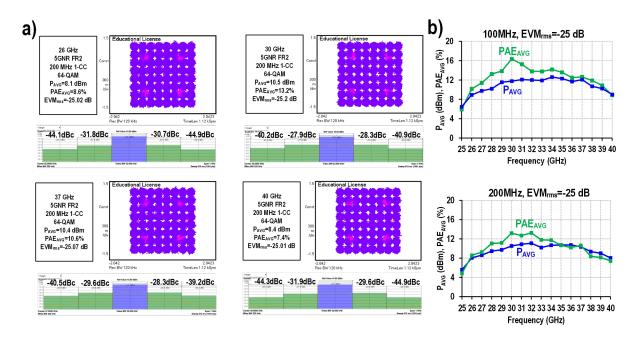

#### B. Modulation Measurements

The chip is tested with 5G NR FR2 64-QAM OFDM signals with 100 MHz and 200 MHz bandwidth. This signal has a PAPR of approximately 9.6 dB. Figure 18(a) shows the constellation and spectrum at different frequencies, and Fig. 18(b) shows the performance summary across frequency. With a 100 MHz signal and at an EVM $_{\rm rms}$  of -25 dB, the PA achieves an average  $P_{\rm out}$  and PAE of 6.45 dBm - 12.61 dBm and 5.9% - 16.4% from 25 - 40 GHz. The best overall performance is achieved at 30 GHz, with a PAE $_{\rm avg}$  of 16% and a  $P_{\rm avg}$  of 13.6 dBm. With a 200 MHz signal at the same EVM $_{\rm rms}$  and frequency range, the PA achieves an average  $P_{\rm out}$  and PAE of 5.58 dBm - 11.1 dBm and 4.8% - 13.3%.

# C. Discussion and Comparison

This PA is compared with other CMOS mm-wave PAs in Fig. 19. This PA achieves comparable modulation efficiency compared to the higher-order Doherty PAs ([17], [15], [19]) while at the same time achieving much higher bandwidth. Compared to [21], this design achieves a significant reduction in core area and has much higher gain flatness across frequency, although with a lower modulation efficiency. The work in [35] has a similar bandwidth but lower modulation efficiency, particularly in the n257 and n261 bands, and it has much larger gain variations. Overall, this PA achieves an exceptional balance between chip area, bandwidth, and efficiency compared to other designs in the same frequency range.

### V. CONCLUSION

This article describes the design of PA that can achieve Doherty-like PBO efficiency enhancement without the need for load modulation. A prototype is designed in 45nm RFSOI CMOS, verifying its broadband, back-off efficiency enhancement capabilities. From 25 - 40 GHz, the PA demonstrates an  $OP_{1dB}$  of 18.7 - 22.2 dBm, a PAE of 20.9 - 37.6%, and a PAE at 9dB PBO of 8.8 - 18.2%. Lastly, the PA is characterized with modulated signals, confirming its efficiency enhancement capabilities.

#### ACKNOWLEDGMENT

The authors would like to thank members of the ETH IDEAS group for their technical discussions. Additionally, we thank GlobalFoundries for chip fabrication and Keysight for measurement equipment. The authors also thank the lab manager of the IDEAS group, Thomas Kleier, for his assistance during the measurements.

Fig. 18. (a) Constellation and spectrum across frequency and (b) modulation measurement summary across frequency at  $EVM_{\mathrm{rms}}$  = -25 dB.

|                               | This Work                                                |          |          |         | [17]                                                       | [15]                                    |          | [19]                       | [38]                                   | [40]                                    |      |                                          | [18]                     |                 |                                        | [21]                      |      |                           |      |      |

|-------------------------------|----------------------------------------------------------|----------|----------|---------|------------------------------------------------------------|-----------------------------------------|----------|----------------------------|----------------------------------------|-----------------------------------------|------|------------------------------------------|--------------------------|-----------------|----------------------------------------|---------------------------|------|---------------------------|------|------|

| Technology                    | 45nm SOI CMOS                                            |          |          |         | 55nm CMOS                                                  | 40nm CMOS                               |          | 40nm CMOS                  | 45nm SOI CMOS                          | 65nm CMOS                               |      |                                          | 40nm CMOS                |                 |                                        | 45nm SOI CM               |      |                           | os   |      |

| Architecture                  | 3-Way Parallel-Series with No Main<br>PA Load Modulation |          |          |         | Transformer-<br>based 3-way<br>Parallel -Series<br>Doherty | Coupled-Inductor-based<br>3-Way Doherty |          | Digital Polar<br>TX        | Transformer-<br>Based 4-Way<br>Doherty | Broadband<br>Doherty-Like<br>Multi-Port |      | Balun-first 3-way<br>Parallel Doherty PA |                          |                 | Coupler Based Parall<br>Series Doherty |                           |      |                           |      |      |

| Supply (V)                    | 2                                                        |          |          | 2.4     | 1.8                                                        |                                         | 1        | 2                          | 1.1                                    |                                         |      | 1.1                                      |                          |                 | 2                                      |                           |      |                           |      |      |

| -3dB S <sub>21</sub> BW (GHz) | 25-41<br>(48%)                                           |          |          |         | 25.9-32.6<br>(23%)                                         | 35.9-39.5<br>(10%)                      |          | 24-31<br>(26%)             | 43.3-50.7<br>(15%)                     | N/A                                     |      |                                          | 23-28*<br>(20%)          |                 |                                        | N/A                       |      |                           |      |      |

| Core Area (mm²)               | 1.07                                                     |          |          |         | 0.54                                                       | 1.4                                     |          | 0.55 <sup>b</sup>          | 0.81                                   | 1.35 (incl. pads)                       |      |                                          | 0.77                     |                 |                                        | 1.55                      |      |                           |      |      |

| Freq (GHz)                    | 26                                                       | 30       | 37       | 40      | 28 38                                                      |                                         | 8        | 29.5                       | 47                                     | 28                                      | 37   | 39                                       | 26                       |                 |                                        | 26                        | 33   | 38                        | 40   |      |

| Gain (dB)                     | 14.5                                                     | 14.9     | 13.7     | 13.7    | 16.1                                                       | 15                                      |          | N/A                        | 17.1                                   | 15*                                     | 16*  | 17.5*                                    | 20                       |                 |                                        | 12*                       | 15*  | 12*                       | 13*  |      |

| P <sub>SAT</sub> (dBm)        | 21.4                                                     | 22.6     | 20.2     | 19.1    | 25.5                                                       | 18.9                                    |          | 18.7                       | 24                                     | 19                                      | 19.6 | 19.2                                     | 20.7                     |                 |                                        | 23.5                      | 24.1 | 22.8                      | 22.7 |      |

| OP <sub>1dB</sub> (dBm)       | 21.1                                                     | 22.2     | 20.1     | 18.7    | 24.3                                                       | 18.4                                    |          | N/A                        | 23.7                                   | 19                                      | 16   | 18.1                                     | 19.5*                    |                 |                                        | 22.8                      | 23.9 | 22.7                      | 22.5 |      |

| PAE <sub>1dB</sub> (%)        | 28.4                                                     | 37.6     | 22.8     | 20.9    | 24.4                                                       | 23                                      |          | 36° (PAE <sub>max</sub> )  | 26.3                                   | 21.6                                    | 21.9 | 21.7                                     | 22*                      |                 |                                        |                           | 27.6 | 38.2                      | 26.8 | 26.2 |

| PAE@9dB PBO (%)               | 16.1                                                     | 18.2     | 11.3     | 10.4    | 18*                                                        | 13.                                     | 7**      | 26°∗                       | 18*                                    | 7*                                      | 13*  | 12*                                      | 7*                       |                 |                                        | 18*                       | 29*  | 15*                       | 12*  |      |

| Modulation                    | 5G NR FR2 1-CC 64-QAM OFDM                               |          |          |         | Single-Carrier<br>64-QAM                                   | 5G NR FR2<br>1-CC 64-<br>QAM OFDM       | 2-CC 64- | 64-QAM<br>OFDM (/w<br>DPD) | 5G NR FR2 1-CC<br>64-QAM OFDM          | 64-QAM OFDM                             |      |                                          | 64-QAM OFDM              |                 |                                        | 5G NR 1-<br>CC 64-<br>QAM |      | 5G NR 1-<br>CC 16-<br>QAM |      |      |

| PAPR (dB)                     | 9.64                                                     |          |          |         | 6                                                          | 9.64                                    | 11.85    | 10.7                       | 9.8                                    |                                         | N/A  |                                          | 11.6<br>1000 800 400 200 |                 | 9.64                                   |                           |      | .64                       |      |      |

| Bandwidth(MHz)                | 100/200                                                  |          |          | 250     | 100                                                        | 100                                     | 300      | 2000                       | 1000                                   |                                         | 00   | 1000                                     |                          |                 | 200                                    | 10                        |      |                           |      |      |

| Freq. (GHz)                   | 28                                                       |          |          | 28      |                                                            | 8                                       | 29.5     | 47                         | 28                                     | 37                                      | 39   |                                          | 26                       |                 |                                        | 33                        |      | 35                        |      |      |

| EVM <sub>rms</sub> (dB)       | -25                                                      |          |          | -25.2   | -25                                                        | -25.1                                   | -27.58   | -25                        | -22                                    | -24                                     | -23  |                                          |                          | -25             | -27                                    |                           |      | -20                       |      |      |

| avy t /                       | 10.2/9.5                                                 |          | 12.1/10. | 9/8.04  | 17.7                                                       | 11.3                                    | 10       | 7.9                        | 14.1                                   | 7.5                                     | 9.8  | 9.1                                      | -                        |                 | 9.4                                    | 9.3                       | 14   |                           |      | 6.6  |

| PAE <sub>avg</sub> (%)        | 13.2/11                                                  | 10.4/13. | 12.0/10. | 8.9/7.4 | 17.5                                                       | 14.7                                    | 13.4     | 18°                        | 13.7                                   | 5.1                                     | 10.2 | 8.5                                      | 15 <sup>c</sup>          | 15 <sup>c</sup> | 14 <sup>c</sup>                        | 13°                       | 25   | .2                        | 26   | 6.4  |

Fig. 19. Comparison table.

The work was supported in part by an ETH Zurich grant, the Swiss State Secretariat for Education, Research, and Innovation (SERI) under the SwissChips initiative, HORIZON-JU-SNS-2023 6G REFERENCE Project with the project number 101139155 and VINNOVA under grant number 2016-00324.

#### **APPENDIX**

The  $\lambda\!/4$  transmission line expression (1) can be applied to determine  $V_{\rm a1}$  as a function of  $I_{\rm m}$ , which is

$$V_{a1} = -jR_{opt}I_m (17)$$

Next, by applying (3) to (17) Z<sub>a1</sub> is determined to be

$$Z_{a1} = R_{opt} (18)$$

which is as expected, since both the Main and Aux1 PAs are the same size, and therefore should see the same optimum impedance at the peak power level. Next, since  $I_{\rm C} = I_{\rm o}$  due to the series combiner, another application of (1) results in

$$-j\frac{2}{R_{opt}}V_{a2} = I_o (19)$$

Furthermore, since  $V_{\rm o}$  =  $V_{\rm C}$  +  $V_{\rm a1}$ , by combining (4), (5) and (17),  $V_{\rm o}$  is calculated in terms of  $I_{\rm a2}$  as

$$V_o = -jR_{opt}I_{a2} \tag{20}$$

substituting (20) into (19) and using the output boundary condition  $V_o = I_o R_{\rm opt}$  results in

$$Z_{a2} = \frac{V_{a2}}{I_{a2}} = \frac{R_{opt}}{2} \tag{21}$$

Again, this result is as expected, since the Aux2 PA is double the size of the Main / Aux1 PA, and therefore naturally requires an  $R_{\rm opt}$  that is halved.

To derive the impedance seen by the main PA as a function of frequency at PBO, first we consider the schematic of Fig. 3 with both  $I_{a1}$  and  $I_{a1}$  set to 0.  $TL_2$  is terminated with an open circuit, and therefore it introduces an impedance of  $-jZ_o\cot(\theta)$  at the input of the lower transformer. Since the transformers are 1:1 ideal and connected in series, the impedance seen at the input of the upper transformer is  $R_{\rm opt}-j\frac{R_{\rm opt}}{2}\cot(\theta).$  This because the same current flows through the load resistor and the impedance by  $TL_2$ , so their respective impedances are combined in series. Then,  $Z_{\rm in}$  can be calculated as

$$Z_{in} = R_{opt} \frac{1 - j(\frac{1}{2}\cot(\theta) - \tan(\theta))}{\frac{3}{2} + j\tan(\theta)}$$

(22)

since the characteristic impedance is  $Z_{\rm o}=R_{\rm opt}$  and the load impedance is  $Z_{\rm L}=R_{\rm opt}-j\frac{R_{\rm opt}}{2}\cot(\theta)$ .

#### REFERENCES

- "3GPP Specification Series," https://www.3gpp.org/dynareport?code=38series.htm, accessed: 2023-07-18.

- [2] F. Wang and H. Wang, "A Broadband Linear Ultra-Compact mm-Wave Power Amplifier With Distributed-Balun Output Network: Analysis and Design," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 8, pp. 2308–2323, 2021.

- [3] J. Zhao, M. Bassi, A. Bevilacqua, A. Ghilioni, A. Mazzanti, and F. Svelto, "A 40–67GHz power amplifier with 13dBm PSAT and 16% PAE in 28 nm CMOS LP," in ESSCIRC 2014 - 40th European Solid State Circuits Conference (ESSCIRC), 2014, pp. 179–182.

- [4] U. Madhow, Fundamentals of digital communication. Cambridge university press, 2008.

- [5] H. Wang et al., "Power Amplifiers Performance Survey 2000-Present," [Online]. Available: https://ideas.ethz.ch/Surveys/pa-survey.html, accessed: 2024-12-12.

- [6] F. Wang, T.-W. Li, S. Hu, and H. Wang, "A Super-Resolution Mixed-Signal Doherty Power Amplifier for Simultaneous Linearity and Efficiency Enhancement," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 12, pp. 3421–3436, 2019.

- [7] H.-C. Park, S. Kim, J. Lee, J. Jung, S. Baek, T. Kim, D. Kang, D. Minn, and S.-G. Yang, "Single Transformer-Based Compact Doherty Power Amplifiers for 5G RF Phased-Array ICs," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 5, pp. 1267–1279, 2022.

- [8] Z. Zong, X. Tang, K. Khalaf, D. Yan, G. Mangraviti, J. Nguyen, Y. Liu, and P. Wambacq, "A 28-GHz SOI-CMOS Doherty Power Amplifier With a Compact Transformer-Based Output Combiner," *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 6, pp. 2795–2808, 2021.

- [9] N. Rostomyan, M. Özen, and P. Asbeck, "28 GHz Doherty Power Amplifier in CMOS SOI With 28% Back-Off PAE," *IEEE Microwave* and Wireless Components Letters, vol. 28, no. 5, pp. 446–448, 2018.

- [10] M. Pashaeifar, L. C. N. de Vreede, and M. S. Alavi, "A Millimeter-Wave CMOS Series-Doherty Power Amplifier With Post-Silicon Inter-Stage Passive Validation," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 10, pp. 2999–3013, 2022.

- [11] E. Kaymaksut, D. Zhao, and P. Reynaert, "Transformer-Based Doherty Power Amplifiers for mm-Wave Applications in 40-nm CMOS," *IEEE Transactions on Microwave Theory and Techniques*, vol. 63, no. 4, pp. 1186–1192, 2015.

- [12] H. Oh et al., "32.2 A 24.25-to-29.5GHz Extremely Compact Doherty Power Amplifier with Differential-Breaking Phase Offset Achieving 23.7% PAEavg for 5G Base-Station Transceivers," in 2024 IEEE International Solid-State Circuits Conference (ISSCC), vol. 67, 2024, pp. 522–524.

- [13] E. Liu and H. Wang, "32.9 An Ultra-Compact 28GHz Doherty Power Amplifier with an Asymmetrically-Coupled-Transformer Output Combiner," in 2024 IEEE International Solid-State Circuits Conference (ISSCC), vol. 67, 2024, pp. 536–538.

- [14] X. Fang, J. Xia, and S. Boumaiza, "A 28-GHz Beamforming Doherty Power Amplifier With Enhanced AM-PM Characteristic," *IEEE Trans*actions on Microwave Theory and Techniques, vol. 68, no. 7, pp. 3017– 3027, 2020.

- [15] X. Zhang, S. Li, D. Huang, and T. Chi, "A Millimeter-Wave Three-Way Doherty Power Amplifier for 5G NR OFDM," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 5, pp. 1256–1270, 2023.

- Solid-State Circuits, vol. 58, no. 5, pp. 1256–1270, 2023.

[16] X. Zhang, H. Guo, and T. Chi, "32.1 a 47GHz 4-way Doherty PA with 23.7dBm P1dB and 21.7% / 13.1% PAE at 6 / 12dB Back-off Supporting 2000MHz 5G NR 64-QAM OFDM," in 2024 IEEE International Solid-State Circuits Conference (ISSCC), vol. 67, 2024, pp. 520–522.

- [17] Z. Ma, K. Ma, K. Wang, and F. Meng, "A 28GHz Compact 3-Way Transformer-Based Parallel-Series Doherty Power Amplifier With 20.4%/14.2% PAE at 6-/12-dB Power Back-off and 25.5dBm PSAT in 55nm Bulk CMOS," in 2022 IEEE International Solid-State Circuits Conference (ISSCC), vol. 65, 2022, pp. 320–322.

- [18] A. K. Kumaran et al., "A Single-Supply Balun-First Three-Way mm-Wave Doherty PA," IEEE Transactions on Microwave Theory and Techniques, vol. 72, no. 5, pp. 2757–2772, 2024.

- [19] M. Mortazavi, Y. Shen, D. Mul, L. C. N. de Vreede, M. Spirito, and M. Babaie, "A Four-Way Series Doherty Digital Polar Transmitter at mm-Wave Frequencies," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 3, pp. 803–817, 2022.

- [20] N. S. Mannem, T.-Y. Huang, and H. Wang, "Broadband Active Load-Modulation Power Amplification Using Coupled-Line Baluns: A Multifrequency Role-Exchange Coupler Doherty Amplifier Architecture," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 10, pp. 3109–3122, 2021.

- [21] E. Liu and H. Wang, "A Broadband Four-Way Parallel–Series Doherty Power Amplifier for 5G Communications," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 5, pp. 1312–1322, 2024.

- [22] J. Guo and K. Chen, "Reconfigurable Hybrid Asymmetrical Load Modulated Balanced Amplifier with High Linearity, Wide Bandwidth, and Load Insensitivity," in 2023 IEEE/MTT-S International Microwave Symposium - IMS 2023, 2023, pp. 462–465.

- [23] H. Lyu and K. Chen, "Analysis and Design of Reconfigurable Multi-band Mismatch-Resilient Quasi-Balanced Doherty Power Amplifier for Massive MIMO Systems," *IEEE Transactions on Microwave Theory and Techniques*, vol. 70, no. 10, pp. 4410–4421, 2022.

- [24] Y. Cao and K. Chen, "Pseudo-Doherty Load-Modulated Balanced Amplifier With Wide Bandwidth and Extended Power Back-Off Range," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 7, pp. 3172–3183, 2020.

- [25] P. Gong, J. Guo, N. Bharadwaj Vangipurapu, and K. Chen, "Decade-Bandwidth RF-Input Pseudo-Doherty Load-Modulated Balanced Amplifier Using Signal-Flow-Based Phase Alignment Design," *IEEE Microwave and Wireless Technology Letters*, vol. 34, no. 6, pp. 761–764, 2024.

- [26] Y. Cao, H. Lyu, and K. Chen, "Asymmetrical Load Modulated Balanced Amplifier With Continuum of Modulation Ratio and Dual-Octave Bandwidth," *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 1, pp. 682–696, 2021.

- [27] J. Pang et al., "Analysis and Design of Highly Efficient Wideband RF-Input Sequential Load Modulated Balanced Power Amplifier," IEEE Transactions on Microwave Theory and Techniques, vol. 68, no. 5, pp. 1741–1753, 2020.

- [28] C. Chu et al., "Waveform Engineered Sequential Load Modulated Balanced Amplifier With Continuous Class-F-1 and Class-J Operation," *IEEE Transactions on Microwave Theory and Techniques*, vol. 70, no. 2, pp. 1269–1283, 2022.

- [29] C. Belchior, L. C. Nunes, P. M. Cabral, and J. C. Pedro, "Sequential LMBA Design Technique for Improved Bandwidth Considering the Balanced Amplifiers off-State Impedance," *IEEE Transactions on Microwave Theory and Techniques*, vol. 71, no. 8, pp. 3629–3643, 2023.

- [30] C. Zhao et al., "A Ka-Band Pseudo-Doherty Load-Modulated Balanced Amplifier With Gain Flatness Enhancement Technique," *IEEE Transactions on Microwave Theory and Techniques*, vol. 72, no. 6, pp. 3423–3437, 2024.

- [31] P. Saad, R. Hou, R. Hellberg, and B. Berglund, "A 1.8–3.8-GHz Power Amplifier With 40% Efficiency at 8-db Power Back-Off," *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 11, pp. 4870–4882, 2018.

- [32] P. Saad, R. Hou, R. Hellberg, and B. Berglund, "An 80W Power Amplifier with 50% Efficiency at 8dB Power Back-off over 2.6-3.8 GHz," in 2019 IEEE MTT-S International Microwave Symposium (IMS), 2019, pp. 1328–1330.

- [33] P. Saad, R. Hou, R. Hellberg, and B. Berglund, "A 65w Power Amplifier Without Load Modulation to Achieve 50% Efficiency at 8db Power Back-Off over 1.8-2.5 GHz," in 2020 50th European Microwave Conference (EuMC), 2021, pp. 1095–1098.

- [34] E. Liu, H. Zhou, C. Fager, and H. Wang, "A 25-40 GHz Three-Way Power Amplifier with No Load Modulation Achieving Broadband Deep Power Back-Off Efficiency Enhancement," in 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2024, pp. 127–130.

- [35] T.-Y. Huang *et al.*, "A Coupler Balun Load-Modulated Power Amplifier With Extremely Wide Bandwidth," *IEEE Transactions on Microwave Theory and Techniques*, vol. 71, no. 4, pp. 1573–1586, 2023.

- [36] J. S. Park and H. Wang, "A Transformer-Based Poly-Phase Network for Ultra-Broadband Quadrature Signal Generation," *IEEE Transactions* on Microwave Theory and Techniques, vol. 63, no. 12, pp. 4444–4457, 2015.

- [37] H. T. Nguyen, T. Chi, S. Li, and H. Wang, "A Linear High-Efficiency Millimeter-Wave CMOS Doherty Radiator Leveraging Multi-Feed On-Antenna Active Load Modulation," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 12, pp. 3587–3598, 2018.

- [38] X. Zhang, H. Guo, and T. Chi, "A Millimeter-Wave Four-Way Doherty Power Amplifier With Over-GHz Modulation Bandwidth," *IEEE Journal* of Solid-State Circuits, vol. 59, no. 12, pp. 3898–3914, 2024.

- [39] S. Hu, F. Wang, and H. Wang, "2.1 A 28GHz/37GHz/39GHz multiband linear Doherty power amplifier for 5G massive MIMO applications," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 32–33.

- [40] C. R. Chappidi and K. Sengupta, "A 26-42 GHz Broadband, Back-off Efficient and Vswr Tolerant CMOS Power Amplifier Architecture for 5G Applications," in 2019 Symposium on VLSI Circuits, 2019, pp. C22– C23.

Edward Liu (Student Member, IEEE) received the B.S. and M.S. degrees in Electrical and Computer Engineering (ECE) from the University of Texas at Austin, both in 2020. He is currently pursuing the Ph.D. degree in the Department of Information Technology and Electrical Engineering at the Swiss Federal Institute of Technology in Zürich, Switzerland. His research interests include RF/mm-wave integrated circuits and systems.

Han Zhou (Member, IEEE) received his B.Sc. degree in space science and technology from the Harbin Institute of Technology, Harbin, China, in 2016. He received his M.Sc. and Ph.D. degrees in electrical engineering from the Chalmers University of Technology, Gothenburg, Sweden, in 2018 and 2023, respectively. In 2019, he joined the Microwave Electronics Laboratory at Chalmers University of Technology. In 2022, he was a visiting researcher with the IDEAS Group at the Swiss Federal Institute of Technology Zürich (ETH Zurich), Switzerland.

He is currently a postdoctoral researcher at Chalmers University of Technology.

Dr. Zhou's research interests include highly efficient, wideband, and linear power amplifier architectures for future wireless transmitters, the design of RF/mm-wave integrated circuits for 5G/6G communication and sensing, and AI-assisted, deep-learning-enabled design for circuits and systems. He received the IEEE Microwave Theory and Techniques Society (MTT-S) Graduate Fellowship Award in 2023 and the EuMC Young Engineer Prize at the 52nd European Microwave Conference in 2022. He also received grants from the Ericsson Research Foundation in 2021.

Christian Fager (Fellow, IEEE) received his Ph.D. degree from Chalmers University of Technology, Sweden, in 2003. He became Full Professor at the same university in 2019 and is currently Head of the Microwave Electronics Laboratory. He has authored or co-authored more than 200 publications in international journals and conferences, where he has made significant contributions to the area of linear and energy efficient power amplifiers and transmitters for wireless communications.

Dr. Fager serves as Associate Editor of IEEE Microwave Magazine and IEEE Microwave and Wireless Components Letters. He is representative for Sweden, Norway and Iceland in the European Microwave Association (EuMA) and member of the IEEE MTT-S Technical Committee on Wireless Communications. He served as chair of the 2021 IEEE Topical Conference on RF/microwave Power Amplifiers and TPC cochair for the 2020 European Microwave Integrated Circuits Conference. Dr. Fager received Chalmers Supervisor of the Year Award in 2018 and the IEEE International Microwave Symposium Best Student Paper Award in 2002.

**Hua Wang** (Fellow, IEEE) received the M.S. and Ph.D. degrees in electrical engineering from the California Institute of Technology, Pasadena, CA, USA, in 2007 and 2009, respectively. He was a Tenure-Track Assistant Professor and then a Tenured Associate Professor at the School of Electrical and Computer Engineering (ECE), Georgia Institute of Technology, Atlanta, GA, USA, from 2012 to 2021, where he held the Demetrius T. Paris Professorship with the School of ECE. He was the Founding Director of the Georgia Tech Center of Circuits and

Systems (CCS), Atlanta, and the Director of the Georgia Tech Electronics and Micro-System (GEMS) Laboratory, Atlanta. Prior to that, he was with Intel Corporation, Santa Clara, CA, USA, and Skyworks Solutions, Irvine, CA, USA, from 2010 to 2011. In 2021, he joined the Faculty of the Swiss Federal Institute of Technology Zürich (ETH Zürich), Zürich, Switzerland, where he is a Full Professor and the Chair of electronics with the Department of Information Technology and Electrical Engineering (DITET). He is also the Director of the ETH Integrated Devices, Electronics, and Systems (IDEAS) Group. He has authored or coauthored over 200 peer reviewed journals and conference papers. He is interested in innovating analog, mixed-signal, RF, and millimeter-wave (mm-Wave) integrated circuits and hybrid systems for wireless communication, sensing, and bioelectronics applications.

Dr. Wang received the DARPA Director's Fellowship Award in 2020 (the first awardee in Georgia Tech's history), the DARPA Young Faculty Award in 2018, the National Science Foundation CAREER Award in 2015, the Qualcomm Faculty Award in 2020 and 2021, the IEEE MTT-S Outstanding Young Engineer Award in 2017, the Georgia Tech Sigma Xi Young Faculty Award in 2016, the Georgia Tech ECE Outstanding Junior Faculty Member Award in 2015, and the Lockheed Dean's Excellence in Teaching Award in 2015. His research group has won multiple academic awards and best paper awards, including the 2019 Marconi Society Paul Baran Young Scholar, the IEEE RFIC Best Student Paper Awards in 2014, 2016, 2018, and 2021; the IEEE International Microwave Symposium (IMS) Best Student Paper Award in 2021; the IEEE CICC Outstanding Student Paper Awards in 2015, 2018, and 2019; the IEEE CICC Best Conference Paper Award in 2017; the 2016 IEEE Microwave Magazine Best Paper Award; and the IEEE Sensors Best Live Demo Award (Second Place) in 2016. He has served on the Technical Program Committee (TPC) Member for the IEEE ISSCC, RFIC, CICC, and BCICTS conferences. He has been a Steering Committee Member of IEEE RFIC and CICC. He is the Conference Chair of CICC 2019, the Conference General Chair of CICC 2020, and the Conference TPRC Co-Chair of IMS 2021. He is a Distinguished Microwave Lecturer (DML) for the IEEE Microwave Theory and Techniques Society (MTT-S) from 2022 to 2024. He is a Distinguished Lecturer (DL) of the IEEE Solid-State Circuits Society (SSCS) from 2018 to 2019. He serves as the Chair for the Atlanta's IEEE CAS/SSCS Joint Chapter that won the IEEE SSCS Outstanding Chapter Award in 2014.