#### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### Trapping Effects in Gallium Nitride High Electron Mobility Transistors: Mechanisms, Modeling, and Applications

RAGNAR FERRAND-DRAKE DEL CASTILLO

#### **CHALMERS**

Microwave Electronics Laboratory

Department of Microtechnology and Nanoscience – MC2

Chalmers University of Technology

Göteborg, Sweden, 2025

# Trapping Effects in Gallium Nitride High Electron Mobility Transistors: Mechanisms, Modeling, and Applications

RAGNAR FERRAND-DRAKE DEL CASTILLO

© Ragnar Ferrand-Drake del Castillo, 2025

Chalmers University of Technology

Department of Microtechnology and Nanoscience – MC2

Microwave Electronics Laboratory

SE-412 96 Göteborg, Sweden

+ 46 (0) 31-772 1000

ISBN 978-91-8103-270-3 Doktorsavhandlingar vid Chalmers tekniska högskola, Ny serie nr 5728 ISSN 0346-718X

Printed by Chalmers digitaltryck Göteborg, Sweden 2025

## **Abstract**

While GaN-based high electron mobility transistors (HEMTs) have become indispensable for 5G and RADAR systems and shown potential for astronomy and space exploration. Knowledge gaps remain in how epitaxial and processing design impact device performance. Downscaling of GaN HEMTs exacerbates source-drain current dispersion due to trapping and self-heating effects. This thesis focuses on characterizing and optimizing back-barrier/buffer design and processing methods to mitigate trap-induced degradation.

Although back-barrier and buffer doping individually enhance two-dimensional electron gas (2DEG) confinement, carbon-induced trapping creates a trade-off between confinement and dispersion. This work explores variations in carbon doping levels in the GaN buffer and AlGaN back-barrier to improve 2DEG confinement. By employing extensive electrical and spectroscopic methods, trapping mechanisms and their origins are investigated. The results show that dispersion dominates over short-channel effects at the investigated carbon levels, offering guidance for RF performance optimization.

Annealing during gate opening is widely used to counteract damage from fluorine-based plasma treatments. However, the influence of high-temperature pre-gate annealing ( $500-800\,^{\circ}\text{C}$ ), particularly in relation to  $CF_4$  and  $CF_4$  chemistries, remains underexplored. This study demonstrates that fluorine implantation and surface oxidation affect device behavior via thermally activated and deactivated traps. It identifies optimal combinations of fluorine plasma and annealing treatments, showing that up to  $60\,\%$  of  $CF_4$  plasma-induced  $F^-$  states can be deactivated by  $600\,^{\circ}\text{C}$  annealing.

Buffer trapping is also studied under cryogenic conditions, where Fe-induced traps manifest slow de-trapping dynamics. Field plates are found to mitigate these effects, emphasizing epi-structure and layout design strategies critical for reliable cryogenic GaN HEMT operation.

This thesis further shows that charged states introduced during gate-defining processing can be deliberately harnessed to modulate reverse gate-bias C–V characteristics. By varying fluorine plasma chemistry and pre-gate annealing conditions, the distribution and concentration of charged states in the barrier/channel region can be tuned. This enables the development of GaN-based varactors for MMIC applications, offering low nonlinear distortion in RF systems.

By addressing key challenges in reliability and performance, and exploring emerging applications such as cryogenic operation and varactor integration. This thesis is well placed to advance and diversify GaN HEMT technology.

**Keywords:** AlGaN/GaN, HEMT, RF, characterization, Trapping effects, downscaling, GaN varactor

iv Abstract

# **List of Publications**

#### **Appended Publications**

This thesis is based on the content in the following papers:

- [A] R. Ferrand-Drake del Castillo, D-Y. Chen, J-T. Chen, M. Thorsell, V. Darakchieva, and N. Rorsman, "Characterization of Trapping Effects Related to Carbon Doping Level in AlGaN Back-Barriers for AlGaN/GaN HEMTs," *IEEE Transactions on Electron Devices*, vol. 71, no. 6, pp. 3596-3602, June, 2024.

- [B] R. Ferrand-Drake del Castillo, V. Darakchieva, and N. Rorsman, "Effects of Fluorine-Based Plasma Etching and Pre-Gate Annealing on AlGaN/GaN HEMT Characteristics," *IEEE Transactions on Electron Devices*, Submitted: 2025/04/07.

- [C] R. Ferrand-Drake del Castillo, B. Hult, M. Thorsell, and N. Rorsman, "Linear C–V Characteristics in GaN HEMT Varactors by Fluorine Plasma-Enhanced Gate Engineering," *IEEE Electron Device Letters*, Submitted: 2025/08/12.

- [D] M. A. Mebarki, R. Ferrand-Drake Del Castillo, D. Meledin, E. Sundin, M. Thorsell, A. Papamichail, V. Darakchieva, N. Rorsman, F. Joint, V. Belitsky, and V. Desmaris, "Cryogenic Trapping Effects in GaN-HEMTs: Influences of Fe-doped buffer and Field-Plates," *IEEE Transactions on Electron Devices*, vol. 72, no. 8, pp. 4042-4048, Aug. 2025.

Vi List of Publications

#### **Other Publications**

The content of the following papers partially overlaps with the appended papers or is out of the scope of this thesis.

- [a] M. A. Mebarki, R. Ferrand-Drake Del Castillo, D. Meledin, E. Sundin, M. Thorsell, N. Rorsman, V. Belitsky, and V. Desmaris, "Noise characterization and modeling of GaN-HEMTs at cryogenic temperatures," *IEEE Transactions on Microwave Theory and Techniques*, vol. 71, no. 5, pp. 1923-1931, May 2023.

- [b] M. A. Mebarki, R. Ferrand-Drake Del Castillo, A. Pavolotsky, D. Meledin, E. Sundin, M. Thorsell, N. Rorsman, V. Belitsky, and V. Desmaris, "GaN High-Electron-Mobility Transistors with Superconducting Nb Gates for Low-Noise Cryogenic Applications," *Phys. Status Solidi A*, vol. 220, no. 8, 2200468, 2023.

- [c] R. Ferrand-Drake del Castillo, N. Rorsman, M. Thorsell "GaN Varactor with linear C–V realized through F plasma treatment," 15th ICNS (International Conference on Nitride Semiconductors), Malmö, Sweden, July, 2025.

- [d] R. Ferrand-Drake del Castillo, D-Y. Chen, J-T. Chen, M. Thorsell, V. Darakchieva, and N. Rorsman, "Impact of Carbon Doping Levels in AlGaN Back-Barriers for GaN HEMTs," 14th ICNS (International Conference on Nitride Semiconductors), Fukuoka, Japan, November, 2023.

- [e] R. Ferrand-Drake del Castillo, and N. Rorsman, "Considerations in the development of a gate process module for ultra-scaled GaN HEMTs," *CSW (Compound Semiconductor Week)*, Ann Arbor MI, USA, June, 2022.

- [f] M. A. Mebarki, R. Ferrand-Drake Del Castillo, D. Meledin, E. Sundin, M. Thorsell, N. Rorsman, V. Belitsky, and V. Desmaris, "Comparison of the low noise performance of GaN HEMTs and MIS-HEMTs at cryogenic temperatures," 18th EuMIC (European Microwave Integrated Circuits Conference), Berlin, Germany, September, 2023.

- [g] M. Mebarki, R. Ferrand-Drake Del Castillo, and E. Sundin, "A Cryogenic Scalable Small-Signal and Noise Model of GaN HEMTs," *32nd ISSTT (International Symposium on Space Terahertz Technology)*, Baeza, Spain, October, 2022.

- [h] M. A. Mebarki, R. Ferrand-Drake Del Castillo, A. Pavolotskiy, D. Meledin, E. Sundin, M. Thorsell, N. Rorsman, V. Belitsky, and V. Desmaris, "GaN HEMT with superconducting Nb gates for low noise cryogenic applications," *CSW (Compound Semiconductor Week)*, Ann Arbor MI, USA, June, 2022.

# **Abbreviations & Notations**

AlGaN Aluminium gallium nitride

AlN Aluminium nitride

BV Breakdown voltage

CC Current collapse

DUT Device under test

DCTS Drain current transient spectroscopy

DIBL Drain induced barrier lowering

ICP Inductively coupled plasma

InP Indium phosphide

FET Field-effect transistor

GaN Gallium nitride

GaAs Gallium arsenide

HEMT High electron mobility transistor

LNA Low noise amplifier

LPCVD Low pressure chemical vapor deposition MMIC Monolithic microwave integrated circuit

NF Noise figure

PA Power amplifier

PAE Power added efficiency

PGA Pre-gate annealing

PIV Pulsed-IV

PVD Physical vapor deposition

RF Radio frequency

RTA Rapid thermal annealing SCE Short channel effect

SEM Scanning electron microscopy

SiC Silicon Carbide

TCAD Technology computer-aided design

TLM Transfer length method UID Un-intentional Doping

2DEG Two-dimensional electron gas

$CF_4$  Tetrafluoromethane (Carbon tetrafluoride)  $C_{Ga}$  Carbon occupying a gallium-vacancy site  $C_I$  Carbon occupying an interstitial site VIII Abbreviations

$C_{\rm N}$  Carbon occupying a nitrogen-vacancy site

DX - like Oxygen donor state transitioned to deep acceptor state

E Electric field

$E_{\rm a}$  Apparent activation energy

$f_{\text{max}}$  Maximum frequency of oscillation  $f_{\text{T}}$  Current gain cut-off frequency

I Current  $I_d$  Drain current  $I_g$  Gate current  $I_s$  Source current  $I_{ds}$  Drain-source current

I<sub>ds.max</sub> Maximum drain-source current

$L_{\text{FPD}}$  Drain field-plate length  $L_{\text{FPS}}$  Source field-plate length

L<sub>g</sub> Gate-length

$L_{\rm sd}$  Source-drain contact distance

$n_s$ sheet carrier density $NF_3$ Nitrogen trifluoridePPower dissipation $R_{on}$ On-resistance $R_c$ Contact resistance

$SiN_x$  Silicon nitride (non-stoichiometric)

$T_{\rm ck}$  Thermal chuck temperature  $T_{\rm ch}$  Estimated channel temperature  $T_{\rm min-opt}$  Minimum noise temperature

V Voltage

$V_{

m gs}$  Gate-source voltage  $V_{

m dg}$  Drain-gate voltage  $V_{

m ds}$  Drain-source voltage

$V_{\rm ds,max}$  Maximum drain-source voltage

$V_{

m d}$  Drain voltage  $V_{

m knee}$  Knee voltage  $V_{

m po}$  Pinch-off voltage

v<sub>s</sub> electron saturation velocity

$V_{\rm T}$ Threshold-voltageWDevice width $\mu$ Electron mobility $\sigma$ Apparent cross-section $\tau$ De-trapping time constant

# **Contents**

| Al | Abstract                                                             |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|----|----------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Li | st of l                                                              | Publicati | trion vii ction 1  I HEMTs Design and Characterization istructure engineering 1  EMT Layout design and contact formation 2  EMT fabrication 3  EMT operation 6  Ap origin 7  Inventional IV and Signal-Based Measurements 7  EMeasurements 8  I Pulsed IV Measurements 8  I Pulsed IV Measurements 8  I Pulsed IV Measurements 10  I A Large-Signal Operation 10  I Drain Current Transient Spectroscopy 12  I Drain Current Transient Spectroscopy 12  I Back-barrier C doping: trade-offs in dispersive and SCEs 17  I Trap Manifestation 17 |     |  |  |  |

| Al | bbrev                                                                | iations & | k Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vii |  |  |  |

| 1  | Intr                                                                 | oduction  | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   |  |  |  |

| 2  | RF                                                                   | GaN HE    | MTs Design and Characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1   |  |  |  |

|    | 2.1                                                                  | Epi-stru  | acture engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   |  |  |  |

|    | 2.2                                                                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|    | 2.3                                                                  | HEMT      | fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3   |  |  |  |

|    | 2.4                                                                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|    | 2.5                                                                  | Trap ori  | igin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7   |  |  |  |

|    | 2.6                                                                  | Conven    | tional IV and Signal-Based Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7   |  |  |  |

|    | 2.7                                                                  | DC Me     | asurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8   |  |  |  |

|    |                                                                      | 2.7.1     | Pulsed IV Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8   |  |  |  |

|    |                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|    |                                                                      | 2.7.3     | Large-Signal Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10  |  |  |  |

|    | 2.8                                                                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|    |                                                                      | 2.8.1     | Drain Current Transient Spectroscopy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12  |  |  |  |

| 3  | Characterization of trapping effects limiting the performance of mi- |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|    | crov                                                                 |           | . , ====:==                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |  |  |  |

|    | 3.1                                                                  |           | 1 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |  |  |  |

|    |                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |

|    |                                                                      |           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |  |  |  |

|    |                                                                      | 3.1.3     | Trap Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22  |  |  |  |

|    | 3.2                                                                  |           | e plasma gate opening and device recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |  |  |  |

|    |                                                                      |           | High temperature pre-gate annealing for device recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |  |  |

|    |                                                                      |           | Trap manifestation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

|    |                                                                      |           | Trap Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |  |  |

|    | 3.3                                                                  |           | ng dynamics at cryogenic temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |  |

|    |                                                                      |           | Buffer doping and field plate modulation of trap activation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |  |  |  |

|    |                                                                      |           | Trap manifestation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |  |

|    |                                                                      | 3.3.3     | Trap Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39  |  |  |  |

X Contents

| 4  | Har   | nessing | deep-level charge effects in varactor applications | 43 |

|----|-------|---------|----------------------------------------------------|----|

|    | 4.1   | The G   | aN HEMT Varactor development                       | 43 |

|    |       | 4.1.1   | C-V modulation using F plasma and annealing        | 44 |

|    |       | 4.1.2   | Small-Signal Modeling                              | 44 |

|    |       | 4.1.3   | TCAD simulations                                   | 46 |

| 5  | Con   | clusion | s and Future Outlook                               | 53 |

| A  | knov  | vledgme | ents                                               | 55 |

| Bi | bliog | raphy   |                                                    | 57 |

# Chapter 1

# Introduction

Gallium Nitride (GaN) High Electron Mobility Transistors (HEMTs) have established themselves as key components in advanced radio frequency (RF) systems, enabling a wide range of applications including fifth-generation (5G) communication infrastructure [1], and defense industry such as RADAR systems [2], while showing potential for future applications within spaceborne communication [3], and radio astronomy systems [4] [5]. These diverse applications place highly demanding requirements on the underlying amplifier technologies, driving the need for solutions that can deliver high output power ( $P_{out}$ ), efficiency, linearity, dynamic range, and stability across a broad range of operating conditions. In particular, spaceborne and defense platforms are strongly driven by size, weight, and power (SWaP) constraints, where a reduction in SWaP is critical for mission viability, cost, and system integration. The rapid evolution of radio frequency (RF) systems is driving unprecedented demands for power amplifiers (PAs) and low-noise amplifiers (LNAs) in a wide array of sectors, including telecommunications, aerospace, and defense. For 5G and beyond massive multiple input multiple output (MIMO) configurations are utilized, requiring amplifiers that can operate efficiently under high peak-to-average power ratio (PAPR) signals, while ensuring linearity, dynamic response, and power efficiency over wide bandwidths and varying load conditions [6]. Simultaneously, backhaul links place emphasis on maximizing peak output power, and long-term stability, particularly at microwave and millimeter-wave frequencies up to 170 GHz [1].

In the defense and aerospace sectors, active electronically scanned array (AESA) radar systems are evolving toward multifunction and high-duty-cycle operation, placing new demands on efficiency, wideband capability, and dynamic range, while increasingly exploring architectures that benefit from dynamic impedance tuning and load modulation to improve platform agility and reduce power consumption [7]. In satellite communications (Satcom), increasing demand for high data rates, wide bandwidths, and compact ground terminals places emphasis on RF components that offer high efficiency, linearity, and thermal robustness.

For ground and spaceborne applications, heterodyne THz front-ends typically use a cryogenically cooled mixer, such as a NbN-based hot electron bolometer (HEB), to downconvert signals to an intermediate frequency (IF), which is then amplified by a low-noise amplifier (LNA). While InP and SiGe LNAs are common, they face limitations in radiation tolerance, thermal robustness, and power handling. GaN integration, as shown in [8], offers advantages in thermal and power performance.

2 Chapter 1. Introduction

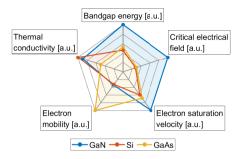

**Figure 1.1:** Material property comparison between GaN and two legacy semiconductors (Si, GaAs), for parameters relevant to high-power, high-frequency operation. All values are normalized to the material with the highest value for each property, resulting in dimensionless units [a.u.]

On a further note, with the perspective of SWaP constraints, these applications where GaN HEMTs are already indispensable, incentives for a full GaN Monolithic Microwave Integrated Circuits (MMIC) technology have become strong. In these contexts, emerging dynamic load modulation architectures and multifunction array systems demand components with high linearity and predictable behavior [9]. Varactor-based tuning networks, central to these architectures, have traditionally been hindered by nonlinear capacitance-voltage C(V) characteristics and distortion, which limit power handling and integration potential [10].

#### **RF GaN HEMTs**

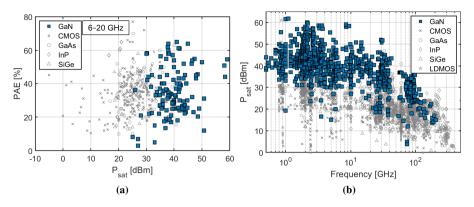

Within this landscape, GaN HEMTs have emerged as a key enabling technology capable of addressing many of the above challenges. The wide bandgap of GaN (Eg = 3.4 eV), combined with a high critical breakdown field ( $E_c \approx 3.3$  MV/cm), supports robust device operation under high voltages and powers, with good thermal stability. The polarization-induced two-dimensional electron gas (2DEG) at the AlGaN/GaN interface provides high carrier mobility ( $\mu > 2000 \text{ cm}^2/\text{Vs}$ ), high electron velocity saturation ( $v_s \sim 2 \cdot 10^7$  cm/s), and high sheet carrier density ( $n_s \sim 1 \cdot 10^1 3 cm^2$ ) Fig. 1.1. Together these properties support high current density, (which is critical for large output power and efficiency), fast carrier transport (enabling operation at microwave and millimeter-wave frequencies), and low on-resistance (improving gain and reducing power loss). These properties allow for aggressive downscaling of a GaN HEMT while still maintaining a high output power and breakdown voltage, since a smaller device structure entails lower parasitic capacitances that impede high frequency performance. With these qualities, GaN HEMTs are able to achieve transition frequency and maximum oscillation frequency, ( $f_T$  and  $f_{max}$ ) reaching (454 and 444 GHz) [11]. Thereby enabling 3W/mm output power density at 96 GHz [12]. In this thesis the GaN heterostructure is grown on semi-insulating 4H SiC substrates, thus leveraged by the high thermal conductivity of 3.8 W cm<sup>-1</sup> K<sup>-1</sup> enabling high output power density and efficiency. Nonetheless, as demonstrated recently by IMEC even a less ideal substrate as Si, can be used for achieving 6G compatible performance combined with using a regrown  $n^+$ (In)GaN layer to obtain record-low contact resistance of 0.024  $\Omega \cdot$  mm [13]. Up to today, there is ample evidence of how GaN HEMTs outperform other technologies with respect to output power and power added efficiency (PAE) at microwave

**Figure 1.2:** (a): PAE and saturated output power ( $P_{sat}$ ) for different PA technologies within the 6-20 GHz range. (b): the  $P_{sat}$  for PA technologies with respect to frequency of operation [14].

frequencies relevant for 5G and RADAR systems, Fig. 1.1a-b.

GaN is a III-V material with stronger atomic bonding compared to InP and GaAs, hence can withstand more ionizing radiation before degrading, making it highly suitable technology for space communication. Furthermore, the potential for monolithic integration between NbN-based HEBs and GaN MMICs makes GaN LNAs with their favorable low noise figure, strong candidates for next-generation low-noise amplification under SWaP-constrained conditions.

Despite these advantages, GaN HEMTs continue to face challenges related to device reliability and stability. Both in terms of thermal and/or trapping induced dispersion, of which the latter is of main concern in this thesis. Charge carriers becoming temporarily trapped at surface states or within the buffer layer, introduce time- and bias-dependent variations (memory effects) in device performance. The resulting increase in dynamic on-resistance and gain compression degrades key amplifier metrics such as linearity, efficiency, and power consistency. In 5G power amplifier systems, especially those operating under high PAPR signals and advanced load modulation schemes, trapping directly limits output power capability and reduces efficiency at power back-off [15]. In AESA radar systems, where PAs must operate over wide bandwidths and duty cycles, low dispersion is essential to maintain linearity and predictable behavior [16]. In spaceborne and high-reliability systems the slow emission rates of trapped charges lead to persistent dispersion and long recovery times, compromising gain stability and noise figure performance under pulsed or varying signal conditions [17]. Hence, minimizing trapping effects remains a critical objective for realizing the full potential of GaN HEMTs in next-generation RF systems.

#### **GaN HEMT Varactors**

The same material properties that make GaN an exceptional platform for high-power transistors also make it highly attractive for MMIC-compatible varactors, particularly GaN HEMT and metal—semiconductor—metal (MSM) varactors. These technologies offer a promising route to on-chip tunability in high-power and high-frequency systems. GaN's wide bandgap enables high breakdown voltages and low thermionic leakage currents, allowing for high reverse-bias operation with minimal leakage. This supports improved Q-factor, wider tunability range, and lower distortion under high-

4 Chapter 1. Introduction

power conditions. Additionally, GaN's inherent thermal stability ensures consistent capacitance behavior in environments with elevated junction temperatures, which is critical in RF power amplifier systems.

Among MMIC-compatible varactors, MSM structures offer distinct advantages due to their inherently low parasitics and high Q-factor, while HEMT-based varactors provide design flexibility by leveraging the transistor structure itself. However, a key limitation in both types remains the nonlinear capacitance-voltage (C–V) behavior, which can degrade overall system performance [18]. In particular, nonlinearity in the C–V response can impact phase and amplitude consistency, which is critical in applications such as beamforming and adaptive RF front ends [19]. Despite recent progress, no study to date has demonstrated a GaN HEMT MMIC-compatible varactor with both high Q-factor and a highly linear C–V response across a broad voltage range. The GaN HEMT varactors investigated in this thesis address this gap by introducing new strategies for engineering linear C–V behavior in both HEMT and MSM device architectures.

#### Thesis Motivation and Outline

Charge trapping phenomena arising from defects and impurities at the surface, barrier, and buffer represent a key impediment to achieving high efficiency, output power, and dynamic stability in power amplifiers and other MMIC components. This thesis is motivated by the dual need to suppress these unwanted trapping effects in GaN HEMTs while also exploring opportunities to deliberately manipulate charge states introduced during processing.

Chapter 2 discusses the design features of RF AlGaN/GaN HEMTs and their relation to trapping behavior, along with a brief overview of the electrical and spectroscopic techniques used for trap characterization.

Chapter 3 presents a detailed study on minimizing trapping effects across cryogenic temperatures, room temperatures up to 160 °C. Detailing how these effects manifest in DC, pulsed-IV, small- and large-signal operations. The origin and nature of different trap states are analyzed using both electrical and spectroscopic methods. In paper [A] special focus is given to the role of back-barrier C-doping, whereas iron buffer doping in cryogenic LNAs is treated in Paper [D]. Additionally, minimization of process related traps induced by F plasma and how an additional annealing process for removal of the same traps is treated in Paper [B]

Chapter 4 presents a method for realizing GaN varactors with highly linear reverse-bias C(V) characteristics using standard GaN HEMT processing steps [Paper C]. This enables co-integration with power amplifier technologies with minimal additional fabrication. As a result, discrete components can be eliminated, reducing interconnect parasitics, size, and packaging complexity, while improving system-level reliability and performance. Small-signal measurements and TCAD simulations are used to assess device behavior and model charge distribution effects on C(V) linearity.

Collectively, these studies provide a deeper understanding of trapping physics with a dual approach of mitigating harmful traps while leveraging controllable charge states. The findings of this thesis introduce practical pathways for performance enhancement through optimization of epitaxial design, device layout, and processing strategies.

# Chapter 2

# RF GaN HEMTs Design and Characterization

This chapter lays the groundwork for the thesis, building on previous descriptions of GaN HEMT technology [20]. Efforts to downscale these devices for enhanced high-frequency performance often exacerbate transient effects, i.e. charge trapping and self-heating induced performance drift. Wherein trapping is the primary concern of this thesis. As a wide-bandgap III-V semiconductor, GaN is particularly susceptible to trapping effects, which, if left unaddressed, can reduce the reliability of GaN HEMTs. Consequently, comprehensive methods for trap characterization are needed when optimizing the epitaxial structure and refining device processing. Given that the transient response of GaN HEMTs may arise from both thermal dynamics and charge trapping, careful attention must be paid to measurement chronology, bias levels and experimental setup. Below, a brief introduction to the GaN HEMT technology and the origin of trapping behavior is detailed. Thereafter, various measurement methods for identifying and quantifying trap states are elucidated.

#### 2.1 Epi-structure engineering

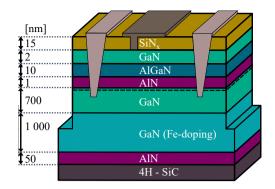

The AlGaN/GaN HEMT heterostructure has ever since its conception in the 90's been grown on a foreign substrate [21], although native substrates are emerging, industrial processing is mostly limited to Sapphire, Si and SiC substrates for 100 mm wafer sizes [22]. Out of thermal management reasons and relatively well-matched lattice constants, GaN HEMT power amplifiers are preferably based on a heterostructure using semi-isolating SiC 4H substrate (rather than Si). Since the thesis does not concern N-polar devices, the epitaxial growth detailed below is applicable for a Gapolar orientation growth.

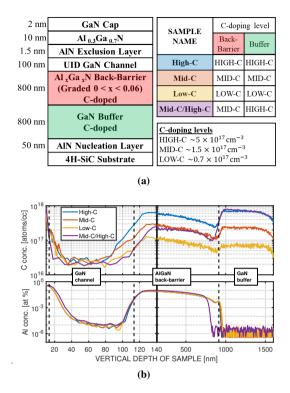

The aspect of GaN being grown on foreign substrate entails elevated epitaxial dislocation density, which ideally is kept to a minimum in the channel layer where the 2DEG resides. Typically, this is achieved by growing an AlN nucleation layer to bridge the lattice mismatch combined with a thick GaN buffer layer. The most common growth technique metal organic chemical vapor deposition (MOCVD) inevitably leads to residual impurities (Si, O and N-vacancies) in un-intentionally doped (UID) Gapolar (Al)GaN, resulting in n-type doping [23]. Thus, the thick GaN buffer provides an

alternative un-gated leakage path between source and drain, limiting gate-modulation of the 2DEG. To maintain high 2DEG confinement, Fe and C buffer doping was introduced [24] [25]. Both elements have the net effect of acting as deep-level acceptor states, raising the buffer resistivity, thereby inhibiting un-gated leakage paths. An alternative method to increase 2DEG confinement is to use back-barriers, by such means creating a conduction band discontinuity between the channel layer and the back-barrier, which may include AlGaN, InGaN, and AlN layer [26] [27] [28] [29].

The top barrier exhibits intrinsically a sufficiently large piezoelectric and spontaneous polarization charge in tandem with surface state donors to give rise to a 2DEG predominately located in the underlying GaN channel. Generally, the top barrier consists of an  $Al_xGa_{1-x}N$  layer where an increase in x leads to a larger polarization field, forcing the electrons towards the underlying GaN layer. Note that x is limited to ca 0.3 imposed by risk of lattice relaxation [30]. This effect together with the conduction-band discontinuity ensures an electron confinement inside the GaN layer. However, having AlGaN as a surface layer is not preferable out of reliability concerns due to Al being highly prone to oxidation and giving rise to gate-lag and current-collapse. A GaN cap is instead often used as the topmost layer of the top barrier. Although this leads to a slightly lower 2DEG concentration, it improves device reliability [31]. At the  $Al_xGa_{1-x}N/GaN$  interface (x = 0.3), part of the 2DEG distribution will extend into the AlGaN layer, hence compromising the electron mobility. Therefore, an ultrathin 1-2nm AlN layer, (below the critical thickness for lattice relaxation) is inserted between the AlGaN and GaN layers, Fig. 2.1a.

The main characteristics to describe the 2DEG are the electron sheet concentration  $(n_s)$ , mobility ( $\mu$ ) and saturation velocity ( $v_s$ ). With a higher polarization, the higher the  $n_s$  becomes, whereas  $\mu$  and  $v_s$  are mostly dependent on crystal quality and AlN/GaN interface sharpness. Although it should be mentioned that  $v_s$  could degrade due to increased electron-electron interactions, which become more prevalent with higher 2DEG concentration [32].

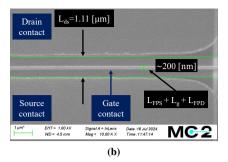

#### 2.2 HEMT Layout design and contact formation

The bare epitaxial structure described above needs to be processed to obtain the functionality of a three terminal device such as a transistor. Source and drain should have pure ohmic contact with minimal contact resistance to the 2DEG, thereby ensuring high  $I_{ds}$  and linear correlation towards  $V_{ds}$ . The third contact (gate) on the other hand forms a Schottky contact, which through the field effect will modulate the current between source and drain Fig. 2.1a. In this thesis two-finger co-planar devices are used, with a symmetrical plane going vertically through the middle of the gate and drain contact pads Fig. 2.1b. This enables a more compact device design as opposed to single fingered devices, while avoiding the need for complex processing using e.g. air-bridges as is the case of devices with more than two fingers. Additionally, by using co-planar design, control of characteristic impedance is enhanced while parasitics are kept low compared to e.g. microstrip where ground plane and signal plane are vertically separated.

Apart from potential aggravation of memory effects, the downscaling of GaN HEMTs poses challenges in electric field management to maintain a high breakdown voltage, thus influencing layout design. During operation the largest potential differences will be between gate and drain. Therefore, the gate-drain distance  $(L_{pd})$  is kept

2.3. HEMT fabrication 3

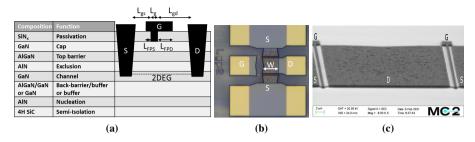

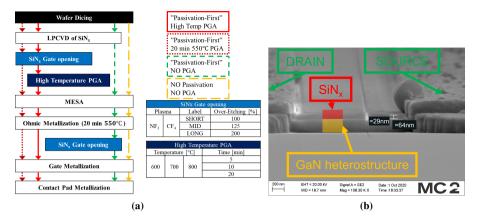

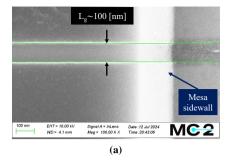

Figure 2.1: HEMT cross-section and layout [C], (a): typical epitaxial layer stack used in this thesis, note the layer below the GaN channel layer varies between studies. (b): optical top-view image with labels showing source, drain, gate contacts and device width. (c): Scanning electron microscope image taken at an angled view before contact pad deposition.

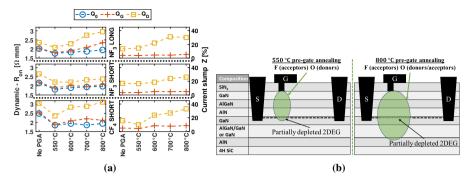

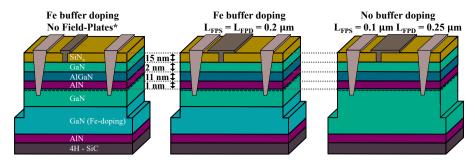

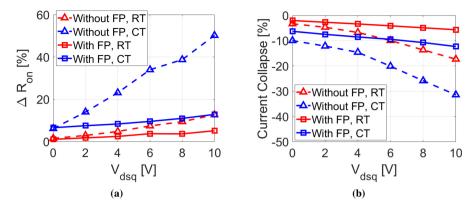

larger than gate-source distance ( $L_{gs}$ ) Fig. 2.1a, thereby ensuring that the breakdown voltage is maximized for a given source-drain distance ( $L_{sd}$ ) and gate-length ( $L_g$ ). The gate exhibits a T-shaped structure with field plates, (deposited on the  $SiN_x$  passivation layer) which extend towards source ( $L_{FPS}$ ) and drain ( $L_{FPD}$ ) Fig. 2.1a. Although field plates introduce additional parasitic capacitance, it lowers the gate-resistance and the peak electric field, thus ensuring higher breakdown voltage while also reducing the severity of trapping effects most notably in cryogenic environments, Paper [D].

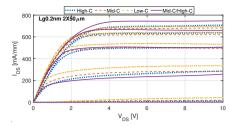

A typical cross-sectional epitaxial structure used in this thesis is shown in Fig. 2.1a, with dimensions indicated along the current flow direction. While [Papers B, C, and D] employ a GaN buffer structure, [Paper A] uses an AlGaN/GaN back-barrier and buffer combination to improve 2DEG confinement.

An optical microscope top-view image taken from a normal angle to the device shows a typical device layout with all three contact terminals denoted including the gate width (W), Fig. 2.1b. A device prior to contact pad deposition is seen in Fig. 2.1c.

#### 2.3 HEMT fabrication

Processing technique and sequence is of high import when understanding the final device performance, as detailed in Paper [B]. Here the typical processing steps for GaN HEMT fabrication is presented. Except for Paper [B], the reader can assume these main steps and chronology to represent how all devices in the thesis were processed.

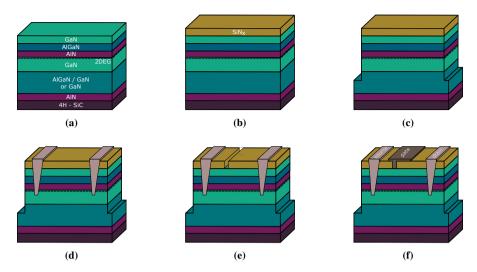

The wafers processed in this thesis are provided by different foundries, and delivered with the epitaxial structure as shown in Fig. 2.2a. Where the GaN heterostructure is grown upon a semi-isolating 4H-SiC 100mm substrate. The wafer is diced into 20x20mm chips before processing, thereafter the chips individually go through the following process steps:

#### SiN<sub>x</sub> Passivation

The positively charged surface states in the GaN cap act as electron traps under off-state and high drain bias. Silicon nitride  $(SiN_x)$  passivation has been shown to be successful in reducing the density of surface states, [33] [34]. For this purpose low-pressure chemical vapor deposition (LPCVD) has proved to be most effective as opposed to plasma enhanced CVD (PECVD) [35]. Generally, passivation with LPCVD requires a passivation-first process due to the high temperature involved (up to 820°C), which is

**Figure 2.2: step-by-step HEMT processing, (a)**: The bare wafer pre-processing. **(b)**:  $SiN_x$  passivation deposition. **(c)**: MESA isolation etch down into the highly resistive AlGaN back-barrier or GaN buffer. **(d)**: OHMIC metal processing, connecting source and drain to the 2DEG. **(e)**: Gate opening process, recess etch through the  $SiN_x$  enabling Schottky gate formation. **(f)**: Gate metal deposition, now all three terminals are established.

not compatible with ohmic or gate mentalization, Fig. 2.2b. Passivation-first ensures no processing related impurities impact the sensitive surface states of the GaN cap.

#### Mesa Isolation

Electrical isolation is essential to prevent unwanted conduction paths or leakage currents between adjacent GaN HEMT devices. In this thesis, isolation is implemented using MESA etching via Cl-based inductively coupled plasma (ICP), by etching down to the highly resistive AlGaN back-barrier or GaN buffer Fig. 2.2c. An alternative approach is ion implantation, which introduces insulating defects through high-energy ion bombardment [36]. While ion implantation offers smoother surface morphology and avoids issues like sidewall leakage and gate structure fragility, its main advantage lies in preserving breakdown voltage [37]. However, since this work focuses on high-frequency rather than high-power applications, MESA isolation remains a practical choice.

#### **Ohmic Contact Formation**

Achieving low contact resistance to a wide-bandgap material such as GaN is challenging but essential, particularly in high-frequency devices where contact resistance constitutes a larger part of the total on-resistance as device dimensions are scaled down. In this work, ohmic contacts were formed by first recess etching through the barrier and partially into the GaN channel, exposing the 2DEG along the GaN channel sidewall, as illustrated in Fig. 2.2d.

An alternative approach, is the use of regrown  $n^+(In)$ GaN contact layers, which can achieve contact resistances as low as  $0.024 \Omega \cdot mm$  [13]. However, such regrown contacts require selective-area epitaxy using MOCVD or molecular beam epitaxy

2.3. HEMT fabrication 5

(MBE), technologies that were not readily available during this thesis work. Instead, a metal stack was directly deposited onto the recessed region followed by rapid thermal annealing (RTA).

The annealing step induces interfacial reactions that reduce the Schottky barrier height ( $\phi^B$ ) and enable carrier transport across the metal–semiconductor interface. For ohmic contacts to GaN, tunneling transport is expected to dominate over thermionic emission due to the material's wide bandgap [38].

The metal stack used in this thesis was Ta/Al/Ta (25/280/15 nm) [39]. Tantalum was chosen not only for its relatively low metal work function ( $\phi_0 = 4.19 \text{ eV}$  [40]), but more importantly for its ability to react with GaN and form TaN. This reaction extracts nitrogen from the GaN surface, generating nitrogen vacancies that enhance tunneling probability [18].

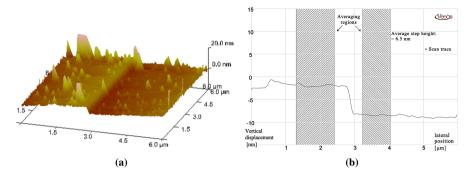

Compared to conventional ohmic schemes, using planar contacts annealed at 800 -  $900^{\circ}$ C [41] [42], this approach enables low-temperature processing at around  $550^{\circ}$ C. The reduced thermal budget minimizes the risk of 2DEG degradation due to atomic diffusion and yields improved surface morphology. The resulting contact resistance for this process typically falls in the range of 0.3– $0.5~\Omega~mm$ .

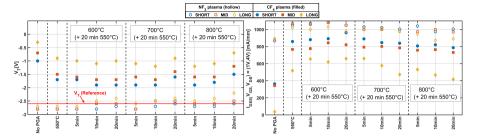

#### **Gate Opening**

patterning for gate opening is done through e-beam lithography. Gate opening is performed by selectively etching the  $SiN_x$  layer using a fluorine-based ICP process to expose the underlying GaN cap, enabling Schottky gate metal deposition in the subsequent step. Since this step defines the gate length ( $L_g$ ), precise dimensional control is critical. Furthermore, exposure of the GaN surface to fluorine plasma can impact device performance negatively, making the choice of plasma chemistry, control of etch duration, and post-etch recovery strategies especially important. These considerations are addressed in detail in this thesis through an extensive study presented in Paper [B].

#### **Gate Metal Deposition**

The Schottky gate is deposited using a Au/Pt/Ni (450/20/30 nm) metal stack, as illustrated in Fig. 2.2f. This step involves a dedicated e-beam lithography process, separate from the gate opening, which can introduce a  $\sim 50$  nm offset between the gate and the field plate. While alignment to the gate opening is generally critical particularly for minimizing parasitic capacitance and ensuring effective field modulation the gate architecture used in this work is relatively forgiving to small misalignments. This is in contrast to mushroom gates where the reduced overlap makes precise alignment more critical, although it should be mentioned that slight overlap i.e. mini/micro-field-plates are demonstrated to ensure lower current collapse (CC) and better power density scaling [43]. Moreover, since this thesis does not investigate breakdown voltage characteristics, which are strongly influenced by field plate design [37], such minor deviations are not expected to significantly affect the results. In the cryogenic trapping study (Paper [D]), where field plate dimensions were found to influence performance, SEM imaging confirmed no deviations from the nominal design geometry.

#### **Contact Pad Deposition**

Contact pads, formed after all terminal metallization steps (not shown in Fig. 2.2f), are fabricated using a Ti/Au/Ti (30/300/20 nm) metal stack. The bottom Ti layer promotes adhesion to the underlying layers, while the thick Au layer ensures low electrical resistance. These pads serve as probing interfaces for electrical characterization of the devices. The processing steps conclude at this stage. In a complete MMIC process, additional steps would be required. However, such steps could potentially degrade HEMT performance. Therefore, this work reports HEMT performance based on a minimal set of necessary processing steps.

#### 2.4 HEMT operation

Intrinsically, the GaN HEMT is usually a normally-on (depletion-mode) device. Hence, turning off the device, i.e. depleting the 2DEG below the gate, necessitates a negative bias on the gate contact, sufficiently large to elevate the two-dimensional quantum well above the fermi level. Whereas a gate-source voltage  $V_{gs}$  exceeding the threshold voltage  $(V_T)$ , enables 2DEG accumulation. By adjusting the forward gate bias, the electron sheet density  $(n_s)$  in the 2DEG can be modulated, thereby directly influencing  $I_{ds}$ . However, no current can flow unless a non-zero  $V_{ds}$  bias is applied, inducing an electric field forcing free electrons from source to drain, where the  $\mu$  determines how efficiently electrons accelerate under the electric field. At a sufficiently high  $V_{ds}$ , the  $I_{ds}$  saturates, as the drift velocity approaches the material's  $v_s$ . Unto this day, new studies attempt to link the abovementioned physical parameters to an analytical expression for  $I_{ds}(V_{gs}, V_{ds})$  [44]. With the resistive and saturation region current described as:

$$I_{\rm ds,resistive} = \frac{q\mu n_s}{L_g} V_{ds} \tag{2.1}$$

$$I_{\rm ds,saturation} = \frac{q\mu n_s}{L_g} \cdot \frac{v_{\rm sat}(V_{gs} - V_T)}{v_{\rm sat} + \left(\frac{\mu}{2L_g}\right)(V_{gs} - V_T)}$$

(2.2)

Where q is the electron charge. A unified expression of Eq. (2.1) and Eq. (2.2) for all drain-source current was formulated as:

$$I_{DS} = \frac{I_{\text{DS,resistive}} \cdot I_{\text{DS,saturation}}}{\sqrt{I_{\text{DS,resistive}}^2 + I_{\text{DS,saturation}}^2}}$$

(2.3)

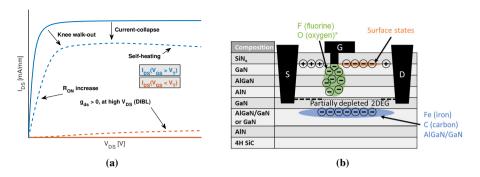

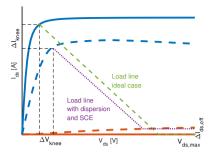

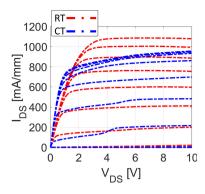

From this expression Eq. (2.3), ideal output characteristics, without self-heating, trapping and short channel effect (SCE) is depicted with solid lines in Fig. 2.3a. To contrast the ideal case, striped lines of a physical device measurement are displayed Fig. 2.3a. For  $V_{gs} < V_T$ , the device is expected to remain off ( $I_{ds} = 0$ ) independent of  $V_{ds}$  bias, but for the non-ideal case the output conductance ( $g_{ds} > 0$ ), i.e. gate control is compromised leading to SCE. In the case of  $V_{gs} > V_T$  multiple non-ideal effects are depicted, primarily caused by trapping and/or self-heating. Electron trapping can occur at various sites within the epitaxial structure, such as at surface states, interfaces, in the gate vicinity, or within the buffer/back-barrier layers. The location and nature of the trap strongly influence the dynamics of charge capture and emission. Which in turn affects the transient and steady-state performance of the device. In this thesis

2.5. Trap origin 7

**Figure 2.3:** (a): off- (orange) and on- (blue) state output characteristics of ideal HEMT (filled lines) contrasted to a HEMT suffering from dispersive and SCEs (striped lines). (b): electrons can get trapped in different locations in the epitaxial structure, here three different regions with likely trap states are exemplified. Trapped electrons will cause a reduction in the 2DEG density. \*Although O typically acts as a donor state, it can act as a DX-like acceptor state [47].

three main regions for potential trapping are depicted in Fig. 2.3b, which are addressed depending on the study split.

#### 2.5 Trap origin

Any deviation from an ideal crystal structure periodical arrangement can be considered as a defect state. Examples are point-defects, vacancies, interstitials and antisite, extended defects, screw dislocations, edge dislocations, interface states and impurities [45]. Whenever considering an optimal epi-structure used for effective 2DEG confinement, attention towards how the proposed design will influence the density of defect states in vicinity of the 2DEG is crucial. The defect states introduce allowed energy-states within the forbidden energy gap of GaN, with varying trapping/de-trapping time constants, causing a time-dependent partial depletion of the 2DEG Fig. 2.3a, creating  $I_{ds}$  time-transient behavior depending on the previous bias-settings the HEMT has been subjected to. Commonly reported de-trapping time constants range from  $\mu$ s to a few seconds [46], hence potentially having adverse impact on the performance of RF GaN HEMTs. Therefore, a central theme throughout this thesis is how trapping can be minimized [Papers A, B and D]. With [Paper C] serving as the exception where surface charge state modulation instead is utilized for enhancing GaN varactor performance.

#### 2.6 Conventional IV and Signal-Based Measurements

This chapter presents the electrical measurement techniques employed throughout the thesis to evaluate device performance. Each subsection first introduces the method in a general context, outlining the key parameters and figures of merit that can be extracted.

To emphasize the central theme of trap characterization, each method is subsequently revisited in a dedicated section, where its specific relevance to trapping effects is discussed. In this way, the reader can clearly distinguish between standard measurement principles and their interpretation in the context of charge trapping.

#### 2.7 DC Measurements

Direct current (DC) measurements are widely used to extract low-frequency or steadystate parameters in field-effect transistors. Among the key figures of merit obtained from DC sweeps and referenced throughout this thesis are the threshold voltage  $(V_T)$ , saturation current  $(I_{ds,sat})$ , knee current  $(I_{knee})$ , knee voltage  $(V_{knee})$ , transconductance  $(g_m)$ , on-resistance  $(R_{on})$ , subthreshold swing (SS), and drain-induced barrier lowering (DIBL).

How these parameters are influenced by trapping is hard to discern due to most being influenced by self-heating, (and may have quasi-static behavior). Therefore low-power conditions are typically used when attempting to link DC performance to trapping effects. In this thesis, such an approach is used in [Paper A], where  $R_{on}$ , SS, and DIBL are analyzed as indirect indicators of charge trapping.

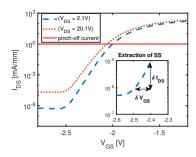

SS and DIBL are extracted from the transfer characteristics near the threshold or pinch-off region. DIBL is determined by tracking the shift in  $V_{gs}$  required to reach a defined pinch-off current ( $I_{po} = 1 \text{ mA/mm}$ ) across different  $V_{ds}$  values. SS is obtained from the steepest slope of the  $\log(I_{ds})$  versus  $V_{gs}$  curve in the subthreshold regime, as illustrated in Fig. 2.4.

$$DIBL = \frac{V_{po,high} - V_{po,low}}{V_{ds,high} - V_{ds,low}} = \frac{\Delta V_{po}}{\Delta V_{ds}}$$

(2.4)

$$SS = \frac{\delta V_{gs}}{\delta \log_{10}(I_{ds})}$$

(2.5)

Lower DIBL and SS values typically indicate improved gate control and reduced short-channel effects.  $R_{on}$  is extracted from the output characteristics in the linear regime, with the gate in forward bias and drain voltage kept low. In this region,  $R_{on}$  primarily reflects access resistance and carrier mobility.

#### DC Trap Characterization

In [Paper A], an increase in negatively charged traps (e.g., electrons at the channel or back-barrier interface) was shown to cause further depletion of the 2DEG through a back-gating effect. This led to lower apparent SS and DIBL values, even though the actual gate control was not improved. Simultaneously, the reduced channel conductivity also resulted in an increase in  $R_{on}$ .

Thus, under low-power DC conditions, a combination of low SS and DIBL with increased  $R_{on}$  may indicate the presence of trapped charge. However, because detrapping in III-nitride materials can occur over timescales of several seconds, DC measurements may capture non-equilibrium charge states and should therefore be interpreted with caution. For example, in [Paper B], slow  $F^-$ -related traps induce apparent permanent shifts in threshold voltage  $(V_T)$ , as the measurement timescale is shorter than the de-trapping time of these states at room temperature [48].

#### 2.7.1 Pulsed IV Measurements

As described in the previous section, DC measurements are constrained not only by self-heating, which can mask or distort trapping phenomena, but also by long transient effects that may result in apparent steady-state readings that are, in fact, non-equilibrium. Pulsed IV (PIV) measurements overcome these limitations by applying

2.7. DC Measurements 9

**Figure 2.4:** Transfer characteristics at low and high  $V_{ds}$  showing DIBL extraction from  $I_{po}$  intersections. Inset: region used for SS extraction.

short, low duty-cycle voltage pulses to the gate and drain terminals. This approach minimizes thermal effects and allows for time-resolved analysis of charge dynamics.

In this thesis, PIV measurements were implemented with pulse widths of approximately 1  $\mu$ s and a duty cycle of 1 %. This ensures that most of the self-heating, which occurs on millisecond timescales, is avoided, and any generated heat can dissipate between pulses.

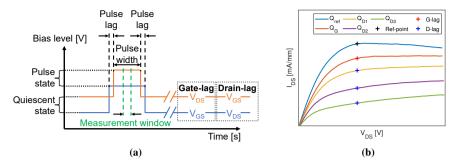

The distinction between gate-lag and drain-lag configurations is illustrated in Fig. 2.5a. In gate-lag mode, the drain-pulse defines the measurement window, and no drain field is present during the quiescent period. In drain-lag mode, the gate-pulse defines the window, ensuring no heating occurs during off periods. The current is typically sampled at the center of the measurement pulse to avoid distortions due to transients.

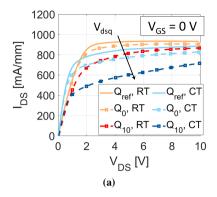

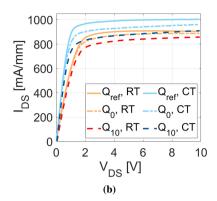

Fig. 2.5b shows a representative PIV sweep for five different quiescent bias conditions, labeled by their gate and drain quiescent voltages:  $Q_{\rm ref}$  (0,0),  $Q_g$  (gate-lag), and  $Q_{d1}$ – $Q_{d3}$  (increasing drain-lag bias).

Current collapse  $Z(Q_x)$  is defined as the relative reduction in saturation current compared to the reference condition:

$$Z(Q_x)[\%] = \frac{I_{ds}(Q_x) - I_{ds}(Q_{\text{ref}})}{I_{ds}(Q_{\text{ref}})} \cdot 100$$

(2.6)

#### **PIV Trap Characterization**

PIV enables qualitative insight into the spatial origin and dynamics of traps through the use of targeted quiescent bias conditions. Therefore, extensively used method for trap evaluation, as demonstrated in [Paper A, B, and D]. While no single pulse scheme can isolate surface from buffer traps entirely, the relative contributions of each can be inferred. In Fig. 2.5b, gate-lag measurements, which apply a negative quiescent gate bias and zero drain bias, predominantly activate surface traps, hence a slight CC and increase in  $R_{on}$  is seen. Drain-lag measurements, which include both gate and drain quiescent biases, activate both surface and deeper buffer traps, hence typically manifesting a larger CC and dynamic- $R_{on}$ . With increasing quiescent drain bias progressively larger trapping is seen Fig. 2.5b, likely located in the buffer/back-barrier region.

**Figure 2.5:** (a) Time-domain schematic of PIV operation, illustrating the timing of gate and drain pulses for gate- and drain-lag configurations. (b) Output characteristics of a GaN HEMT measured under five different quiescent bias conditions. CC and increased dynamic- $R_{on}$  are observed in both gate- and drain-lag cases relative to  $Q_{ref}$ .

#### 2.7.2 Small-signal operation

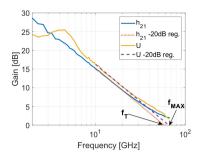

Initial assessment of high frequency performance is done through small signal measurements. With sufficiently small input and output signals, an inherently non-linear device such as a GaN HEMT can be considered linear, thus simplifying the description of the intrinsic parameters. However, this approximation means that the modelled equivalent circuit is only applicable for the specific bias point for which the parameters are extracted. Through extracted s-parameters the small signal current and unilateral power gains can be obtained, which by extension is used to obtain two figures of merit at which frequency the short-circuit current and the unilateral power gain become 0 dB denoted as transit frequency  $(f_T)$  and maximum oscillation frequency  $f_{max}$ .  $f_T$  can be expressed in terms of transconductance  $g_m$ , gate-source capacitance  $C_{gs}$  and gate-drain capacitance  $C_{gd}$ , typically  $C_{gd}$  is neglected since  $L_{gs} < L_{gd}$  [49].

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \tag{2.7}$$

$f_{max}$  depends on additional parameters such as  $R_i$ ,  $R_s$  and  $R_g$ , which represent gate charging, source and gate resistance, including  $g_{ds}$  which is the output conductance [50].

$$f_{\text{max}} = \frac{f_T}{2\sqrt{(R_i + R_s + R_g)g_{ds} + 2\pi f_T R_g C_{gd}}}$$

(2.8)

#### **Small-signal Trap Characterization**

In [Paper A],  $f_T$  and  $f_{max}$  were found to be relatively insensitive to trapping-induced dispersion effects, only for sufficiently large  $V_{ds}$  could some insight into the dispersive behavior of the devices be observed in  $f_{max}$ . Although the reader should note that dispersion was better addressed through large-signal measurements.

#### 2.7.3 Large-Signal Operation

Power amplifiers (PAs) often operate under large-signal conditions. Key figures of merit in this regime include output power ( $P_{out}$ ), PAE, gain, and linearity. The

2.7. DC Measurements

**Figure 2.6:** the extraction of  $f_T$  and  $f_{max}$  is extracted by using the small signal unilateral power and current gain (U and  $h_{21}$ ) and by imposing a -20dB/decade regression line.

maximum output power ( $P_{out,max}$ ), as expressed for Class A operation in Eq. (2.9), corresponds to RF voltage and current swings that fully span the device's load line from the knee point to the off-state at maximum  $V_{ds}$ .

$$P_{\text{out,max}} = \frac{(V_{ds,\text{max}} - V_{ds,\text{knee}})(I_{ds,\text{knee}} - I_{ds,\text{off}})}{8}$$

(2.9)

PAE quantifies how efficiently a power amplifier converts DC power ( $P_{DC}$ ) into additional RF output power, Eq. (2.10):

$$PAE = \frac{P_{\text{out}}^{\text{RF}} - P_{\text{in}}^{\text{RF}}}{P_{\text{DC}}}$$

(2.10)

In Fig. 2.7, two load lines are shown for Class AB operation (an operation mode that is typically chosen as a compromise between  $P_{out,\max}$  and  $PAE_{\max}$ ). The ideal case assumes no dispersive or SCE, while the non-ideal case includes them. The latter thus demonstrates a reduction in the usable RF swing and hence limiting both  $P_{out}$  and PAE.

#### Large-Signal Trap Characterization

Under RF operation, trapping-related dispersion manifests as a reduced output current swing, particularly near the knee region. This results in a decrease in  $I_{ds,knee}$  and an increase in  $V_{ds,knee}$  (Fig. 2.7), ultimately leading to a reduction in  $P_{out,max}$  and degradation of PAE. In contrast, short-channel effects (SCE) such as the loss of gate control at high  $V_{ds}$ , cause an elevation in  $I_{ds,off}$ , Fig. 2.7, which increases DC power consumption and further reduces PAE. Additionally, the increased self-heating can impair  $P_{out}$  by degrading carrier mobility.

In aggressively scaled devices, a critical trade-off emerges between mitigating SCE and suppressing trap induced dispersion. This trade-off is central to the back-barrier C-doping study reported in [Paper A].

Whereas DC and PIV measurements can reveal manifestations of SCE or dispersion under specific bias conditions, they fall short of capturing their interaction under realistic RF stress. The large-signal load-pull methodology enables joint analysis of  $P_{out}$  and PAE across frequency and power levels, providing a more comprehensive picture. By tracking these metrics simultaneously, the dominant degradation mechanism, whether trap-related or due to SCE can be identified.

**Figure 2.7:** the demonstrated dispersive and SCE seen in Fig. 2.3a result in a Compressed load line swing compared to the ideal case.

#### 2.8 Trap Analysis

In the above mentioned measurement techniques, ample ways of describing trapping is provided. However, the manifestation of trapping may be difficult to ascribe to a certain device epitaxial design, layout or processing technique and by extension, to a specific defect. Thus, an additional measurement technique is implemented throughout this thesis, drain current transient spectroscopy (DCTS). which facilitates to go from showing correlation to causation by providing the means to tie specific trap signatures to a specific defect state.

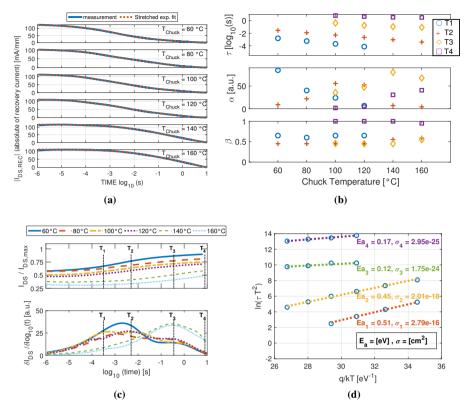

#### 2.8.1 Drain Current Transient Spectroscopy

Drain Current Transient Spectroscopy (DCTS) is a technique based on Shockley-Read-Hall (SRH) theory used to characterize trap states in GaN HEMTs. Similar to Pulsed IV (PIV), a specific bias condition, called the filling state, is applied for a fixed duration to activate trap states. In this thesis, the fill state typically corresponds to an off-state with the gate bias  $V_{GF} < V_T$ , and a filling time of 10 s is frequently used.

The filling-state drain voltage  $V_{DF}$  influences which traps are activated. A low  $V_{DF}$  tends to activate surface-related traps, while a high  $V_{DF}$  can engage both surface and buffer/back-barrier traps. The device is then pulsed into an on-state, where the gate voltage  $V_{G,ON}$  is typically set to 1 V. The drain voltage  $V_{D,ON}$  is kept low to avoid self-heating, which could distort transient behavior and obscure trap detection [51]. However, since some traps induce not only dynamic  $R_{on}$  degradation but also  $V_T$  shifts [52], an accurate characterization often requires biasing the device in the saturation regime. Therefore, in this thesis, most DCTS measurements use  $V_{D,ON}$  values above the knee voltage, typically 4–6 V.

#### **Modeling Current Transients and Extraction of Trap Parameters**

By analyzing the transient drain current following the gate or drain voltage pulse, DCTS allows for the extraction of key trap parameters, such as activation energy  $(E_a)$  and capture cross-section  $(\sigma)$ . These parameters are generally evaluated under the assumption that thermionic emission dominates over tunneling as the primary de-trapping mechanism [52]. The transient current can be modeled using stretched exponentials as described in [53]:

2.8. Trap Analysis 13

$$I_{DS}(t) = I_{DS,\text{final}} - \sum_{i=1}^{N} \alpha_i \exp\left[-\left(\frac{t}{\tau_i}\right)^{\beta_i}\right]$$

(2.11)

Here, N is the number of distinguishable transient components;  $\alpha_i$  is the amplitude,  $\tau_i$  is the de-trapping time constant, and  $\beta_i$  is the stretching exponent associated with the  $i^{\text{th}}$  trap. A value of  $\beta_i \approx 1$  suggests a narrow energy distribution, typical of discrete point defects, while  $\beta_i \ll 1$  indicates a broader distribution, often linked to extended or interface-related trap states.

Under the thermionic emission assumption, the time constant  $\tau_i$  varies with channel temperature. Measuring  $\tau_i$  across a temperature series enables extraction of  $E_a$  and  $\sigma$  through an Arrhenius plot [51], using the relation:

$$\ln(\tau T^2) = \ln\left(\frac{\gamma}{\sigma}\right) + \frac{E_a}{kT}, \quad \gamma = \frac{h^3}{2(2\pi)^{3/2}\sqrt{3}\,m_e^*k^2}$$

(2.12)

Here, the channel temperature T denotes the estimated channel temperature, which is calculated based on the chuck temperature  $t_{\rm chuck}$ , the dissipated power  $P_D$ , and a thermal resistance  $R_{\rm th} \approx 5\,{\rm K}$  mm/W, the value of which reflects devices with a finger pitch of  $\sim 100\,{\rm \mu m}$  and finger width of  $\sim 50\,{\rm \mu m}$ , [54].

It is important to note that extracting the actual values of  $E_a$  and  $\sigma$  presents several challenges. For instance, the extracted time constants  $\tau_i$  in such fits represent effective values, not single emission rates, especially when  $\beta_i \ll 1$ . This spectral dispersion can distort Arrhenius plots, leading to inaccurate activation energies  $E_a$ , often underestimated or non-physical. Since the capture cross-section  $\sigma$  is derived from the same fit intercept, its accuracy is equally affected. These issues are particularly critical when multiple traps contribute simultaneously to the transient [52]. Furthermore, the extraction of  $\sigma$  can be complicated by the nature of the defect states. For non-interacting point defects, the capture rate remains constant, and the trap occupancy depends exponentially on the fill pulse time, making  $\sigma$  effectively time-independent. However, for interacting point defects (such as those arranged linearly) electrons already captured create a time-dependent Coulombic repulsive potential. This repulsion suppresses subsequent capture events, effectively reducing the capture cross-section  $\sigma$  over time. This effect becomes more pronounced when the fill time is significantly longer than the characteristic emission time constant  $\tau$  of the trap [55]. While stretched exponentials offer robust empirical fits, care must be taken in interpreting the extracted parameters as uniquely representing physical trap states.

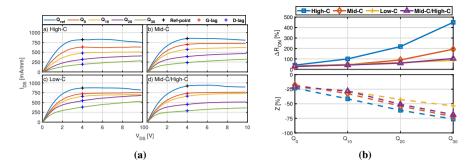

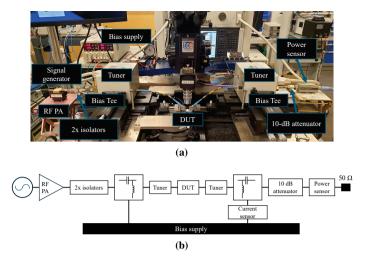

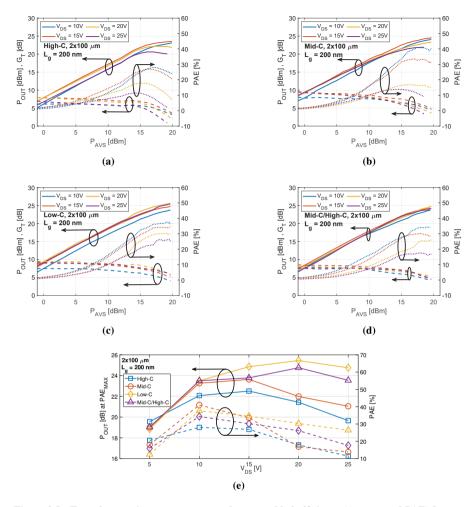

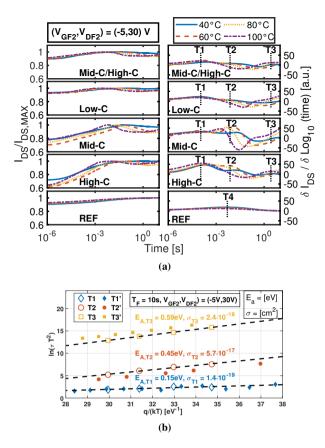

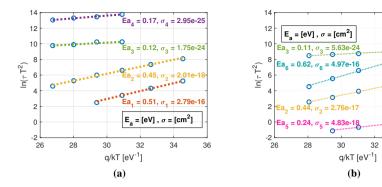

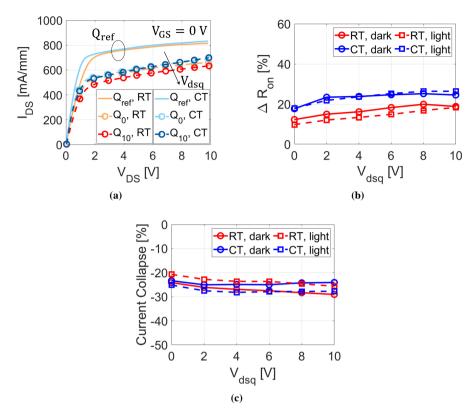

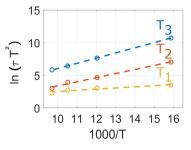

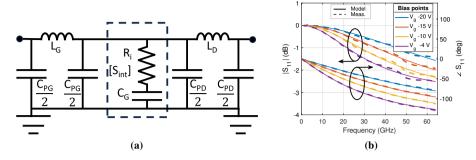

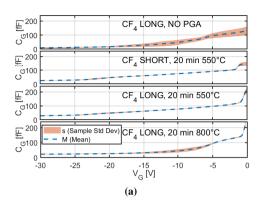

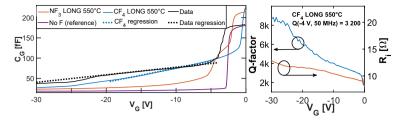

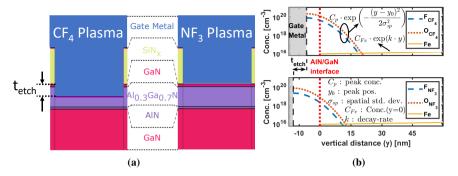

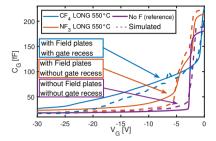

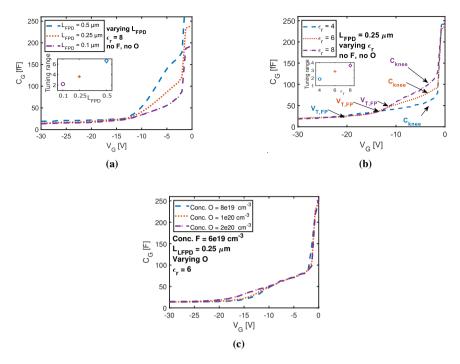

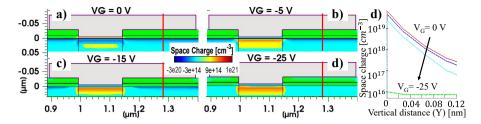

#### **DCTS Implementation**