# Semantic Relaxation of Concurrent Data Structures: Efficient and Elastic Designs

Kåre von Geijer

# Semantic Relaxation of Concurrent Data Structures: Efficient and Elastic Designs

Kåre von Geijer

© Kåre von Geijer, 2025 except where otherwise stated. All rights reserved.

#### ISSN 1652-876X

Department of Computer Science and Engineering Division of Computer and Network Systems Distributed Computing and Systems Chalmers University of Technology | University of Gothenburg SE-412 96 Göteborg, Sweden

Phone: +46(0)317721000

Printed by Chalmers Digitaltryck, Gothenburg, Sweden 2025. "The only thing that makes life possible is permanent, intolerable uncertainty: not knowing what comes next."

- Ursula K. Le Guin, The Left Hand of Darkness

# Semantic Relaxation of Concurrent Data Structures: Efficient and Elastic Designs

Kåre von Geijer

Department of Computer Science and Engineering Chalmers University of Technology | University of Gothenburg

## Abstract

The growing availability of hardware parallelism continues to challenge developers to design programs that efficiently utilize it. Many widely used concurrent data structures — such as FIFO queues and priority queues — enforce strict ordering semantics that inevitably create memory contention, limiting scalability. Semantic relaxation has emerged as a powerful technique for increasing parallelism at the expense of a controlled weakening of the ordering semantics. However, many open questions remain in the field of relaxed data structures, both in the terms of efficient, flexible designs, and in their practical applicability.

This thesis advances the theory and practice of relaxed concurrent data structures. First, we revisit the classic balanced allocations paradigm in the context of queues, introducing the d-CBO relaxed FIFO queue. The d-CBO queue utilizes the classical d-choice in a new way to evenly balance operation counts across sub-queues. Our analysis shows provably low, stable relaxation errors, and experiments demonstrate a better relaxation-performance trade-off than previous relaxed FIFO designs.

Second, we explore the applicability of relaxation in graph analytics. Using a relaxed priority queue in a parallel Single-Source Shortest Path (SSSP) implementation, we achieve state-of-the-art performance on sparse graphs and remain competitive across other graph types. Our findings show that relaxed designs can be used within parallel algorithms to outperform state-of-the-art without extensive parameter tuning or problem-specific tailoring.

Finally, we introduce the concept of elastic relaxation, which enables relaxed implementations to adjust their semantics dynamically during run time. We extend a state-of-the-art framework for relaxed data structures to support elastic variants of queues, stacks, deques, and counters, with correctness guarantees and deterministic relaxation bounds. Experiments show that these elastic capabilities incur minimal overhead. When combined with a lightweight controller for relaxation, they demonstrated an improved trade-off between throughput and work-efficiency compared to static designs.

#### **Keywords**

Semantic Relaxation, Concurrency, Data Structures, Multicore, Shared-Memory, FIFO Queue, Single-Source Shortest Path, Elastic Relaxation

# List of Publications

# Appended publications

This thesis is based on the following publications:

- [Paper A] K. von Geijer, P. Tsigas, E. Johansson, S. Hermansson, Balanced Allocations over Efficient Queues: A Fast Relaxed FIFO Queue Proceedings of the 30th ACM SIGPLAN Annual Symposium on Principles and Practice of Parallel Programming (PPoPP), 2025, pp. 382–395.

- [Paper B] M. D'Antonio\*, K. von Geijer\*, T. Son Mai, P. Tsigas, H. Van-dierendonck, Relax and don't Stop: Graph-Aware Asynchronous SSSP Proceedings of the 1st FastCode Programming Challenge (FCPC), 2025, pp. 43-47.

- [Paper C] K. von Geijer, P. Tsigas, Elastic Relaxation of Concurrent Data Structures IEEE Transactions on Parallel and Distributed Systems (TPDS), 2025, vol. 36, no. 12, pp. 2578–2595.

<sup>\*</sup>Authors contributed equally

# Other publications

The following publications were published during my PhD studies, or are currently in submission/under revision. However, they are not appended to this thesis, due to contents overlapping that of appended publications or contents not related to the thesis.

[Paper a] K. von Geijer, P. Tsigas, How to Relax Instantly: Elastic Relaxation of Concurrent Data Structures

Euro-Par 2024: Parallel Processing, 2024, pp. 119-133.

# Research Contribution

I was the lead author, designer, and implementor in **Paper A**, **Paper C**, and **Paper a**. Me and Marco D'Antonio shared the lead equally in **Paper B**.

# Acknowledgment

First of all, I am grateful for my supervisor Philippas Tsigas for his steady guidance and trust in me. Thank you for always listening to my ideas, for our many discussions, and for taking a chance on me. I would also like to thank my co-supervisors Marina Papatriantafilou, for always checking in with me and for providing many teaching opportunities, and Vincenzo Massimiliano Gulisano, for your feedback and discussions. Thank you Marvin Williams for discussions regarding the analysis of the d-choice and multi-queue designs. Furthermore, many thanks to Marco D'Antonio and Hans Vandierendonck for our fruitful collaboration and interesting discussions.

I am honored and thankful to have professor Michael Spear serve as the discussion leader for my Licentiate seminar. I am also grateful for my Ph.D. examiner Aarne Ranta for his support.

I want to thank all the teachers and mentors I have had over the years, for believing in me and pushing me to go further. Thank you, Jonas Johnsson, for getting me to participate in Skolornas matematiktävling and for your warm teaching style. Thank you Jonas Skeppstedt for your interesting courses, contagious enthusiasm, and for helping me take my first steps toward pursuing a Ph.D.

A special thank you to Martin, Yixing, Vinh, Jingyu, and Jacob for making the journey so enjoyable. I want to thank my dear colleagues for all the corridor chats and for making a nice work environment (including, but not limited to): Huaifeng, Yenan, Atmane, Hashim, Wanya, Umer, Magnus, Romaric, Moui, Elad, and Thomas. Thank you to Katya, Lorenzo, and Krishna, whom I enjoyed working with in the Ph.D. council. I also want to thank those who came before, for warmly welcoming me into the group during my master thesis visit and during the start of my Ph.D. Thank you Dimitrios, Christos, Georgia, Bastian, and Kalle.

I want to express my gratitude to the Swedish Research Council for providing funding for my Ph.D. under grant No. 2021-05443.

Finally, I want to thank my family and friends. Thank you to my parents, for your unwavering love and support. I would never have gotten here without you. Thank you, Hanna, for always being there for me and brightening my days. At last, thank you to my lovely friends. I feel so lucky to have you all, and I am looking forward to continuing to enjoy your friendship throughout life.

# Contents

| <b>A</b> b     | stra                   | .ct    |                                                        | iii |

|----------------|------------------------|--------|--------------------------------------------------------|-----|

| $\mathbf{Lis}$ | t of                   | Publi  | cations                                                | v   |

| $\mathbf{Ac}$  | knov                   | wledgr | nent                                                   | vii |

| I              | $\mathbf{T}\mathbf{h}$ | esis ( | Overview                                               | 1   |

|                | 1                      | Introd | $\operatorname{luction}$                               | 3   |

|                | 2                      | Share  | d-Memory Multicore Systems                             | 4   |

|                |                        | 2.1    | System and Memory Model                                | 5   |

|                |                        | 2.2    | Atomic Primitives                                      | 6   |

|                | 3                      | Synch  | ronization                                             | 8   |

|                |                        | 3.1    | Blocking Methods                                       | 8   |

|                |                        | 3.2    | Non-blocking Methods                                   | 6   |

|                | 4                      |        | ırrent Data Structures                                 | 10  |

|                |                        | 4.1    | Correctness                                            | 11  |

|                |                        | 4.2    | Memory Reclamation                                     | 11  |

|                |                        | 4.3    | Non-blocking Concurrent Data Structures                | 12  |

|                | 5                      |        | ed Concurrent Data Structures and Research Questions . | 16  |

|                |                        | 5.1    | Correctness                                            | 17  |

|                |                        | 5.2    | Relaxed Concurrent FIFO Queues                         | 18  |

|                |                        | 5.3    | Relaxed Concurrent Priority Queues                     | 19  |

|                | 6                      |        | s Contributions                                        | 20  |

|                |                        | 6.1    | Efficient Relaxed Data Structure Designs               | 20  |

|                |                        | 6.2    | Relaxation in Efficient Graph Processing               | 21  |

|                | -                      | 6.3    | Elastic Relaxation of Concurrent Data Structures       | 21  |

|                | 7                      | Conci  | usions and Future Work                                 | 22  |

| Bil            | bliog                  | graphy | •                                                      | 23  |

| II             | Λ                      | nnan   | ded Papers                                             | 31  |

| 11             | А                      | bben   | ucu i apeis                                            | 91  |

|                | _                      |        | Balanced Allocations over Efficient Queues: A Fas      |     |

|                | Rela                   | axed I | FIFO Queue                                             | 33  |

X CONTENTS

| 1             | Intro         | $\operatorname{duction} \ldots \ldots$ | 86 |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2             | Relat         | ed Work                                                                                                                                  | 8  |

| 3             | Algor         | rithmic Description                                                                                                                      | 10 |

| 4             |               |                                                                                                                                          | 12 |

|               | 4.1           | Probabilistic Relaxation Guarantees                                                                                                      | 12 |

|               | 4.2           | Correctness Guarantees                                                                                                                   | 15 |

| 5             | Imple         | ementations                                                                                                                              | 16 |

|               | 5.1           | Integrating Fast Sub-Queues                                                                                                              | 16 |

|               | 5.2           | -                                                                                                                                        | 18 |

| 6             | Expe          | - · · · · · · · · · · · · · · · · · · ·                                                                                                  | 19 |

|               | 6.1           |                                                                                                                                          | 19 |

|               | 6.2           | v v                                                                                                                                      | 64 |

| 7             | Conc          |                                                                                                                                          | 66 |

| Bi            |               |                                                                                                                                          | 57 |

|               | O             | 1 0                                                                                                                                      |    |

| Paper         | r B - F       | Relax and Don't Stop: Graph-Aware Asynchronous                                                                                           |    |

| $\mathbf{SS}$ | $\mathbf{SP}$ |                                                                                                                                          | 3  |

| 1             | Intro         | duction                                                                                                                                  | 66 |

| 2             | Back          | ground                                                                                                                                   | 57 |

|               | 2.1           | 1 0                                                                                                                                      | 57 |

|               | 2.2           | •                                                                                                                                        | 8  |

| 3             |               |                                                                                                                                          | 8  |

| 4             | The A         | AdaMW Scheduler                                                                                                                          | 8  |

|               | 4.1           | Estimating $\Delta$ in Wasp-mode                                                                                                         | 69 |

|               | 4.2           | Configuring MultiQueue-mode                                                                                                              | 69 |

|               | 4.3           | SSSP Optimizations                                                                                                                       | 69 |

| 5             | Evalu         | $\operatorname{ation} \dots \dots$ | 0  |

| 6             | Conc          | lusion                                                                                                                                   | 73 |

| $\mathbf{Bi}$ | bliogra       | phy                                                                                                                                      | 75 |

| _             | ~ -           |                                                                                                                                          |    |

| -             |               |                                                                                                                                          | 9  |

| 1             |               |                                                                                                                                          | 32 |

| 2             |               |                                                                                                                                          | 34 |

|               | 2.1           |                                                                                                                                          | 34 |

| 3             | _             | ,                                                                                                                                        | 37 |

|               | 3.1           | 1                                                                                                                                        | 88 |

|               | 3.2           | •                                                                                                                                        | 00 |

|               | 3.3           |                                                                                                                                          | )1 |

|               | 3.4           | 1                                                                                                                                        | 93 |

|               | 3.5           | 1                                                                                                                                        | 95 |

|               | 3.6           | 1                                                                                                                                        | 97 |

| 4             | Analy         | <b>,</b>                                                                                                                                 | 9  |

|               | 4.1           | Elastic LpW Queue                                                                                                                        |    |

|               | 4.2           | Elastic LaW Queue                                                                                                                        |    |

|               | 4.3           | Elastic LaW Stack                                                                                                                        |    |

|               | 4.4           | Elastic LpW 2D Stack                                                                                                                     |    |

|               | 4.5           | Elastic LaW 2D Deque                                                                                                                     | )4 |

CONTENTS xi

|      | 4.6    | Elast  | ic I | ĹpV  | V 2 | $^{2}D$ | С  | ou  | $_{ m nt}$ | er |    |     |     |    |   |                     |    |    |   |  |  |  |  | 105 |

|------|--------|--------|------|------|-----|---------|----|-----|------------|----|----|-----|-----|----|---|---------------------|----|----|---|--|--|--|--|-----|

| 5    | Experi | mentə  | ılΕ  | val  | ua  | tio     | n. |     |            |    |    |     |     |    |   |                     |    |    |   |  |  |  |  | 105 |

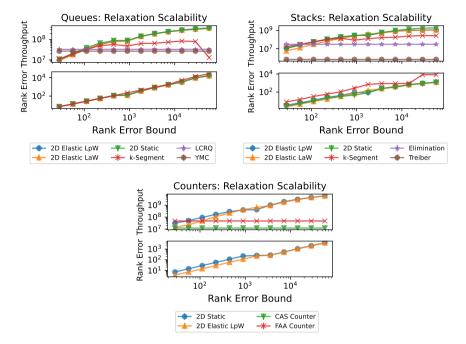

|      | 5.1    | Statio | c R  | elaz | xat | io      | n. |     |            |    |    |     |     |    |   |                     |    |    |   |  |  |  |  | 106 |

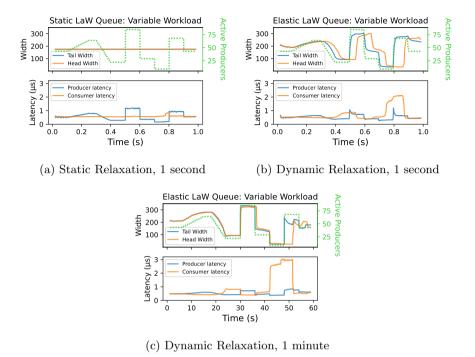

|      | 5.2    | Elast  | ic I | Rela | axa | tic     | n  | - ] | Dу         | 'n | an | nie | c ( | Co | n | $\operatorname{tr}$ | ol | le | r |  |  |  |  | 108 |

| 6    | Relate | d Wor  | k.   |      |     |         |    |     |            |    |    |     |     |    |   |                     |    |    |   |  |  |  |  | 114 |

| 7    | Conclu | sion   |      |      |     |         |    |     |            |    |    |     |     |    |   |                     |    |    |   |  |  |  |  | 115 |

| Bibl | iograp | hy .   |      |      |     |         |    |     |            |    |    |     |     |    |   |                     |    |    |   |  |  |  |  | 117 |

# Part I Thesis Overview

# 1 Introduction

The exponential growth predicted by Moore's Law [1], [2] has defined the evolution of computer hardware for over half a century. This so-called law is a prediction from the sixties [1], refined in the seventies [2], by Intel's co-founder Gordon E. Moore who predicted that the number of transistors on a chip would double every two years. This prediction has been incredibly accurate until very recently [3]. For decades, this transistor scaling also translated into rapidly increasing CPU clock frequencies. Around 2005, however, this frequency scaling largely came to an end due to power and thermal limits [4], and architects started turning to parallelism. Since then, computers have shifted from one or a few cores to dozens or hundreds, ushering in the multicore age [5].

While this hardware parallelism allows for a high level of computation, it also places the onus on programmers to efficiently utilize the available parallelism. One of the central challenges in writing parallel programs is how to synchronize threads accessing the same resources [6]. This challenge is not unique to multicore programming, as the idiom "Too many cooks spoil the broth" suggests: coordination is hard. Programmers must ensure threads work effectively toward the same goal, avoid destroying each other's work, and preferably not spending all their time communicating with other threads.

Concurrent data structures are at the heart of many parallel applications. A naïve approach for making a data structure concurrent to completely encapsulate it within a mutual exclusion lock. However, this serializes all access and eliminates most potential parallelism, as only one thread can interact with the data structure at a time. To further exploit multicore hardware, developers use fine-grained synchronization schemes where multiple threads can work concurrently on disjoint parts of the data structure. Among the most prominent techniques enabling high-performance synchronization are lock-free and wait-free data structures [7]. These designs ensure that system progress is never blocked by individual thread failures or delays, yielding both robustness and practical efficiency.

Over the last few decades, the design of concurrent data structures has advanced dramatically. Fundamental structures such as stacks, queues, and lists have been refined to achieve ever-higher performance, leveraging efficient atomic primitives, sophisticated memory models, and careful cache-aware layouts. Despite these advances, many data structures still face scalability limits, as bottlenecks inevitably emerge when hundreds of threads contend for the same shared access point, such as a head or tail pointer. One promising solution to circumventing these issues is relaxed data structures [5], [8], which trade strict semantics for greater scalability. For example, in a relaxed FIFO queue, dequeues need not return the oldest item, and may instead return one of the oldest items. This relaxation preserves the spirit of the queue while enabling designs with far higher parallelism [9]–[12]. Different forms of relaxation have been proposed—ranging from bounded worst-case relaxations [8], [10]–[12] to probabilistic guarantees [9], [11], [13]–[15]—each balancing correctness and performance in distinct ways.

This thesis studies the use of relaxation in concurrent data structures

for shared-memory multicore systems. We focus mostly on queues—such as FIFO, LIFO, deques, and priority queues—whose strict ordering semantics make parallelization hard. Relaxed semantics alleviate this and make higher parallelism possible. Relaxed queues have for example proved efficient schedulers for parallel algorithms [9], [11], [13], [15]–[17]. Furthermore, we also focus on lock-free algorithms, as they provide desirable liveness guarantees and excellent performance in practice. In broad strokes, this thesis spans the area of relaxation by (i) designing a new relaxed FIFO queue in Paper A, (ii) efficiently utilizing relaxed data structures for graph traversals in Paper B, and (iii) extends pre-existing designs with elastic relaxation in Paper C.

The thesis is structured in two parts: Thesis Overview and Appended Papers. The thesis overview starts with this introduction. Section 2 then covers some basics of modern shared-memory multicore systems. Section 3 describes different shared-memory synchronization strategies, like non-blocking algorithms. Section 4 covers concurrent data structures, including correctness conditions, memory reclamation, and some foundational designs and design patterns. Section 5 similarly covers relaxed concurrent data structures, and also highlights research questions for the thesis. Section 6 then summarizes the the contributions of the thesis, including how they connect to the research questions. Section 7 concludes the thesis overview part with conclusions and future work directions. The Appended Papers part includes the three papers making up the contributions of this thesis. The appended papers were originally published in peer-reviewed venues and the appended versions differ mainly in presentation, with the following deviations. The appended Paper A includes a revised analysis, establishing the relaxation bound as  $\mathcal{O}(n \log n)$  with high probability, in place of the previously stated  $\mathcal{O}(n \log \log n / \log d)$ . The appended Paper B adds four missing subplots to its Figure 2, which were previously cut due to space constraints.

# 2 Shared-Memory Multicore Systems

Designing practically efficient algorithms requires accounting for the underlying system. For example, state-of-the-art BFS differs greatly on CPUs [18] versus TCUs [19]. This section highlights the hardware aspects of shared-memory multicore systems most relevant to efficient parallel algorithms.

In multicore systems, a *software thread* is an execution context scheduled to run on hardware. We distinguish software threads, which are created by the program, from *hardware threads*, which are execution slots provided by the CPU capable of executing software threads. A multicore CPU has multiple cores, each of which may expose multiple hardware threads, with modern CPUs typically providing 2 hardware threads per core via simultaneous multithreading (SMT). A *process* is an operating system abstraction that contains one or more software threads and its own address space. We use *processor* to mean the physical multicore chip. Theoretical works sometimes use processor to mean an abstract unit of computation (roughly a software thread).

# 2.1 System and Memory Model

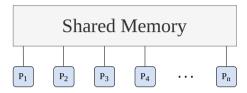

The parallel random-access machine (PRAM) [20], [21] models a shared-memory system with a single memory and many processors (often denoted by P), see Figure 1. Each instruction, including accessing memory, takes one unit of time. The simplicity of PRAM enables clean analyses, but algorithms which are theoretically optimal in PRAM are rarely optimal on real hardware.

Figure 1: PRAM system model.

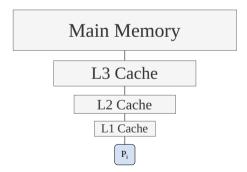

Modern systems have a hierarchical memory architecture [22]. As in Figure 2, several cache levels sit between each core and main memory. The L1 cache is small and fast, holding recently accessed data. Farther levels are larger but slower, with main memory the slowest relevant level for our purposes. Accessed data is brought into the L1 cache and less-used data is evicted to farther (slower) levels to make room for hot data. Caches typically work on a cache line granularily (txypically 64 bytes), instead of tracking and moving individual bytes. A read that finds the requested line in a given cache is a cache hit; otherwise it is a miss. Maximizing cache hits is critical for performance (see, e.g., cache-friendly queues [23]–[26]).

Figure 2: Hierarchical system memory model from the perspective of one core.

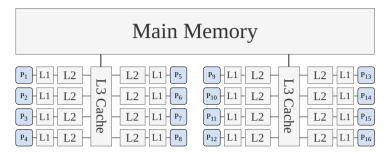

Many systems exhibit non-uniform memory access (NUMA). Figure 3 shows cores grouped into 8-core complexes sharing an L3 cache. If core  $P_1$  reads data used by  $P_2$  in the same complex, the request can be satisfied from the shared L3, avoiding main memory. Accessing data owned by  $P_{16}$  in another complex typically traverses main memory and is slower. Each core commonly exposes two hardware threads (sibling threads) via SMT. Siblings share private resources such as L1. The evaluation platform used in the appended papers (AMD EPYC 9754) has 2 hardware threads per core, 8 cores per complex,

16 complexes per socket (128 cores), and 2 sockets. Algorithm design should minimize inter-complex traffic and prefer locality within NUMA regions when feasible.

Figure 3: Example NUMA topology with two 8-core complexes with one shared L3 cache each.

Hardware provides cache coherence, ensuring that threads observe a consistent value for each memory location at all times. Most systems use invalidation-based protocols (e.g., MESI/MOESI), where multiple caches may hold a shared copy of a value, but writes require first invalidating other copies to obtain exclusivity. Therefore, read-mostly shared data is cheap, but frequently written shared data incurs invalidations and misses, degrading performance. Coherence operates at a cache line granularity. Writing to x invalidates the entire line, potentially evicting nearby y (false sharing). Padding or aligning per-thread data are common methods to avoid false sharing.

Modern CPUs include hardware prefetchers that speculatively fetch cache lines likely to be accessed soon. Common mechanisms include next-line and streaming prefetchers—capturing sequential scans— and simple stride detectors—capturing regular step patterns—. These work well for contiguous data such as arrays, but are far less effective for pointer-chasing structures like linked lists with their irregular access. Effective algorithms therefore structure hot paths to expose simple access patterns the prefetchers can learn, even if this leads to a slightly higher number of memory accesses.

Minimizing cache misses is paramount when designing efficient algorithms. On an AMD EPYC Rome system, typical memory latencies are: L1  $\approx$  2 ns, L2  $\approx$  6 ns, L3  $\approx$  19.5 ns, DRAM  $\approx$  110 ns [27]. Thus, these three principles are useful to keep in mind when designing concurrent algorithms (1: thread locality) minimize writes to data contended by other threads, (2: temporal locality) attempt to return to the same set of data repeatedly, instead of excessively reading new cold memory, (3: spatial locality) prefer contiguous memory layouts such as arrays over pointer-chasing when possible.

#### 2.2 Atomic Primitives

Plain reads and writes are insufficient for implementing many non-blocking synchronization tasks [7]. Consequently, shared-memory CPUs provide a set of atomic read-modify-write (RMW) primitives to coordinate data access

between threads. Atomic means that the operation appears indivisible and from software's perspective takes effect in a single step.

Algorithm 1 gives the semantics of compare-and-swap (CAS) and fetch-and-add (FAA) – the two mainly utilized primitives in this thesis. CAS atomically replaces a memory location with desired iff its current value equals expected; otherwise it fails. Many APIs (e.g., C/C++ atomic.h) overwrite the caller's expected argument on CAS failure with the observed value, for easier implementations of eg. CAS retry loops. CAS can suffer from the ABA problem on pointer-like values, and common mitigations include version tagging or hazard pointers (see §4.3). Some platforms provide load-linked/store-conditional (LL/SC) instead of CAS, which in turn can implement CAS. In practice, most portable libraries expose CAS-like operations, so algorithm descriptions usually assume CAS. On x86 processors, CAS is supported for up to 128-bit wide variables [28], but other architectures such as ARM only support up to 64-bit wide CAS [29]. x86-64 supports 16-byte CAS (e.g., CMPXCHG16B) [28]. On ARM, availability depends on the extension set and many systems only guarantee CAS up to 64 bits [29].

FAA atomically adds an integer to a location and returns the old value. Unlike CAS, FAA can not fail due to interference, so it often scales better for counters, indices, and ticket-style allocation. In highly contended hotspots, replacing CAS with FAA (when semantics allow) can markedly improve throughput. This is for example seen in the LCRQ [23] FIFO queue, which shifts a hot-spot from CAS to FAA and significantly outscales earlier works. However, FAA is still a RMW operation and thus generates coherence traffic, meaning excessive use can remain a bottleneck.

**Algorithm 1:** Semantics of compare-and-swap (CAS) and fetch-and-add (FAA).

```

1.1 function CAS(address: pointer, expected: type, desired: type) \rightarrow bool

1.2

atomically do

if *address = expected then

1.3

*address \leftarrow desired;

1.4

return true;

1.5

else return false;

1.6

1.7 function FAA(address: pointer, increment: integer) \rightarrow integer

atomically do

1.8

oldvalue \leftarrow *address;

1.9

*address \leftarrow oldvalue + increment;

1.10

return oldvalue;

1.11

```

# 3 Synchronization

When several threads cooperate on a task, they must at some point synchronize to reach a consistent shared state. On shared-memory multicore systems, synchronization relies on atomic primitives (§2.2) combined into different strategies. The two main approaches are blocking (§3.1), which is simpler to use, and non-blocking (§3.2), which is more intricate but can be more efficient.

# 3.1 Blocking Methods

The traditional way of synchronizing access to some shared state is through mutual exclusion. Here we define certain blocks of code as *critical sections*, and ensures that only one thread can be in the critical section at a time. The common way to achieve this is through a *lock* object, which can be seen as a lock around the critical section with a single key. Such lock objects have two main methods: *acquire* and *release*. When a thread calls acquire, it waits its turn until it can get the shared key, after which it takes the key and enters the critical section. During the time the thread is in the critical section, we usually say it holds the lock, or is the lock owner. When the thread is done with the critical section, it calls release to give up the key, either to the next waiting thread or just leaving it for the next thread to arrive. Locks commonly also support the *try-lock* method, which tries to acquire the lock immediately, but if it is already held by another thread, the calling thread aborts to maybe do something else.

The traditional mechanism is *mutual exclusion*. Here, *critical sections* are created – often with *lock* objects – ensuring only one thread enters at a time. A lock typically exposes *acquire*, *release*, and optionally *try\_lock*. A successful acquire operation grants the caller ownership of the lock. A release operation either transfers ownership to the next waiting thread or leaves the lock free. If the lock is already held, try\_lock returns immediately so the caller can perform other work. We typically call the thread with lock ownership the *lock holder*.

Locks are widely used because they are simple and well supported by operating system and language runtimes. Blocking designs are often easier to implement and reason about than non-blocking ones (§3.2). However, they have some drawbacks, as we will soon describe.

There are many flavors of locks, each with different performance and fairness properties. A minimal test-and-set/CAS spinlock (Algorithm 2) flips a shared boolean to to true when aquiring the lock, and flips it back to false on release. Under contention this design causes heavy coherence traffic, which reduces throughput. A ticket lock [30], [31] instead assigns each acquirer a ticket via FAA and grants entry when the serving counter equals its ticket (Algorithm 3). Ticket locks provide FIFO fairness and reduce some contention by separating arrival (ticket) from waiting (serving). However, the single shared serving counter still invalidates globally on each release, causing unnecessary coherence traffic.

Even though there are many nice lock implementations [30]–[36], algorithms using them all suffer from common drawbacks. A major problem is vulnerability

3. SYNCHRONIZATION 9

## Algorithm 2: A minimal CAS spinlock.

## **Algorithm 3:** The Ticket Lock.

to failures, as a stalled or crashed lock holder will prevent others from making progress. Additionally, composing multiple locks can create dependency cycles, where threads wait for each other indefinitely in a deadlock. Finally, time spent spinning or blocking reduces throughput, often leading to sub-optimal parallelism. These issues can be mitigated with scalable locks and careful design, but many high-performance data structures achieve better scalability with non-blocking methods.

# 3.2 Non-blocking Methods

The alternative to blocking is non-blocking synchronization, which avoids critical sections and mutual exclusion. Herlihy and Shavit [37] define non-blocking as a progress condition, where an arbitrary delay of one thread does not prevent other threads from making progress. The main progress conditions are wait-freedom and lock-freedom [7]. The weaker obstruction-freedom [38], also exists but is less commonly used in practice.

Obstruction-freedom [38] guarantees a thread makes progress if it runs in isolation for a finite number of steps. Obstruction-free operations often access multiple shared locations. Under contention, a write by one thread can invalidate another thread's tentative state and force a restart. Because the progress guarantee is weaker, these algorithms are often simpler to implement than lock-free or wait-free ones. Practical implementations often add a con-

tention manager that backs off colliding threads to create isolation windows. With effective contention management, obstruction-free designs can approach wait-free behavior in practice [39], although lacking its worst-case guarantees.

Lock-freedom [7] garantees that one thread makes progress in a finite number of system-wide steps. This is the most common non-blocking guarantee in practice, and many lock-free algorithms tend to behave as if they were wait-free in practice [40]. A classic lock-free pattern is to design data structures around a CAS retry loop [41]–[44], where a thread tries to complete its operation with a single CAS. If the CAS fails, another thread must have succeeded, ensuring the system-wide progress guarantee. Recent designs replace contended CAS loops with FAA where semantics permit [23]–[25]. As FAA cannot fail, updates serialize without retries, reducing wasted work on hot spots.

Wait-freedom [7] is the strongest progress condition, and guarantees that each thread makes progress in a finite number of steps. Unlike lock-freedom, it prevents a few fast threads from monopolizing progress. Universal constructions [7] and general techniques [45], [46] provide general recipes for creating wait-free implementations, but specialized designs often perform better [24]. A common technique is *helping*, where threads assist each other's in-flight operations to guarantee per-thread completion.

Compared to blocking, non-blocking methods provide stronger progress guarantees and often deliver better performance. The trade-off is algorithmic complexity and a higher risk of subtle bugs, which hinders more wide-spread adaption. Nonetheless, for data structures such as queues, stacks, and priority queues, which can often become hot-spots in larger applications, efficient non-blocking designs are well established [23]–[25], [42], [47]–[50]. That said, lock-based approaches can become competitive, for example by utilizing techniques such as batching or combining [51].

# 4 Concurrent Data Structures

Data structures efficiently organize and utilize data, and sit at the core of many algorithms. Concurrent data structures are ones designed to be access concurrently by multiple threads. Concurrency adds a new dimension to the design space, as efficient sequential designs often face difficulties scaling under parallel access. It also introduces correctness concerns since threads must synchronize in ways so that the data structure remains in a consistent state.

When implementing a concurrent data structure, an important decision is whether to design it with blocking (§3.1) or non-blocking (§3.2) synchronization. Blocking is generally simpler, especially with coarse-grained locks, while non-blocking often can reach higher scalability. Designers should also try to optimize for memory locality (§2.1), and avoid designs where many threads mutate the same cache cache line. Furthermore, one should prefer more scalable primitives when semantics allow, for example using FAA instead of CAS loops at hot-spots (§2.2).

## 4.1 Correctness

The most common correctness condition for concurrent data structures is linearizability [52]. Informally, a concurrent data structure is linearizable if all operations on it appears to take effect instantaneously, while upholding the sequential semantics of the data structure. This is powerful, as it unables us to reason about concurrent executions as if operations occurred in a total sequential order.

Linearizability is most easily proven by identifying so called *linearization* points for each operation. This is the instant at which the operation appears to take effect, or *linearize*. With coarse-grained locking, any point between the lock acquisition and release can serve as linearization point. Linearization points can become complex in non-blocking designs. In simple cases like the Michael and Scott queue [41] or Treiber stack [42], the operations repeatedly try to linearize with a single CAS, after which they they get help from other threads with potential finishing writes. Other designs such as LCRQ [23] use a sequence of writes to complete an operation and the linearization point may only be identifiable in retrospect.

For a slightly more complete definition of linearizability, consider a data structure *history* as a set of operation calls with arguments and returns with values. In a sequential history, each call is immediately followed by its return. In a concurrent history, operations from different threads can overlap, so calls and returns form a partial order that respects real-time orderings. A data structure is linearizable if for every partially ordered concurrent history, there exists an extension to a total order that yields a valid sequential history under the data structure specification [52].

Strong linearizability [53] strengthens linearizability by requiring a prefix-preserving mapping from concurrent histories to sequential histories. Intuitively, this means that the choice of linearization point cannot depend on future events. It is surprisingly hard to design strongly linearizable non-blocking data structures, and even very simple classical designs don't satisfy the condition [54]. The advantage of strong linearizability is that it – unlike linearizability – does not allow adversarials schedulers to control the probability distribution of the program result.

Quiescent consistency [6] requires that operations separated by a quiescent period (a period when no operation is executing) appear in real-time order. A data structure satisfies quiescent consistency if (1) all operations appear to take effect once at a time, and (2) all operations separated by a period of quiescence appear to take effect in real-time order. It is weaker than linearizability because it does not preserve real-time order for operations that are not separated by quiescence.

# 4.2 Memory Reclamation

Data structures often work with dynamic memory, which has to be allocated and deallocated (freed) dynamically during an execution. In sequential programs, or when using coarse-grained locking, one can directly free pieces of data when detached from the data structure. In non-blocking or fine-grained locking

designs, immediate deallocation becomes unsafe, as a concurrent traversal may still hold a reference to some node after it has been unlinked. If that node is freed, a reader can dereference an invalid pointer, which results in undefined behavior.

Innumerable memory reclamation schemes have been proposed. As an example, reference counting [55], [56] struggles with cycles and has performance overheads, but are simple to use and for example used by the CPython interpreter [57]. In the literature, two families dominate for non-blocking structures. Hazard pointers (HP) [58] and epoch-based reclamation (EBR) [59].

Hazard pointers [58] provide robust reclamation, even in the presence of thread failures. Each thread publishes the addresses it may dereference in a small array of hazard slots that is visible to others. When a node is unlinked it is retired to a per-thread list. Periodically, each thread scans the published hazard slots across threads and frees nodes in its own list that are not currently protected. If another thread still protects a node, reclamation is deferred. Hazard Pointers adds per-access overhead to protect pointers and incur scans whose complexity grow with the number of threads and hazard slots. They are also not generally applicable in all data structures. Recent works such as Hazard Eras [60] and HP++ [61] work toward improving performance and increasing applicability, respectively.

Epoch-based reclamation [59] trades some robustness for speed and easy of use. The core idea is that a global epoch counter advances over time and that each thread announces the epoch it is operating in. When an object is unlinked it is retired with the current epoch. It can later be freed once every active thread has advanced past the corresponding epoch, ensuring they don't retain any references to deallocated data. The speed of EBR comes from it avoiding per-pointer announcements, only occasionally updating its epoch. Although being fast and easy to applicate, it lacks robustness, as one stalled thread block all further data from being deallocated. Recent work, like Debra+ [62], NBR [63], and PEBR [64], use similar methods to EBR and resolve the robustness issue, but re-introduce issues like applicability.

# 4.3 Non-blocking Concurrent Data Structures

This section surveys classical non-blocking designs and recurring design patterns. It starts with the classical Treiber stack [42] and Michael & Scott queue [41], and then follows up with more efficient state-of-the-art queues such as LCRQ [23]. These designs are fundamental prerequisites for the appended Paper A and Paper C.

A common problem in non-blocking designs is the ABA problem. Consider a data structure which is implemented as a single mutable pointer to an otherwise immutable data structure. To make an operation on the data structure, you copy the whole current state, make a local modification, and then update the shared state by using CAS to change the shared pointer to your modified copy. If another thread has changed the pointer, you have to read the new shared pointer and recompute the new state before trying to linearize with CAS again. Now, the ABA problem is when you read A as the shared pointer and compute

your update, but before your CAS, some other thread swaps the shared pointer to B, deallocates A, allocates a new pointer which becomes A, and then uses CAS to change B to A. In this case, your CAS will succeed, as the shared pointer was A, as you expected, but what the pointer actually pointed to had changed, making your update incorrect. This is an important problem to keep in mind when using CAS. It can often be solved by a good memory reclamation scheme (§4.2), or by embedding a strict monotonic counter into the CAS object which makes the CAS distinguish identical states based on the counter.

A recurring pitfall is the ABA problem. The key issue is that CAS compares only value equality, not distinguishing different writes of one value. Suppose a shared pointer has value A. A thread reads A and prepares an update. Meanwhile another thread changes the pointer to B, frees the node at A, then allocates a new node that reuses the same address A, which is finally written back to the shared pointer. The first thread now sees the expected value A and its CAS succeeds, even though the underlying object is not the one it observed. Mitigations include robust memory reclamation that prevents reuse while references may exist (§4.2), and tagged pointers that pair the pointer with a version counter. Tags can overflow on small counters, so tagged pointers reduce rather than eliminate risk in some cases.

## 4.3.1 A Simple Lock-free Stack

The Treiber stack [42] is a beautifully simple lock-free stack, shown in Algorithm 4. The shared state is only the pointer to its top node. Each stack node stores a value and a link to the next node. A push reads the current top, sets the new node's next pointer to that top, and then uses CAS to swing the top pointer to the new node, restarting if failing the CAS. Similarly, popping a node from the stack also uses a CAS retry loop, trying to swing the top pointer to the second node in the stack.

This CAS-retry pattern appears in many lock-free designs. In this simple design, nodes are immutable after insertion and the only mutable shared state is the top pointer. Thus, operations repeatedly try to linearize with a successful CAS, and after a failed CAS do some small recomputations before trying to linearize again.

Algorithm 4 omits memory reclamation by design. The Treiber stack is commonly paired with hazard pointers [58] or EBR [59] as discussed in Section 4.2.

Finally, the Treiber stack is a great example of the ABA problem in action. With nodes A and B on the stack, thread 1 initiates a pop, reads A as the top, its next node as B, and then stalls. Thread 2 pops twice and later pushes a node that reuses A's address. Thread 1 resumes and its CAS on the top pointer from A to B now succeeds, even though the node at A is different. Robust reclamation (§4.2) or a tagged top pointer, avoids the bug. Tags must be sized to avoid wraparound in the expected lifetime of the program, with implementations often relying on the 16-byte CAS of x86-64 [28].

#### Algorithm 4: The Treiber Stack.

```

4.1 struct Stack

top: *StackNode;

4.3 struct StackNode

4.4

data: Any;

next: *StackNode;

4.5

4.6 function push(stack: *Stack, value: Any)

new\_top \leftarrow StackNode\{.data = value\};

4.7

4.8

do

new\_top.next \leftarrow stack.top;

49

while !CAS(&stack.top, new_top.next, new_top);

4.11 function pop(stack: *Stack) \rightarrow Any|Null

do

4.12

top \leftarrow stack.top;

4.13

if top = Null then return Null;

4.14

4.15

next \leftarrow top.next;

while !CAS(&stack.top, top, next);

4.16

4.17

return top.data;

```

## 4.3.2 A Simple Lock-free Queue

The Michael and Scott (MS) FIFO queue [41] is the most foundational lock-free FIFO queue, and influences many later designs [10], [11], [23]–[25]. Algorithm 5 shows the simplified pseudocode, again omitting memory reclamation for simplicity.

Like the Treiber stack [42], the MS queue uses CAS loops to link and unlink nodes. A successful dequeue linearizes when CAS advances the head to the successive node at line 5.31. Enqueues linearize at line 5.17 by making the previous tail point to the newly enqueued node. Updating the shared tail pointer is a best-effort update for efficient tail access and any thread may help advance it at lines 5.18, 5.15, 5.28.

The drawback shared by both the MS queue and the Treiber stack is that they suffer poor scalability under high contention. When many threads want to dequeue an item at once, they all enter a CAS retry loop trying to update the same head pointer. This causes cache-line bouncing and a high rate of failed CAS attempts.

#### 4.3.3 Faster Lock-free Queues

There have been many lock-free FIFO queue designs which improve on the MS queue [26], [44], [65], [66]. The LCRQ [23] was the first design to efficiently replace the CAS retry loop with FAA, achieving significantly improved scalability. It organizes the queue as a linked list – as the MS queue – of cyclic ring buffers. Each buffer maintains head and tail indices, which are updated with FAA. An enqueue (dequeue) reserves a slot by using FAA on the tail

## Algorithm 5: The Michael & Scott FIFO Queue.

```

5.1 struct Queue

head: *QueueNode;

5.2

tail: *QueueNode;

5.3

5.4 struct QueueNode

5.5

data: Any:

next: *QueueNode;

5.6

5.7 function create_queue() \rightarrow Queue

dummy \leftarrow QueueNode\{.next = Null\};

5.8

return Queue{.head = dummy, .tail = dummy};

5.9

5.10 function enqueue(queue: *Queue, value: Any)

new\_tail \leftarrow QueueNode\{.data = value, .next = Null\};

5.11

5.12

do

old_{tail} \leftarrow queue.tail;

5.13

if old_tail.next \neq Null then

5.14

5.15

CAS(&queue.tail, old_tail, old_tail.next);

continue;

5.16

while !CAS(&old_tail.next, Null, new_tail);

5.17

CAS(&queue.tail, old_tail, new_tail);

5.18

5.19

function dequeue(queue: *Queue) \rightarrow Any|Null

while true do

5.20

head \leftarrow queue.head;

5.21

tail \leftarrow queue.tail;

5.22

next \leftarrow head.next;

5.23

if head = queue.head then

5.24

if head = tail then

5.25

if next = Null then;

5.26

return Null;

5.27

CAS(&queue.tail, tail, tail.next);

5.28

else

5.29

data \leftarrow next.data;

5.30

if CAS(&queue.head, head, next) then return data;

5.31

```

(head) buffer's tail (head) counter and writes (reads) its value to (from) the reserved index. The design includes mechanisms to handle wraparound, close and allocate new buffers, reclaim empty buffers, and preserve lock-freedom under stalled producers and consumers. The core idea is that hot spots are changed from CAS loops to FAA increments. This allows the LCRQ to scale significantly better than earlier works, and it is still among state-of-the-art.

One problem with the LCRQ is that it requires CAS2 (128-bit wide CAS). This is due to it having to write both the enqueued value itself into the buffer, as well as some metadata for the cyclic nature of the queue. A practical issue for LCRQ is the need for a wide (16-byte) CAS to update a value together with its metadata atomically. This is included for the cyclic buffers to function correctly. As CAS2 is not generally accessible in hardware, a recent work introduces the LPRQ [67] as a portable modification that only uses regularly sized CAS, while retaining similar performance.

The FAAArrayQueue [25] adopts the FAA reservation idea of the LCRQ, but removes its cyclic buffers. This trades some space efficiency at small sizes for a simpler algorithm that is easier to understand and extend. It performs very similarly to the LCRQ in many benchmarks.

The YMC queue [24] also builds on the LCRQ but removes its cyclic buffers to be able to achieve wait-freedom. It uses a fast-path that mirrors the FAA-reservation pattern and a slow-path that guarantees per-thread completion, following the fast-path slow-path approach [45]. Most operations take the fast-path while the slow-path enforces the wait-free bound with helping.

# 5 Relaxed Concurrent Data Structures and Research Questions

Although there are many smart data structure designs optimized for scalability, many of them still suffer from limited parallelism. For example, in the LCRQ [23] lock-free queue, all enqueues and dequeues contend for calling FAA on the tail or head counter, respectively. FAA does not fail like CAS, but the frequency at which the counter's cache line bounces between cores becomes a significant bottleneck. As long as operations modify a few shared variables, such as head or tail pointers or counters, these access points will incur high synchronization costs and become scalability bottlenecks.

Relaxed concurrent data structures alleviate the bottleneck of a few shared access points [5]. The mos common form is *out-of-order* relaxation [8], where the order of linearized operations may deviate up to some distance from the sequential specification. This deviation can be bounded deterministically [8], [10]–[12], [68] or probabilistically [9], [11], [13], [14], [69]. By changing the specification, operations no longer have to access the same few memory locations, allowing higher parallelism at the cost of some controlled disorder.

As an example, out-of-order relaxed FIFO queues [8] allow the dequeue operation to return out of order with respect to the linearization order of the corresponding enqueue operations. If using a bounded relaxation bound of k, such as the 2D queue [10], the dequeue may return any of the k+1 oldest

items in the queue. If there are fewer than k+1 dequeueing threads, then implementations could in theory direct each thread to dequeue a different item in parallel, alleviating the load on a single memory location.

A common design pattern for out-of-order designs is to split the data structure into n disjoint *sub-structures*. For instance, a relaxed FIFO queue can be built from n MS queues [41] as sub-queues. Then, each operation is directed to linearize on one of the n sub-queues. Different ways of selecting sub-queues to operate on results in different trade-offs between performance and relaxation [9]–[11], [13].

#### 5.1 Correctness

One advantage of this type of relaxed data structures is that only the data structure semantics are relaxed, meaning linearizability [52] can still be used as a correctness condition. The most common semantic relaxation is out-of-order relaxation. Here, the order of operations is relaxed, but all other properties, like only deueueing each enqueued once, are retained. The effect of the relaxation is measured by the relaxation error of each operation, and the two main such errors are rank errors and delays. The rank error is the number of previous operations we would ignore to make the relaxed operation correct, such as the number of items with higher rank than the dequeued item in a priority queue. Delay is used mainly for queues and, for each dequeued item, counts how many other dequeues utilize relaxation to skip the specified item, effectively postponing its removal.

Quantitative relaxation is a theoretical framework for defining semantic relaxations. The idea is to define a cost function over the transitions between each two states in the linearized history. The paper defines k-relaxation, where each such transition cost is bounded by k. The framework formalizes and introduces k-out-of-order relaxation, and its  $rank\ errors$  (although with another term). It is a useful foundation for defining relaxations, but it only targets relaxations with worst-case bounds. Thes becomes limiting for later designs such as the MultiQueue [70], which only provide probabilistic error guarantees rather than worst-case bounds.

Following quantitative relaxation [8], distributional linearizability [14] was proposed as a correctness condition for relaxed concurrent data structures with probabilistic bounds. The paper [14] also gavn an early analysis of the popular MultiQueue [70], under simplifying assumptions. Adaption has been limited, likely because the model includes the scheduler of the concurrent algorithm. Later work often simplifies the analysis to the sequential setting, where it derives probabilistic bounds on the relaxation errors [9], [13], [71].

In summary, relaxation errors are measured in linearized histories, meaning linearizability first has to be used to linearize the concurrent history. The main error is the out-of-order rank error, formalized by quantitative relaxation [8]. A second common error is the delay, mainly used for queues [9], [72]. Although quantitative relaxation [8] and distributional linearizability [14] cover many designs, they assume static relaxation and do not caputer designs where the relaxation can be reconfigured on the fly. This leads to our first research

question:

#### Research Question 1

What is a good correctness condition for relaxed data structures where the relaxation can be re-configured during runtime?

## 5.2 Relaxed Concurrent FIFO Queues

FIFO queues, together with priority queues, are among the most studied relaxed data structures. Here we highlight a few of the prominent relaxed FIFO queues.

The k-segment queue [12] is perhaps the simplest relaxed FIFO queue. It can be seen as a MS queue [41] whose nodes are segments of size k. Operations respect the order between segments, while the order within a segment is unspecified. For example, when enqueueing an item, the thread searches for an empty slot in the tail segment, trying to linearize by writing its item into that slot with a CAS. If no slot is found, a new segment is enqueued in an MS queue fashion. The design is simple and yields rank error and delay bounds of k-1. However, it suffers from scalability issues as the search for a valid spot becomes a bottleneck at larger values of k.

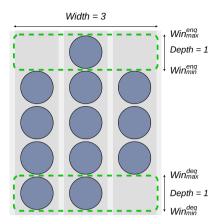

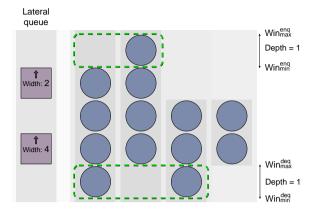

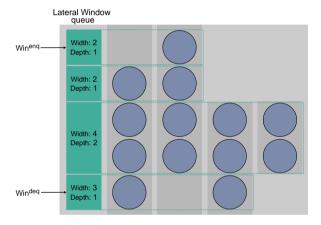

The 2D framework [10] defines relaxed counters, a FIFO queue, LIFO queues, and a deque, with worst-case rank errors. The idea is use n sub-structures and superimpose a window of a given depth over the sub-structures. The window specifies what sub-structures are eligible to linearize on, for example being allowed to do depth linearizations on each sub-structure each window. As in the k-queue [12], the order within a window is undefined, but the order between windows is preserved. For a 2D queue with window depth of 4, threads may enqueue up to 4 items per sub-queue each window, with each subqueue becoming saturated after the fourth enqueue. When all sub-queues are saturated, the window shifts upward, enabling 4 more enqueues per sub-queue. The queue maintains two windows, one at the tail for enqueues and one at the head for dequeues. The 2D queue uses MS queues [41] as sub-queues. The 2D queue resembles the k-segment queue but improves scalability via the window depth, reducing search time and improving memory locality. To our knowledge, it is the fastest published relaxed FIFO queue with bounded rank and delay errors, especially at higher allowed relaxation levels.

The d-RA queue [11] takes a different approach than k-segment [8], [12] and 2D [10] queues. It maintains n sub-queues, implemented as MS queues [41]. To enqueue an item, a thread samples d sub-queues ( $d \geq 2$ ) at random, estimating their sizes from head and tail ABA counters, and linearizes on the smallest sampled sub-queue. Similarly, dequeues linearize on the largest of the d sampled sub-queues. This yields good scalability as the sampling cost is independent of thread count and number of sub-queues. However, the paper does not give theoretical guarantees on relaxation errors, which leads to our second research question:

#### Research Question 2

Does the d-RA load-balancing scheme provide probabilistic guarantees on rank or delay errors? If not, can it be adapted so that errors solely depend on the number of sub-queues?

There are other relaxed FIFO queues, such as the family of distributed queues [11], but the above implementations cover state-of-the-art. Currently, all relaxed queues using the sub-queue design pattern, such as the d-RA [11], distributed queues [11], and 2D queue [10], use the MS queue [41] as their sub-queue. However, as noted in Section 4.3, the MS queue slower compared than more recent FIFO designs. This leads us to our next research question:

#### Research Question 3

Can state-of-the-art FIFO queues be integrated as sub-queues in relaxed FIFO queues to improve performance?

# 5.3 Relaxed Concurrent Priority Queues

Relaxed priority queues have received significant attention recent years, in part due to their potential to parallelize algorithms like single-source shortest-path (SSSP) [13], [15]–[17], [68]. The SprayList [69] keeps a concurrent skiplist [73] with non-relaxed insertions, while deletions perform a random walk to remove an item near the head, spreading out operations and reducing contention. The k-LSM [68] keeps a small per-thread LSM [74], only synchronizing with an unbounded shared LSM when the local becomes full. Deletions remove the highest priority item from the local and one of the highest priority ones in the shared LSM. The CA-PQ [75] follows a similar idea with an unbounded shared priority queue, and threads insert and delete items in large batches under high contention. These designs all have their own trade-offs, and are able to significantly outperform strict concurrent priority queues.

The most popular relaxed priority queue design in recent years is the MultiQueue [70], similar in spirit to d-RA (§5.2). It maintains n concurrent priority queues as sub-queues. Each insertion linearizes at one sub-queue uniformly at random. Each deletion samples d sub-queues ( $d \geq 2$ ) and deletes from the sub-queue whose top has the highest priority. The beauty of the MultiQueue is its simplicity and extensibility. Furthermore, there has been significant efforts in theoretically analyzing the MultiQueue, showing that its relaxation errors can be probabilistically bounded in terms of the number of sub-queues [14], [71], [76], under some simplifying assumptions.

Although the base MultiQueue [70] scales well and exhibit low relaxation error, it suffers from poor cache locality, as each operation tends to sample and linearize on different sub-queues. Recent extensions [13], [72] mitigate this with buffering and stickiness. Buffering adds flat insertion and deletion buffers in front of each sub-queue so that most operations only hit a flat buffer, improving spatial locality. Stickiness alters the load balancing such that each thread stays

with a small set of sub-queues for several successive operations, improving temporal locality at the cost of higher relaxation errors. These optimizations lead to a very fast implementation with good rank-error guarantees that outperforms earlier relaxed priority queues on most benchmarks.

The base MultiQueue idea [70] also gave rise to variants such as the Stealing MultiQueue [17] and MultiBucketQueue [15]. These show strong results on SSSP and related benchmarks, but often require careful tuning across inputs to reach peak performance. It would be preferable if one could use a less specialized data structure that required less tuning to be used efficiently for general algorithms such as SSSP, which leads into our final research question:

#### Research Question 4

Can general relaxed data structures be competitive as parallel schedulers against tailored state-of-the-art algorithms in parallel graph processing problems?

## 6 Thesis Contributions

This section briefly describes the main contributions of each appended paper and how they relate to the research questions in Section 5.

# 6.1 Efficient Relaxed Data Structure Designs

Relaxed data structures should ideally have high performance, for example measured in throughput or latency, while keeping relaxation errors close to zero. In practice this is rarely achievable, so designs must carefully balance performance and relaxation.

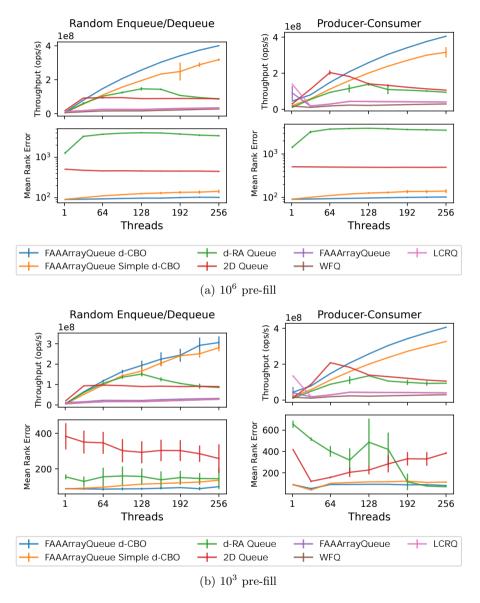

As described in Section 5, the sub-structure design pattern is popular for creating relaxed designs. As noted in Research Question 2, the d-RA queue [11] achieves great scalability with threads, but lacks analysis of its relaxation errors. In Paper A, we show that the d-RA rank errors can scale with queue size, which is neither expected nor prefered.

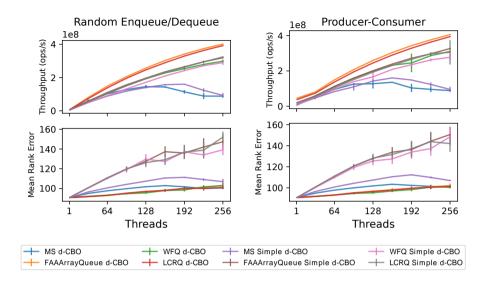

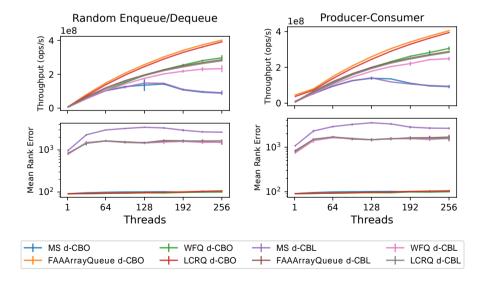

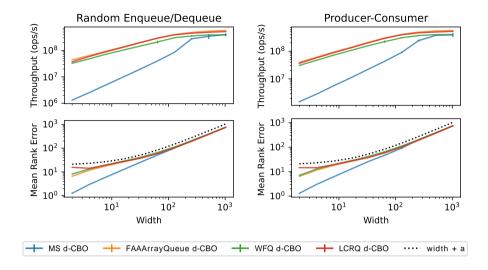

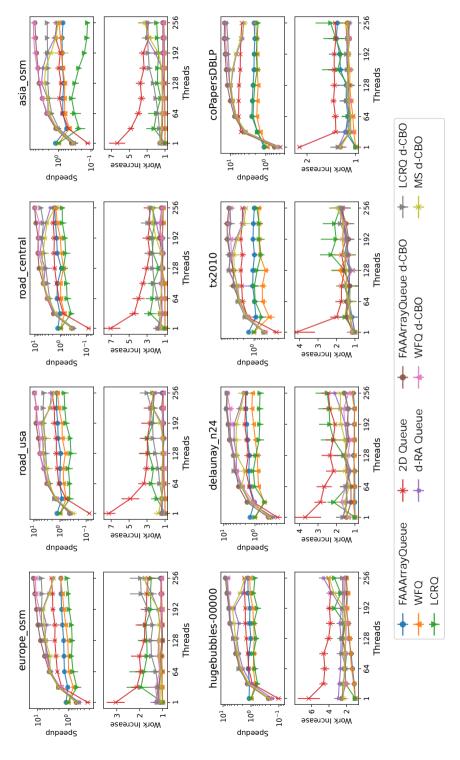

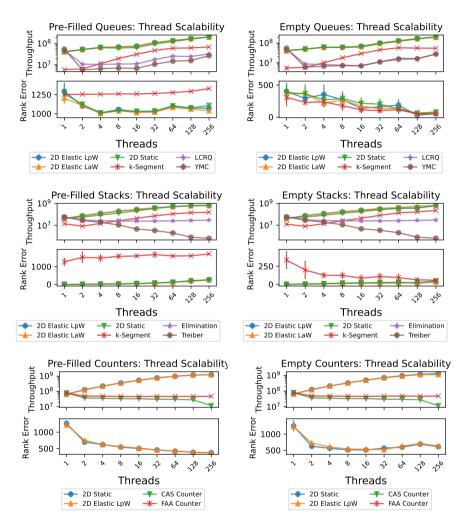

Paper A introduces the d-CBO queue, which similarly to d-RA uses the d-choice [77] to select sub-queue for operations, although in a different manner. It retains good scalability, while simultaneously probabilistically bounding relaxation errors with the number of sub-queues. The d-CBO selects a sub-queue for its enqueue (dequeue) by sampling d sub-queues and linearizing on the sampled one with fewest earlier enqueues (dequeues). Our analysis shows that, with high probability in n (the number of sub-queues), the d-CBO queue has delay and rank errors of  $\mathcal{O}(n \log n)$  under some simplifying assumptions following the MultiQueue analysis [14], [71], [72], [76]. Experimentally, the d-CBO has stable, low rank errors, averaging around n for d = 2.

While the d-CBO queue has low relaxation errors, good designs must also be fast. As highlighted by Research Question 3, one method to increase performance is to use faster sub-structures. State-of-the-art FIFO queues are harder to use as sub-queues than the MS queue [41], but the d-CBO manages to only rely on a generic sub-queue interface that can be implemented by all of the state-of-the-art queues, significantly improving performance.

Thus, the d-CBO design from Paper A both reduces relaxation errors – via a new load balancing scheme – and improves performance – via a flexible, simple interface that suits state-of-the-art concurrent FIFO queues. Compared to d-RA, its most similar competitor, it simultaneously achieves higher throughput and lower relaxation errors. It offers a better trade-off between relaxation and performance than other state-of-the-art relaxed FIFO queues.

# 6.2 Relaxation in Efficient Graph Processing

One of the exciting applications of relaxed data structures is within graph algorithms such as SSSP. While previous work has applied relaxed data structures to these problems, papers benchmarking against state-of-the-art within these problems [15], [17] often require careful tuning and deviations from simple base relaxed designs like the MultiQueue [70]. Research Question 4 therefore asks whether less custom-tailored relaxed implementations can compete with state-of-the-art within these problems.

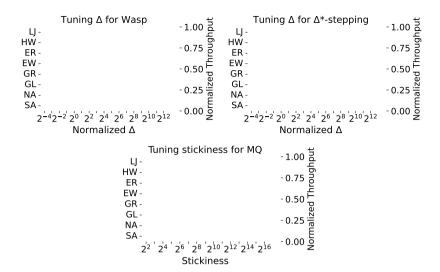

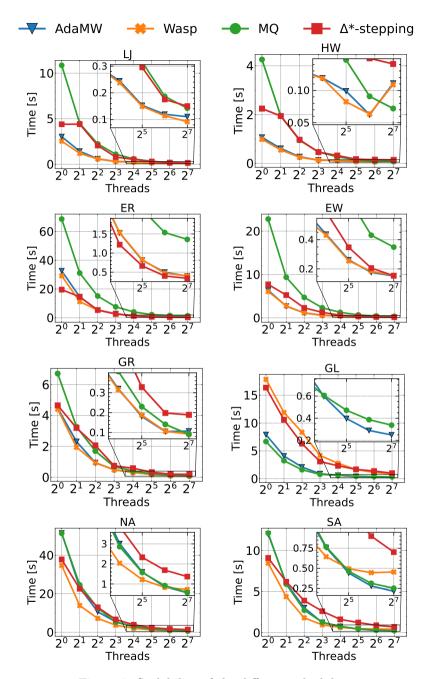

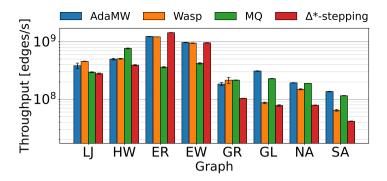

Paper B presents the parallel SSSP solver AdaMW, with which we won the FastCode Programming Challenge at PPoPP 2025, challenging researchers to create the fastest possible parallel SSSP solvers. AdaMW is graph-aware, configuring itself based on sampling the input graph, and selecting either Wasp [78] or the MultiQueue [13] to solve the SSSP. Wasp can be seen as a relaxed sheduler based on bucket queues and work-stealing, but it is not a general relaxed data structure. By contrast, the MultiQueue is an general relaxed priority queue, and with just a few SSSP-specific optimizations, it performed extremely well. On low-diameter graphs, Wasp generally performed better, but the MultiQueue was often very competetive. On high-diameter graphs, the MultiQueue dominated the competition. The paper also showed that the MultiQueue was very forgiving to configuring, while other methods only have a narrow band of optimal settings.

Paper A and Paper C both benchmark their queues on parallel BFS. Paper C shows that elastic relaxation can reduce work and execution time over static relaxation. Paper A shows that the *d*-CBO queue is faster for BFS than other relaxed and non-relaxed concurrent FIFO queues. However, neither paper compares against state-of-the-art BFS algorithms and further work is needed to match direction-optimizing approaches [18], especially on low-diameter graphs.

#### 6.3 Elastic Relaxation of Concurrent Data Structures

As shown in Paper B, optimally configuring relaxed data structures is hard and depends on the characteristics of the targeted workload. Thus, workloads with temporal variation would benefit from relaxed data structures that can be elastically reconfigured at runtime. Research Question 1 thus addresses how such elastic relaxation should work.

Paper C introduces the term *elastic relaxation* for relaxed data structures that can be reconfigured during runtime. The elastic correctness condition builds on the relaxation errors defined in the quantitative relaxation framework [8], but instead of a static bound for the whole execution, the bound is a function of the relaxation history up to that point.

Paper C goes on to extend the 2D framework for relaxed data structures [10] to encompass elastic relaxation. It identifies two patterns for elastically extending 2D data structures, yielding two FIFO queues, two stacks, one counter, and one deque. Experiments show that the elastic capabilities incur negligible overheads when unused. Furthermore, the paper designs a lightweight controller for dynamically adapting relaxation based on contention. Utilizing the dynamic controller demonstrated improved trade-offs between throughput and relaxation errors than static implementations in a parallel BFS macro-benchmark.

# 7 Conclusions and Future Work

This thesis introduces, extends, and applies, out-of-order relaxed concurrent data structures. These data structures achieve far better performance at high thread counts than classical designs – more efficiently utilizing hardware parallelism – and can serve as building blocks in fast parallel algorithms. Our d-CBO queue attains low relaxation errors via a new sub-queue selection scheme and high throughput in part through its use of efficient sub-queues. Our elastic designs can trade relaxation for performance at runtime across a range of data structures. We also apply relaxed data structures to outperform state-of-the-art on SSSP for sparse graphs, indicating the broader value of relaxation in parallel algorithms.

There are several promising directions for future work within relaxation. One direction is to extend the d-CBO queue. Practically, performance could be improved by improving cache locality – for example adding MultiQueue-like stickiness, a key factor in the MultiQueue's competitive SSSP performance. Analytically, it would be useful to analyze rank and delay errors in expectation and extend the theory toward histories better reflect arbitrary concurrent executions.

Another direction is to apply elastic relaxation to relaxed priority queues such as the MultiQueue, given their demonstrated usefulness. Adjusting d in the d-choice, or the stickiness at runtime is straightforward and a natural first step. Efficiently changing the number of sub-queues at runtime is harder and an orthogonal configuration, making it an interesting problem.

Finally, the field of relaxed data structures would benefit from increased cross-pollination with parallel algorithms. We took a step by using the MultiQueue for parallel SSSP in the FCPC competition, and we hope it will be one of many. Since the MultiQueue does not target SSSP specifically, it would be interesting to test competitiveness in parallel algorithms for other problems. Another open question is whether analysis of relaxation errors can be used to bound application properties such as work efficiency.

### Bibliography

- [1] G. E. Moore, 'Cramming more components onto integrated circuits,' *Electronics*, vol. 38, no. 8, pp. 114–117, 1965.

- [2] G. E. Moore, 'Progress in digital integrated electronics [technical literature, copyright 1975 ieee. reprinted, with permission. technical digest. international electron devices meeting, ieee, 1975, pp. 11-13.],' *IEEE Solid-State Circuits Society Newsletter*, vol. 11, no. 3, pp. 36–37, 2006. DOI: 10.1109/N-SSC.2006.4804410.

- [3] C. E. Leiserson, N. C. Thompson, J. S. Emer, B. C. Kuszmaul, B. W. Lampson, D. Sanchez and T. B. Schardl, 'There's plenty of room at the top: What will drive computer performance after moore's law?' Science, vol. 368, no. 6495, eaam9744, 2020. DOI: 10.1126/science.aam9744. eprint: https://www.science.org/doi/pdf/10.1126/science.aam9744.

- [4] P. E. Ross, 'Why cpu frequency stalled,' *IEEE Spectrum*, vol. 45, no. 4, pp. 72–72, 2008. DOI: 10.1109/MSPEC.2008.4476447.

- [5] N. Shavit, 'Data structures in the multicore age,' Commun. ACM, vol. 54, no. 3, pp. 76–84, 2011. DOI: 10.1145/1897852.1897873.

- [6] M. Herlihy, N. Shavit, V. Luchangco and M. Spear, The Art of Multiprocessor Programming. Elsevier Science, 2020.

- [7] M. Herlihy, 'Wait-free synchronization,' ACM Trans. Program. Lang. Syst., vol. 13, no. 1, pp. 124–149, Jan. 1991. DOI: 10.1145/114005. 102808.

- [8] T. A. Henzinger, C. M. Kirsch, H. Payer, A. Sezgin and A. Sokolova, 'Quantitative relaxation of concurrent data structures,' SIGPLAN Not., vol. 48, no. 1, pp. 317–328, 2013. DOI: 10.1145/2480359.2429109.

- [9] K. von Geijer, P. Tsigas, E. Johansson and S. Hermansson, 'Balanced allocations over efficient queues: A fast relaxed fifo queue,' in Proceedings of the 30th ACM SIGPLAN Annual Symposium on Principles and Practice of Parallel Programming, ser. PPoPP '25, Las Vegas, NV, USA: Association for Computing Machinery, 2025, pp. 382–395. DOI: 10.1145/3710848.3710892.

24 Thesis overview

[10] A. Rukundo, A. Atalar and P. Tsigas, 'Monotonically Relaxing Concurrent Data-Structure Semantics for Increasing Performance: An Efficient 2D Design Framework,' in 33rd International Symposium on Distributed Computing (DISC 2019), ser. Leibniz International Proceedings in Informatics (LIPIcs), vol. 146, Dagstuhl, Germany: Schloss Dagstuhl – Leibniz-Zentrum für Informatik, 2019, 31:1–31:15. DOI: 10.4230/LIPIcs. DISC.2019.31.

- [11] A. Haas, M. Lippautz, T. A. Henzinger, H. Payer, A. Sokolova, C. M. Kirsch and A. Sezgin, 'Distributed queues in shared memory: Multicore performance and scalability through quantitative relaxation,' in *Proceedings of the ACM International Conference on Computing Frontiers*, ser. CF '13, Ischia, Italy: Association for Computing Machinery, 2013. DOI: 10.1145/2482767.2482789.