# Ultra-Broadband Frequency Multiplier (x8) Chain in 90-nm SiGe BICMOS Technology at H-Band

Downloaded from: https://research.chalmers.se, 2025-12-04 20:43 UTC

Citation for the original published paper (version of record):

Strömbeck, F., Zirath, H., Aufinger, K. (2025). Ultra-Broadband Frequency Multiplier (x8) Chain in 90-nm SiGe BICMOS Technology at H-Band. 2025 20th European Microwave Integrated Circuits Conference (EuMIC). http://dx.doi.org/10.5281/zenodo.17702944

N.B. When citing this work, cite the original published paper.

research.chalmers.se offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all kind of research output: articles, dissertations, conference papers, reports etc. since 2004. research.chalmers.se is administrated and maintained by Chalmers Library

# Ultra-Broadband Frequency Multiplier (x8) Chain in 90-nm SiGe BiCMOS Technology at H-band

Frida Strömbeck<sup>#1</sup>, Herbert Zirath<sup>#</sup>, Klaus Aufinger<sup>\$</sup>,

\*Microwave Electronics Laboratory, Chalmers University of Technology, Sweden

\$Infineon Technologies AG, Neubiberg, Germany

1 stfrida@chalmers.se

Abstract — This work presents an H-band (220–325 GHz) frequency octupler realized in a 90-nm SiGe BiCMOS process. The 3-dB bandwidth is between 234–305 GHz, resulting in a fractional bandwidth of 26.3 %. The multiplier achieves a conversion gain between 230–310 GHz. The peak output power is -0.5 dBm, using an input power of -5 dBm. The DC power consumption is 122 mW. This type of circuit is suitable for future communication and radar systems.

*Keywords* — 220–325 GHz, Broadband, Frequency multiplier, H-band, Octupler, SiGe, x8

# I. INTRODUCTION

High data rate communication and radar systems are actively taking advantage of the development of semiconductor processes, which support increasing frequencies. The millimeter wave spectrum offers more bandwidth and higher resolution, but struggles with output power. The oscillator design is especially cumbersome at 200+ GHz, which is why frequency multipliers are usually used. Successful high frequency low power multipliers in InP DHBT/HEMT technology have been presented in [1] [2]. However, for large-scale commercial production, silicon technologies are preferred, due to cost and yield. In [3], a 40-nm CMOS x9 multiplier is presented that covers 213 to 233 GHz. For larger bandwidths and higher frequencies, there are several SiGe BiCMOS solutions [4] [5] [6] [7] [8] [9], showing the potential of high-frequency SiGe BiCMOS multipliers. High output power can be achieved, but requires high DC power consumption. For low DC power consumption, the fractional bandwidth is limited. For large fractional bandwidth, the output power is limited.

In this work a power efficient, broadband H-band (220–325 GHz) SiGe BiCMOS octupler is presented. It achieves a conversion gain between 230 and 310 GHz, and the 3-dB bandwidth is between 234 and 305 GHz. The peak output power is -0.5 dBm, and only -5 dBm is needed to drive the frequency multiplier.

## II. CIRCUIT DESIGN

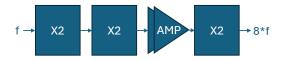

The frequency multiplier is designed and manufactured using a 90-nm SiGe BiCMOS process (B12HFC) developed by Infineon technologies. The process includes high-speed npn HBTs with  $f_t/f_{max}$  of 300 GHz/500 GHz [10]. The frequency multiplier consists of two cascaded frequency doublers, followed by a two-stage buffer amplifier and a

last-stage frequency doubler. The circuit block diagram can be seen in Fig. 1.

Fig. 1. Simple block diagram of the frequency multiplier.

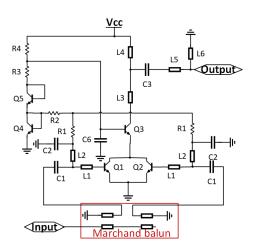

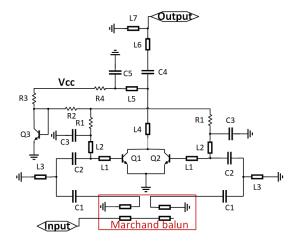

The first two doublers in the multiplier chain use the same topology. The simplified schematic is shown in Fig. 2. It is a class-B biased emitter coupled pair which is differentially fed. The differential signal is created using a passive folded Marchand balun. The combined waveform from the collectors is rich in the second harmonic, while the fundamental and uneven harmonics are ideally canceled out. The output of the combined collectors is fed to the emitter of a cascoded transistor to achieve a higher output power. Both input and output are stub matched to 50  $\Omega$  to enable easy integration. The size of the transistors of the first emitter coupled pair and the cascoded transistor is 8  $\mu$ m. The second stage also has 8  $\mu$ m transistors, but in this case two base fingers are chosen instead of one. This is done to slightly increase the output power while keeping the design energy efficient.

Fig. 2. Simplified schematic of the doublers used in the first two stages.

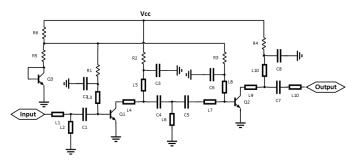

The D-band buffer amplifier is based on a two-stage common emitter topology. The simplified schematic is shown in Fig. 3. The interstage matching has high pass characteristics, to achieve a wideband flat gain, covering the entire D-band. The emitter size of both transistors is 8  $\mu$ m.

Fig. 3. Simplified schematic of the two stage D-band buffer amplifier.

The doubler of the last stage uses a similar design as the first two, excluding the cascoded transistor (Fig. 4). For the upper part of the H-band such a configuration will not provide any gain ( $f_t=300~{\rm GHz}$  in this process). The size of the transistors of the emitter coupled pair is 4  $\mu$ m. All stages in the multiplier chain use internally biased bases, through diod and resistor stacks.

Fig. 4. Simplified schematic of the last stage H-band doubler.

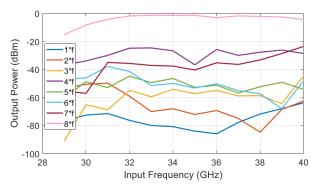

The combined circuit was simulated using Cadence. In Fig. 5, a harmonic balance simulation of the first eight harmonics of the multiplier is shown. The HiCUM model was used and the input power of the multiplier is -5 dBm. The suppression of unwanted harmonics is more than 25 dB.

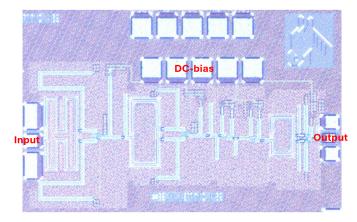

In Fig. 6, a photo of the frequency octupler can be seen, with the input to the left and the output to the right. The circuit is using two different DC-bias (2.4 V and 1.8 V), corresponding to first-stage doublers and buffer amplifier/last-stage doubler. The size of the circuit including the pads is 580  $\mu m \times 1250~\mu m$ , resulting in an area of 0.725  $mm^2$ .

Fig. 5. Simulated harmonics of the frequency multiplier. The input power is  $-5~\mathrm{dBm}$ .

Fig. 6. Photo of the fabricated frequency octupler. The size of the circuit is  $580~\mu m \times 1250~\mu m$  including pads.

# III. MEASUREMENT RESULTS

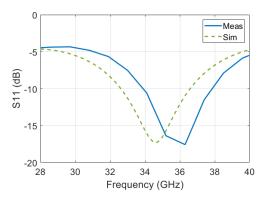

The frequency multiplier was evaluated on-wafer using a probe station (MPI TS200 and Cascade MPS150). The input matching of the multiplier and the D-band buffer amplifier, as well as the D-band balun was measured using a Anritsu VectorStar (ME7838G) broadband VNA. The measured and simulated input matching can be seen in Fig. 7.

Fig. 7. Measured and simulated input matching.

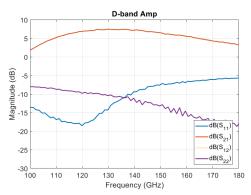

In Fig. 8, the S-parameter measurements of the buffer amplifier are shown. The buffer amplifier's maximum

conversion gain was 7.4 dB, and the 3-dB bandwidth was between 108 and 170 GHz, thus covering the entire D-band.

Fig. 8. Measured conversion gain of the D-band buffer amplifier.

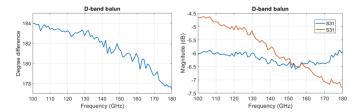

The insertion loss and phase balance of the D-band Marchand balun (a breakout) used at the last stage doubler was also measured. The phase/amplitude imbalance was less than 3.5 degrees and 1.2 dB for the entire D-band. The measurement can be seen in Fig. 9.

Fig. 9. Measured insertion loss and phase balance of the D-band balun, used before the last stage of multiplication.

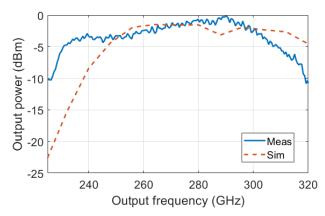

The multiplier's output power was measured using a Keysight PNA-X (67 GHz N5247A). The input signal (-5 dBm) was connected using a coaxial cable and a 67 GHz GGB probe. The output signal was connected through an Infinity probe (I67) and a VDI extender (WR 3.4) to the PNA-X. The measured and simulated output of the 8th harmonic can be seen in Fig. 10. The measured 3-dB bandwidth is between 234 and 305 GHz, and the multiplier achieves a conversion gain between 230 and 310 GHz. That corresponds to a 3-dB fractional bandwidth of 26.3%. The peak output power is -0.5 dBm. The measurement and simulation agree on the output power. However, the frequency is shifted down  $\approx$  10 GHz, which corresponds to less than 4%.

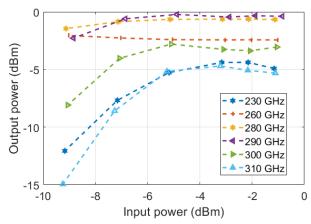

The output power of the octupler was measured for varying input power, between -9 and -1 dBm. In Fig. 11, the result for 230, 260, 280, 290, 300 and 310 GHz can be seen. An input power of -5 dBm is enough to saturate the multiplier. 290 GHz has the highest output power, and 260 GHz is saturated for the entire sweep.

The total DC power consumption for the octupler is 122 mW, and the maximum conversion gain is 4.5 dB.

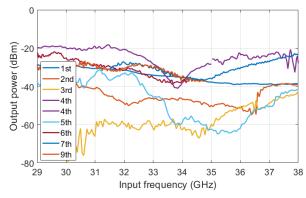

The unwanted harmonics were characterized (Fig. 12) in the same way as the 8th harmonic. The 9th, 7th and 6th harmonic was measured using the same extender (WR 3.4).

Fig. 10. Measured and simulated output power of the 8th harmonic. The input power was  $-5~\mathrm{dBm}$ .

Fig. 11. Measured output power vs input power for different frequencies.

The 5th harmonic was measured using a WR 5.1 extender and the corresponding probe. The 4th harmonic was also measured with the WR 5.1 extender, as well as with a WR 8.0 extender. The 3rd harmonic used the WR 8.0 extender, and the 2nd harmonic used WR 12.0. The fundamental tone was measured using a 67 GHz infinity probe. The input power was -2 dBm, which is double the input power required for the octupler.

Fig. 12. Measured power of the unwanted harmonics harmonic. The input power was  $-2~\mathrm{dBm}$ .

Table 1. Comparison with other 200+ GHz frequency multipliers in SiGe BiCMOS

| Reference          | [4]     | [5]     | [6]     | [7]     | [8]     | [9]     | [this work] |

|--------------------|---------|---------|---------|---------|---------|---------|-------------|

| $f_t/f_{ m max}$   | 250/370 | 350/450 | 350/450 | 470/650 | 350/450 | 470/650 | 300/500     |

| Frequency          | 210-291 | 281-320 | 245-295 | 244-300 | 212–260 | 238–278 | 234-305     |

| (GHz)              |         |         |         |         |         |         |             |

| Multiplication     | 8       | 4       | 8       | 9       | 4       | 6       | 8           |

| factor             |         |         |         |         |         |         |             |

| Fractional         | 32.3    | 13.0    | 18.5    | 20.7    | 20.3    | 15.5    | 26.3        |

| bandwidth (%)      |         |         |         |         |         |         |             |

| $P_{\mathbf{sat}}$ | -7.7    | 2.5     | -5      | 9.6     | 5.5     | 4.3     | -0.5        |

| (dBm)              |         |         |         |         |         |         |             |

| Harmonic           | >22.3   | N/A     | >25     | >30     | >20*    | >20     | >18         |

| suppression (dB)   |         |         |         |         |         |         |             |

| DC power           | 240     | 384     | 125     | 660     | 270     | 119     | 122         |

| (mŴ)               |         |         |         |         |         |         |             |

\*simulated value

### IV. CONCLUSION

In this work, an H-band octupler in a SiGe BiCMOS technology is designed and evaluated. In Table 1 the circuit is compared with other 200+ GHz SiGe BiCMOS multipliers. It achieves the second largest fractional bandwidth, with almost half the DC power consumption and more than 4 times the output power. The frequency multiplier only needs -5 dBm input power and has a maximum conversion gain of 4.5 dB. It has a 3-dB bandwidth that covers more than 70 GHz. Furthermore, it is area efficient using only 0.725 mm<sup>2</sup>. The circuit is an excellent candidate for energy efficient, ultra-broadband H-band communication and radar systems.

### ACKNOWLEDGMENT

This work is funded in part by the COREnext project supported by the EU Horizon Europe research and innovation programme under grant agreement No. 101092598. This work is also funded in part by the TeraGreen project which has received funding from the Smart Networks and Services Joint Undertaking (SNS JU) under the European Union's Horizon Europe research and innovation programme under Grant Agreement No 101139117.

#### REFERENCES

- U. Soylu, A. Alizadeh, M. Seo, and M. J. Rodwell, "280-ghz frequency multiplier chains in 250-nm inp hbt technology," *IEEE Journal of Solid-State Circuits*, vol. 58, 9 2023, ISSN: 1558173X. DOI: 10.1109/ JSSC.2023.3292182.

- [2] C. M. Grotsch, S. Wagner, A. Leuther, D. Meier, and I. Kallfass, "Ultra-broadband frequency multiplier mmics for communication and radar applications," in *EuMIC* 2018 - 2018 13th European Microwave Integrated Circuits Conference, 2018. DOI: 10.23919/EuMIC.2018. 8539865.

- [3] R. Dong, S. Hara, I. Watanabe, S. Tanoi, T. Hagino, and A. Kasamatsu, "A 213-233 ghz x9 frequency multiplier chain with 4.1 dbm output power in 40nm bulk cmos," in *IEEE MTT-S International Microwave Symposium Digest*, vol. 2021-June, 2021. DOI: 10.1109/IMS19712. 2021.9574846.

- [4] T. Buecher, S. Malz, K. Aufinger, and U. R. Pfeiffer, "A 210-291-ghz (8x) frequency multiplier chain with low power consumption in 0.13-m sige," *IEEE Microwave and Wireless Components Letters*, vol. 30, 5 2020, ISSN: 15581764. DOI: 10.1109/LMWC.2020.2979715.

- [5] P. Zhou, J. Chen, P. Yan, Z. Chen, D. Hou, and W. Hong, "A 280-325 ghz frequency multiplier chain with 2.5 dbm peak output power," in *Proceedings of the Custom Integrated Circuits Conference*, vol. 2019-April, 2019. DOI: 10.1109/CICC.2019.8780333.

- [6] A. Gadallah, M. H. Eissa, T. Mausolf, D. Kissinger, and A. Malignaggi, "A 250-300 ghz frequency multiplier-by-8 chain in sige technology," in *IEEE MTT-S International Microwave Symposium Digest*, vol. 2022-June, 2022. DOI: 10.1109/IMS37962.2022.9865638.

- [7] A. C. Prabhu, J. Grzyb, P. Hillger, T. Bucher, H. Rucker, and U. Pfeiffer, "A 300 ghz x9 multiplier chain with 9.6 dbm output power in 0.13-m sige technology," in 2024 IEEE Radio and Wireless Week, RWW 2024 - 2024 IEEE 24th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, SiRF 2024, 2024. DOI: 10.1109/ SiRF59913.2024.10438581.

- [8] J. Yu, J. Chen, Z. Li, D. Hou, Z. Chen, and W. Hong, "A 212-260 ghz broadband frequency multiplier chain (x4) in 130-nm bicmos technology," in *IEEE MTT-S International Microwave Symposium Digest*, vol. 2021-June, 2021. DOI: 10.1109/IMS19712.2021.9575010.

- [9] M. Möck, K. Balaban, and A. Ulusoy, "A compact 238–278-ghz frequency sextupler based on a single bootstrapped gilbert cell," *IEEE Transactions on Microwave Theory and Techniques*, pp. 1–11, 2024. DOI: 10.1109/TMTT.2024.3520824.

- [10] P. Chevalier, W. Liebl, H. RÜcker, et al., "Sige bicmos current status and future trends in europe," in 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2018, pp. 64–71. DOI: 10.1109/BCICTS.2018. 8550963.